Professional Documents

Culture Documents

Puassembly Instructions & General Information: 23006 - 611 User Manual

Puassembly Instructions & General Information: 23006 - 611 User Manual

Uploaded by

freddy brigstoneCopyright:

Available Formats

You might also like

- StreamCaster 4400 OEM Integration Manual v1.0Document9 pagesStreamCaster 4400 OEM Integration Manual v1.0236251457.hcNo ratings yet

- BI1202-I Flex Focus Service ManualDocument135 pagesBI1202-I Flex Focus Service ManualПавел Геннадьевич100% (2)

- BG825 Om 27.02.15Document158 pagesBG825 Om 27.02.15bml100% (2)

- Helicopter PDFDocument57 pagesHelicopter PDFEdi GuarnizoNo ratings yet

- PLC Automation of Cartoning Machine IC 150Document18 pagesPLC Automation of Cartoning Machine IC 150shashi1986100% (5)

- 21.2 HYDAC KineSys HFI-MM Commissioning Instruction V1.0 變頻馬達DAV-Kit 試車說明Document30 pages21.2 HYDAC KineSys HFI-MM Commissioning Instruction V1.0 變頻馬達DAV-Kit 試車說明Maxi GonzalezNo ratings yet

- Skema Ic ProgramDocument16 pagesSkema Ic ProgramAndy AnsahNo ratings yet

- IDBS07 and IDBM07 Wiring Manual: February 2008Document16 pagesIDBS07 and IDBM07 Wiring Manual: February 2008phankhoa83-1No ratings yet

- DVP-MC I Mul 20120507Document20 pagesDVP-MC I Mul 20120507Rafael ZilsNo ratings yet

- Conexiones - BazánDocument3 pagesConexiones - BazánJavier Vidal GonzalesNo ratings yet

- MICOM P139 CortecDocument1 pageMICOM P139 CortecSvetla IvanovaNo ratings yet

- Manual Tuxon C Uo3rDocument64 pagesManual Tuxon C Uo3relkin carrilloNo ratings yet

- Infineon Tle7230r Ds v03 04 enDocument15 pagesInfineon Tle7230r Ds v03 04 enياسين الطنفوريNo ratings yet

- CAN CommunicationDocument12 pagesCAN Communicationsuguamaran mNo ratings yet

- Grundig gmm1100-stf55-1001 t2s08 Chassis (ET)Document23 pagesGrundig gmm1100-stf55-1001 t2s08 Chassis (ET)Simion VictorasNo ratings yet

- OpenVPX - B196910460 - BKP6 CEN10 11.2.4 4Document11 pagesOpenVPX - B196910460 - BKP6 CEN10 11.2.4 4NorozKhanNo ratings yet

- Datasheet Micro M65582AMF-105FPDocument46 pagesDatasheet Micro M65582AMF-105FPsel_mor100% (1)

- Electronic Control (Machine System) : Systems OperationDocument25 pagesElectronic Control (Machine System) : Systems OperationMbahdiro KolenxNo ratings yet

- Kenwood Kdc-448u Kdc-5051u kdc-5751sd Kdc-Bt51u Kdc-Bt848u Kdc-U6049 Kdc-U6049l Kdc-U7049bt Kdc-U7049btl kdc-x595 kdc-x895Document54 pagesKenwood Kdc-448u Kdc-5051u kdc-5751sd Kdc-Bt51u Kdc-Bt848u Kdc-U6049 Kdc-U6049l Kdc-U7049bt Kdc-U7049btl kdc-x595 kdc-x895EdwarddSandy100% (1)

- Data SheetDocument12 pagesData SheetpunithNo ratings yet

- Manual de Servicio Lider 25 29 y 34 TMPA8859Document14 pagesManual de Servicio Lider 25 29 y 34 TMPA8859Joel Roberto MolinaNo ratings yet

- 3Y11 FullDocument24 pages3Y11 FulltodorloncarskiNo ratings yet

- Short Sm2a GB - 1849Document7 pagesShort Sm2a GB - 1849Ady MihailaNo ratings yet

- Chassis Sanyo Con UOC TMPA8823-5VA4 Manual de ServicioDocument16 pagesChassis Sanyo Con UOC TMPA8823-5VA4 Manual de ServicioRobert Vicuña100% (1)

- CHAMPION Microcontroller.1Document5 pagesCHAMPION Microcontroller.1Vinay KunwarNo ratings yet

- TV/VCR Tuner Ic With DC/DC Converter: FeaturesDocument21 pagesTV/VCR Tuner Ic With DC/DC Converter: FeaturesEdsel SilvaNo ratings yet

- Philips Chassis Tpm6.1e LaDocument112 pagesPhilips Chassis Tpm6.1e LatarpinoNo ratings yet

- Argus 7SR22Document1 pageArgus 7SR22Arun dasNo ratings yet

- Sanyo TVS-2542MDocument15 pagesSanyo TVS-2542MMartin Antonio Bautista CastilloNo ratings yet

- KDC Mp7090uDocument46 pagesKDC Mp7090uAntonio SaitoNo ratings yet

- Dephy DS ActPack41Document7 pagesDephy DS ActPack41sanchitNo ratings yet

- 2 Page S40 Data SheetDocument2 pages2 Page S40 Data SheetThinh DaoNo ratings yet

- PAC5527EVK1 UserManual Rev1p0Document11 pagesPAC5527EVK1 UserManual Rev1p0avv81419No ratings yet

- TDA8366Document48 pagesTDA8366Rigoberto Martinez LopezNo ratings yet

- Arduino Pin Mapping On FBV 2560Document3 pagesArduino Pin Mapping On FBV 2560Ashish YadavNo ratings yet

- GS-Oolite Spec V1.14Document5 pagesGS-Oolite Spec V1.14Abbas Raza ZaidiNo ratings yet

- AC6900A规格书V1 2Document14 pagesAC6900A规格书V1 2ghNo ratings yet

- RENAULT Scube Standard Dressout & Controller Details (2014)Document26 pagesRENAULT Scube Standard Dressout & Controller Details (2014)franck.nzonzitenwhil.comNo ratings yet

- New Microsoft Word DocumentDocument11 pagesNew Microsoft Word DocumentsaravananNo ratings yet

- Kuman 3.5 Inch Touch Screen DatasheetDocument15 pagesKuman 3.5 Inch Touch Screen DatasheetMarcGarciaNo ratings yet

- Short Sb4a3042x261 00 GB - 1757Document8 pagesShort Sb4a3042x261 00 GB - 1757NIO NIETONo ratings yet

- Tda 18211 HDDocument16 pagesTda 18211 HDMohammad IsmailNo ratings yet

- 74ABT245 Octal Transceiver With Direction Pin (3-State) : Features DescriptionDocument6 pages74ABT245 Octal Transceiver With Direction Pin (3-State) : Features DescriptionBontha RajuNo ratings yet

- Philips 32pfl5605 LC9.3LDocument85 pagesPhilips 32pfl5605 LC9.3Ldivubi20040% (1)

- TV Led Philips Chassi LC9.2LADocument85 pagesTV Led Philips Chassi LC9.2LAJandira Santos0% (1)

- Users Manual 1249702Document15 pagesUsers Manual 1249702Faber Alexis Maldonado PembertyNo ratings yet

- 04 - 4L-QSFP - 4SFPPxDocument5 pages04 - 4L-QSFP - 4SFPPxLeonardo FiúzaNo ratings yet

- TDA8425Document24 pagesTDA8425Muhammad IsmailNo ratings yet

- 74LVT244ADocument11 pages74LVT244Aatomo atomoNo ratings yet

- LCBTHT 6Document16 pagesLCBTHT 6hermesNo ratings yet

- Wabtec - Digital Mine - PROD1182 BROCHURE EN FDocument2 pagesWabtec - Digital Mine - PROD1182 BROCHURE EN FAlvaro Morales MendozaNo ratings yet

- Rak3172-Sip Wisduo Lpwan Sip Datasheet: DescriptionDocument9 pagesRak3172-Sip Wisduo Lpwan Sip Datasheet: DescriptionoliviercorianNo ratings yet

- GS-232B Om Eng Eaa14x105Document24 pagesGS-232B Om Eng Eaa14x105bsaylor123No ratings yet

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142From EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Exploring Arduino: Tools and Techniques for Engineering WizardryFrom EverandExploring Arduino: Tools and Techniques for Engineering WizardryRating: 4.5 out of 5 stars4.5/5 (5)

- The Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsFrom EverandThe Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsSylvain ClercNo ratings yet

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDFrom EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Performance Analysis 5Mwp Solar PV PlantDocument26 pagesPerformance Analysis 5Mwp Solar PV PlantKanika KhannaNo ratings yet

- Aa75a-M1t Bios 111028Document35 pagesAa75a-M1t Bios 111028JuscaNo ratings yet

- Apx1000-2000-4000 Service Manual 68012004061 f-11Document96 pagesApx1000-2000-4000 Service Manual 68012004061 f-11buenodrNo ratings yet

- Msp74Ja: Differential Pressure SwitchDocument1 pageMsp74Ja: Differential Pressure SwitchChhomNo ratings yet

- Um3ab1 Cylinder HeadDocument2 pagesUm3ab1 Cylinder HeadBurik8100% (1)

- 5MZ4500T Electrical Scheme PDFDocument57 pages5MZ4500T Electrical Scheme PDFKishan BhartiNo ratings yet

- LG MDD62 Service Manual PDFDocument69 pagesLG MDD62 Service Manual PDFIvan AsimovNo ratings yet

- The CMOS Inverter: Slides Adapted From: N. Weste, D. Harris, CMOS VLSI Design,, 3/e, 2004Document27 pagesThe CMOS Inverter: Slides Adapted From: N. Weste, D. Harris, CMOS VLSI Design,, 3/e, 2004Priyanka AshishNo ratings yet

- 25 Series: Power - Reserve ReserveDocument10 pages25 Series: Power - Reserve ReservefazalNo ratings yet

- Table T-233.1 For RTDocument1 pageTable T-233.1 For RTLipika GayenNo ratings yet

- SchneiderDocument46 pagesSchneiderTareq JildehNo ratings yet

- DE2-115 Computer NiosIIDocument63 pagesDE2-115 Computer NiosIITran Quang Thai B1708908No ratings yet

- Service Manual: WM-GX400Document30 pagesService Manual: WM-GX400london335No ratings yet

- Mil-Dtl-38999 2015 - Corsair - Electrical - CatalogDocument106 pagesMil-Dtl-38999 2015 - Corsair - Electrical - CatalogAVDBNo ratings yet

- Outdoor Lighting Control Details SKi Village-ModelDocument1 pageOutdoor Lighting Control Details SKi Village-ModelAmr EidNo ratings yet

- TransferDocument51 pagesTransferWaqas HaiderNo ratings yet

- Uei DL39 Instruction ManualDocument7 pagesUei DL39 Instruction ManualBlue AlienNo ratings yet

- Osw sw14Document3 pagesOsw sw14Carlos AlbertoNo ratings yet

- HIPASE-E 002-CP-300 Processor BoardDocument7 pagesHIPASE-E 002-CP-300 Processor BoardChi PhamNo ratings yet

- Fast, Connections: Leak FreeDocument8 pagesFast, Connections: Leak FreeEnrique AssmannNo ratings yet

- Simulasi Ryzen 5600 + RTX 2060 + Lenovo Ideapad Slim 3i 14I - Enterkomputer Jual Beli Online Komputer, Rakit PC, Termurah & TerlengkapDocument3 pagesSimulasi Ryzen 5600 + RTX 2060 + Lenovo Ideapad Slim 3i 14I - Enterkomputer Jual Beli Online Komputer, Rakit PC, Termurah & TerlengkapAlfianardiwNo ratings yet

- KP1 PDFDocument1 pageKP1 PDFarllanbdNo ratings yet

- Appliance DiagnosisDocument76 pagesAppliance Diagnosisjergreen6100% (1)

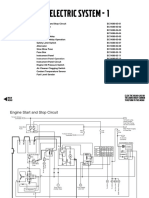

- Electric System - 1: Master Switch Battery RelayDocument18 pagesElectric System - 1: Master Switch Battery RelayInjeletro Diesel100% (2)

- Vantrue N2 Pro Dashcam ManualDocument75 pagesVantrue N2 Pro Dashcam Manual88quiznos88No ratings yet

- Tr110 Portable Roughness Tester Instruction ManualDocument12 pagesTr110 Portable Roughness Tester Instruction ManualandresNo ratings yet

Puassembly Instructions & General Information: 23006 - 611 User Manual

Puassembly Instructions & General Information: 23006 - 611 User Manual

Uploaded by

freddy brigstoneOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Puassembly Instructions & General Information: 23006 - 611 User Manual

Puassembly Instructions & General Information: 23006 - 611 User Manual

Uploaded by

freddy brigstoneCopyright:

Available Formats

23006 - 611 User Manual

puAssembly Instructions & general Information

1. Mechanical Mounting: Attach the backplane through the mounting holes in at least every second

connector position at top and bottom of the CPCI and power slots slots using M2,5 screws and isolating

washers.

2. VI/O: Check VI/O coding and VI/O (power) bridge, default assembly is +5V (blue key at connector P1). If

VI/O shall be set to 3,3V, use conversion kit (order# 21101-658, including keys and tool) to change keys

and move the bridge between the power slots.

3. Geographical Addressing (GA) is set by default to start from number one from bottom position within the

chassis.A change of geographical addresses can be made. Cut copper links in between SMD pads to

open, and zero Ohm resistors to close. Package size shall be 0603. Position is labelled "nGA[x]" where

"n" stands for slot# , and "x" for address#, see drawing #1.

4. Hot Swap: Schroff CPCI backplanes fulfil the requirements for Basic Hot Swap of the Hot Swap

Specification PICMG 2.1 R2.0. The signal BD_SEL# is tied to GND by a removable copper link. It can be

replaced by a resistor-capacitor combination, both of package size 0603. Position is labelled "nB" where

"n" stands for slot# , see drawing.

5. Dimensions 405.45 x 161.56mm

6. Power input: Power input is realized with P47 connectors below the CPCI slots. 2 CPCI power input slots

(3U, 8HP) are equipped with the P47 connectors. 2 additional power slots can be equipped on request.

The AC power is brought to the P47 connectors by “feed through” contacts.

7. Assembling of Power Cables (optional power output using the power bugs): M4 cable lugs should

be used to connect the power output cables to the powerbugs on the backplane. Maximum 2 cables are

allowed per powerbug. Please assemble the cable lugs with the flat side to the power bug to ensure the

correct isolation distance between unisolated part of the power cable and unisolated parts of the

backplane.

Correct orientation Wrong orientation

Cable

Cable

Powerbug Powerbug

8. CPSB Links / H.110 Bus

• 2 Fabric Slots including optional Link between both

• 5 Node Slots, Node capability of the CPCI system slot can be implemented on request

• 2 PSU Slots acc. to PICMG 2.11 (2x 3U PSU’s)

• Fabric Slots are placed right of the Node Slots

• CompactPCI bus (PICMG2.0 R.3.0) is implemented at all 8 Slots, 64-bit, System slot left

• Computer Telephony Bus (H.110) is implemented on the P4 area, Slot 2 to 6

• Applicable Specifications:

PICMG 2.16 R1.0 Packed Switched Backplane

PICMG 2.5 R1.0 Computer Telephony Specification

PICMG 2.0 R3.0 CPCI Core Specification

PICMG 2.01 R2.0 Hot Swap

PICMG 2.09 R1.0 System Management Bus

PICMG 2.10 R1.0 Keying

PICMG 2.11 R1.0 Power Interface Specification

Schroff GmbH, May 2006; Document#: 63972-216 Rev.000

www.schroff.de Page 1 of 3

23006 - 611 User Manual

Rear I/O Rear I/O Fabric b cPCI 64-bit peripheral 8

P47 PSU Slot (X130)

Rear I/O Rear I/O Fabric a cPCI 64-bit peripheral

7

Rear I/O H.110 Node 1 cPCI 64-bit peripheral 6

P47 PSU Slot (X140)

Rear I/O H.110 Node 2 cPCI 64-bit peripheral 5

Rear I/O H.110 Node 3 cPCI 64-bit peripheral 4

optional PSU Slot (X120)

Rear I/O H.110 Node 4 cPCI 64-bit peripheral 3

Rear I/O H.110 Node 5 cPCI 64-bit peripheral 2

optional PSU Slot (X110)

Rear I/O Rear I/O optional cPCI 64-bit System Slot

1

23006-611 Backplane Topology (front view)

23006-611 Backplane (rear view)

Schroff GmbH, May 2006; Document#: 63972-216 Rev.000

www.schroff.de Page 2 of 3

23006 - 611 User Manual

Connectors:

Fan P47 (X110 – X140) Status

1 +12V Pin# Signal Name Description

2 +12V 1 V1 V1 Output (+5V)

3 GND 2 V1 V1 Output (+5V)

4 GND 3 V1 V1 Output (+5V)

5 +5V 4 V1 V1 Output (+5V)

6 fanfail 5 RTN V1 and V2 Return (GND)

7 tempfail 5 RTN V1 and V2 Return (GND)

8 GND 7 RTN V1 and V2 Return (GND)

9 Signal 1 8 RTN V1 and V2 Return (GND)

10 Signal 2 9 RTN V1 and V2 Return (GND)

10 RTN V1 and V2 Return (GND)

11 RTN V1 and V2 Return (GND)

12 RTN V1 and V2 Return (GND)

INH# 13 V2 V2 Output (3,3V)

1 INH# 14 V2 V2 Output (3,3V)

2 GND 15 V2 V2 Output (3,3V)

16 V2 V2 Output (3,3V)

17 V2 V2 Output (3,3V)

Sig1 18 V2 V2 Output (3,3V)

19 RTN V3 Return (GND)

1 nc 20 V3 V3 Output (+12V)

2 GND 21 V4 V4 Output (-12V)

3 Signal 1 22 RTN Signal Return (GND)

23 RESERVED Reserved

24 RTN V4 V4 Return (GND)

Sig2 25 GA0 Geographic Address Bit 0

26 RESERVED Reserved

1 nc 27 EN# Enable (set to GND)

2 GND 28 GA1 Geographic Address Bit 1

3 Signal 2 29 V1ADJ V1 Adjust

30 V1 SENSE V1 Remote Sense

31 GA2 Geographic Address Bit 2

X155 32 V2ADJ V2 Adjust

33 V2 SENSE V2 Remote Sense

1 +5V 34 S RTN Sense Return

2 GND 35 V1 SHARE V1 Current Share

36 V3 SENSE V3 Remote Sense

3 GND 37 IPMB_SCL System Management Bus

38 DEG# Degrade Signal

4 +12V

39 INH# Inhibit

40 IPMB_SDA System Management Bus

41 V2 SHARE V2 Current Share

42 FAL# Fail Signal

43 IPMB_PWR System Management Bus

44 V3 SHARE V3 Current Share

45 CGND Chassis Ground (safety

ground)

46 ACN/+DC IN AC Input – Neutral; +DC

Input

47 ACL/-DC IN AC Input – Line; =-DC

Input

Schroff GmbH, May 2006; Document#: 63972-216 Rev.000

www.schroff.de Page 3 of 3

You might also like

- StreamCaster 4400 OEM Integration Manual v1.0Document9 pagesStreamCaster 4400 OEM Integration Manual v1.0236251457.hcNo ratings yet

- BI1202-I Flex Focus Service ManualDocument135 pagesBI1202-I Flex Focus Service ManualПавел Геннадьевич100% (2)

- BG825 Om 27.02.15Document158 pagesBG825 Om 27.02.15bml100% (2)

- Helicopter PDFDocument57 pagesHelicopter PDFEdi GuarnizoNo ratings yet

- PLC Automation of Cartoning Machine IC 150Document18 pagesPLC Automation of Cartoning Machine IC 150shashi1986100% (5)

- 21.2 HYDAC KineSys HFI-MM Commissioning Instruction V1.0 變頻馬達DAV-Kit 試車說明Document30 pages21.2 HYDAC KineSys HFI-MM Commissioning Instruction V1.0 變頻馬達DAV-Kit 試車說明Maxi GonzalezNo ratings yet

- Skema Ic ProgramDocument16 pagesSkema Ic ProgramAndy AnsahNo ratings yet

- IDBS07 and IDBM07 Wiring Manual: February 2008Document16 pagesIDBS07 and IDBM07 Wiring Manual: February 2008phankhoa83-1No ratings yet

- DVP-MC I Mul 20120507Document20 pagesDVP-MC I Mul 20120507Rafael ZilsNo ratings yet

- Conexiones - BazánDocument3 pagesConexiones - BazánJavier Vidal GonzalesNo ratings yet

- MICOM P139 CortecDocument1 pageMICOM P139 CortecSvetla IvanovaNo ratings yet

- Manual Tuxon C Uo3rDocument64 pagesManual Tuxon C Uo3relkin carrilloNo ratings yet

- Infineon Tle7230r Ds v03 04 enDocument15 pagesInfineon Tle7230r Ds v03 04 enياسين الطنفوريNo ratings yet

- CAN CommunicationDocument12 pagesCAN Communicationsuguamaran mNo ratings yet

- Grundig gmm1100-stf55-1001 t2s08 Chassis (ET)Document23 pagesGrundig gmm1100-stf55-1001 t2s08 Chassis (ET)Simion VictorasNo ratings yet

- OpenVPX - B196910460 - BKP6 CEN10 11.2.4 4Document11 pagesOpenVPX - B196910460 - BKP6 CEN10 11.2.4 4NorozKhanNo ratings yet

- Datasheet Micro M65582AMF-105FPDocument46 pagesDatasheet Micro M65582AMF-105FPsel_mor100% (1)

- Electronic Control (Machine System) : Systems OperationDocument25 pagesElectronic Control (Machine System) : Systems OperationMbahdiro KolenxNo ratings yet

- Kenwood Kdc-448u Kdc-5051u kdc-5751sd Kdc-Bt51u Kdc-Bt848u Kdc-U6049 Kdc-U6049l Kdc-U7049bt Kdc-U7049btl kdc-x595 kdc-x895Document54 pagesKenwood Kdc-448u Kdc-5051u kdc-5751sd Kdc-Bt51u Kdc-Bt848u Kdc-U6049 Kdc-U6049l Kdc-U7049bt Kdc-U7049btl kdc-x595 kdc-x895EdwarddSandy100% (1)

- Data SheetDocument12 pagesData SheetpunithNo ratings yet

- Manual de Servicio Lider 25 29 y 34 TMPA8859Document14 pagesManual de Servicio Lider 25 29 y 34 TMPA8859Joel Roberto MolinaNo ratings yet

- 3Y11 FullDocument24 pages3Y11 FulltodorloncarskiNo ratings yet

- Short Sm2a GB - 1849Document7 pagesShort Sm2a GB - 1849Ady MihailaNo ratings yet

- Chassis Sanyo Con UOC TMPA8823-5VA4 Manual de ServicioDocument16 pagesChassis Sanyo Con UOC TMPA8823-5VA4 Manual de ServicioRobert Vicuña100% (1)

- CHAMPION Microcontroller.1Document5 pagesCHAMPION Microcontroller.1Vinay KunwarNo ratings yet

- TV/VCR Tuner Ic With DC/DC Converter: FeaturesDocument21 pagesTV/VCR Tuner Ic With DC/DC Converter: FeaturesEdsel SilvaNo ratings yet

- Philips Chassis Tpm6.1e LaDocument112 pagesPhilips Chassis Tpm6.1e LatarpinoNo ratings yet

- Argus 7SR22Document1 pageArgus 7SR22Arun dasNo ratings yet

- Sanyo TVS-2542MDocument15 pagesSanyo TVS-2542MMartin Antonio Bautista CastilloNo ratings yet

- KDC Mp7090uDocument46 pagesKDC Mp7090uAntonio SaitoNo ratings yet

- Dephy DS ActPack41Document7 pagesDephy DS ActPack41sanchitNo ratings yet

- 2 Page S40 Data SheetDocument2 pages2 Page S40 Data SheetThinh DaoNo ratings yet

- PAC5527EVK1 UserManual Rev1p0Document11 pagesPAC5527EVK1 UserManual Rev1p0avv81419No ratings yet

- TDA8366Document48 pagesTDA8366Rigoberto Martinez LopezNo ratings yet

- Arduino Pin Mapping On FBV 2560Document3 pagesArduino Pin Mapping On FBV 2560Ashish YadavNo ratings yet

- GS-Oolite Spec V1.14Document5 pagesGS-Oolite Spec V1.14Abbas Raza ZaidiNo ratings yet

- AC6900A规格书V1 2Document14 pagesAC6900A规格书V1 2ghNo ratings yet

- RENAULT Scube Standard Dressout & Controller Details (2014)Document26 pagesRENAULT Scube Standard Dressout & Controller Details (2014)franck.nzonzitenwhil.comNo ratings yet

- New Microsoft Word DocumentDocument11 pagesNew Microsoft Word DocumentsaravananNo ratings yet

- Kuman 3.5 Inch Touch Screen DatasheetDocument15 pagesKuman 3.5 Inch Touch Screen DatasheetMarcGarciaNo ratings yet

- Short Sb4a3042x261 00 GB - 1757Document8 pagesShort Sb4a3042x261 00 GB - 1757NIO NIETONo ratings yet

- Tda 18211 HDDocument16 pagesTda 18211 HDMohammad IsmailNo ratings yet

- 74ABT245 Octal Transceiver With Direction Pin (3-State) : Features DescriptionDocument6 pages74ABT245 Octal Transceiver With Direction Pin (3-State) : Features DescriptionBontha RajuNo ratings yet

- Philips 32pfl5605 LC9.3LDocument85 pagesPhilips 32pfl5605 LC9.3Ldivubi20040% (1)

- TV Led Philips Chassi LC9.2LADocument85 pagesTV Led Philips Chassi LC9.2LAJandira Santos0% (1)

- Users Manual 1249702Document15 pagesUsers Manual 1249702Faber Alexis Maldonado PembertyNo ratings yet

- 04 - 4L-QSFP - 4SFPPxDocument5 pages04 - 4L-QSFP - 4SFPPxLeonardo FiúzaNo ratings yet

- TDA8425Document24 pagesTDA8425Muhammad IsmailNo ratings yet

- 74LVT244ADocument11 pages74LVT244Aatomo atomoNo ratings yet

- LCBTHT 6Document16 pagesLCBTHT 6hermesNo ratings yet

- Wabtec - Digital Mine - PROD1182 BROCHURE EN FDocument2 pagesWabtec - Digital Mine - PROD1182 BROCHURE EN FAlvaro Morales MendozaNo ratings yet

- Rak3172-Sip Wisduo Lpwan Sip Datasheet: DescriptionDocument9 pagesRak3172-Sip Wisduo Lpwan Sip Datasheet: DescriptionoliviercorianNo ratings yet

- GS-232B Om Eng Eaa14x105Document24 pagesGS-232B Om Eng Eaa14x105bsaylor123No ratings yet

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142From EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Exploring Arduino: Tools and Techniques for Engineering WizardryFrom EverandExploring Arduino: Tools and Techniques for Engineering WizardryRating: 4.5 out of 5 stars4.5/5 (5)

- The Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsFrom EverandThe Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsSylvain ClercNo ratings yet

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDFrom EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Performance Analysis 5Mwp Solar PV PlantDocument26 pagesPerformance Analysis 5Mwp Solar PV PlantKanika KhannaNo ratings yet

- Aa75a-M1t Bios 111028Document35 pagesAa75a-M1t Bios 111028JuscaNo ratings yet

- Apx1000-2000-4000 Service Manual 68012004061 f-11Document96 pagesApx1000-2000-4000 Service Manual 68012004061 f-11buenodrNo ratings yet

- Msp74Ja: Differential Pressure SwitchDocument1 pageMsp74Ja: Differential Pressure SwitchChhomNo ratings yet

- Um3ab1 Cylinder HeadDocument2 pagesUm3ab1 Cylinder HeadBurik8100% (1)

- 5MZ4500T Electrical Scheme PDFDocument57 pages5MZ4500T Electrical Scheme PDFKishan BhartiNo ratings yet

- LG MDD62 Service Manual PDFDocument69 pagesLG MDD62 Service Manual PDFIvan AsimovNo ratings yet

- The CMOS Inverter: Slides Adapted From: N. Weste, D. Harris, CMOS VLSI Design,, 3/e, 2004Document27 pagesThe CMOS Inverter: Slides Adapted From: N. Weste, D. Harris, CMOS VLSI Design,, 3/e, 2004Priyanka AshishNo ratings yet

- 25 Series: Power - Reserve ReserveDocument10 pages25 Series: Power - Reserve ReservefazalNo ratings yet

- Table T-233.1 For RTDocument1 pageTable T-233.1 For RTLipika GayenNo ratings yet

- SchneiderDocument46 pagesSchneiderTareq JildehNo ratings yet

- DE2-115 Computer NiosIIDocument63 pagesDE2-115 Computer NiosIITran Quang Thai B1708908No ratings yet

- Service Manual: WM-GX400Document30 pagesService Manual: WM-GX400london335No ratings yet

- Mil-Dtl-38999 2015 - Corsair - Electrical - CatalogDocument106 pagesMil-Dtl-38999 2015 - Corsair - Electrical - CatalogAVDBNo ratings yet

- Outdoor Lighting Control Details SKi Village-ModelDocument1 pageOutdoor Lighting Control Details SKi Village-ModelAmr EidNo ratings yet

- TransferDocument51 pagesTransferWaqas HaiderNo ratings yet

- Uei DL39 Instruction ManualDocument7 pagesUei DL39 Instruction ManualBlue AlienNo ratings yet

- Osw sw14Document3 pagesOsw sw14Carlos AlbertoNo ratings yet

- HIPASE-E 002-CP-300 Processor BoardDocument7 pagesHIPASE-E 002-CP-300 Processor BoardChi PhamNo ratings yet

- Fast, Connections: Leak FreeDocument8 pagesFast, Connections: Leak FreeEnrique AssmannNo ratings yet

- Simulasi Ryzen 5600 + RTX 2060 + Lenovo Ideapad Slim 3i 14I - Enterkomputer Jual Beli Online Komputer, Rakit PC, Termurah & TerlengkapDocument3 pagesSimulasi Ryzen 5600 + RTX 2060 + Lenovo Ideapad Slim 3i 14I - Enterkomputer Jual Beli Online Komputer, Rakit PC, Termurah & TerlengkapAlfianardiwNo ratings yet

- KP1 PDFDocument1 pageKP1 PDFarllanbdNo ratings yet

- Appliance DiagnosisDocument76 pagesAppliance Diagnosisjergreen6100% (1)

- Electric System - 1: Master Switch Battery RelayDocument18 pagesElectric System - 1: Master Switch Battery RelayInjeletro Diesel100% (2)

- Vantrue N2 Pro Dashcam ManualDocument75 pagesVantrue N2 Pro Dashcam Manual88quiznos88No ratings yet

- Tr110 Portable Roughness Tester Instruction ManualDocument12 pagesTr110 Portable Roughness Tester Instruction ManualandresNo ratings yet