Professional Documents

Culture Documents

CAD For IC Design: (MEL ZG641)

CAD For IC Design: (MEL ZG641)

Uploaded by

Nitin PatelCopyright:

Available Formats

You might also like

- Samsung rv511 SchematicDocument52 pagesSamsung rv511 SchematicGanesh Prasad50% (2)

- Solution Manual For Engineering Design Graphics Sketching Modeling and Visualization Leake 2nd EditionDocument3 pagesSolution Manual For Engineering Design Graphics Sketching Modeling and Visualization Leake 2nd EditionCory Smith100% (37)

- CSC Orion TutorialDocument190 pagesCSC Orion TutorialBenedict OgbaghaNo ratings yet

- 2004 Sportsman 700 - Parts ManualDocument61 pages2004 Sportsman 700 - Parts ManualGregoryKaufmann100% (1)

- Article Parametric Design of Steel StructuresDocument11 pagesArticle Parametric Design of Steel StructuresRamkishore ChelvinMurugeshNo ratings yet

- Engineering Drawing EE-155 Lab Manual-2Document27 pagesEngineering Drawing EE-155 Lab Manual-2abdulsamadNo ratings yet

- Module PBM9 (BCD 7 Segment Introduction)Document14 pagesModule PBM9 (BCD 7 Segment Introduction)Fajar FatahillahNo ratings yet

- Module 5Document18 pagesModule 5Cherrie Mae DiazNo ratings yet

- Ge6261 Computer Aided Drafting and Modeling Lab (Mech)Document43 pagesGe6261 Computer Aided Drafting and Modeling Lab (Mech)T.A. Sundara VadivelNo ratings yet

- RM Dcc1012 Jun 14Document9 pagesRM Dcc1012 Jun 14red_wing86No ratings yet

- Syllabus: Don Bosco Technical Institute - TarlacDocument2 pagesSyllabus: Don Bosco Technical Institute - TarlacEdwin SorianoNo ratings yet

- SKR Internship Report - Docx 14-10-2015Document39 pagesSKR Internship Report - Docx 14-10-2015Karthik N NargundNo ratings yet

- BCD To 7 Segment LED Display Decoder Circuit Diagram and WorkingDocument19 pagesBCD To 7 Segment LED Display Decoder Circuit Diagram and WorkingAashish KumarNo ratings yet

- Catia TutoroalDocument9 pagesCatia TutoroalSantu SanthoshNo ratings yet

- CATIA V5 Lesson - 1Document9 pagesCATIA V5 Lesson - 1Xue Guan SongNo ratings yet

- 2021 Recovery ATP Mediation For EGDDocument31 pages2021 Recovery ATP Mediation For EGDmontananewman526No ratings yet

- 156 - Engineering - Drawing - EE-155 - Lab - Manual Final-2Document24 pages156 - Engineering - Drawing - EE-155 - Lab - Manual Final-2Hamza AkhtarNo ratings yet

- Auto Cad JoshuDocument15 pagesAuto Cad Joshuvaibhav mhaseNo ratings yet

- Irjet V9i7575Document7 pagesIrjet V9i7575shubs2226No ratings yet

- CaD 9211 June 2010Document2 pagesCaD 9211 June 2010Remo RamNo ratings yet

- Aveva AnsysDocument9 pagesAveva AnsysFelipe Rivera TiradoNo ratings yet

- ED WorkBook 1Document30 pagesED WorkBook 1sheikh4503856No ratings yet

- Design of PCB LayoutDocument19 pagesDesign of PCB LayoutcharenchittiNo ratings yet

- S7EE-Project - Phase - IDocument11 pagesS7EE-Project - Phase - IAswinkumar KNNo ratings yet

- Aft End Structure Model ReportDocument15 pagesAft End Structure Model ReportDeepak PooranachandranNo ratings yet

- Divya Solanki PDFDocument15 pagesDivya Solanki PDFDeepak PooranachandranNo ratings yet

- CHAMP - Chip Floor Plan For Hierarchical VLSI Layout DesignDocument11 pagesCHAMP - Chip Floor Plan For Hierarchical VLSI Layout Designxzxuan2005No ratings yet

- PP20132 - Revit - Final Assessment File - PEM 2Document22 pagesPP20132 - Revit - Final Assessment File - PEM 2SandeepNo ratings yet

- Layout Lab ManualDocument26 pagesLayout Lab ManualM Yasir AnjumNo ratings yet

- Mini Project NewDocument9 pagesMini Project NewF1042 HaikalNo ratings yet

- CAD System AlgorithmDocument11 pagesCAD System Algorithmsachin bNo ratings yet

- Fluid MechanicDocument24 pagesFluid MechanicT J Construction LimitedNo ratings yet

- SPU/SDOT Design Drafting GuidelinesDocument6 pagesSPU/SDOT Design Drafting Guidelinesjouie tabilinNo ratings yet

- Cadguide 2Document20 pagesCadguide 2kgsatish1979No ratings yet

- Electronic Engineering Drawing & WorkshopDocument80 pagesElectronic Engineering Drawing & Workshopstephen562001No ratings yet

- B.tech 7th Semester Project PresentationDocument12 pagesB.tech 7th Semester Project PresentationSoumya RanjanNo ratings yet

- Computer Help Presentaion of Sofware and Services OfferedDocument55 pagesComputer Help Presentaion of Sofware and Services OfferedKishor GavaliNo ratings yet

- CmosDocument23 pagesCmoselumalaianithaNo ratings yet

- CG ManualDocument39 pagesCG Manualsanthosh reddyNo ratings yet

- Handout 21179 FAB21179 Pullinger AU2016Document26 pagesHandout 21179 FAB21179 Pullinger AU2016Ryan WoolfsonNo ratings yet

- Cad Standard ManualDocument23 pagesCad Standard ManualNoly TicsayNo ratings yet

- Software Based Lab Manual - 2Document31 pagesSoftware Based Lab Manual - 2Shekhar V kumbarNo ratings yet

- Assignment 7 Subdivision 2020.03.12.sbDocument10 pagesAssignment 7 Subdivision 2020.03.12.sbSaroj UpadhyayNo ratings yet

- Design Calculations Concrete Column SpreadsheetDocument16 pagesDesign Calculations Concrete Column SpreadsheetSanjeeb SinhaNo ratings yet

- ArchiCAD - Step 1 - Creating A Building ModelDocument43 pagesArchiCAD - Step 1 - Creating A Building ModeldpNo ratings yet

- BCD To 7 Segment Display PDFDocument18 pagesBCD To 7 Segment Display PDFRobertoRodríguezNo ratings yet

- Revit Integration With IES VEDocument19 pagesRevit Integration With IES VEAdi CrimuNo ratings yet

- Seven SegmentsDocument12 pagesSeven SegmentsMohammed Abdalla AliNo ratings yet

- Archit. Working DrawingDocument20 pagesArchit. Working DrawingMarvin Messi100% (2)

- Lect1 2 1642214538630Document17 pagesLect1 2 1642214538630Mainak TarafdarNo ratings yet

- Digital Techniques: Diploma in Computer TechnologyDocument17 pagesDigital Techniques: Diploma in Computer TechnologySharaneshwar PunjalNo ratings yet

- 3d Modeling For The Architectural Engineering andDocument7 pages3d Modeling For The Architectural Engineering andicNo ratings yet

- Learn Flat Slab-Flat Slab Analysis Design and Drawing SoftwareDocument128 pagesLearn Flat Slab-Flat Slab Analysis Design and Drawing SoftwareMohammad FawwazNo ratings yet

- CNC Cut Files With Autodesk Product Design Suites, Part 1Document16 pagesCNC Cut Files With Autodesk Product Design Suites, Part 1vikhnuNo ratings yet

- EG Introduction - Sheets, Standards and InstrumentsDocument20 pagesEG Introduction - Sheets, Standards and Instrumentsmani88kctNo ratings yet

- Conveyor Belt ProjectDocument5 pagesConveyor Belt ProjectJacob KimballNo ratings yet

- Architectural Working DrawingsDocument52 pagesArchitectural Working DrawingseddieNo ratings yet

- Floorplan Will No Longer Be Difficult To Do (Digital Back-End Design and Implementation of Floorplan) - IC Pioneer's Blog-CSDN BlogDocument8 pagesFloorplan Will No Longer Be Difficult To Do (Digital Back-End Design and Implementation of Floorplan) - IC Pioneer's Blog-CSDN BlogAgnathavasiNo ratings yet

- Application of Evolutionary Operation To The Minimum Cost Design of Continuos Prestressed Concrete Bridge StructureDocument11 pagesApplication of Evolutionary Operation To The Minimum Cost Design of Continuos Prestressed Concrete Bridge StructureParth TrivediNo ratings yet

- Chapter 11: General Arrangement Drawings December 2020Document27 pagesChapter 11: General Arrangement Drawings December 2020gogo2021No ratings yet

- Manual ProConcreteDocument1,036 pagesManual ProConcreteBavedi San75% (4)

- Antenna Matching Within An EnclosureDocument5 pagesAntenna Matching Within An EnclosureNitin PatelNo ratings yet

- EDA Open Source Tools WikiDocument13 pagesEDA Open Source Tools WikiNitin PatelNo ratings yet

- SerDes 45nmDocument47 pagesSerDes 45nmNitin PatelNo ratings yet

- SERDESDocument1 pageSERDESNitin PatelNo ratings yet

- Migration in Solid State MaterialsDocument15 pagesMigration in Solid State MaterialsNitin PatelNo ratings yet

- Amsg Ic Physical Design Syllabus 3-13-2015Document2 pagesAmsg Ic Physical Design Syllabus 3-13-2015Nitin PatelNo ratings yet

- Common Analog IC Layout Tips-And-TricksDocument4 pagesCommon Analog IC Layout Tips-And-TricksNitin PatelNo ratings yet

- 510B Backhoe Loader: Engine PerformanceDocument5 pages510B Backhoe Loader: Engine PerformancebalajimetturNo ratings yet

- Atomic and Molecular Physics JEST 2012-2017 PDFDocument5 pagesAtomic and Molecular Physics JEST 2012-2017 PDFShrutiNo ratings yet

- Pc210lc-11 Sen06695-01 Circuit DiagramsDocument26 pagesPc210lc-11 Sen06695-01 Circuit DiagramsdatphuongNo ratings yet

- Presentation On SPS: (Special Protection Scheme)Document9 pagesPresentation On SPS: (Special Protection Scheme)Abhishek SinhaNo ratings yet

- Mobile Tower and Mobile Phone Radiation Hazards - Prof Girish KumarDocument52 pagesMobile Tower and Mobile Phone Radiation Hazards - Prof Girish KumarNeha KumarNo ratings yet

- 7SR242 - Duobias Technical Manual Chapter 02 Settings, Configuration and InstrumentsDocument20 pages7SR242 - Duobias Technical Manual Chapter 02 Settings, Configuration and InstrumentsssNo ratings yet

- Ae53 Ac53 At53Document4 pagesAe53 Ac53 At53M Taher BamyaniNo ratings yet

- Filter Manual: Vacon Cx/Cxl/Cxs Frequency ConvertersDocument13 pagesFilter Manual: Vacon Cx/Cxl/Cxs Frequency ConvertersnabeelNo ratings yet

- Minimizing Excessive PDFDocument130 pagesMinimizing Excessive PDFMoriyasu NguyenNo ratings yet

- " Power Details ": Project NameDocument14 pages" Power Details ": Project NameEdmar BataqueNo ratings yet

- Aventics Coil Series CO1 Form BDocument3 pagesAventics Coil Series CO1 Form BCarlos Andrés CuelloNo ratings yet

- Vutek UltraVU 5300 ManualDocument250 pagesVutek UltraVU 5300 ManualGeorge Scurtu100% (2)

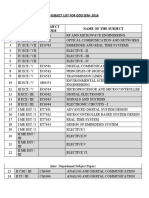

- Subject List For Odd Sem-2016 Class/ SEM Subject Code Name of The SubjectDocument3 pagesSubject List For Odd Sem-2016 Class/ SEM Subject Code Name of The SubjectRamesh MallaiNo ratings yet

- CHAPTER 4 Source transformation-SVDocument29 pagesCHAPTER 4 Source transformation-SVnurul najwaNo ratings yet

- Answer (454.57W and 250W) : Power Electronics and Electrical Drives Work Sheet Department of Electromechanical EngDocument2 pagesAnswer (454.57W and 250W) : Power Electronics and Electrical Drives Work Sheet Department of Electromechanical EngDilamo FelekeNo ratings yet

- Network HandoutDocument151 pagesNetwork HandoutLeti TadesseNo ratings yet

- Yamaha Receiver Rxv-595 SchematicDocument7 pagesYamaha Receiver Rxv-595 SchematicMauricio Bumba100% (2)

- ACS880-01 Drives: Hardware ManualDocument302 pagesACS880-01 Drives: Hardware ManualMarcos QuezadaNo ratings yet

- TC1047/TC1047A: Precision Temperature-to-Voltage ConverterDocument12 pagesTC1047/TC1047A: Precision Temperature-to-Voltage ConverterjuanNo ratings yet

- 8049Document239 pages8049adnantanNo ratings yet

- Homework 8 TCDocument12 pagesHomework 8 TCSebastián TorresNo ratings yet

- EE264 Introduction To Digital Design Project-2Document7 pagesEE264 Introduction To Digital Design Project-2TimsinaKrishnaNo ratings yet

- Example 2:: To Get Square Wave Mode 3 Is Selected Count Should Be 1 MHZ 1 KHZ 1000Document16 pagesExample 2:: To Get Square Wave Mode 3 Is Selected Count Should Be 1 MHZ 1 KHZ 1000Athul Raj100% (1)

- HTB 313K (2V) Series Cyclic Performance V1.3, 21st Oct 2015Document5 pagesHTB 313K (2V) Series Cyclic Performance V1.3, 21st Oct 2015M. ShaatNo ratings yet

- Guia de Laboratorio XenMobileDocument181 pagesGuia de Laboratorio XenMobileAlienígena MaryNo ratings yet

- SimplorerDocument115 pagesSimplorerSreerag Kunnathu SugathanNo ratings yet

- EE370 Chapter1 SlidesDocument18 pagesEE370 Chapter1 SlidesAbhinavJainNo ratings yet

- A Comparative Study of Audio Steganography Techniques PDFDocument6 pagesA Comparative Study of Audio Steganography Techniques PDFUtsav GuptaNo ratings yet

CAD For IC Design: (MEL ZG641)

CAD For IC Design: (MEL ZG641)

Uploaded by

Nitin PatelOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CAD For IC Design: (MEL ZG641)

CAD For IC Design: (MEL ZG641)

Uploaded by

Nitin PatelCopyright:

Available Formats

CAD for IC Design

(MEL ZG641)

Lecture 7 8: Floorplanning

August 14, 2021

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 1 / 15

Outline

1 Introduction

2 Problem definition

3 Cost functions

4 Terminology

5 Slicing Floorplan

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 2 / 15

Introduction

Tasks to be followed sequentially to obtain layout from specification:

1 Layout hierarchy

2 Computing overall silicon area

3 To determine the aspect ratios of each module

4 Pin and IO pad locations

5 Placement

6 Routing (clock and power/ground signal)

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 3 / 15

Introduction

VLSI circuit as a set of rectangular blocks with interconnection

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 4 / 15

Introduction

VLSI circuit as a set of rectangular blocks with interconnection

Placing blocks on a 2-d surface such that no two blocks overlap

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 4 / 15

Introduction

VLSI circuit as a set of rectangular blocks with interconnection

Placing blocks on a 2-d surface such that no two blocks overlap

Certain objectives are to be optimized

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 4 / 15

Introduction

More flexible than placement

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 5 / 15

Introduction

More flexible than placement

Block orientation, shapes and sizes may be chosen for optimization or

to fulfill user specified constraints

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 5 / 15

Problem Definition

Input:

– A set of n rectangular modules S = {1, 2, ..., n}

– S1 and S2 are partition of S

– Interconnection matrix of size n × n

– A list of N triplets (Ai , ri , si ) A: area, r and s are lower and upper bound

constraints of the shape

– Lower (p) and upper bound (q) constraints for enveloping rectangle

containing n blocks

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 6 / 15

Floorplanning model

Output:

– Area of each module ≤ Ai

– Aspect ratio (H/W) should be within r and s

– Each rectangle should be large enough to accommodate the given

module

– No space left (may be rotated)

– The enveloping rectangle aspect ratio should be within p an q

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 7 / 15

Example

Figure: Modules to be placed

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 8 / 15

Cost functions

For a given problem the number of possible solution is very large

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 9 / 15

Cost functions

For a given problem the number of possible solution is very large

For an unbounded total area it is infinite

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 9 / 15

Cost functions

For a given problem the number of possible solution is very large

For an unbounded total area it is infinite

Objective function allows to select the best possible solution

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 9 / 15

Cost functions

1 Minimum area

2 Minimum wire-length

3 Maximum routability

4 Minimum delay

5 Any combination of above

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 10 / 15

Performance

Speed is treated as the deciding factor

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 11 / 15

Performance

Speed is treated as the deciding factor

Decided by identifying the critical path

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 11 / 15

Performance

Speed is treated as the deciding factor

Decided by identifying the critical path

Implementation where the connected modules are placed nearby are

considered better for minimizing the interconnect delay

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 11 / 15

Performance

To find a feasible floorplan with minimum overall area

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 12 / 15

Performance

To find a feasible floorplan with minimum overall area

Rectangles are kept in sorted queue (W /H)

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 12 / 15

Performance

To find a feasible floorplan with minimum overall area

Rectangles are kept in sorted queue (W /H)

Queue is dynamic

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 12 / 15

Performance

To find a feasible floorplan with minimum overall area

Rectangles are kept in sorted queue (W /H)

Queue is dynamic

Cost function is a weighted sum of area and the overall length as:

cost = α × A + β × L

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 12 / 15

Terminology

Rectangular dissection:

– Subdivision of a rectangle by a finite number of horizontal and

vertical line segments

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 13 / 15

Terminology

Rectangular dissection:

– Subdivision of a rectangle by a finite number of horizontal and

vertical line segments

Slicing structure:

– Rectangular dissection that can be obtained by repetitively

subdividing rectangles horizontally and vertically into smaller

rectangles

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 13 / 15

Slicing Floorplan

Slicing tree (slicing floorplan tree):

– Similar to binary tree with leaves (rectangle) and nodes

(vertical/horizontal cut lines)

– More than one slicing tree is possible for a given structure

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 14 / 15

Slicing Floorplan

Slicing tree (slicing floorplan tree):

– Similar to binary tree with leaves (rectangle) and nodes

(vertical/horizontal cut lines)

– More than one slicing tree is possible for a given structure

Slicing floorplans:

– Floorplan that corresponds to a slicing structure is called slicing

floor plan

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 14 / 15

Slicing Floorplan

Slicing tree (slicing floorplan tree):

– Similar to binary tree with leaves (rectangle) and nodes

(vertical/horizontal cut lines)

– More than one slicing tree is possible for a given structure

Slicing floorplans:

– Floorplan that corresponds to a slicing structure is called slicing

floor plan

Non-slicing floorplans:

– Floorplan that corresponds to non-slicing structure is called

non-slicing floorplan (wheel)

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 14 / 15

Example

Figure: Obtain slicing tree for the above floor plan

Lecture 7 8: Floorplanning CAD for IC Design August 14, 2021 15 / 15

You might also like

- Samsung rv511 SchematicDocument52 pagesSamsung rv511 SchematicGanesh Prasad50% (2)

- Solution Manual For Engineering Design Graphics Sketching Modeling and Visualization Leake 2nd EditionDocument3 pagesSolution Manual For Engineering Design Graphics Sketching Modeling and Visualization Leake 2nd EditionCory Smith100% (37)

- CSC Orion TutorialDocument190 pagesCSC Orion TutorialBenedict OgbaghaNo ratings yet

- 2004 Sportsman 700 - Parts ManualDocument61 pages2004 Sportsman 700 - Parts ManualGregoryKaufmann100% (1)

- Article Parametric Design of Steel StructuresDocument11 pagesArticle Parametric Design of Steel StructuresRamkishore ChelvinMurugeshNo ratings yet

- Engineering Drawing EE-155 Lab Manual-2Document27 pagesEngineering Drawing EE-155 Lab Manual-2abdulsamadNo ratings yet

- Module PBM9 (BCD 7 Segment Introduction)Document14 pagesModule PBM9 (BCD 7 Segment Introduction)Fajar FatahillahNo ratings yet

- Module 5Document18 pagesModule 5Cherrie Mae DiazNo ratings yet

- Ge6261 Computer Aided Drafting and Modeling Lab (Mech)Document43 pagesGe6261 Computer Aided Drafting and Modeling Lab (Mech)T.A. Sundara VadivelNo ratings yet

- RM Dcc1012 Jun 14Document9 pagesRM Dcc1012 Jun 14red_wing86No ratings yet

- Syllabus: Don Bosco Technical Institute - TarlacDocument2 pagesSyllabus: Don Bosco Technical Institute - TarlacEdwin SorianoNo ratings yet

- SKR Internship Report - Docx 14-10-2015Document39 pagesSKR Internship Report - Docx 14-10-2015Karthik N NargundNo ratings yet

- BCD To 7 Segment LED Display Decoder Circuit Diagram and WorkingDocument19 pagesBCD To 7 Segment LED Display Decoder Circuit Diagram and WorkingAashish KumarNo ratings yet

- Catia TutoroalDocument9 pagesCatia TutoroalSantu SanthoshNo ratings yet

- CATIA V5 Lesson - 1Document9 pagesCATIA V5 Lesson - 1Xue Guan SongNo ratings yet

- 2021 Recovery ATP Mediation For EGDDocument31 pages2021 Recovery ATP Mediation For EGDmontananewman526No ratings yet

- 156 - Engineering - Drawing - EE-155 - Lab - Manual Final-2Document24 pages156 - Engineering - Drawing - EE-155 - Lab - Manual Final-2Hamza AkhtarNo ratings yet

- Auto Cad JoshuDocument15 pagesAuto Cad Joshuvaibhav mhaseNo ratings yet

- Irjet V9i7575Document7 pagesIrjet V9i7575shubs2226No ratings yet

- CaD 9211 June 2010Document2 pagesCaD 9211 June 2010Remo RamNo ratings yet

- Aveva AnsysDocument9 pagesAveva AnsysFelipe Rivera TiradoNo ratings yet

- ED WorkBook 1Document30 pagesED WorkBook 1sheikh4503856No ratings yet

- Design of PCB LayoutDocument19 pagesDesign of PCB LayoutcharenchittiNo ratings yet

- S7EE-Project - Phase - IDocument11 pagesS7EE-Project - Phase - IAswinkumar KNNo ratings yet

- Aft End Structure Model ReportDocument15 pagesAft End Structure Model ReportDeepak PooranachandranNo ratings yet

- Divya Solanki PDFDocument15 pagesDivya Solanki PDFDeepak PooranachandranNo ratings yet

- CHAMP - Chip Floor Plan For Hierarchical VLSI Layout DesignDocument11 pagesCHAMP - Chip Floor Plan For Hierarchical VLSI Layout Designxzxuan2005No ratings yet

- PP20132 - Revit - Final Assessment File - PEM 2Document22 pagesPP20132 - Revit - Final Assessment File - PEM 2SandeepNo ratings yet

- Layout Lab ManualDocument26 pagesLayout Lab ManualM Yasir AnjumNo ratings yet

- Mini Project NewDocument9 pagesMini Project NewF1042 HaikalNo ratings yet

- CAD System AlgorithmDocument11 pagesCAD System Algorithmsachin bNo ratings yet

- Fluid MechanicDocument24 pagesFluid MechanicT J Construction LimitedNo ratings yet

- SPU/SDOT Design Drafting GuidelinesDocument6 pagesSPU/SDOT Design Drafting Guidelinesjouie tabilinNo ratings yet

- Cadguide 2Document20 pagesCadguide 2kgsatish1979No ratings yet

- Electronic Engineering Drawing & WorkshopDocument80 pagesElectronic Engineering Drawing & Workshopstephen562001No ratings yet

- B.tech 7th Semester Project PresentationDocument12 pagesB.tech 7th Semester Project PresentationSoumya RanjanNo ratings yet

- Computer Help Presentaion of Sofware and Services OfferedDocument55 pagesComputer Help Presentaion of Sofware and Services OfferedKishor GavaliNo ratings yet

- CmosDocument23 pagesCmoselumalaianithaNo ratings yet

- CG ManualDocument39 pagesCG Manualsanthosh reddyNo ratings yet

- Handout 21179 FAB21179 Pullinger AU2016Document26 pagesHandout 21179 FAB21179 Pullinger AU2016Ryan WoolfsonNo ratings yet

- Cad Standard ManualDocument23 pagesCad Standard ManualNoly TicsayNo ratings yet

- Software Based Lab Manual - 2Document31 pagesSoftware Based Lab Manual - 2Shekhar V kumbarNo ratings yet

- Assignment 7 Subdivision 2020.03.12.sbDocument10 pagesAssignment 7 Subdivision 2020.03.12.sbSaroj UpadhyayNo ratings yet

- Design Calculations Concrete Column SpreadsheetDocument16 pagesDesign Calculations Concrete Column SpreadsheetSanjeeb SinhaNo ratings yet

- ArchiCAD - Step 1 - Creating A Building ModelDocument43 pagesArchiCAD - Step 1 - Creating A Building ModeldpNo ratings yet

- BCD To 7 Segment Display PDFDocument18 pagesBCD To 7 Segment Display PDFRobertoRodríguezNo ratings yet

- Revit Integration With IES VEDocument19 pagesRevit Integration With IES VEAdi CrimuNo ratings yet

- Seven SegmentsDocument12 pagesSeven SegmentsMohammed Abdalla AliNo ratings yet

- Archit. Working DrawingDocument20 pagesArchit. Working DrawingMarvin Messi100% (2)

- Lect1 2 1642214538630Document17 pagesLect1 2 1642214538630Mainak TarafdarNo ratings yet

- Digital Techniques: Diploma in Computer TechnologyDocument17 pagesDigital Techniques: Diploma in Computer TechnologySharaneshwar PunjalNo ratings yet

- 3d Modeling For The Architectural Engineering andDocument7 pages3d Modeling For The Architectural Engineering andicNo ratings yet

- Learn Flat Slab-Flat Slab Analysis Design and Drawing SoftwareDocument128 pagesLearn Flat Slab-Flat Slab Analysis Design and Drawing SoftwareMohammad FawwazNo ratings yet

- CNC Cut Files With Autodesk Product Design Suites, Part 1Document16 pagesCNC Cut Files With Autodesk Product Design Suites, Part 1vikhnuNo ratings yet

- EG Introduction - Sheets, Standards and InstrumentsDocument20 pagesEG Introduction - Sheets, Standards and Instrumentsmani88kctNo ratings yet

- Conveyor Belt ProjectDocument5 pagesConveyor Belt ProjectJacob KimballNo ratings yet

- Architectural Working DrawingsDocument52 pagesArchitectural Working DrawingseddieNo ratings yet

- Floorplan Will No Longer Be Difficult To Do (Digital Back-End Design and Implementation of Floorplan) - IC Pioneer's Blog-CSDN BlogDocument8 pagesFloorplan Will No Longer Be Difficult To Do (Digital Back-End Design and Implementation of Floorplan) - IC Pioneer's Blog-CSDN BlogAgnathavasiNo ratings yet

- Application of Evolutionary Operation To The Minimum Cost Design of Continuos Prestressed Concrete Bridge StructureDocument11 pagesApplication of Evolutionary Operation To The Minimum Cost Design of Continuos Prestressed Concrete Bridge StructureParth TrivediNo ratings yet

- Chapter 11: General Arrangement Drawings December 2020Document27 pagesChapter 11: General Arrangement Drawings December 2020gogo2021No ratings yet

- Manual ProConcreteDocument1,036 pagesManual ProConcreteBavedi San75% (4)

- Antenna Matching Within An EnclosureDocument5 pagesAntenna Matching Within An EnclosureNitin PatelNo ratings yet

- EDA Open Source Tools WikiDocument13 pagesEDA Open Source Tools WikiNitin PatelNo ratings yet

- SerDes 45nmDocument47 pagesSerDes 45nmNitin PatelNo ratings yet

- SERDESDocument1 pageSERDESNitin PatelNo ratings yet

- Migration in Solid State MaterialsDocument15 pagesMigration in Solid State MaterialsNitin PatelNo ratings yet

- Amsg Ic Physical Design Syllabus 3-13-2015Document2 pagesAmsg Ic Physical Design Syllabus 3-13-2015Nitin PatelNo ratings yet

- Common Analog IC Layout Tips-And-TricksDocument4 pagesCommon Analog IC Layout Tips-And-TricksNitin PatelNo ratings yet

- 510B Backhoe Loader: Engine PerformanceDocument5 pages510B Backhoe Loader: Engine PerformancebalajimetturNo ratings yet

- Atomic and Molecular Physics JEST 2012-2017 PDFDocument5 pagesAtomic and Molecular Physics JEST 2012-2017 PDFShrutiNo ratings yet

- Pc210lc-11 Sen06695-01 Circuit DiagramsDocument26 pagesPc210lc-11 Sen06695-01 Circuit DiagramsdatphuongNo ratings yet

- Presentation On SPS: (Special Protection Scheme)Document9 pagesPresentation On SPS: (Special Protection Scheme)Abhishek SinhaNo ratings yet

- Mobile Tower and Mobile Phone Radiation Hazards - Prof Girish KumarDocument52 pagesMobile Tower and Mobile Phone Radiation Hazards - Prof Girish KumarNeha KumarNo ratings yet

- 7SR242 - Duobias Technical Manual Chapter 02 Settings, Configuration and InstrumentsDocument20 pages7SR242 - Duobias Technical Manual Chapter 02 Settings, Configuration and InstrumentsssNo ratings yet

- Ae53 Ac53 At53Document4 pagesAe53 Ac53 At53M Taher BamyaniNo ratings yet

- Filter Manual: Vacon Cx/Cxl/Cxs Frequency ConvertersDocument13 pagesFilter Manual: Vacon Cx/Cxl/Cxs Frequency ConvertersnabeelNo ratings yet

- Minimizing Excessive PDFDocument130 pagesMinimizing Excessive PDFMoriyasu NguyenNo ratings yet

- " Power Details ": Project NameDocument14 pages" Power Details ": Project NameEdmar BataqueNo ratings yet

- Aventics Coil Series CO1 Form BDocument3 pagesAventics Coil Series CO1 Form BCarlos Andrés CuelloNo ratings yet

- Vutek UltraVU 5300 ManualDocument250 pagesVutek UltraVU 5300 ManualGeorge Scurtu100% (2)

- Subject List For Odd Sem-2016 Class/ SEM Subject Code Name of The SubjectDocument3 pagesSubject List For Odd Sem-2016 Class/ SEM Subject Code Name of The SubjectRamesh MallaiNo ratings yet

- CHAPTER 4 Source transformation-SVDocument29 pagesCHAPTER 4 Source transformation-SVnurul najwaNo ratings yet

- Answer (454.57W and 250W) : Power Electronics and Electrical Drives Work Sheet Department of Electromechanical EngDocument2 pagesAnswer (454.57W and 250W) : Power Electronics and Electrical Drives Work Sheet Department of Electromechanical EngDilamo FelekeNo ratings yet

- Network HandoutDocument151 pagesNetwork HandoutLeti TadesseNo ratings yet

- Yamaha Receiver Rxv-595 SchematicDocument7 pagesYamaha Receiver Rxv-595 SchematicMauricio Bumba100% (2)

- ACS880-01 Drives: Hardware ManualDocument302 pagesACS880-01 Drives: Hardware ManualMarcos QuezadaNo ratings yet

- TC1047/TC1047A: Precision Temperature-to-Voltage ConverterDocument12 pagesTC1047/TC1047A: Precision Temperature-to-Voltage ConverterjuanNo ratings yet

- 8049Document239 pages8049adnantanNo ratings yet

- Homework 8 TCDocument12 pagesHomework 8 TCSebastián TorresNo ratings yet

- EE264 Introduction To Digital Design Project-2Document7 pagesEE264 Introduction To Digital Design Project-2TimsinaKrishnaNo ratings yet

- Example 2:: To Get Square Wave Mode 3 Is Selected Count Should Be 1 MHZ 1 KHZ 1000Document16 pagesExample 2:: To Get Square Wave Mode 3 Is Selected Count Should Be 1 MHZ 1 KHZ 1000Athul Raj100% (1)

- HTB 313K (2V) Series Cyclic Performance V1.3, 21st Oct 2015Document5 pagesHTB 313K (2V) Series Cyclic Performance V1.3, 21st Oct 2015M. ShaatNo ratings yet

- Guia de Laboratorio XenMobileDocument181 pagesGuia de Laboratorio XenMobileAlienígena MaryNo ratings yet

- SimplorerDocument115 pagesSimplorerSreerag Kunnathu SugathanNo ratings yet

- EE370 Chapter1 SlidesDocument18 pagesEE370 Chapter1 SlidesAbhinavJainNo ratings yet

- A Comparative Study of Audio Steganography Techniques PDFDocument6 pagesA Comparative Study of Audio Steganography Techniques PDFUtsav GuptaNo ratings yet