Professional Documents

Culture Documents

D D D D D D: TMS57535A 480Ch 64G/S Color TFT Source Driver

D D D D D D: TMS57535A 480Ch 64G/S Color TFT Source Driver

Uploaded by

zigmund zigmundCopyright:

Available Formats

You might also like

- Placa 1156 - Pegatron Ipmip-Dp (Pos-Piq57bq) Rev 1.01Document68 pagesPlaca 1156 - Pegatron Ipmip-Dp (Pos-Piq57bq) Rev 1.01Francisco FreireNo ratings yet

- Esquema Schematic IPISB-VR Rev 1.01Document76 pagesEsquema Schematic IPISB-VR Rev 1.01Roberto MouraNo ratings yet

- Schematic Diagram t240Document6 pagesSchematic Diagram t240dany weinfeldNo ratings yet

- Asus X505BP Rev2.0Document97 pagesAsus X505BP Rev2.0santiago rodriguezNo ratings yet

- Desktop Dell HNJFVDocument51 pagesDesktop Dell HNJFVjoao batistaNo ratings yet

- HP Confidential MSI MS-7557 Ver:0A 2008-0722: WWW - Vinafix.vnDocument52 pagesHP Confidential MSI MS-7557 Ver:0A 2008-0722: WWW - Vinafix.vnMinh Tran100% (2)

- Wistron K6 IBM R51eDocument71 pagesWistron K6 IBM R51eMario Rodriguez JuradoNo ratings yet

- (DELL) 一款七寸平板电脑原理图JWT - V1A - 0721 - 16P2 PDFDocument30 pages(DELL) 一款七寸平板电脑原理图JWT - V1A - 0721 - 16P2 PDFsamuelNo ratings yet

- Pegatron Ipmip-GsDocument68 pagesPegatron Ipmip-GsBruno MartinsNo ratings yet

- TLC 549Document18 pagesTLC 549lanjiao333No ratings yet

- PEGATRON IPISB-SB Rev1.00 PDFDocument76 pagesPEGATRON IPISB-SB Rev1.00 PDFClaudeciNo ratings yet

- Quanta FH2A Intel Calpella Arrandale REV 1ADocument46 pagesQuanta FH2A Intel Calpella Arrandale REV 1AВиктор СёминNo ratings yet

- Datasheet 80C85 (Oki)Document29 pagesDatasheet 80C85 (Oki)José AdelinoNo ratings yet

- MC14442PDocument10 pagesMC14442PRuben AparicioNo ratings yet

- TLC 7225Document21 pagesTLC 7225tajpan77No ratings yet

- TDA8753A PhilipsSemiconductorsDocument20 pagesTDA8753A PhilipsSemiconductorsDaanNo ratings yet

- TLC 1514Document40 pagesTLC 1514Hoii ClarkNo ratings yet

- Fujitsu LifeBook LH530 Quanta FH1 Intel UMA Rev1A SchematicDocument37 pagesFujitsu LifeBook LH530 Quanta FH1 Intel UMA Rev1A SchematicAsep IndraNo ratings yet

- TLC5620Document14 pagesTLC5620Dirson Volmir WilligNo ratings yet

- ths5661 PDFDocument29 pagesths5661 PDFIqbal AchmadiNo ratings yet

- Dell - XPS One 2710 - IPIMB-PVDocument5 pagesDell - XPS One 2710 - IPIMB-PVisai ramos sotoNo ratings yet

- n91 MV d3h 0322Document58 pagesn91 MV d3h 0322Moh HamNo ratings yet

- Biostar G41D3 (Ver 7.0) PDFDocument32 pagesBiostar G41D3 (Ver 7.0) PDFEl TécnicoNo ratings yet

- 06060214-GJ-S8640002 - Tembagapura Emergency Power - Cable Schedule Buat PrintDocument9 pages06060214-GJ-S8640002 - Tembagapura Emergency Power - Cable Schedule Buat PrintJan Richardo GultomNo ratings yet

- Sharp MS-7082-3.0RohsDocument31 pagesSharp MS-7082-3.0RohsAladino SanchezNo ratings yet

- ¡ Semiconductor: MSM80C85AHRS/GS/JSDocument22 pages¡ Semiconductor: MSM80C85AHRS/GS/JScamaferNo ratings yet

- Fujitsu A 530Document34 pagesFujitsu A 530Makhtar SeyeNo ratings yet

- Safa Micro hw-1Document30 pagesSafa Micro hw-1suhailhajajjiNo ratings yet

- 74LS164Document4 pages74LS164jaja558No ratings yet

- Block Diagram 1381743Document1 pageBlock Diagram 1381743Andrzej GomulaNo ratings yet

- Mini Pcie Card Reference Design - V Rev 10 PDFDocument2 pagesMini Pcie Card Reference Design - V Rev 10 PDFanhxcoNo ratings yet

- Da0zhdmb8d0 LODocument40 pagesDa0zhdmb8d0 LOJacob TevenalNo ratings yet

- Pegatron Iaxbt-Bl Rev Rev. 1.01 Acer Aspire Zc-606Document67 pagesPegatron Iaxbt-Bl Rev Rev. 1.01 Acer Aspire Zc-606Ban NeoNo ratings yet

- Dell XPS One 2720 Pegatron IPPLP-PL Rev 1.01Document82 pagesDell XPS One 2720 Pegatron IPPLP-PL Rev 1.01Дамир АшеновNo ratings yet

- Xiufix WistronDocument66 pagesXiufix WistronCedomir Gajic100% (1)

- Fujitsu Ah530 SchimaticDocument38 pagesFujitsu Ah530 SchimaticabdullahNo ratings yet

- D D D D D D D D D D D D: TLV5618A 2.7-V TO 5.5-V LOW-POWER DUAL 12-BIT Digital-To-Analog Converter With Power DownDocument23 pagesD D D D D D D D D D D D: TLV5618A 2.7-V TO 5.5-V LOW-POWER DUAL 12-BIT Digital-To-Analog Converter With Power DownJulio Rafael GamboaNo ratings yet

- Sitronix: Dot Matrix LCD Controller/DriverDocument35 pagesSitronix: Dot Matrix LCD Controller/DriverSair Puello RuizNo ratings yet

- Asus Prime Z390-A Rev1.02 (60mb0yt0-Mb0a01)Document121 pagesAsus Prime Z390-A Rev1.02 (60mb0yt0-Mb0a01)mm aaNo ratings yet

- MS-6728 AtxDocument33 pagesMS-6728 AtxRisoSilvaNo ratings yet

- MS-6728 AtxDocument33 pagesMS-6728 AtxRisoSilvaNo ratings yet

- TLV0831C etcTIDocument21 pagesTLV0831C etcTIEsen KayaNo ratings yet

- D D D D D D D D D D: DescriptionDocument12 pagesD D D D D D D D D D: DescriptionRogério MorenoNo ratings yet

- Quanta FH9 DA0FH9MB6C0 - R2aDocument48 pagesQuanta FH9 DA0FH9MB6C0 - R2aYetawa GuaviareNo ratings yet

- Esquema Placa Mae BiostarDocument39 pagesEsquema Placa Mae BiostarERICO STRAMANDINOLINo ratings yet

- 8-CHANNEL, 12-/10-/8-BIT, 2.7-V TO 5.5-V LOW POWER Digital-To-Analog Converter With Power DownDocument26 pages8-CHANNEL, 12-/10-/8-BIT, 2.7-V TO 5.5-V LOW POWER Digital-To-Analog Converter With Power Downjasonkee111No ratings yet

- Tca9555 Low-Voltage 16-Bit I C and Smbus I/O Expander With Interrupt Output and Configuration RegistersDocument46 pagesTca9555 Low-Voltage 16-Bit I C and Smbus I/O Expander With Interrupt Output and Configuration RegistersLuiz LuizNo ratings yet

- CDocument35 pagesCJagopati Jr.No ratings yet

- d8dc8 MS-7348Document29 pagesd8dc8 MS-7348rolan444No ratings yet

- Ak4351vt AkmDocument14 pagesAk4351vt Akmpuh1967No ratings yet

- MS-6728 AtxDocument33 pagesMS-6728 AtxRisoSilvaNo ratings yet

- ST7066 EtcDocument29 pagesST7066 Etcjose aponteNo ratings yet

- AK4346Document31 pagesAK4346naeem_aaNo ratings yet

- 85C471 OVERVIEW: 85C471 Green PC ISA-VESA Single ChipDocument79 pages85C471 OVERVIEW: 85C471 Green PC ISA-VESA Single ChipevasiveNo ratings yet

- 14 Router Connection DetailsDocument22 pages14 Router Connection DetailsErik VahlandNo ratings yet

- ASUS IPPSB-SFA DELL Inspiron One 2320Document79 pagesASUS IPPSB-SFA DELL Inspiron One 2320Mustafa FanuswalaNo ratings yet

- Asrock G41M-VS3 - 1.01 PDFDocument35 pagesAsrock G41M-VS3 - 1.01 PDFthiago date100% (2)

- Генерация SMI# - SCI - 004 - ID - 631119 - Встроенное описание концентратора контроллеров платформы семейства наборов микросхем Intel® серии 500, том 1Document38 pagesГенерация SMI# - SCI - 004 - ID - 631119 - Встроенное описание концентратора контроллеров платформы семейства наборов микросхем Intel® серии 500, том 1zigmund zigmundNo ratings yet

- NS-A031 ODD To VGA Board Schematic Compal)Document17 pagesNS-A031 ODD To VGA Board Schematic Compal)zigmund zigmundNo ratings yet

- NVIDIA P407-A00 NVIDIA G84M MXM SchematicDocument18 pagesNVIDIA P407-A00 NVIDIA G84M MXM Schematiczigmund zigmundNo ratings yet

- Ultrahigh-Speed Switching Applications: Package Dimensions FeaturesDocument4 pagesUltrahigh-Speed Switching Applications: Package Dimensions Featureszigmund zigmundNo ratings yet

- Dmn66D0Ldw: Dual N-Channel Enhancement Mode MosfetDocument5 pagesDmn66D0Ldw: Dual N-Channel Enhancement Mode Mosfetzigmund zigmundNo ratings yet

- Intel Procecor RaznDocument20 pagesIntel Procecor Raznzigmund zigmundNo ratings yet

- LM358 Low Power Dual Op-Amp - Datasheet: TrendingDocument10 pagesLM358 Low Power Dual Op-Amp - Datasheet: Trendingzigmund zigmundNo ratings yet

- Internal Photos PDF 2208521Document4 pagesInternal Photos PDF 2208521zigmund zigmundNo ratings yet

- Dmn66D0Ldw Product Summary Features and Benefits: Dual N-Channel Enhancement Mode MosfetDocument6 pagesDmn66D0Ldw Product Summary Features and Benefits: Dual N-Channel Enhancement Mode Mosfetzigmund zigmundNo ratings yet

- Datasheet DTC115EDocument13 pagesDatasheet DTC115Ezigmund zigmundNo ratings yet

- BQ 26501Document31 pagesBQ 26501zigmund zigmundNo ratings yet

- Description: N-Channel Enhancement Mode Field-Effect TransistorDocument13 pagesDescription: N-Channel Enhancement Mode Field-Effect Transistorzigmund zigmundNo ratings yet

- Cec - in Stock - CrystalsDocument3 pagesCec - in Stock - Crystalszigmund zigmundNo ratings yet

- SN 74 LVC 1 G 04Document44 pagesSN 74 LVC 1 G 04zigmund zigmundNo ratings yet

- Dtc115eefra Dtc115ekafra Dtc115emfha Dtc115euafraDocument10 pagesDtc115eefra Dtc115ekafra Dtc115emfha Dtc115euafrazigmund zigmundNo ratings yet

- JMB38X JMicronDocument3 pagesJMB38X JMicronzigmund zigmundNo ratings yet

- Si 2399 DsDocument11 pagesSi 2399 Dszigmund zigmundNo ratings yet

- Two-Level Temperature Switch Circuit With LM358Document10 pagesTwo-Level Temperature Switch Circuit With LM358zigmund zigmundNo ratings yet

- Datasheet NCP81109Document28 pagesDatasheet NCP81109zigmund zigmundNo ratings yet

- SMB30 DatasheetDocument4 pagesSMB30 Datasheetzigmund zigmundNo ratings yet

- Compal La-8691p r0.3Document66 pagesCompal La-8691p r0.3zigmund zigmundNo ratings yet

- Compal Confidential: G400S/G500S Hematics DocumentDocument113 pagesCompal Confidential: G400S/G500S Hematics Documentzigmund zigmundNo ratings yet

- datasheet ABS2~ABS10-мост-выпрямительDocument3 pagesdatasheet ABS2~ABS10-мост-выпрямительzigmund zigmundNo ratings yet

- SN74AVC4 DatasheetDocument19 pagesSN74AVC4 Datasheetzigmund zigmundNo ratings yet

- NX7002AKS NexperiaDocument15 pagesNX7002AKS Nexperiazigmund zigmundNo ratings yet

- Compal La-8691p r0.2Document66 pagesCompal La-8691p r0.2zigmund zigmundNo ratings yet

- Proposal Lab 5Document4 pagesProposal Lab 5darkzainiNo ratings yet

- Apollo Valves: 94A / 95A SeriesDocument1 pageApollo Valves: 94A / 95A Seriesmaruthappan sundaramNo ratings yet

- SEAS RSRC 57bfe799620e0Document4 pagesSEAS RSRC 57bfe799620e0WunNaNo ratings yet

- Harris Ts100 User ManualDocument24 pagesHarris Ts100 User ManualMiguel Alfonso Ruiz MendezNo ratings yet

- 5S (Methodology) : 5S Is The Name of A Workplace Organization Methodology That Uses A List of FiveDocument3 pages5S (Methodology) : 5S Is The Name of A Workplace Organization Methodology That Uses A List of FiveRoberto DiyNo ratings yet

- TM-Editor 25.04.2016 Seite 1 050-Meteorology - LTMDocument308 pagesTM-Editor 25.04.2016 Seite 1 050-Meteorology - LTMIbrahim Med100% (1)

- PUD Ingles 6 y 7Document66 pagesPUD Ingles 6 y 7Hilda Elizabeth VeraNo ratings yet

- SeminarDocument29 pagesSeminarAkash shindeNo ratings yet

- Activity Sheets: Quarter 3 - MELC 2Document9 pagesActivity Sheets: Quarter 3 - MELC 2Alexa HullezaNo ratings yet

- Bundle Bundle Js LICENSEDocument11 pagesBundle Bundle Js LICENSE333surimaNo ratings yet

- Fundamentals of Economics and ManagementDocument3 pagesFundamentals of Economics and Managementuot.shakeelNo ratings yet

- Material-Handler HydraForce 2015Document10 pagesMaterial-Handler HydraForce 2015yonggilNo ratings yet

- ABB Unit Trip EMAX PR112-PD PDFDocument27 pagesABB Unit Trip EMAX PR112-PD PDFPedro MartinsNo ratings yet

- Masterclass ReflectionDocument3 pagesMasterclass Reflectionapi-537874530No ratings yet

- Tabelas Roscas TrapezoidaisDocument49 pagesTabelas Roscas TrapezoidaisDesenvolvimento MHNo ratings yet

- DS IV Unit NotesDocument29 pagesDS IV Unit NotesAlagandula KalyaniNo ratings yet

- My First 10 Years ProjectDocument2 pagesMy First 10 Years ProjectahdyalNo ratings yet

- Ambivalent Relationships: The Balance Between Letting Go and Holding OnDocument11 pagesAmbivalent Relationships: The Balance Between Letting Go and Holding OnFernando FiallosNo ratings yet

- Ecs 2ar FDocument39 pagesEcs 2ar FĐức LêNo ratings yet

- Elizabeth Winifred Brewster,: CanadianDocument4 pagesElizabeth Winifred Brewster,: CanadianVinnoDarmawanNo ratings yet

- SYNTHESIS Filipino 1Document6 pagesSYNTHESIS Filipino 1DhanNo ratings yet

- Direction: Show Your Clear and Complete Solution To The Following Reliability Tests by Completing The Attached Tables. I. Test Retest MethodDocument8 pagesDirection: Show Your Clear and Complete Solution To The Following Reliability Tests by Completing The Attached Tables. I. Test Retest MethodJan Aries ManiponNo ratings yet

- ASSIGNMENT 1 FinalsDocument2 pagesASSIGNMENT 1 FinalsAnne Dela CruzNo ratings yet

- Year 9 Naplan Non CalcDocument12 pagesYear 9 Naplan Non CalcSophieNoorSalibiNo ratings yet

- DP FourSeals ENGDocument60 pagesDP FourSeals ENGgeorgia83609No ratings yet

- Accelerated Construction of Urban Intersections With Portlandcement Concrete Pavement (PCCP)Document3 pagesAccelerated Construction of Urban Intersections With Portlandcement Concrete Pavement (PCCP)A-16 RUSHALINo ratings yet

- Revision On Unit 1,2 First Secondry (Hello)Document11 pagesRevision On Unit 1,2 First Secondry (Hello)Vivian GendyNo ratings yet

- Safety Data Sheet: Section 1 - Product and Company IdentificationDocument4 pagesSafety Data Sheet: Section 1 - Product and Company IdentificationAnnaAffandieNo ratings yet

- Dokumen - Tips - Incalzire Cu Pompe de CalduraDocument34 pagesDokumen - Tips - Incalzire Cu Pompe de CalduraPitique De TarencriqueNo ratings yet

- Instruction Manual: HF TransceiverDocument88 pagesInstruction Manual: HF TransceiverRahadianNo ratings yet

D D D D D D: TMS57535A 480Ch 64G/S Color TFT Source Driver

D D D D D D: TMS57535A 480Ch 64G/S Color TFT Source Driver

Uploaded by

zigmund zigmundOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

D D D D D D: TMS57535A 480Ch 64G/S Color TFT Source Driver

D D D D D D: TMS57535A 480Ch 64G/S Color TFT Source Driver

Uploaded by

zigmund zigmundCopyright:

Available Formats

TMS57535A

480CH 64G/S COLOR TFT SOURCE DRIVER

SLDS142 – AUGUST 2001

D Dot and N-Line Inversion Available PACKAGE INFORMATION

D Six-Bit (64 Gray-Scale) Digital Driver The TCP’s external shape is customized. To

D Mini-LVDS Level Input (Five Pairs of Serial order the required shape, contact a TI sales

Data Inputs) representative.

D 480 Output Ports (for UXGA Format)

D VDD for Logic Port: 2.7 V to 3.6 V

D VDD for LCD Driving Port: 8 V to 13.5 V

description

TMS57535A is a six bit (64 gray-scale) source

driver for TFT liquid-crystal display (LCD) with 480

output ports to deal with UXGA format.

Reduction in the number of input ports and

electromagnetic interference (EMI) is expected

with the introduction of mini-LVDS (low voltage

differential signaling) interface at the input ports.

PRODUCT PREVIEW

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCT PREVIEW information concerns products in the formative or Copyright 2001, Texas Instruments Incorporated

design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right to

change or discontinue these products without notice.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

TMS57535A

480CH 64G/S COLOR TFT SOURCE DRIVER

SLDS142 – AUGUST 2001

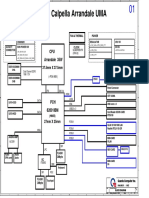

functional block diagram

OUT479

OUT1 OUT2 OUT3 OUT478 OUT480

LCH

LP Output Circuit

POL

Digital to Analog

GMA1 to GMA10

Converter

6 6 6 6 6 6

480 × 6 Bit

TP1

× 2 Line Latch

PRODUCT PREVIEW

LV0A

LV0B

LV1A

LV1B Dn0 to Dn5

Serial

to

Parallel

LV5A

Converter

LV5B

Shift Register

CLKA

CLKB

SB

EIO1

Logic Controller

EIO2

L/R

2 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TMS57535A

480CH 64G/S COLOR TFT SOURCE DRIVER

SLDS142 – AUGUST 2001

TCP pin assignments

TMS57535A

VSS1

VDD1

GMA10 OUT 480

GMA9 OUT 479

GMA8 OUT 478

GMA7 OUT 477

GMA6 OUT 476

SB

LCH

LP

L/R

VSS2

VSS*

LV5B

LV5A

VSS*

LV4B

LV4A

VSS*

PRODUCT PREVIEW

LV3B

LV3A

VSS*

CLKB

CLKA

VSS*

LV2B

LV2A

VSS*

LV1B

LV1A

VSS*

LV0B

LV0A

VSS*

VDD2 (*1)

VDD2 (*2)

TP1

POL

EIO2 OUT 5

EIO1 OUT 4

GMA5 OUT 3

GMA4 OUT 2

GMA3 OUT 1

GMA2

GMA1

VDD1

VSS1

NOTE: Pattern side up and no dimension specification for the TCP

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 3

TMS57535A

480CH 64G/S COLOR TFT SOURCE DRIVER

SLDS142 – AUGUST 2001

Terminal Functions

TERMINAL

I/O DESCRIPTION

NAME

CLKA, CLKB I Clock (mini-LVDS). Shift clock (refer to Table 1)

LV0A, B–LV5A, B I Display data (mini-LVDS). Displays data with gray-scale data (6-bit) and control signal (RST=reset) (refer to Table

1)

L/R I Shift direction. Controls the direction of loaded data at the shift register (refer to Table 2)

EIO1, EIO2 I/O Start pulse. Input/Output definition of address shift register (refer to Table 2)

TP1 I Input mode and output timing control. Changes the input mode, latches the registered data, and transfers to the DAC

at the rising edge. Voltage to LCD pixel is output at falling edge.

POL I Polarity control. Controls the polarity of the output. Defined by the POL signal at TP1 as H

(refer to Table 3)

LCH I Drivability control.

LCH = H: Higher drivability for heavy load

LCH = L; Normal drivability

LP I Low power mode selection. Decreases the charge/discharge current to output load. LP=H: low power mode. Refer

to the application notes.

SB I Bus-line set-back. Changes the data order of mini-LVDS input (see Table 1)

PRODUCT PREVIEW

OUT1–OUT480 O Output. Supplies voltage to each LCD pixel.

VDD1, VSS1 I Power supply (output circuits). Power supply for output (driving) circuits

VDD2(*1) I Power supply (control=logic circuits). VDD2(*1) is for mini-LVDS receiver and VDD2(*2) is for other logic circuits.

VDD2(*2) Supplies stable voltage to VDD2(*1).

VSS2 VDD2(*1) and VDD2(*2) must be at the same electric potential.

VSS* Possible to wire the VSS potential between each mini-LVDS signal line from VSS* terminal, though no wiring, no

relation to function itself.

GMA1–GMA10 I γ-corrected power supplies. Receives the external γ-corrected power supplies by using operational amplifiers.

Maintain the recommended operating conditions.

Table 1. Function Table (Bus-Line Set-Back)

PIN NAME SB=L SB=H

LV0A DUMMY LV4–

LV0B DUMMY LV4+

LV1A LV0+ LV3–

LV1B LV0– LV3+

LV2A LV1+ LV2–

LV2B LV1– LV2+

CLKA CLK+ CLK–

CLKB CLK– CLK+

LV3A LV2+ LV1–

LV3B LV2– LV1+

LV4A LV3+ LV0–

LV4B LV3– LV0+

LV5A LV4+ DUMMY

LV5B LV4– DUMMY

Suffix + indicates positive potential and – indicates negative potential

at each differential signal input pair.

4 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TMS57535A

480CH 64G/S COLOR TFT SOURCE DRIVER

SLDS142 – AUGUST 2001

Table 2. Function Table (L/R and EIOn)

L/R EIO1 EIO2 Shift Direction

H Right shift: in Right shift: out OUT1 → OUT480

L Left shift: out Left shift: in OUT480 → OUT1

Table 3. Function Table (POL and Reference GAMMA)

POL ODD-NUMBERED OUTPUT EVEN-NUMBERED OUTPUT

H GMA6 to GMA10 GMA1 to GMA5

L GMA1 to GMA5 GMA6 to GMA10

detailed description

data mapping

Display and control data (RST) are input to LV0+,– to LV4+,–.

Data mapping is changed in response to the mode; the mode is changed by TP1.

<Data Input Mode>

PRODUCT PREVIEW

CLK+

LV0+ D00 D01 D02 D03 D04 D05 D00

LV1+ D10 D11 D12 D13 D14 D15 D10

LV2+ D20 D21 D22 D23 D24 D25 D20

LV3+ D30 D31 D32 D33 D34 D35 D30

LV4+ D40 D41 D42 D43 D44 D45 D40

Data Input Cycle

< Control Signal Input Mode >

CLK+

LV0+

RST RST RST RST RST RST RST

LV0–

There is no assignment from LV1+,– to LV4+,–. Therefore, they are don’t care.

Output timing and polarity are controlled by TP1 and POL signals. Refer to the Terminal Function table and

Table 3.

composition of display data

MSB LSB

Dn5 Dn4 Dn3 Dn2 Dn1 Dn0 N = 0 to 4

relation between display data and output number

OUTPUT OUT1 OUT2 OUT3 OUT478 OUT479 OUT480

Display data D00 to D05 D10 to D15 D20 to D25 ––––––– D20 to D25 D30 to D35 D40 to D45

This relationship is irrespective of L/R condition.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 5

TMS57535A

480CH 64G/S COLOR TFT SOURCE DRIVER

SLDS142 – AUGUST 2001

detailed description (continued)

cascade

Multiple chips can be used in a cascade connection.

D Input EIO pad at lead (head) chip is fixed to H.

D Input EIO after secondary chips are connected to output EIO of lead chip.

Receiving the display data

D The lead (head) chip is set to control signal input mode (also called control mode), and the receivers at

LV0+,– and CLK+,– on all chips are activated by the rising edge of TP1.

D Input the reset (RST) signal to LV0+,– as L. This RST must be maintained over 200 ns after rising of TP1.

D Input RST as H to LV0+,–. The duration of H must be over 50 ns and at least three CLK cycles.

D Input the RST as L to LV0+,–; then change to the data input mode function. Input TP1 again when a second

RST is necessary.

D Data sampling starts at the rising edge of CLK after reading of RST=L.

D The internal counter starts counting the data cycle for EIO signal generation at the same time data sampling

PRODUCT PREVIEW

starts.

D When data sampling is finished, the receivers turn off.

D After the receivers turn off, keep the timing for at least five more CLK cycles until TP1 is applied.

D Figure 1 shows the rough timing chart from application of TP1 to the start of data sampling.

Read Reset (RST) Read RST = L

CLK1

CLK+

LV0+ RST DATA1 DATA2

Greater than 50 ns

LV1+ to LV4+ and 3 CLK Cycles DATA1 DATA2

200 ns Start Data Sampling

TP1

H

Input EIO

Control Signal Input Mode Data Input Mode

Figure 1. Timing From Start to Sampling (Reference)

6 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TMS57535A

480CH 64G/S COLOR TFT SOURCE DRIVER

SLDS142 – AUGUST 2001

detailed description (continued)

relation between input data and output voltage

The digital-to-analog converter (D/A) consists of resistors connected in a ladder configuration. Figure 2 shows

an outline of the relation between input data and γ-corrected voltages.

VDD1

GMA1

GMA2

GMA3

GMA4

GMA5

GMA6

GMA7

GMA8

GMA9

PRODUCT PREVIEW

GMA10

VSS1

0 10 20 30 3F

Input Data – Hex

Figure 2. γ-Corrected Power Supplies

ladder resistors

Resistors are connected to each terminal of the power supplies for γ-corrected supplies, and the resistance ratio

is given in Table 4.

Table 4. Resistor Ratio

GMA1 GMA6

RESISTOR RATIO

R1 R5

R1, R8 161

GMA2 GMA7

R2, R7 55

R2 R6 R3, R6 32

GMA3 GMA8 R4, R5 69

R3 R7

GMA4 GMA9

R4 R8

GMA5 GMA10

Positive Polarity Negative Polarity

Figure 3. Ladder Resistors Connection

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 7

TMS57535A

480CH 64G/S COLOR TFT SOURCE DRIVER

SLDS142 – AUGUST 2001

detailed description (continued)

relation between input data and output voltage

Table 5. Positive Polarity

DATA DATA

OUTPUT VOLTAGE OUTPUT VOLTAGE

(HEX) (HEX)

00 GMA1 20 GMA3

01 GMA2+(GMA1–GMA2)X 145/161 21 GMA4+(GMA3–GMA4)X 30/32

02 GMA2+(GMA1–GMA2)X 130/161 22 GMA4+(GMA3–GMA4)X 28/32

03 GMA2+(GMA1–GMA2)X 116/161 23 GMA4+(GMA3–GMA4)X 26/32

04 GMA2+(GMA1–GMA2)X 103/161 24 GMA4+(GMA3–GMA4)X 24/32

05 GMA2+(GMA1–GMA2)X 91/161 25 GMA4+(GMA3–GMA4)X 22/32

06 GMA2+(GMA1–GMA2)X 80/161 26 GMA4+(GMA3–GMA4)X 20/32

07 GMA2+(GMA1–GMA2)X 69/161 27 GMA4+(GMA3–GMA4)X 18/32

08 GMA2+(GMA1–GMA2)X 59/161 28 GMA4+(GMA3–GMA4)X 16/32

09 GMA2+(GMA1–GMA2)X 49/161 29 GMA4+(GMA3–GMA4)X 14/32

0A GMA2+(GMA1–GMA2)X 41/161 2A GMA4+(GMA3–GMA4)X 12/32

PRODUCT PREVIEW

0B GMA2+(GMA1–GMA2)X 33/161 2B GMA4+(GMA3–GMA4)X 10/32

0C GMA2+(GMA1–GMA2)X 26/161 2C GMA4+(GMA3–GMA4)X 8/32

0D GMA2+(GMA1–GMA2)X 19/161 2D GMA4+(GMA3–GMA4)X 6/32

0E GMA2+(GMA1–GMA2)X 12/161 2E GMA4+(GMA3–GMA4)X 4/32

0F GMA2+(GMA1–GMA2)X 6/161 2F GMA4+(GMA3–GMA4)X 2/32

10 GMA2 30 GMA4

11 GMA3+(GMA2–GMA3)X 49/55 31 GMA5+(GMA4–GMA5)X 67/69

12 GMA3+(GMA2–GMA3)X 44/55 32 GMA5+(GMA4–GMA5)X 65/69

13 GMA3+(GMA2–GMA3)X 39/55 33 GMA5+(GMA4–GMA5)X 63/69

14 GMA3+(GMA2–GMA3)X 34/55 34 GMA5+(GMA4–GMA5)X 61/69

15 GMA3+(GMA2–GMA3)X 30/55 35 GMA5+(GMA4–GMA5)X 59/69

16 GMA3+(GMA2–GMA3)X 26/55 36 GMA5+(GMA4–GMA5)X 56/69

17 GMA3+(GMA2–GMA3)X 22/55 37 GMA5+(GMA4–GMA5)X 53/69

18 GMA3+(GMA2–GMA3)X 19/55 38 GMA5+(GMA4–GMA5)X 50/69

19 GMA3+(GMA2–GMA3)X 16/55 39 GMA5+(GMA4–GMA5)X 46/69

1A GMA3+(GMA2–GMA3)X 13/55 3A GMA5+(GMA4–GMA5)X 42/69

1B GMA3+(GMA2–GMA3)X 10/55 3B GMA5+(GMA4–GMA5)X 37/69

1C GMA3+(GMA2–GMA3)X 8/55 3C GMA5+(GMA4–GMA5)X 32/69

1D GMA3+(GMA2–GMA3)X 6/55 3D GMA5+(GMA4–GMA5)X 26/69

1E GMA3+(GMA2–GMA3)X 4/55 3E GMA5+(GMA4–GMA5)X 16/69

1F GMA3+(GMA2–GMA3)X 2/55 3F GMA5

NOTE: GMA5 and GMA6 are not connected in the chip.

8 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TMS57535A

480CH 64G/S COLOR TFT SOURCE DRIVER

SLDS142 – AUGUST 2001

relation between input data and output voltage (continued)

Table 6. Negative Polarity

DATA OUTPUT VOLTAGE DATA OUTPUT VOLTAGE

(HEX) (HEX)

00 GMA10 20 GMA8

01 GMA10+(GMA9–GMA10)X 16/161 21 GMA8+(GMA7–GMA8)X 2/32

02 GMA10+(GMA9–GMA10)X 31/161 22 GMA8+(GMA7–GMA8)X 4/32

03 GMA10+(GMA9–GMA10)X 45/161 23 GMA8+(GMA7–GMA8)X 6/32

04 GMA10+(GMA9–GMA10)X 58/161 24 GMA8+(GMA7–GMA8)X 8/32

05 GMA10+(GMA9–GMA10)X 70/161 25 GMA8+(GMA7–GMA8)X 10/32

06 GMA10+(GMA9–GMA10)X 81/161 26 GMA8+(GMA7–GMA8)X 12/32

07 GMA10+(GMA9–GMA10)X 92/161 27 GMA8+(GMA7–GMA8)X 14/32

08 GMA10+(GMA9–GMA10)X 102/161 28 GMA8+(GMA7–GMA8)X 16/32

09 GMA10+(GMA9–GMA10)X 112/161 29 GMA8+(GMA7–GMA8)X 18/32

0A GMA10+(GMA9–GMA10)X 120/161 2A GMA8+(GMA7–GMA8)X 20/32

OB GMA10+(GMA9–GMA10)X 128/161 2B GMA8+(GMA7–GMA8)X 22/32

PRODUCT PREVIEW

OC GMA10+(GMA9–GMA10)X 135/161 2C GMA8+(GMA7–GMA8)X 24/32

OD GMA10+(GMA9–GMA10)X 142/161 2D GMA8+(GMA7–GMA8)X 26/32

OE GMA10+(GMA9–GMA10)X 149/161 2E GMA8+(GMA7–GMA8)X 28/32

OF GMA10+(GMA9–GMA10)X 155/161 2F GMA8+(GMA7–GMA8)X 30/32

10 GMA9 30 GMA7

11 GMA9+(GMA8–GMA9)X 6/55 31 GMA7+(GMA6–GMA7)X 2/69

12 GMA9+(GMA8–GMA9)X 11/55 32 GMA7+(GMA6–GMA7)X 4/69

13 GMA9+(GMA8–GMA9)X 16/55 33 GMA7+(GMA6–GMA7)X 6/69

14 GMA9+(GMA8–GMA9)X 21/55 34 GMA7+(GMA6–GMA7)X 8/69

15 GMA9+(GMA8–GMA9)X 25/55 35 GMA7+(GMA6–GMA7)X 10/69

16 GMA9+(GMA8–GMA9)X 29/55 36 GMA7+(GMA6–GMA7)X 13/69

17 GMA9+(GMA8–GMA9)X 33/55 37 GMA7+(GMA6–GMA7)X 16/69

18 GMA9+(GMA8–GMA9)X 36/55 38 GMA7+(GMA6–GMA7)X 19/69

19 GMA9+(GMA8–GMA9)X 39/55 39 GMA7+(GMA6–GMA7)X 23/69

1A GMA9+(GMA8–GMA9)X 42/55 3A GMA7+(GMA6–GMA7)X 27/69

1B GMA9+(GMA8–GMA9)X 45/55 3B GMA7+(GMA6–GMA7)X 32/69

1C GMA9+(GMA8–GMA9)X 47/55 3C GMA7+(GMA6–GMA7)X 37/69

1D GMA9+(GMA8–GMA9)X 49/55 3D GMA7+(GMA6–GMA7)X 43/69

1E GMA9+(GMA8–GMA9)X 51/55 3E GMA7+(GMA6–GMA7)X 53/69

1F GMA9+(GMA8–GMA9)X 53/55 3F GMA6

NOTE: GMA5 and GMA6 are not connected in the chip.

electrical/timing specifications

Basically, the ground-level voltage is VSS1 = VSS2 = 0 V.

Electrical and timing characteristics are assured under the recommended operating conditions.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 9

TMS57535A

480CH 64G/S COLOR TFT SOURCE DRIVER

SLDS142 – AUGUST 2001

absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

Supply voltage at logic port, VDD2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 V to 5 V

Supply voltage at driver port, VDD1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 V to 14.0 V

Input voltage: GMA1 to GMA10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 V to VDD1 + 0.5 V

Except GMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 V to VDD2 + 0.5 V

Output voltage: EIO1, EIO2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 V to VDD2 + 0.5 V

OUT1 to OUT480 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 V to VDD1 + 0.5 V

Storage temperature, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –55°C to 125°C

† Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

D Keep the order of the VDD2 input port except GMA, VDD1, and GMA1 to GMA10 when turning on the device,

and reverse the order when turning it off.

recommended operating conditions

MIN NOM MAX UNIT

VDD1 8 13.5

Supply voltage V

PRODUCT PREVIEW

VDD2 2.7 3 3.6

GMA1 to GMA5 1/2VDD1 VDD1–0.2

γ-corrected

corrected supply voltage V

GMA6 to GMA10 VSS1+0.2 1/2VDD1

Clock frequency, CLK 146 152 MHz

Load capacitance, driver output (CL), OUT1 to OUT480 125 pF

Operating free-air temperature range, TA –10 75 °C

EIO1, EIO2 10

capacitance CI

Input capacitance, pF

Except EIO and GMAn 5

NOTE: Relation of γ-corrected input voltage

VDD1>GMA1, GMAn ≤ GMAn+1 (n=1 to 9), GMA10>VSS1

10 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TMS57535A

480CH 64G/S COLOR TFT SOURCE DRIVER

SLDS142 – AUGUST 2001

electrical characteristics

TEST

PARAMETERS MIN TYP MAX UNIT

CONDITIONS

EIO1, EIO2,

VIH1 High-level input voltage L/R, TP1, LCH 0.7×VDD2 VDD2 V

LP, SB, POL

EIO1, EIO2,

VIL1 Low-level input voltage L/R, TP1, LCH 0 0.25×VDD2 V

LP, SB, POL

EIO1, EIO2,

L/R, TP1, LCH

II(lkg) Input leakage current LP, SB, POL, –1 1 µA

CLKA,B,

LV0A,B to LV5A,B

Mini-LVDS input voltage CLKA,B,

VI 0.3+(VID/2) (VDD2–1.2)–VID/2 V

(center) LV0A.B to LV5A,B

Mini-LVDS differential voltage CLKA,B,

VID 0.2 0.6 V

(amplitude: peak to peak) LV0A,B to LV5A,B

VX = VDD1–0.2

IO(chg) TBD µA

VO = VX–1.0

PRODUCT PREVIEW

Output current OUT1 to OUT480

VX = VSS+0.2

IO(dis) TBD µA

VO = VX+1.0

Output swing difference

δVO OUT1 to OUT480 See Note 1 ±10 mV

deviation

Averaged output voltage

δVO(avg) OUT1 to OUT480 See Note 2 ±10 mV

deviation

GMA1–GMA5

RGMA Ladder resistance 15850 Ω

GMA6–GMA10

VO Output voltage range OUT1 to OUT480 VSS1+0.2 VDD1–0.2 V

Black raster,

Driver port dynamic current VDD1 = 13.5 V,

ID(dp) VDD1–VSS1 TBD mA

consumption TP1 = 10 µs

No load

Black raster,

Driver port static current

IS(dp) VDD1–VSS1 VDD1 = 13.5 V, TBD mA

consumption

No load

TP1 = 10 µs,

Logic port dynamic current

ID(lp) VDD2–VSS2 fCLK = 110 MHz, TBD mA

consumption

Checkered

Logic port static current No clock, no

IS(lp) VDD2–VSS2 TBD mA

consumption input

NOTES: 1. Amplitude offset when all ports output the same data

2. Deviation in averaged amplitude offset between chips

3. Input the same value to all pairs of mini-LVDS inputs and mini-LVDS differential voltage ports.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 11

TMS57535A

480CH 64G/S COLOR TFT SOURCE DRIVER

SLDS142 – AUGUST 2001

timing requirements

PARAMETERS TEST CONDITIONS MIN TYP MAX UNIT

t1 Clock pulse cycle 6.5 6.8 ns

t2 Clock pulse high period 2.5 ns

t3 Clock pulse low period 2.5 ns

t4 Data setup time 1.25 ns

t5 Data hold time 1.25 ns

t6 EIO setup time –1 ns

t8 EIO signal delay time Load = 25 pF 16 TBD ns

t9 CLK, LV0 to LV5 rising time 0.5 ns

t10 CLK, LV0 to LV5 falling time 0.5 ns

t15 Target voltage ±0.1 VDD1 4

Driver output delay time (see Note 4) µss

t16 6-bit accuracy 8

50 ns over 3

t20 Reset (RST) high period

CLK cycles

t25 TP1 high period 0.2 µs

t28 POL setup time –5 ns

PRODUCT PREVIEW

t29 POL hold time 6.0 ns

CLK

t30 Receiver off to TP1 timing 5

cycles

t31 TP1 to reset input time 200 ns

t32 Reset low to TP1 rising time 0 ns

NOTE 4: Output load condition:

R R R R R

C C C C C

R = 4 kΩ

C = 25 pF

t1

t2 t3

CLK–

80%

50% VID

20%

CLK+

t10 t9

t4 t5 t4 t5

LV0+,– 80%

to 50% VID

20%

LV4+,–

t10 t9

Figure 4. Data Read Timing

12 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TMS57535A

480CH 64G/S COLOR TFT SOURCE DRIVER

SLDS142 – AUGUST 2001

Read RST = H Read RST = L

Starting Data Sampling

1 2

CLK+ 50% 50%

LV0+,– NA RST = L RST = L RST = H RST = H RST = H NA RST = L NA Data Data Data

t20

LV1+,–

to NA NA NA NA NA NA NA NA NA Data Data Data

LV4+,–

t32 t31

TP1 70%

EIO (IN) H

Control Signal Input Mode Data Input Mode

NOTE: No assigned data for NA

PRODUCT PREVIEW

Figure 5. Input Data Timing (Lead Chip)

276 277 280 286 288 289(1)

CLK+ 50% 50% 50% 50%

LV0+,–

to Data Data Data Data Data Data Data Data Data Data Data Data Data

LV4+,–

t8 t8

EIO (OUT) 70% 25%

t6 t6

EIO (IN) 70% 25%

Figure 6. Input Data Timing (Cascade Port)

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 13

TMS57535A

480CH 64G/S COLOR TFT SOURCE DRIVER

SLDS142 – AUGUST 2001

Last Data Timing

288 289 292

CLK+ 50% 50%

LV0+,– Data Data NA NA NA NA NA NA NA NA RST = L RST = L RST = L

LV1

to Data Data NA NA NA NA NA NA NA NA NA NA NA

LV4+,–

t32

TP1 25% 70%

t30

NOTE: No assigned data for NA

Figure 7. Last Data Sampling to TP1 Timing

PRODUCT PREVIEW

t25

t28 70% 70% t29

TP1

25% 25%

70% 70%

POL

25% 25%

t16

t15

OUTn Hi-Z

(n = 1 to 480)

Figure 8. Output Timing

Dxx n Line n+1 Line n+2 Line n+3 Line

TP1

OUT n–1 Line n Line n+1 Line n+2 Line

Figure 9. Relation Between Input and Output Data

14 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with

TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary

to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except

those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

products or services might be or are used. TI’s publication of information regarding any third party’s products

or services does not constitute TI’s approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without

alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation

or reproduction of this information with alteration voids all warranties provided for an associated TI product or

service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI’s products or services with statements different from or beyond the parameters stated by TI for

that product or service voids all express and any implied warranties for the associated TI product or service,

is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products. www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright 2001, Texas Instruments Incorporated

You might also like

- Placa 1156 - Pegatron Ipmip-Dp (Pos-Piq57bq) Rev 1.01Document68 pagesPlaca 1156 - Pegatron Ipmip-Dp (Pos-Piq57bq) Rev 1.01Francisco FreireNo ratings yet

- Esquema Schematic IPISB-VR Rev 1.01Document76 pagesEsquema Schematic IPISB-VR Rev 1.01Roberto MouraNo ratings yet

- Schematic Diagram t240Document6 pagesSchematic Diagram t240dany weinfeldNo ratings yet

- Asus X505BP Rev2.0Document97 pagesAsus X505BP Rev2.0santiago rodriguezNo ratings yet

- Desktop Dell HNJFVDocument51 pagesDesktop Dell HNJFVjoao batistaNo ratings yet

- HP Confidential MSI MS-7557 Ver:0A 2008-0722: WWW - Vinafix.vnDocument52 pagesHP Confidential MSI MS-7557 Ver:0A 2008-0722: WWW - Vinafix.vnMinh Tran100% (2)

- Wistron K6 IBM R51eDocument71 pagesWistron K6 IBM R51eMario Rodriguez JuradoNo ratings yet

- (DELL) 一款七寸平板电脑原理图JWT - V1A - 0721 - 16P2 PDFDocument30 pages(DELL) 一款七寸平板电脑原理图JWT - V1A - 0721 - 16P2 PDFsamuelNo ratings yet

- Pegatron Ipmip-GsDocument68 pagesPegatron Ipmip-GsBruno MartinsNo ratings yet

- TLC 549Document18 pagesTLC 549lanjiao333No ratings yet

- PEGATRON IPISB-SB Rev1.00 PDFDocument76 pagesPEGATRON IPISB-SB Rev1.00 PDFClaudeciNo ratings yet

- Quanta FH2A Intel Calpella Arrandale REV 1ADocument46 pagesQuanta FH2A Intel Calpella Arrandale REV 1AВиктор СёминNo ratings yet

- Datasheet 80C85 (Oki)Document29 pagesDatasheet 80C85 (Oki)José AdelinoNo ratings yet

- MC14442PDocument10 pagesMC14442PRuben AparicioNo ratings yet

- TLC 7225Document21 pagesTLC 7225tajpan77No ratings yet

- TDA8753A PhilipsSemiconductorsDocument20 pagesTDA8753A PhilipsSemiconductorsDaanNo ratings yet

- TLC 1514Document40 pagesTLC 1514Hoii ClarkNo ratings yet

- Fujitsu LifeBook LH530 Quanta FH1 Intel UMA Rev1A SchematicDocument37 pagesFujitsu LifeBook LH530 Quanta FH1 Intel UMA Rev1A SchematicAsep IndraNo ratings yet

- TLC5620Document14 pagesTLC5620Dirson Volmir WilligNo ratings yet

- ths5661 PDFDocument29 pagesths5661 PDFIqbal AchmadiNo ratings yet

- Dell - XPS One 2710 - IPIMB-PVDocument5 pagesDell - XPS One 2710 - IPIMB-PVisai ramos sotoNo ratings yet

- n91 MV d3h 0322Document58 pagesn91 MV d3h 0322Moh HamNo ratings yet

- Biostar G41D3 (Ver 7.0) PDFDocument32 pagesBiostar G41D3 (Ver 7.0) PDFEl TécnicoNo ratings yet

- 06060214-GJ-S8640002 - Tembagapura Emergency Power - Cable Schedule Buat PrintDocument9 pages06060214-GJ-S8640002 - Tembagapura Emergency Power - Cable Schedule Buat PrintJan Richardo GultomNo ratings yet

- Sharp MS-7082-3.0RohsDocument31 pagesSharp MS-7082-3.0RohsAladino SanchezNo ratings yet

- ¡ Semiconductor: MSM80C85AHRS/GS/JSDocument22 pages¡ Semiconductor: MSM80C85AHRS/GS/JScamaferNo ratings yet

- Fujitsu A 530Document34 pagesFujitsu A 530Makhtar SeyeNo ratings yet

- Safa Micro hw-1Document30 pagesSafa Micro hw-1suhailhajajjiNo ratings yet

- 74LS164Document4 pages74LS164jaja558No ratings yet

- Block Diagram 1381743Document1 pageBlock Diagram 1381743Andrzej GomulaNo ratings yet

- Mini Pcie Card Reference Design - V Rev 10 PDFDocument2 pagesMini Pcie Card Reference Design - V Rev 10 PDFanhxcoNo ratings yet

- Da0zhdmb8d0 LODocument40 pagesDa0zhdmb8d0 LOJacob TevenalNo ratings yet

- Pegatron Iaxbt-Bl Rev Rev. 1.01 Acer Aspire Zc-606Document67 pagesPegatron Iaxbt-Bl Rev Rev. 1.01 Acer Aspire Zc-606Ban NeoNo ratings yet

- Dell XPS One 2720 Pegatron IPPLP-PL Rev 1.01Document82 pagesDell XPS One 2720 Pegatron IPPLP-PL Rev 1.01Дамир АшеновNo ratings yet

- Xiufix WistronDocument66 pagesXiufix WistronCedomir Gajic100% (1)

- Fujitsu Ah530 SchimaticDocument38 pagesFujitsu Ah530 SchimaticabdullahNo ratings yet

- D D D D D D D D D D D D: TLV5618A 2.7-V TO 5.5-V LOW-POWER DUAL 12-BIT Digital-To-Analog Converter With Power DownDocument23 pagesD D D D D D D D D D D D: TLV5618A 2.7-V TO 5.5-V LOW-POWER DUAL 12-BIT Digital-To-Analog Converter With Power DownJulio Rafael GamboaNo ratings yet

- Sitronix: Dot Matrix LCD Controller/DriverDocument35 pagesSitronix: Dot Matrix LCD Controller/DriverSair Puello RuizNo ratings yet

- Asus Prime Z390-A Rev1.02 (60mb0yt0-Mb0a01)Document121 pagesAsus Prime Z390-A Rev1.02 (60mb0yt0-Mb0a01)mm aaNo ratings yet

- MS-6728 AtxDocument33 pagesMS-6728 AtxRisoSilvaNo ratings yet

- MS-6728 AtxDocument33 pagesMS-6728 AtxRisoSilvaNo ratings yet

- TLV0831C etcTIDocument21 pagesTLV0831C etcTIEsen KayaNo ratings yet

- D D D D D D D D D D: DescriptionDocument12 pagesD D D D D D D D D D: DescriptionRogério MorenoNo ratings yet

- Quanta FH9 DA0FH9MB6C0 - R2aDocument48 pagesQuanta FH9 DA0FH9MB6C0 - R2aYetawa GuaviareNo ratings yet

- Esquema Placa Mae BiostarDocument39 pagesEsquema Placa Mae BiostarERICO STRAMANDINOLINo ratings yet

- 8-CHANNEL, 12-/10-/8-BIT, 2.7-V TO 5.5-V LOW POWER Digital-To-Analog Converter With Power DownDocument26 pages8-CHANNEL, 12-/10-/8-BIT, 2.7-V TO 5.5-V LOW POWER Digital-To-Analog Converter With Power Downjasonkee111No ratings yet

- Tca9555 Low-Voltage 16-Bit I C and Smbus I/O Expander With Interrupt Output and Configuration RegistersDocument46 pagesTca9555 Low-Voltage 16-Bit I C and Smbus I/O Expander With Interrupt Output and Configuration RegistersLuiz LuizNo ratings yet

- CDocument35 pagesCJagopati Jr.No ratings yet

- d8dc8 MS-7348Document29 pagesd8dc8 MS-7348rolan444No ratings yet

- Ak4351vt AkmDocument14 pagesAk4351vt Akmpuh1967No ratings yet

- MS-6728 AtxDocument33 pagesMS-6728 AtxRisoSilvaNo ratings yet

- ST7066 EtcDocument29 pagesST7066 Etcjose aponteNo ratings yet

- AK4346Document31 pagesAK4346naeem_aaNo ratings yet

- 85C471 OVERVIEW: 85C471 Green PC ISA-VESA Single ChipDocument79 pages85C471 OVERVIEW: 85C471 Green PC ISA-VESA Single ChipevasiveNo ratings yet

- 14 Router Connection DetailsDocument22 pages14 Router Connection DetailsErik VahlandNo ratings yet

- ASUS IPPSB-SFA DELL Inspiron One 2320Document79 pagesASUS IPPSB-SFA DELL Inspiron One 2320Mustafa FanuswalaNo ratings yet

- Asrock G41M-VS3 - 1.01 PDFDocument35 pagesAsrock G41M-VS3 - 1.01 PDFthiago date100% (2)

- Генерация SMI# - SCI - 004 - ID - 631119 - Встроенное описание концентратора контроллеров платформы семейства наборов микросхем Intel® серии 500, том 1Document38 pagesГенерация SMI# - SCI - 004 - ID - 631119 - Встроенное описание концентратора контроллеров платформы семейства наборов микросхем Intel® серии 500, том 1zigmund zigmundNo ratings yet

- NS-A031 ODD To VGA Board Schematic Compal)Document17 pagesNS-A031 ODD To VGA Board Schematic Compal)zigmund zigmundNo ratings yet

- NVIDIA P407-A00 NVIDIA G84M MXM SchematicDocument18 pagesNVIDIA P407-A00 NVIDIA G84M MXM Schematiczigmund zigmundNo ratings yet

- Ultrahigh-Speed Switching Applications: Package Dimensions FeaturesDocument4 pagesUltrahigh-Speed Switching Applications: Package Dimensions Featureszigmund zigmundNo ratings yet

- Dmn66D0Ldw: Dual N-Channel Enhancement Mode MosfetDocument5 pagesDmn66D0Ldw: Dual N-Channel Enhancement Mode Mosfetzigmund zigmundNo ratings yet

- Intel Procecor RaznDocument20 pagesIntel Procecor Raznzigmund zigmundNo ratings yet

- LM358 Low Power Dual Op-Amp - Datasheet: TrendingDocument10 pagesLM358 Low Power Dual Op-Amp - Datasheet: Trendingzigmund zigmundNo ratings yet

- Internal Photos PDF 2208521Document4 pagesInternal Photos PDF 2208521zigmund zigmundNo ratings yet

- Dmn66D0Ldw Product Summary Features and Benefits: Dual N-Channel Enhancement Mode MosfetDocument6 pagesDmn66D0Ldw Product Summary Features and Benefits: Dual N-Channel Enhancement Mode Mosfetzigmund zigmundNo ratings yet

- Datasheet DTC115EDocument13 pagesDatasheet DTC115Ezigmund zigmundNo ratings yet

- BQ 26501Document31 pagesBQ 26501zigmund zigmundNo ratings yet

- Description: N-Channel Enhancement Mode Field-Effect TransistorDocument13 pagesDescription: N-Channel Enhancement Mode Field-Effect Transistorzigmund zigmundNo ratings yet

- Cec - in Stock - CrystalsDocument3 pagesCec - in Stock - Crystalszigmund zigmundNo ratings yet

- SN 74 LVC 1 G 04Document44 pagesSN 74 LVC 1 G 04zigmund zigmundNo ratings yet

- Dtc115eefra Dtc115ekafra Dtc115emfha Dtc115euafraDocument10 pagesDtc115eefra Dtc115ekafra Dtc115emfha Dtc115euafrazigmund zigmundNo ratings yet

- JMB38X JMicronDocument3 pagesJMB38X JMicronzigmund zigmundNo ratings yet

- Si 2399 DsDocument11 pagesSi 2399 Dszigmund zigmundNo ratings yet

- Two-Level Temperature Switch Circuit With LM358Document10 pagesTwo-Level Temperature Switch Circuit With LM358zigmund zigmundNo ratings yet

- Datasheet NCP81109Document28 pagesDatasheet NCP81109zigmund zigmundNo ratings yet

- SMB30 DatasheetDocument4 pagesSMB30 Datasheetzigmund zigmundNo ratings yet

- Compal La-8691p r0.3Document66 pagesCompal La-8691p r0.3zigmund zigmundNo ratings yet

- Compal Confidential: G400S/G500S Hematics DocumentDocument113 pagesCompal Confidential: G400S/G500S Hematics Documentzigmund zigmundNo ratings yet

- datasheet ABS2~ABS10-мост-выпрямительDocument3 pagesdatasheet ABS2~ABS10-мост-выпрямительzigmund zigmundNo ratings yet

- SN74AVC4 DatasheetDocument19 pagesSN74AVC4 Datasheetzigmund zigmundNo ratings yet

- NX7002AKS NexperiaDocument15 pagesNX7002AKS Nexperiazigmund zigmundNo ratings yet

- Compal La-8691p r0.2Document66 pagesCompal La-8691p r0.2zigmund zigmundNo ratings yet

- Proposal Lab 5Document4 pagesProposal Lab 5darkzainiNo ratings yet

- Apollo Valves: 94A / 95A SeriesDocument1 pageApollo Valves: 94A / 95A Seriesmaruthappan sundaramNo ratings yet

- SEAS RSRC 57bfe799620e0Document4 pagesSEAS RSRC 57bfe799620e0WunNaNo ratings yet

- Harris Ts100 User ManualDocument24 pagesHarris Ts100 User ManualMiguel Alfonso Ruiz MendezNo ratings yet

- 5S (Methodology) : 5S Is The Name of A Workplace Organization Methodology That Uses A List of FiveDocument3 pages5S (Methodology) : 5S Is The Name of A Workplace Organization Methodology That Uses A List of FiveRoberto DiyNo ratings yet

- TM-Editor 25.04.2016 Seite 1 050-Meteorology - LTMDocument308 pagesTM-Editor 25.04.2016 Seite 1 050-Meteorology - LTMIbrahim Med100% (1)

- PUD Ingles 6 y 7Document66 pagesPUD Ingles 6 y 7Hilda Elizabeth VeraNo ratings yet

- SeminarDocument29 pagesSeminarAkash shindeNo ratings yet

- Activity Sheets: Quarter 3 - MELC 2Document9 pagesActivity Sheets: Quarter 3 - MELC 2Alexa HullezaNo ratings yet

- Bundle Bundle Js LICENSEDocument11 pagesBundle Bundle Js LICENSE333surimaNo ratings yet

- Fundamentals of Economics and ManagementDocument3 pagesFundamentals of Economics and Managementuot.shakeelNo ratings yet

- Material-Handler HydraForce 2015Document10 pagesMaterial-Handler HydraForce 2015yonggilNo ratings yet

- ABB Unit Trip EMAX PR112-PD PDFDocument27 pagesABB Unit Trip EMAX PR112-PD PDFPedro MartinsNo ratings yet

- Masterclass ReflectionDocument3 pagesMasterclass Reflectionapi-537874530No ratings yet

- Tabelas Roscas TrapezoidaisDocument49 pagesTabelas Roscas TrapezoidaisDesenvolvimento MHNo ratings yet

- DS IV Unit NotesDocument29 pagesDS IV Unit NotesAlagandula KalyaniNo ratings yet

- My First 10 Years ProjectDocument2 pagesMy First 10 Years ProjectahdyalNo ratings yet

- Ambivalent Relationships: The Balance Between Letting Go and Holding OnDocument11 pagesAmbivalent Relationships: The Balance Between Letting Go and Holding OnFernando FiallosNo ratings yet

- Ecs 2ar FDocument39 pagesEcs 2ar FĐức LêNo ratings yet

- Elizabeth Winifred Brewster,: CanadianDocument4 pagesElizabeth Winifred Brewster,: CanadianVinnoDarmawanNo ratings yet

- SYNTHESIS Filipino 1Document6 pagesSYNTHESIS Filipino 1DhanNo ratings yet

- Direction: Show Your Clear and Complete Solution To The Following Reliability Tests by Completing The Attached Tables. I. Test Retest MethodDocument8 pagesDirection: Show Your Clear and Complete Solution To The Following Reliability Tests by Completing The Attached Tables. I. Test Retest MethodJan Aries ManiponNo ratings yet

- ASSIGNMENT 1 FinalsDocument2 pagesASSIGNMENT 1 FinalsAnne Dela CruzNo ratings yet

- Year 9 Naplan Non CalcDocument12 pagesYear 9 Naplan Non CalcSophieNoorSalibiNo ratings yet

- DP FourSeals ENGDocument60 pagesDP FourSeals ENGgeorgia83609No ratings yet

- Accelerated Construction of Urban Intersections With Portlandcement Concrete Pavement (PCCP)Document3 pagesAccelerated Construction of Urban Intersections With Portlandcement Concrete Pavement (PCCP)A-16 RUSHALINo ratings yet

- Revision On Unit 1,2 First Secondry (Hello)Document11 pagesRevision On Unit 1,2 First Secondry (Hello)Vivian GendyNo ratings yet

- Safety Data Sheet: Section 1 - Product and Company IdentificationDocument4 pagesSafety Data Sheet: Section 1 - Product and Company IdentificationAnnaAffandieNo ratings yet

- Dokumen - Tips - Incalzire Cu Pompe de CalduraDocument34 pagesDokumen - Tips - Incalzire Cu Pompe de CalduraPitique De TarencriqueNo ratings yet

- Instruction Manual: HF TransceiverDocument88 pagesInstruction Manual: HF TransceiverRahadianNo ratings yet