Professional Documents

Culture Documents

Digital Lab Manual To Print 2 Verified

Digital Lab Manual To Print 2 Verified

Uploaded by

Vinooja cOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Lab Manual To Print 2 Verified

Digital Lab Manual To Print 2 Verified

Uploaded by

Vinooja cCopyright:

Available Formats

0

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

IC PIN OUT

74LS00 74LS02

74LS04 74LS08

74LS10 74LS11

74LS20 74LS32

IC PIN OUT

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

1

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

74LS83A 74LS86

74LS151 74LS73A

74LS74A 74LS76

74LS93 555 TIMER

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

2

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

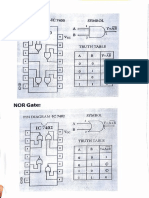

Gate Symbol Truth Table Using NAND Using NOR

and Expression

NOT

A Y

0 1

1 0

AND

A B Y

0 0 0

0 1 0

1 0 0

1 1 1

OR

A B Y

0 0 0

0 1 1

1 0 1

1 1 1

NAND

A B Y

0 0 1

0 1 1

1 0 1

1 1 0

NOR

A B Y

0 0 1

0 1 0

1 0 0

1 1 0

XOR

A B Y

0 0 0

0 1 1

1 0 1

1 1 0

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

3

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Experiment No: 1 Date: …. / …. /…...

REALIZATION OF STANDARD GATES USING UNIVERSAL GATES

AIM:

To realize the standard gates using universal gates and verify their truth tables.

PRE-REQUISITES

Logic functions of various gates

Truth table of various gates

COMPONENTS AND EQUIPMENTS REQUIRED:

IC-7400, IC-7402, IC trainer kit

THEORY:

NAND gate and NOR gate are called universal gates or universal building blocks

because both can be used to implemented any gate like AND or NOT gates.

Realization of logic functions using NAND gates

Any logic function can be implemented using NAND gates. To achieve this, first the

logic function has to be written in SOP (sum of product form) form. Then this can be easily

implemented using NAND gates. In other words, a logic circuit with AND gate in the first level

and OR gate in the second level can be converted into a NAND-NAND gate circuit.

Realization of logic functions using NOR gates

Any logic function can also be implemented using NOR gates. To achieve this first the

logic function has to be written in POS (product of sum) form. Then this can be easily realized

using NOR gates. In other words, a logic circuits with OR gate in the first level and AND gates

in the second level can be converted into a NOR –NOR gate circuit.

PROCEDURE:

1. Test all the components and IC packages using multimeter and digital IC tester.

2. Setup the circuits one by one and verify their truth tables.

3. Observe the output corresponding to input combinations and enter it in the truth table.

RESULT:

Realized the standard gates using universal gates and verified their truth tables.

VIVA QUESTIONS:

1. What is a logic gate?

2. Which are the universal gates? Why are they called so?

3. Develop the truth table for a three input NAND gate.

4. Realize an XNOR gate using NAND gate.

5. What the literals L & S indicate in 74LS00?

6. State De-Morgan’s theorem.

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

4

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

HALF ADDER

Truth table & Expression Circuit Diagram

Input Output

A B S C out

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

Sum = 𝐴 𝐵 + 𝐴𝐵

=𝐴 ⊕ 𝐵

Carry = AB

HALF SUBTRACTOR

Truth table & Expression Circuit Diagram

Input Output

A B D Bo

0 0 0 0

0 1 1 1

1 0 1 0

1 1 0 0

Difference = 𝐴 𝐵 + 𝐴𝐵

=𝐴 ⊕ 𝐵

Borrow =𝐴𝐵

FULL ADDER

Truth table & Expression Circuit Diagram

Input Output

A B C in S C out

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

S =AB𝐶𝑖𝑛 +AB𝐶𝑖𝑛 + AB𝐶𝑖𝑛 +AB𝐶𝑖𝑛 𝐶𝑂𝑈𝑇 =𝐴𝐵𝐶𝑖𝑛 + 𝐴𝐵 𝐶𝑖𝑛 + 𝐴𝐵𝐶𝑖𝑛 + 𝐴𝐵𝐶𝑖𝑛

=𝐴 𝐵 𝐶𝑖𝑛 + 𝐵𝐶𝑖𝑛 +A 𝐵 𝐶 𝑖𝑛 + 𝐵𝐶𝑖𝑛 = 𝐴𝐵 + 𝐴𝐵 𝐶𝑖𝑛 + AB (𝐶𝑖𝑛 +𝐶𝑖𝑛 )

=𝐴 𝐵 ⊕ 𝐶𝑖𝑛 +A(𝐵 ⊕ 𝐶𝑖𝑛 ) = A ⊕ B 𝐶𝑖𝑛 + 𝐴𝐵

= A⊕B⊕𝐶𝑖𝑛

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

5

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Experiment No: 2 Date: …. / …. /…...

HALF ADDER, FULL ADDER, HALF SUBTRACTOR AND FULL

SUBTRACTOR

AIM:

To design and setup the half adder, full adder, half subtractor and full subtractor circuit

using basic gates, universal gates and verify their truth tables.

PRE-REQUISITES

Concept of adders

Simplification of Boolean functions

Conversion of a standard circuit to universal gate circuit

COMPONENTS AND EQUIPMENTS REQUIRED:

IC-7400

IC-7402

IC-7404

IC-7408

IC-7432

IC-7486

IC trainer kit

THEORY:

Half adder

A combinational circuit that performs the addition of two bits is called a half adder. It has

two binary inputs and two binary outputs. The input variables designate the augend and addend

bits; the output variables produce the sum and the carry. We assign symbols A and B to the two

inputs and S (for sum) and C (for carry). The simplified sums of products expressions for the

outputs are

Sum = 𝐴 𝐵 + 𝐴𝐵

=𝐴 ⊕ 𝐵

Carry = AB

Full adder

A full adder is a combinational circuit that performs the arithmetic sum of three bits. It

consists of three inputs and two outputs. Two of the input variables represent the two significant

bits to be added. The third input represent the carry from the previous lower significant position.

The outputs are designated by the symbols S for sum and C for carry. The simplified sum of

product expressions for the outputs are

S = A⊕B⊕𝐶𝑖𝑛

𝐶𝑂𝑈𝑇 = A ⊕ B 𝐶𝑖𝑛 + 𝐴𝐵

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

6

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

FULL SUBTRACTOR

Truth table & Expression Circuit Diagram

Input Output

A B C in D Bo

0 0 0 0 0

0 0 1 1 1

0 1 0 1 1

0 1 1 0 1

1 0 0 1 0

1 0 1 0 0

1 1 0 0 0

1 1 1 1 1

D=AB𝐶𝑖𝑛 +AB𝐶𝑖𝑛 + AB𝐶𝑖𝑛 +AB𝐶𝑖𝑛 𝐵0= 𝐴𝐵 𝐶𝑖𝑛 + 𝐴𝐵𝐶𝑖𝑛 + 𝐴𝐵𝐶𝑖𝑛 + 𝐴𝐵𝐶𝑖𝑛

=𝐴 𝐵 𝐶𝑖𝑛 + 𝐵𝐶𝑖𝑛 +A 𝐵 𝐶 𝑖𝑛 + 𝐵𝐶𝑖𝑛 = 𝐴𝐵 + 𝐴𝐵 𝐶𝑖𝑛 + 𝐴B(𝐶𝑖𝑛 +𝐶𝑖𝑛 )

=𝐴 𝐵 ⊕ 𝐶𝑖𝑛 +A(𝐵 ⊕ 𝐶𝑖𝑛 ) = (𝐴 ⊕ 𝐵)𝐶𝑖𝑛 +𝐴B

= A⊕B⊕𝐶𝑖𝑛

Implementation of Adders and Subtractors using universal gates

Half Adder using NAND gates only

Half Subtractor using NAND gates only

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

7

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Half subtractor

A combinational circuit that performs the subtraction of two bits is called a half

subtractor. It has two binary inputs and two binary outputs. The output variables produce the sum

and the carry. We assign symbols A and B to the two inputs and D (for difference) and BO (for

borrow). The simplified sums of products expressions for the outputs are

Difference = 𝐴 𝐵 + 𝐴𝐵

=𝐴 ⊕ 𝐵

Borrow =𝐴𝐵

Full subtractor

A full subtractor is a combinational circuit that performs the subtraction of three bits. It

consists of three inputs and two outputs. Two of the input variables represent the two significant

bits to be subtracted. The third input represents the borrow from the previous lower significant

position. The outputs are designated by the symbols D for difference and BO for borrow. The

simplified sums of product expressions for the outputs are

Difference = A⊕B⊕𝐶𝑖𝑛

Borrow=(𝐴 ⊕ 𝐵)𝐶𝑖𝑛 +𝐴 B

PROCEDURE:

1. Verify whether the components are good or not.

2. Set up the half adder circuit and feed the input bit combinations.

3. Observe the output corresponding to input combination and enter the input in truth table.

4. Repeat the above steps for full adder circuit.

5. Set up the half subtractor circuit and feed the input bit combinations.

6. Observe the output corresponding to input combination and enter the input in truth table.

7. Repeat the above steps for full subtractor circuit.

RESULT:

The adder and subtractor circuits are set up and verified the operation with the truth table

VIVA QUESTIONS:

1. What is the difference between a half adder and full adder?

2. What is Carry Look Ahead Addition?

3. What is the difference between half subtractor and full subtractor?

4. Implement full adder and full subtractor using universal gates.

5. What are the applications of adders and subtractors?

6. Realize a full adder using two half adders.

7. Realize a full subtractors using two half subtractors.

8. Construct a circuit to add two 2 bit numbers using Half and Full adders.

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

8

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

4 BIT ADDER

S = A+B ; A and B are 4 bit binary numbers

OBSERVATION:

A=___________________B=__________________S=__________________

A=___________________B=__________________S=__________________

4 BIT SUBTRACTOR

Z= X-Y =X + (-Y). Here –Y is assumed as the 2’s complement [ take X>Y]

OBSERVATION:

X=___________________Y=__________________Z=__________________

X=___________________Y=__________________Z=__________________

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

9

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Experiment No: 3 Date: …. / …. /…...

4 BIT ADDER AND SUBTRACTOR

AIM:

To design and setup the 4 bit adder, 4 bit subtractor and 4 bit adder/subtractor - using

mode control using IC-7483.

PRE-REQUISITES

Concept of half and full adders, parallel adders

Concept of binary addition and binary subtraction using 2’s complement method

Concept of preparing truth tables

COMPONENTS AND EQUIPMENTS REQUIRED:

IC-7404, IC-7483, IC-7486, IC trainer kit

THEORY:

The 7483 is a TTL IC with 4 full adders in it. This means it can add nibbles. To add

bytes, we need to use two 7483 ICs. The internal operation of IC 7483 is

A4 A3 A2 A1 +

B4 B3 B2 B1+

. CI

C0 S4 S3 S2 S1 .

The 4 bit addition is a parallel addition in which the operation will be S = A+B ; A

and B are 4 bit binary numbers. And S may be a 4 bit number or 5 bit number. The 5th bit will be

the CO of the IC. During the addition, we keep CI=0

In 4 bit subtractor, the operation is based on the 2’s complement addition for the

subtraction operation

Z= X-Y =X + (-Y). Here –Y is assumed as the 2’s complement. In order to avoid the

negative numbers in subtraction, take X>Y and discard Z5.

The addition subtraction processes are combined in a single circuit by using a mode

control. If the mode M=0, then the two 4 bit numbers will get added and if M=1, then the 2’s

complement of second number is added to the first number to perform subtraction.

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

10

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

4 BIT ADDER/ SUBTRACTOR

If, Mode M=0, then Z= X+Y

If, Mode M=1, then Z= X- Y [Assume X >Y]

OBSERVATION:

M=0 X=___________________Y=__________________Z=__________________

M=0 X=___________________Y=__________________Z=__________________

M=1 X=___________________Y=__________________Z=__________________

M=1 X=___________________Y=__________________Z=__________________

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

11

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

PROCEDURE:

1. Test all components and IC packages using multimeter and digital IC tester.

2. Connect the circuit as in diagram

3. Apply two 4 bit numbers X and Y as the inputs.

4. Apply M=0 and verify the sum output at Z=X+Y.

5. Apply X and Y such that X>Y

6. Apply M=1 and verify the difference result Z = X-Y. Discard the value of Z5.

RESULT:

The four bit adder / subtractor circuit is designed and setup using IC-7483 and the

output is verified.

VIVA QUESTIONS:

1. Write down the internal operation of a parallel adder?

2. Design a subtractor to perform X-Y if X < Y.

3. How the speed of addition can be improved?

4. Explain how two bytes are added with adder ICs.

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

12

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

BCD ADDER

If A+B >9, then, the sum is added with 6 (0110) and the result will be 000S5 S4S3S2S1

S4 S3 S2 S1 Y

0 0 0 0 0

0 0 0 1 0

0 0 1 0 0

0 0 1 1 0

0 1 0 0 0

0 1 0 1 0

0 1 1 0 0

0 1 1 1 0

1 0 0 0 0

1 0 0 1 0

1 0 1 0 1

1 0 1 1 1

1 1 0 0 1

1 1 0 1 1

1 1 1 0 1

1 1 1 1 1

Y= CO+S4(S3+S2)

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

13

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Experiment No: 4 Date: …. / …. /…...

BCD ADDER

AIM:

To design and setup a BCD adder using 4 bit binary adder IC-7483.

PRE-REQUISITES

Concept of Binary coded decimals (BCD)

Concept of conversion from binary to BCD

Concept of combining two adders

COMPONENTS AND EQUIPMENTS REQUIRED:

IC-7483

IC-7400

IC-7410

Logic probe

IC Trainer kit

THEORY:

In the BCD addition, if the sum exceeds 9(i.e, 1001), 6 (i.e,0110) must be added to the

result to convert it into BCD number. For this purpose, two 7483 ICs are required. One for

binary addition and the other for the addition of 6. A combinational circuit is setup so that its

output (Y) helps to make B4B3B2B1 (of 2nd IC)= 0110 when S4S3S2S1(of 1st IC) > 1001 or

Co(of 1st IC) =1.

If A+B >9, then, the sum is added with 6 (0110) and the result will be 000S 5 S4S3S2S1.

Since the maximum BCD sum is 18, most significant BCD digit of the sum output needs only

one bit and it is taken from Co as shown in figure.

PROCEDURE:

1. Test all the components and IC packages using multimeter and digital IC testers.

2. Setup BCD adder and verify the result.

RESULT:

Designed and setup a single digit BCD adder using 4-bit binary adder IC 7483

VIVA QUESTIONS:

1. What is BCD?

2. Convert the following numbers to BCD

a. 1100 c. 1111

b. 1010 d. 1001

3. Explain the process of BCD addition of two numbers.

4. Name some applications of BCD numbers.

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

14

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

A) Y = f(A, B, C, D) = ∑m(1, 2, 7 )

Input Output

A B C in Y

0 0 0 0

0 0 1 1

0 1 0 1

0 1 1 0

1 0 0 0

1 0 1 0

1 1 0 0

1 1 1 1

B) FULL ADDER

Input Output

A B C in S C out

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

15

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Experiment No: 5 Date: …. / …. /…...

REALIZATION OF COMBINATIONAL CIRCUITS USING

MULTIPLEXERS

AIM:

To design and set up the following functions using Multiplexer IC

A. Y = f(A, B, C, D) = ∑m(1, 2, 7 )

B. Full Adder

PRE-REQUISITES

Concept of multiplexers and MUX ICs

Concept of Boolean functions.

COMPONENTS AND EQUIPMENTS REQUIRED:

IC-74151

IC trainer kit

THEORY:

Multiplexer

A multiplexer (MUX) or data selector is a logic circuit that accepts several data inputs

and allows only one of them at a time to get through the output. The routing of the desired

data input to the output is controlled by SELECT inputs. The multiplexer acts like a digitally

controlled multiposition switch. The digital code applied to the SELECT inputs determines

which data inputs will be switched to the output. The multiplexer selects 1-out- of- N input

data sources and transmits the selected data to a single output channel. This is called

multiplexing.

Using multiplexers, we can implement any Boolean functions by giving the n inputs as

the selection pins and connecting the corresponding output values to the data inputs. At the

time of one selection, only one output will be available at the output. By combining same

selection to multiple multiplexers, we can set up multi output circuits too.

PROCEDURE:

1. Test the IC and wires

2. Setup the circuit as per the circuit diagram.

3. Apply the inputs as per the truth table

4. Verify the output.

RESULT:

Designed and implemented the given Boolean expressions using MUX and DEMUX.

VIVA QUESTIONS:

1. Compare multiplexer with de-multiplexer based on their applications

2. Derive the Boolean expression for multiplexer and de-multiplexer.

3. Implement an 8:1 MUX using 4:1 MUXs?

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

16

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

SR Flip Flop

Inputs Output

Comments

S R Q n+1

0 0 Qn No change

0 1 0 Reset/clear

1 0 1 Set

1 1 X Indefinite

D Flip Flop

Inputs Output

Comments

D Q n+1

0 0

Same as input

1 1

JK Flip flop

Inputs Output

Comments

J K Q n+1

0 0 𝑄𝑛 No change

0 1 0 Reset/clear

1 0 1 Set

1 1 𝑄𝑛 Toggle

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

17

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Experiment No: 6 Date: …. / …. /…...

FLIP FLOPS USING GATES

AIM:

To realize SR, T, D, JK and JK Master Slave flip-flops using universal gates.

PRE-REQUISITES

Concept of flip flops

Truth tables of flip flops

Concept of using asynchronous inputs

COMPONENTS AND EQUIPMENTS REQUIRED:

IC 7400

7410

IC7474

IC-7473

IC-7476

IC Trainer Kit

THEORY:

Flip Flop is the basic building block in any memory system since its output will remain

in its state until it is forced to change it by some means.

SR Flip Flop

“S” and “R” stands for set and reset respectively. There are four input combinations

possible at the inputs. When S=R=0 the output will remains in its last state. When S=1,R=0 , the

the flip flop will set its output and when S=0, R= 1, then the flip flop will reset. But S=R=1 is

forbidden since the output will be intermediate. When the flip flop switched ON, its output state

will be uncertain. When initial state is to be assigned, two separate inputs called preset and clear

are used.

JK Flip Flop

The intermediate output state of SR-Flip Flop, when S=R=1 is avoided by converting it

into JK flip flop. In this stage the JK flip flop will toggle its output (complement of the last

output). In all other input combinations the functions will be same as in SR flip flop.

MSJK Flip Flop

It consist of clocked JK flip flop as a master and clocked SR flip flop as a slave, the

output of the master flip flop is fed as an input to the slave flip flop. Clock signal is connected

directly to the master flip flop, but it is connected through inverter to the slave flip flop.

Therefore, the information present at the JK input is transmitted to the output of master flip flop

on the positive clock pulse and it is held there until the negative clock pulse occurs, after which it

is allowed to pass through to the output of slave flip flop. Therefore the circuit will work at the

negative edge of the clock pulse. In all of the input conditions the slave copies what the master

does.

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

18

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Master JK Flip Flop

Inputs Output

Comments

J K Q n+1

0 0 𝑄𝑛 No change

0 1 0 Reset/clear

1 0 1 Set

1 1 𝑄𝑛 Toggle

T Flip Flop

Inputs Output

Comments

T Q n+1

0 𝑄𝑛 No change

1 𝑄𝑛 Toggle

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

19

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

In JK=flip flop, when J=K=1, the output will toggle multiple times irrespective of the

clock. This will happen when the clock applied is much higher compared to the total time delay

of the circuit. This phenomenon is called Race around Condition. By using MS JK flip flop, the

race around condition is avoided as the circuit will operate only due to the negative edge of the

clock.

D Flip Flop

It has only one input referred to as D input or delay input. The input data appears at the output

after a clock pulse applied. D flip flop can be derived from a JK flip flop by using J input as the

D input and J is inverted and fed to K input.

T Flip Flop

In T flip flop, T stands for toggle. The output toggles when a clock input is applied.ie output of

the flip flop changes state for an input pulses. T flip flop can derive from JK flip flop by shorting

J and K inputs.

PROCEDURE:

1. Test all components and IC packages using multimeter and digital IC tester.

2. Set up the flip flops using gates and verify their truth tables.

RESULT:

Various flip flops are implemented using NAND gates.

VIVA QUESTIONS:

1. How many bits can be stored in a single flip-flop?

2. Compare edge triggering and level triggering.

3. What is the advantage of Edge triggering over level triggering?

4. What is race-around condition? How can you avoid it?

5. What is the difference between Flip-Flop & latch?

6. Give examples for synchronous & asynchronous inputs?

7. Convert the J K Flip-Flop into D flip-flop and T flip-flop?

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

20

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

SERIAL IN-SERIAL OUT/SERIAL IN- PARALLEL OUT SHIFT REGISTER

OBSERVATION: Data Input:_______________________

RING COUNTER

Clk Q1 Q2 Q3 Q4

0 0 0 0 0

1 1 0 0 0

2 0 1 0 0

3 0 0 1 0

4 0 0 0 1

5 1 0 0 0

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

21

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Experiment No: 7 Date: …. / …. /…...

SHIFT REGISTERS AND COUNTERS

AIM:

To implement

4 bit serial in serial out shift registers

Register counters

o Ring Counter

o Johnson counter

PRE-REQUISITES

Concept of various shift registers

Truth tables and waveforms of register counters

COMPONENTS REQUIRED:

ICs 7473

7408

7432

7476

7474

IC trainer kit.

THEORY:

A register is a group of flip-flops that can be used to store a binary number. Shift

register accepts a binary number and shifts it. The data can be entered to the shift register either

serially or in parallel. Similarly, the output can be taken from it either in serial or in parallel.

Ring counter and Johnson counter are basically shift registers.

Ring counter

The ring counter utilizes one flip-flop for each state in its sequence. As it can be seen

from the truth table, there are four unique output states for this counter, rendering a mode 4 ring

counter. Ring counter is called a divide by N counter where N is the number of flip-flops.

Johnson counter

The modulo number of a ring counter can be doubled by making a small change in the

ring counter circuit. The Q and Q outputs of the last flip-flop are connected to the J and K inputs

of the first flip-flop respectively. This is the Johnson counter. Johnson counter is also called

twisted ring counter or divide by 2N counter.

PROCEDURE:

1. Test all IC packages using digital IC tester.

2. Connect the circuit as per the circuit

3. Apply clock pulses of frequency 1 Hz or provide clock by mono pulser

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

22

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

JOHNSON COUNTER

Clk Q1 Q2 Q3 Q4

0 0 0 0 0

1 1 0 0 0

2 1 1 0 0

3 1 1 1 0

4 1 1 1 1

5 0 1 1 1

6 0 0 1 1

7 0 0 0 1

8 0 0 0 0

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

23

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Shift Register:

1. Clear all flip flops. And keep clear pin at high afterwards

2. Give serial inputs to the first flip flop

3. Observe the propagation of data through the proceeding flip flops

4. Get the serial output from the last flip flop

Ring Counter:

1. Clear all flip flops. And keep clear pin at high afterwards

2. Give separate preset for the first flip flop. Keep it low for a small duration so that the

first flip flop output becomes 1. Immediately return the preset to high.

3. Verify the output as per the truth table.

Johnson Counter:

1. Clear all flip flops. And keep clear pin at high afterwards

2. Observe the output as per the truth table.

RESULT:

Designed and setup 4 bit serial in serial out shift register, 4 bit Ring and Johnson.

VIVA QUESTIONS:

1. Differentiate between shift registers and counters.

2. Give example of a serial in serial out shift register IC.

3. How can a serial in parallel out register be used as a serial in parallel out register?

4. Give an application of a shift register.

5. How can a shift register be used to count a binary number by 2?

6. How can a shift register be used to divide a binary number by 2?

7. What is the delay introduced by a SISO shift register to an applied digital signal?

8. What is the basic difference between a Ring counter and Johnson counters?

9. What is a twisted ring counter?

10. How many states are there in an N stage Johnson counter?

11. How many states are there in an N stage Ring counter?

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

24

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

4 BIT UP COUNTER

Clk Q4 Q3 Q2 Q1

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

10 1 0 1 0

11 1 0 1 1

12 1 1 0 0

13 1 1 0 1

14 1 1 1 0

15 1 1 1 1

16 0 0 0 0

3 BIT UP/DOWN COUNTER

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

25

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Experiment No: 8 (a) Date: …. / …. /…...

ASYNCHRONOUS COUNTERS

AIM:

To implement the following asynchronous counters and study their working

4 bit Up counter

3 bit up/down counter

Mod-10 (Decade) counter

PRE-REQUISITES

Concept of asynchronous counters

Concept of clocks

Concept of Mod-N counters

COMPONENTS AND EQUIPMENTS REQUIRED:

IC 7476

IC 7400

IC trainer kit.

THEORY:

A counter is a register capable of counting the number of clock pulses arriving at its

clock inputs. In asynchronous counters the flip-flops within the counter are not made to change

states at exactly the same time, here the clock pulses are not connected directly to the C input of

each flip-flop in the counter.

In asynchronous counters, commonly called ripple counters, the first flip flop is

clocked by the external clock pulses and each successive flip flop is clocked by the Q or Q’

output of the previous flip flop.

Three bit up/down counter

The direction of the counting sequence is made dependent on a mode control input. A logic

circuit connected between flip flops does a mere job of connecting either Q or Q! output of the

previous flip flops to the clock input of the succeeding flip flops.

Decade up counter

The circuit of the decade counter is similar to 4 bit ripple counter but with the aid of a

logic circuit called decoder, the count is limited to 9. As soon as the state 1010 reaches, the

decoder using NAND gates detects the presence of 1010 and generates a signal which is used to

clear all the flip flops. Then the counter is restarts from 0.

PROCEDURE:

1. Test all ICs using digital IC tester. Test all wires for continuity using multimeter.

2. Set up the circuit for 4 bitripple counter. Connect all PRESET pins to +5V to disable it.

3. Tie up all CLEAR pins together.

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

26

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

3 BIT UP/ DOWN COUNTER-Truth Table

Clk M Q3 Q2 Q1

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 0 0 0 0

9 1 1 1 1

10 1 1 1 0

11 1 1 0 1

12 1 1 0 0

13 1 0 1 1

14 1 0 1 0

15 1 0 0 1

16 1 0 0 0

DECADE COUNTER / MOD-10 COUNTER

Clk Q4 Q3 Q2 Q1

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

10 0 0 0 0

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

27

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

4. Use monopulse /debouncer to feed the clock manually.

5. Clear all flip-flops initially, by connecting common CLEAR to logic low input. After

the usage of CLEAR pins, keep it open.

6. Apply mono-pulses. Counter starts counting up.

7. Move clock inputs of every flip-flop except FF0 from outputs to the Q outputs. Preset all

flip-flops. Apply mono-pulses. Counter will start counting down.

8. Set up the circuit for decade counter and repeat steps for counting down.

9. Set up 3 bit up/down counter and observe the up counting when the mode control is 1

and down counting when mode control is 0.

RESULT:

Designed and set up the following asynchronous counters

4 bit binary up counter

4 bit binary down counter

3 bit binary up / down counter

Decade counter

VIVA QUESTIONS:

1. What is the difference between a synchronous counter and an asynchronous counter?

2. What is the primary disadvantage of an asynchronous counter?

3. How many flip-flops are required to construct a mod-N counter?

4. What is meant by lock-out?

5. What is an asynchronous counter?

6. How is it different from a synchronous counter?

7. Realize asynchronous counter using T flip-flop

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

28

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

4 BIT UP COUNTER

PRESENT STATE NEXT STATE J K FLIP FLOP INPUTS

𝑸𝟑 𝑸𝟐 𝑸𝟏 𝑸𝟎 𝑸𝟑 𝑸𝟐 𝑸𝟏 𝑸𝟎 𝑱𝟎 𝑲𝟎 𝑱𝟏 𝑲𝟏 𝑱𝟐 𝑲𝟐 𝑱𝟑 𝑲𝟑

0 0 0 0 0 0 0 1 1 X 0 X 0 X 0 X

0 0 0 1 0 0 1 0 X 1 1 X 0 X 0 X

0 0 1 0 0 0 1 1 1 X X 0 0 X 0 X

0 0 1 1 0 1 0 0 X 1 X 1 1 X 0 X

0 1 0 0 0 1 0 1 1 X 0 X X 0 0 X

0 1 0 1 0 1 1 0 X 1 1 X X 0 0 X

0 1 1 0 0 1 1 1 1 X X 0 X 0 0 X

0 1 1 1 1 0 0 0 X 1 X 1 X 1 1 X

1 0 0 0 1 0 0 1 1 X 0 X 0 X X 0

1 0 0 1 1 0 1 0 X 1 1 X 0 X X 0

1 0 1 0 1 0 1 1 1 X X 0 0 X X 0

1 0 1 1 1 1 0 0 X 1 X 1 1 X X 0

1 1 0 0 1 1 0 1 1 X 0 X X 0 X 0

1 1 0 1 1 1 1 0 X 1 1 X X 0 X 0

1 1 1 0 1 1 1 1 1 X X 0 X 0 X 0

1 1 1 1 0 0 0 0 X 1 X 1 X 1 X 1

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

29

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Experiment No: 8 (b) Date: …. / …. /…...

SYNCHRONOUS COUNTERS

AIM:

To implement

4 bit up counter

4 bit down counter

PRE-REQUISITES

Concept of state tables

Concept of excitation tables

K Map simplification.

COMPONENTS AND EQUIPMENT REQUIRED:

IC-7476

IC-7408

IC Trainer Kit

THEORY:

Synchronous and asynchronous counters provide same outputs. The difference is that

in the synchronous counters all flip flops work in synchronism with the input clock pulse.

That means the output of all the flip flops in the counter change state at the same instant.

Therefore the Propagation delay occurring in asynchronous counter is eliminated in

synchronous counters. Synchronous counters for given count sequence or modulus can be

designed and set up by the following procedure.

1. Find the number of flip flop using the relation M=2N, Where M is the modulus of the

counter and N is the minimum number of flip flops required.

2. That is N=log2 M.

3. Write down the count sequence (FF outputs) in the tabular form.

4. Determine the flip flop inputs which must be present for the desired next sate using

excitation table.

5. Prepare K- maps for each flip flop input in terms of flip flop outputs as the input

variable. Obtain the minimized expression from the K-map.

6. Setup the circuit using flip flops and other gates

PROCEDURE:

1. Test all the components using digital IC tester.

2. Set up the circuit one by one and verify the counter states.

3. Clear all the flip flops by resetting clear pin.

4. Set clear pin and apply a clock frequency of 1Hz square pulse or apply pulses using

mono pulsar from the IC trainer kit.

5. Verify the output from the LED status.

RESULT:

Designed and set up a 4 bit synchronous counter using JK flip flops.

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

30

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

3 BIT UP/DOWN COUNTER

PRESENT NEXT

J K FLIP FLOP INPUTS

STATE STATE

MODE 𝑸𝟐 𝑸𝟏 𝑸𝟎 𝑸𝟐 𝑸𝟏 𝑸𝟎 𝑱𝟎 𝑲𝟎 𝑱𝟏 𝑲𝟏 𝑱𝟐 𝑲𝟐

0 0 0 0 0 0 1 1 X 0 X 0 X

0 0 0 1 0 1 0 X 1 1 X 0 X

0 0 1 0 0 1 1 1 X X 0 0 X

0 0 1 1 1 0 0 X 1 X 1 1 X

0 1 0 0 1 0 1 1 X 0 X X 0

0 1 0 1 1 1 0 X 1 1 X X 0

0 1 1 0 1 1 1 1 X X 0 X 0

0 1 1 1 0 0 0 X 1 X 1 X 1

1 1 1 1 1 1 0 X 1 X 0 X 0

1 1 1 0 1 0 1 1 X X 1 X 0

1 1 0 1 1 0 0 X 1 0 X X 0

1 1 0 0 0 1 1 1 X 1 X X 1

1 0 1 1 0 1 0 X 1 X 0 0 X

1 0 1 0 0 0 1 1 X X 1 0 X

1 0 0 1 0 0 0 X 1 0 X 0 X

1 0 0 0 1 1 1 1 X 1 X 1 X

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

31

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

QUESTIONS:

1. What are synchronous counters?

2. What are the advantages of synchronous counters?

3. What is an excitation table?

4. Write the excitation table for D, T FF

5. Design mod-5 synchronous counter using T FF

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

32

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

4 BIT UP COUNTER

Clk Q3 Q2 Q1 Q0

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

10 1 0 1 0

11 1 0 1 1

12 1 1 0 0

13 1 1 0 1

14 1 1 1 0

15 1 1 1 1

16 0 0 0 0

DECADE COUNTER

Clk Q3 Q2 Q1 Q0

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

10 0 0 0 0

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

33

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Experiment No: 9 Date: …. / …. /…...

COUNTER ICs

AIM:

To implement

4 bit up counter

Decade counter

-using counter ICs

PRE-REQUISITES

Concept of counter ICs

Concept of connecting clocks and asynchronous inputs to the IC

COMPONENTS AND EQUIPMENTS REQUIRED:

IC-7493, IC 7400, IC 7408, Digital IC Trainer kit

THEORY:

IC-7493

The logic diagram of 7493 and DIP pin out of 7493 IC are shown in the figure. This

TTL MSI circuit is a 4 bit binary counter that can be used in either a mode 8 or mode16

configuration.

If the clock is applied at input A and QA is connected to input B it behaves as a

mode16, 4 bit binary ripple counter. Internally there is one mode 2 counter and a mode 8

counter in cascade. The outputs are QA, QB, QC and QD.

If the clock is applied at input B, the output will appear at QB, QC & QD. It thus behaves as

a mod 8 counter. In this case, flip flop QA is not used. A high level at both R0(1) and R0(2)

will make all flip flops reset.

PROCEDURE:

1. Test the IC packages and all components using multimeter and digital IC tester.

2. Setup the counter circuits on the trainer kit.

3. Verify the working of counters and their truth tables.

RESULT:

The two IC’s 7493 and 7490 was studied and truth tables were verified.

VIVA QUESTIONS:

1. How many flip-flops are required to make a MOD-32 binary counter?

2. How an up/down counter is set up using counter ICs?

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

34

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

SEQUENCE GENERATOR

Q2 Q1 Q0 Y

0 0 0 1

0 0 1 0

0 1 0 1

0 1 1 1

1 0 0 0

1 0 1 X

1 1 0 X

1 1 1 X Y= Q1+𝑄2 𝑄0

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

35

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Experiment No: 10 Date: …. / …. /…...

SEQUENCE GENERATOR

AIM:

To design a counter to generate the sequence 10110

PRE-REQUISITES

Concept of asynchronous sequential design.

COMPONENTS AND EQUIPMENTS REQUIRED:

IC 7474

IC 7400

THEORY:

Sequence generator is a sequential circuit which will generate a random sequence of data

or states. The sequence may be of indefinite length or of predetermined fixed length. Sequence

generators can be prepared by using the method of designing synchronous counters with the

random order of states and its corresponding next states. There is one other method to design the

sequence generator as asynchronous design, which is a simpler one. Here the counting will be

cleared after the required number of states. And the sequence is designed with the help of a truth

table. Sequence generators are useful in a wide variety of coding and control applications.

PROCEDURE:

1. Test all the components using digital IC tester.

2. Set up the circuit one by one and verify the counter states.

3. Clear all the flip flops by resetting clear pin.

4. Set clear pin and apply a clock frequency of 1Hz square pulse or apply pulses using

mono pulsar from the IC trainer kit.

5. Verify the output from the LED status.

VIVA QUESTIONS:

1. What is the necessity for sequence generation?

2. What are PISO, SIPO, and SISO with respect to shift register?

3. Differentiate between serial data & parallel data

4. What is the significance of Mode control bit?

5. What is a ring counter?

6. What is a Johnson counter?

7. How many Flip-flops are present in IC 7495?

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

36

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

4 BIT ADDER/ SUBTRACTOR

If, Mode M=0, then Z= X+Y

If, Mode M=1, then Z= X- Y [AssumeX >Y]

Master JK Flip Flop

Inputs Output

Comments

J K Q n+1

0 0 Qn No change

0 1 0 Reset/clear

1 0 1 Set

1 1 Q’ n Toggle

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

37

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Experiment No: 11 Date: …. / …. /…...

SIMULATION OF DIGITAL CIRCUITS- COMBINATIONAL AND

SEQUENTIAL CIRCUITS

AIM:

To design and simulate

Adder/Subtractor circuits

JK Master Slave flip-flops using gates

Shift register

UP/DOWN Counter

Arbitrary Sequence Generator

COMPONENTS AND EQUIPMENTS REQUIRED:

Circuit wizard software

THEORY:

Electronic circuit simulation uses mathematical models to replicate the behavior of an

actual electronic device or circuit. Simulation software allows for modeling of circuit operation

and is an invaluable analysis tool. Simulating a circuit’s behavior before actually building it can

greatly improve design efficiency by making faulty designs known as such, and providing insight

into the behavior of electronics circuit designs.

Circuit Wizard is a revolutionary new system that combines circuit design, PCB design,

simulation and CAD/CAM in one complete package. Circuit Wizard provides us with all the

tools necessary to produce an electronics project from start to finish – even including on-screen

testing of the PCB prior to construction.

PROCEDURE:

1. Open circuit wizard.

2. Select components from gallery

3. Arrange and connect components

4. Apply input and connect output components

5. Run the simulation

6. Verify truth tables

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

38

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

SERIAL IN-SERIAL OUT/SERIAL IN- PARALLEL OUT SHIFT REGISTER

3 BIT UP/DOWN COUNTER

SEQUENCE GENERATOR TO GENERATE THE SEQUENCE 10110

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

39

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

RESULT:

The outputs and waveform were observed and compared with the designed theoretical

results

VIVA QUESTIONS:

1. Simulate a code converter using circuit wizard.

2. Explain how the asynchronous inputs are used in simulation

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

40

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

INTERNAL DIAGRAM OF 555 TIMER IC

ASTABLE MULTIVIBRATOR

Design:

Take VCC = 10 V and t c=1 ms and t d = 0.5 ms

We have t c =0.69 R1 + R 2 C and t d =0.69R A C

The R1 and R 2 should be in the range of 1K to 10 K to limit collector current of internal resistor

Take R1 = R 2 = 6.8𝐾

Let C=0.1μF, 𝐶𝑖 =0.01 μF

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

41

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Experiment No: 12 Date: …. / …. /…...

ASTABLE AND MONOSTABLE MULTIVIBRATOR CIRCUITS USING

555 IC

AIM:

To design an Astable and Monostable Multivibrator using IC555 and compare it‟s

theoretical and practical pulse width.

PRE-REQUISITES

Block diagram of 555 IC

Working of 555 IC

COMPONENTS AND EQUIPMENTS REQUIRED:

Bread Board.

Connecting wires

555 Timer,

Resistors,

Capacitors,

IC trainer Kit

THEORY:

Monostable multivibrator is also called as one–shot Multivibrator. When the output is

low, the circuit is in stable state, transistor T1 is ON and Capacitor C is shorted to the ground.

However, upon application of a negative trigger pulse to Pin–2, transistor T1 is turned OFF,

which releases short circuit across the external capacitor and drives the output High. The

capacitor C now starts charging up toward VCC through R. However when the voltage across the

external capacitor equals 2/3 VCC, upper comparator’s output switches from low to high which

in turn derives the output to its low state. And the output of the flip flop turns transistor T1 ON,

and hence the capacitor C rapidly discharges through the transistor. The output of the Monostable

remains low until a trigger pulse is again applied. Then the cycle repeats. The time during which

the output remains high is given by tp = 1.1 RC

Once triggered, the circuit’s output will remain in the high state until the set time tp

elapses. The output will not change its state even if an input trigger is applied again during this

time interval tp.

In the 555 Oscillator above, pin 2 and pin 6 are connected together allowing the circuit to

retrigger itself on each and every cycle allowing it to operate as a free running oscillator. During

each cycle capacitor, C charges up through both timing resistors, R1 and R2 but discharges itself

only through resistor, R2 as the other side of R2 is connected to the discharge terminal, pin 7.

Then the capacitor charges up to 2/3Vcc (the upper comparator limit) which is determined by the

0.693(R1+R2)C combination and discharges itself down to 1/3Vcc (the lower comparator limit)

determined by the 0.693(R2.C) combination. This results in an output waveform whose voltage

level is approximately equal to Vcc - 1.5V and whose output "ON" and "OFF" time periods are

determined by the capacitor and resistors combinations. The individual times required

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

42

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

MONOSTABLE MULTIVIBRATOR

Design:

Take 𝑉𝑐𝑐 = 10 V and T=1ms

T=1.1RC

R=10 K to limit current through internal transistor to 1 mA

Then C=0.1 μF

Design of triggering circuits

𝑅𝑖 𝐶𝑖 ≤0.0016𝑇𝑡 , where 𝑇𝑡 is the time period of trigger

𝑅𝑖 =5.6 K to avoid loading

𝑇𝑡 = 3 ms, 𝐶𝑖 =0.1 μF, 𝐶1 =0.1 μF

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

43

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

completing one charge and discharge cycle of the output is therefore given as: t1 = 0.693

(R1+R2)C, t2 = 0.693 R2C, T = t1 + t2

PROCEDURE:

1. Connect the components/equipment as shown in the circuit diagram.

2. Switch ON the power supply.

3. Connect function generator at the trigger input.

4. Connect channel-1 of CRO to the trigger input and channel-2 of CRO to the output (Pin

3).

5. Using Function Generator, apply 1 KHz square wave with amplitude of approx. equal to 9

Vpp at the trigger input.

6. Observe the output voltage with respect to input and note down the pulse width and

amplitude.

7. Now connect channel-2 of CRO across capacitor and observe the voltage across the

capacitor and note it down.

8. Compare the practical pulse width noted in the step above with its theoretical value

(tp=1.1 RC)

RESULT:

The waveform was traced and compared with the designed theoretical one.

Viva questions:

1. What is the other name for monostable multivibrator (MSMV)?

2. When MSMV is in stable state, what is the output level?

3. Why trigger is required in the case of MSMV?

4. Which type of trigger pulse is required for MSMV?

5. What is the formula for the output pulse width of MSMV?

6. How long MSMV stays in unstable state?

7. What are the different types of multivibrator circuits?

8. What is the disadvantage of an astable multivibrator?

9. How does a monostable multivibrator work in terms of the astable multivibrator?

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

44

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

4 BIT BINARY TO GRAY CODE

BINARY GRAY

B3 B2 B1 B0 G3 G2 G1 G0

0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 1

0 0 1 0 0 0 1 1

0 0 1 1 0 0 1 0

0 1 0 0 0 1 1 0

0 1 0 1 0 1 1 1

0 1 1 0 0 1 0 1

0 1 1 1 0 1 0 0

1 0 0 0 1 1 0 0

1 0 0 1 1 1 0 1

1 0 1 0 1 1 1 1

1 0 1 1 1 1 1 0

1 1 0 0 1 0 1 0

1 1 0 1 1 0 1 1

1 1 1 0 1 0 0 1

1 1 1 1 1 0 0 0

3 BIT BINARY TO GRAY / GRAY TO BINARY CODE CONVERTER USING MODE

CONTROL

MODE INPUT OUTPUT

M D2 D1 D0 Y2 Y1 Y0

0 0 0 0 0 0 0

0 0 0 1 0 0 1

0 0 1 0 0 1 1

0 0 1 1 0 1 0

0 1 0 0 1 1 0

0 1 0 1 1 1 1

0 1 1 0 1 0 1

0 1 1 1 1 0 0

1 0 0 0 0 0 0

1 0 0 1 0 0 1

1 0 1 0 0 1 1

𝑌0 = 𝑀𝐷2 ⊕ 𝐷1 ⊕ 𝐷0 1 0 1 1 0 1 0

1 1 0 0 1 1 1

1 1 0 1 1 1 0

1 1 1 0 1 0 0

1 1 1 1 1 0 1

𝑌1 = 𝐷1 ⊕ 𝐷0 𝑌2 = 𝐷2

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

45

AI 14 408(P): DIGITAL ELECTRONICS LAB MANUAL

Experiment No: 13 Date: …. / …. /…...

CODE CONVERTERS- CONTENT BEYOND SYLLABUS

AIM:

To design and set up the following circuits.

1. A 4 bit Binary to Gray code converter.

2. A 3 bit Binary to Gray / Gray to Binary code converter using mode control.

COMPONENTS AND EQUIPMENTS REQUIRED:

ICs 7486, 7408, and IC trainer kit.

THEORY:

To convert a binary number to corresponding Gray code, the following rules are

applied.

1. The MSB in the Gray code is the same as the corresponding bit in the binary number.

2. Going from left to right, add each adjacent pair of binary digits to get the next gray code

digit. Disregard carries.

As the first step to design a binary to gray code converter, set up a truth table with

binary numbers B3,B2,B1,B0 and corresponding gray code numbers G3, G2,G1,G0. Set up a

circuit realizing the simplified logic expressions obtained using K - maps for Gs as the functions

of Bs.

To convert from Gray code to Binary the following rules are applied.

1. The MSB in the binary number is the same as the corresponding digit in the gray code.

2. Add each binary digit generated to the gray code digit in the next adjacent position.

Disregard carries

To design the Binary to BCD code converter, set up the truth table and gets simplified

expression using Karnaugh maps for each binary bit as a function of Gray code bits. Each Gray

code number differs from the preceding number by a single bit.

PROCEDURE:

1. Test all the components and IC packages using multimeter and digital IC tester.

2. Verify the truth tables of the circuit by feeding the input bit combinations.

Result:

Designed and set up various types of code converters.

Viva Questions:

1. Convert the given gray code to binary using ex-or gate 11000

2. What are code converters?

3. What is gray code?

4. Obtain the Boolean expression for Y0, Y1, Y2 for Binary to Gray/ Gray to Binary code

converter

5. Realize the Boolean expressions for

a) Binary to gray code conversion

b) Gray to binary code conversion

Department of Applied Electronics & Instrumentation Engineering RCET, Akkikkavu

You might also like

- Operator Manual: Inmode™ System With Lumecca™ 515 & 580 HandpieceDocument44 pagesOperator Manual: Inmode™ System With Lumecca™ 515 & 580 HandpieceevgenNo ratings yet

- 21EE303 DSD Lab Manual 1Document43 pages21EE303 DSD Lab Manual 1Bharatesha Gouda M PatilNo ratings yet

- Logic GatesDocument6 pagesLogic GatesMehar GuptaNo ratings yet

- DLD Lab ManualDocument48 pagesDLD Lab ManualShilpa PandeyNo ratings yet

- Logic Circuit Design Lab Manual1 - 2 PDFDocument61 pagesLogic Circuit Design Lab Manual1 - 2 PDFAkhil Kumar SNo ratings yet

- Digital Design and HDL Lab Manual - MergedDocument55 pagesDigital Design and HDL Lab Manual - MergedInstructor KoNo ratings yet

- DSD Exp 1Document8 pagesDSD Exp 1shylaja9No ratings yet

- DT Ica Booklet Final 2024-25 Sem-I With BorderDocument67 pagesDT Ica Booklet Final 2024-25 Sem-I With BorderAvinash HaraleNo ratings yet

- Experiment 1Document10 pagesExperiment 1Hamza AhmedNo ratings yet

- DIGITAL SYSTEM DESIGN LAB MitaliDocument69 pagesDIGITAL SYSTEM DESIGN LAB MitaliMitali JawaNo ratings yet

- Digital Systems and Signals Lab Manual - 2018Document25 pagesDigital Systems and Signals Lab Manual - 2018ram kumarNo ratings yet

- Bca I Semester Subject Code: BCA-104P ELECTRONICS: Laboratory ManualDocument24 pagesBca I Semester Subject Code: BCA-104P ELECTRONICS: Laboratory ManualGamplayNo ratings yet

- 220644-663-666-DLD-Lab#1 (00Document18 pages220644-663-666-DLD-Lab#1 (00Muhammad HamzaNo ratings yet

- DD Lab ManualDocument12 pagesDD Lab ManualKothapalli Likhith Sri SaiNo ratings yet

- Digital Electronic WorksDocument53 pagesDigital Electronic WorksLove GodboleNo ratings yet

- DSD Lab ManualDocument80 pagesDSD Lab Manual22051774No ratings yet

- Logic Design Lab ManualDocument45 pagesLogic Design Lab ManualPrerna GuptaNo ratings yet

- Deld (Ar20) WovDocument96 pagesDeld (Ar20) WovShankarNo ratings yet

- ExperimentDocument5 pagesExperimentRANA RAMEEZNo ratings yet

- List of Experiments: DDVHDLDocument52 pagesList of Experiments: DDVHDLsiri.pogulaNo ratings yet

- Recent PHD ResultDocument72 pagesRecent PHD ResultSavita Kiran BNo ratings yet

- Lab Report DraftDocument2 pagesLab Report Draftyubraj belbaseNo ratings yet

- Hardware Lab-I: (CS-217) Instruction ManualDocument36 pagesHardware Lab-I: (CS-217) Instruction Manualmaen2009No ratings yet

- Modified DLD Lab ManualsDocument40 pagesModified DLD Lab ManualsASHEESH TiwariNo ratings yet

- Lab 1 - Portes LogiquesDocument18 pagesLab 1 - Portes Logiquesnoe finaritra RandriambolaNo ratings yet

- Air University: Lab Title: Basic Logic Gates and Verification of Their Truth TablesDocument18 pagesAir University: Lab Title: Basic Logic Gates and Verification of Their Truth TablesMuhammad Hamza AminNo ratings yet

- Verification of Gates Experimaent: Digital Logic Design Lab ManualDocument5 pagesVerification of Gates Experimaent: Digital Logic Design Lab ManualRana jamshaid Rana jamshaidNo ratings yet

- Modified Mlrit20 DSD Lab ManualDocument46 pagesModified Mlrit20 DSD Lab ManualBantu SandeepNo ratings yet

- Exp3 Universal Gates 1Document23 pagesExp3 Universal Gates 1Joie Marie Yadao BulawanNo ratings yet

- Logic Circuit Long ReportDocument9 pagesLogic Circuit Long ReportSirenjeevi RaoNo ratings yet

- Ali - LAB 01Document5 pagesAli - LAB 01Ali RazaNo ratings yet

- Lab Report 2: Digital Logic Design LabDocument5 pagesLab Report 2: Digital Logic Design LabRaja SaadNo ratings yet

- Lab-1 DLDDocument9 pagesLab-1 DLDdatamass14No ratings yet

- Preboard Practical Exam Electronics 2-Converted-Converted For StudentsDocument14 pagesPreboard Practical Exam Electronics 2-Converted-Converted For StudentsRounak PagareNo ratings yet

- DLD ManualDocument34 pagesDLD ManualmkollamNo ratings yet

- Lab 10 2022 2Document4 pagesLab 10 2022 2CuongNo ratings yet

- Dpco Lab ManuaDocument54 pagesDpco Lab ManuaHANISHA SAALIHNo ratings yet

- DLD - LAB - MANUAL - New - Verilog Spring 2017 PDFDocument48 pagesDLD - LAB - MANUAL - New - Verilog Spring 2017 PDFAli RaoNo ratings yet

- Lab Report 1 Digital SystemDocument8 pagesLab Report 1 Digital Systemmuhammad adibuddinNo ratings yet

- Laboratory Manual: College of Engineering, OsmanabadDocument39 pagesLaboratory Manual: College of Engineering, OsmanabadJaideep SinghNo ratings yet

- EE8461-Linear and Digital Integrated Circuits-Lab Manual PDFDocument95 pagesEE8461-Linear and Digital Integrated Circuits-Lab Manual PDFmuthu Krishnan0% (1)

- EE8461-Linear and Digital Integrated Circuits-Lab ManualDocument96 pagesEE8461-Linear and Digital Integrated Circuits-Lab ManualSETNHILNo ratings yet

- Digital Logic Design Lab FileDocument44 pagesDigital Logic Design Lab FileKiranmai KonduruNo ratings yet

- Digital III B.SC Practical MaterialDocument29 pagesDigital III B.SC Practical Materialtamilsrm003No ratings yet

- EC Lab4 202211008 MergedDocument78 pagesEC Lab4 202211008 Mergedmexodic205No ratings yet

- Simulation Manual PHY340Document12 pagesSimulation Manual PHY340aisyahNo ratings yet

- DEC Lab ManualDocument87 pagesDEC Lab ManualShashidhara H RNo ratings yet

- COA AktuDocument14 pagesCOA AktuIndexNo ratings yet

- Digital Electronics LaboratoryDocument30 pagesDigital Electronics LaboratoryrahulsportyNo ratings yet

- Lab - Manual - DIGITAL LOGIC GATESDocument38 pagesLab - Manual - DIGITAL LOGIC GATESMinh SơnNo ratings yet

- Lab Manual EC AllDocument383 pagesLab Manual EC Allanshuj11No ratings yet

- STLD Lab ExperimentsDocument30 pagesSTLD Lab Experimentslokesh krapaNo ratings yet

- 2303a51649 DL Document For Assignmnet-1Document16 pages2303a51649 DL Document For Assignmnet-1rangarajulokesh77No ratings yet

- Digital Microprocessor Lab Manual 5th SemDocument26 pagesDigital Microprocessor Lab Manual 5th SemRonit ChowdhuryNo ratings yet

- RIVERA Logics - Lab 8Document5 pagesRIVERA Logics - Lab 8Ricardo Edrell RiveraNo ratings yet

- Decodere and Ncoder: ObjectivesDocument3 pagesDecodere and Ncoder: ObjectivesIqea janNo ratings yet

- TTL Logic Gates Lecture NotesDocument33 pagesTTL Logic Gates Lecture NotesDevenderNo ratings yet

- Co Lab ManualDocument81 pagesCo Lab ManualShiva KumarNo ratings yet

- Digital Electronics ManualDocument49 pagesDigital Electronics ManualPratik SinghNo ratings yet

- Rab Alat Jurusan Animasi PDFDocument3 pagesRab Alat Jurusan Animasi PDFdhuana putriNo ratings yet

- For Various Models of LPS. Many Connectors Are Not Named So We Used This Tools Labeling SchemaDocument1 pageFor Various Models of LPS. Many Connectors Are Not Named So We Used This Tools Labeling Schemajeni1086No ratings yet

- Uln 2003Document7 pagesUln 2003CésarAugustoVegaNo ratings yet

- NGD15N41CL, NGB15N41CL, NGP15N41CL Ignition IGBT 15 Amps, 410 VoltsDocument11 pagesNGD15N41CL, NGB15N41CL, NGP15N41CL Ignition IGBT 15 Amps, 410 Voltsmarino246No ratings yet

- SIPROTEC 5 - Configuration: Technical DataDocument7 pagesSIPROTEC 5 - Configuration: Technical DataEuler Moraes dos Reis JuniorNo ratings yet

- Pricelist HagerDocument30 pagesPricelist HagerSeptian CahyanaNo ratings yet

- Intro SynchDocument21 pagesIntro SynchMohamed RashidNo ratings yet

- Takeoff Edu Group Electrical Title ListDocument202 pagesTakeoff Edu Group Electrical Title Listsyed saifullaNo ratings yet

- Chapter 1 Thermal SensorsDocument20 pagesChapter 1 Thermal SensorsAzizIkramNo ratings yet

- Asco Rail WparameterDocument6 pagesAsco Rail WparameterRicardo Escudero VinasNo ratings yet

- LDK DS 185P-24(s) Value EN V3 120817Document2 pagesLDK DS 185P-24(s) Value EN V3 120817doly damanikNo ratings yet

- Arjuna Jee MathematicsModule 02Document24 pagesArjuna Jee MathematicsModule 02Sandip GhoshNo ratings yet

- Per Unit System Practice Problem Solved TransformersDocument11 pagesPer Unit System Practice Problem Solved TransformersdjebienNo ratings yet

- Maytag Neptune Motor TestDocument1 pageMaytag Neptune Motor TestSamurai Appliance Repair ManNo ratings yet

- SACAL, Aljean Paul BarocolDocument30 pagesSACAL, Aljean Paul BarocolJohn Paul DaliopacNo ratings yet

- Shenzhen Bright Technology: UV LED QuotationDocument2 pagesShenzhen Bright Technology: UV LED QuotationCezarNo ratings yet

- DM00628 QUALITROL QTMS-BM Commissioning ManualDocument26 pagesDM00628 QUALITROL QTMS-BM Commissioning Manualijan jansNo ratings yet

- 1SVR427035R0000 CP e 24 10 0Document4 pages1SVR427035R0000 CP e 24 10 0אלירן סויסהNo ratings yet

- F343i Bazzaz Fi InstructionsDocument5 pagesF343i Bazzaz Fi InstructionsMiltonNo ratings yet

- Microcontrollers From Assembly Language To C Using The Pic24 Family 1st Edition Reese Robert B Bruce J W Jones Bryan ADocument70 pagesMicrocontrollers From Assembly Language To C Using The Pic24 Family 1st Edition Reese Robert B Bruce J W Jones Bryan Adebmdroon413100% (7)

- Lesson 5 - Infomation SheetDocument11 pagesLesson 5 - Infomation SheetAlfie LariosaNo ratings yet

- Autrosafe4 PannelsDocument21 pagesAutrosafe4 Pannelsy2zyrkxssgNo ratings yet

- Lesson 3 Safety PrecautionsDocument4 pagesLesson 3 Safety PrecautionsryekeaanNo ratings yet

- A6V11396485 enDocument4 pagesA6V11396485 enالحمزة الراويNo ratings yet

- (TW-P6-F16) - Testing Comm. of Fire Alarm SystemDocument5 pages(TW-P6-F16) - Testing Comm. of Fire Alarm SystemGlames WilliamsNo ratings yet

- Lecture-3 Scales PDFDocument29 pagesLecture-3 Scales PDFkiran kumarNo ratings yet

- German Solar Panel Monocrystalline 300Wp - ASM6610M - Premium - PHILERGY German SolarDocument2 pagesGerman Solar Panel Monocrystalline 300Wp - ASM6610M - Premium - PHILERGY German SolarJohn Joshua UyNo ratings yet

- Ceiling Microphone Array Ds EnusDocument2 pagesCeiling Microphone Array Ds EnusTaryar OoNo ratings yet

- KC 62133-2-제정고시 제2020-0138호 (2020.07.21.)Document52 pagesKC 62133-2-제정고시 제2020-0138호 (2020.07.21.)on.insight1829No ratings yet