Professional Documents

Culture Documents

S1F76610 Series CMOS DC/DC Converter (Voltage Doubler / Tripler) & Voltage Regulator

S1F76610 Series CMOS DC/DC Converter (Voltage Doubler / Tripler) & Voltage Regulator

Uploaded by

AndyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

S1F76610 Series CMOS DC/DC Converter (Voltage Doubler / Tripler) & Voltage Regulator

S1F76610 Series CMOS DC/DC Converter (Voltage Doubler / Tripler) & Voltage Regulator

Uploaded by

AndyCopyright:

Available Formats

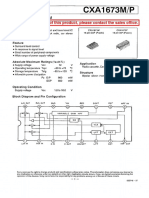

S1F76610 Series

S1F76610 Series CMOS DC/DC Converter (Voltage

Doubler / Tripler) & Voltage Regulator

DESCRIPTION

The S1F76610 Series is a highly effecient CMOS DC/ • External shut-down control

DC converter for doubling or tripling an input voltage. • 2µA maximum output current when shut-down

It incorporates an on-chip voltage regulator to ensure • Two-in-series configuration doubles negative output

stable output at the specified voltage. The S1F76610 voltage.

S1F76610

• On-chip RC oscillator

Series

Series offers a choice of three, optional temperature

gradients for applications such as LCD panel power • S1F76610C0B0 ...... Plastic DIP-14 pin

supplies. S1F76610M0B0 ...... Plastic SOP5-14 Pin

The S1F76610C0B0 is available in 14-pin plastic DIPs, S1F76610M2B0 ...... Plastic SSOP2-16 pin

the S1F76610M0B0, in 14-pin plastic SOPs, and the APPLICATIONS

S1F76610M2B0 in 16-pin plastic SSOPs.

• Power supplies for LCD panels

• Fixed-voltage power supplies for battery-operated

FEATURES equipment

• 95% (Typ.) conversion efficiency • Power supplies for pagers, memory cards, calculators

• Up to four output voltages, VO, relative to the input and similar hand-held equipment

voltage, VI • Fixed-voltage power supplies for medical equipment

• On-chip voltage regulator • Fixed-voltage power supplies for communications

• 20mA maximum output current at VI = –5V equipment

• Three temperature gradients : –0.1, –0.4 and –0.6%/ • Power supplies for microcomputers

°C • Uninterruptable power supplies

BLOCK DIAGRAM

VDD

OSC1 CR

oscilator

OSC2

TC1

Reference Temperature

VI voltge gradient

generator selector TC2

CAP1– Voltage

multiplier

CAP1+ (1)

CAP2– POFF

RV

Voltage Voltage regulator

CAP2+ multiplier VREG

(2)

VO

Multiplication Stabilization

stage stage

S1F70000 Series EPSON 2–1

Technical Manual

S1F76610 Series

PIN ASSIGNMENTS

CAP+ 1 14 VDD CAP+ 1 16 VDD

CAP– 2 13 OSC1 CAP– 2 15 OSC1

NC 3 14 NC

CAP2+ 3 12 OSC2

CAP2+ 4 13 OSC2

CAP2– 4 11 POFF

CAP2– 5 12 POFF

TC1 5 10 RV TC1 6 11 RV

TC2 6 9 VREG TC2 7 10 VREG

VI 7 8 VO VI 8 9 VO

S1F76610C0B0/M0B0 S1F76610M2B0

PIN DESCRIPTIONS

S1F76610C0B0/M0B0

Pin No. Pin name Description

1 CAP1+ Positive charge-pump connection for ×2 multiplier

2 CAP1– Negative charge-pump connection for ×2 multiplier

3 CAP2+ Positive charge-pump connection for ×3 multiplier

4 CAP2– Negative charge-pump connection for ×3 multiplier or ×2 multiplier output

5 TC1

Temperature gradient selects

6 TC2

7 VI Negative supply (system ground)

8 VO ×3 multiplier output

9 VREG Voltage regulator output

10 RV Voltage regulator output adjust

11 POFF Voltage regulator output ON/OFF control

12 OSC2 Resistor connection. Open when using external clock

13 OSC1 Resistor connection. Clock input when using external clock

14 VDD Positive supply (system VCC)

2–2 EPSON S1F70000 Series

Technical Manual

S1F76610 Series

SPECIFICATIONS

Absolute Maximum Ratings

Parameter Codes Ratings Units Remarks

N = 2: Boosting to a double voltage

Input supply voltage VI – VDD –20/N to VDD + 0.3 V

N = 3: Boosting to a triple voltage

VI – 0.3 to VDD + 0.3 V OSC1, OSC2, POFF

Input terminal voltage VI – VDD

VO – 0.3 to VDD + 0.3 V TC1, TC2, RV

S1F76610

Series

–20 to VDD + 0.3 V VO Note 3)

Output voltage V O – VDD

V O to VDD + 0.3 V VREG Note 3)

Allowable dissipation PD Max. 300 mW

Working temperature Topr –40 to +85 °C Plastic package

Storage temperature Tstg –55 to +150 °C

Soldering temperature

Tsol 260 • 10 °C • s At leads

and time

Notes

1. Using the IC under conditions exceeding the aforementioned absolute maximum ratings may lead to permanent destruction of

the IC. Also, if an IC is operated at the absolute maximum ratings for a longer period of time, its functional reliability may be

substantially deteriorated.

2. All the voltage ratings are based on VDD = 0V.

3. The output terminals (VO,VREG) are meant to output boosted voltage or stabilized boosted voltage. They, therefore, are not the

terminals to apply an external voltage. In case the using specifications unavoidably call for application of an external voltage,

keep such voltage below the voltage ratings given above.

Reconmmended Operating Conditions

VDD = 0V, Ta = –40 to +85˚C unless otherwise noted

Rating

Parameter Symbol Conditions Unit

Min. Typ. Max.

R OSC =1MΩ

C 3 = 10 µF, CL/C3 ≤ 1/20,

Ta = –20 to +85˚C. — — –1.8

Oscillator startup voltage VSTA V

See note 1.

R OSC = 1MΩ — — –2.2

Oscillator shutdown voltage V STP R OSC = 1MΩ –1.8 — — V

RLmin.

Load resistance RL — — Ω

See note 2.

Output current IO — — 20.0 mA

Clock frequency fOSC 10.0 — 30.0 kHz

CR oscillator network resistance ROSC 680 — 2,000 kΩ

Capacitance C1, C2, C3 3.3 — — µF

Stabilization voltage sensing resis- —

RRV 100 1,000 kΩ

tance

Notes

1. The recommended circuit configuration for low-valtage operation (when VI is between –1.2V and –2.2V) is shown in

the following figure. Note that diode D1 should have a maximum forward voltage of 0.6V with 1.0mA forward current.

2. RL min can be varied depending on the input voltage.

S1F70000 Series EPSON 2–3

Technical Manual

S1F76610 Series

+ 1 14

C1

10µF ROSC

2 13

1MΩ

3 12

C2 +

10µF 4 11

5 10

6 9 CL RL

7 8

+C3

22µF

D1

3. RLmin is a function of V1

5

VSTA2

Minimum load resistance (kΩ)

VSTA1

4

2

Voltage

tripler

1

Voltage

doubler

0

1 1.5 2 3 4 5 6

Input voltage (V)

Electrical Characteristics

VDD = 0V, V1 = –5V, Ta = –40 to +85°C unless otherwise noted

Rating

Parameter Symbol Conditions Unit

Min. Typ. Max.

Input voltage VI –6.0 — –1.8 V

Output voltage VO –18.0 — — V

RL = ∞, RRV = 1MΩ,

Regulator voltage VREG –18.0 — –2.6 V

VO = –18V

Stabilization circuit operating voltage VO –18.0 — –3.2 V

Multiplier current IOPR1 RL = ∞, ROSC = 1MΩ — 40 80 µA

RL = ∞, RRV = 1MΩ,

Stabilization current IOPR2 — 5.0 12.0 µA

VO = –15V

Quiescent current IQ TC2 = TC1 = VO, RL = ∞ — — 2.0 µA

Clock frequency fOSC ROSC = 1MΩ 16.0 20.0 24.0 kHz

2–4 EPSON S1F70000 Series

Technical Manual

S1F76610 Series

Rating

Parameter Symbol Conditions Unit

Min. Typ. Max.

Output impedance RO IO = 10mA — 150 200 Ω

Multiplication efficiency Peff IO = 5mA 90.0 95.0 — %

∆VREG VO = –18 to –8V,

Stabilization output voltage

∆VO·VREG VREG = –8V, RL = ∞,

— 0.2 — %/V

differential

Ta = 25˚C

VO = –15V,

∆VREG VREG = –8V, Ta = 25˚C,

S1F76610

Stabilization output load differential — 5.0 — Ω

Series

∆IO IO = 0 to 10µA,

TC1 = VDD, TC2 = VO

Stabilization output saturation R SAT = ∆(VREG – VO)/∆IO,

R SAT I O = 0 to 10µA, — 8.0 — Ω

resistance

R V = VDD, Ta = 25˚C

RC2 = VO, TC1 = VDD,

–2.3 –1.5 –1.0

Ta = 25˚C

TC2 = TC1 = VO,

Reference voltage V RV –1.7 –1.3 –1.1 V

Ta = 25˚C

TC2 = VDD, TC1 = VO,

Ta = 25˚C –1.1 –0.9 –0.8

–0.25 –0.1 –0.01

Temperature gradient CT See note. –0.5 –0.4 –0.3 %/˚C

–0.7 –0.6 –0.5

POFF, TC1, TC2, OSC1, and RV ILKI — — 2.0 µA

input leakage current

Note

|VREG (50°C)| – |VREG (0°C)| 100

CT = ×

50°C – 0°C |VREG (25°C)|

S1F70000 Series EPSON 2–5

Technical Manual

S1F76610 Series

Typical Performance Characteristics

1000 26

25

Ta = 25°C 24

23

VI = –5V 22

VI = –3V 21 VI = –5.0V

100 VI = –2V 20

fOSC [kHz]

19 VI = –3.0V

fOSC [kHz]

18

17

VI = –2.0V

16

15

10 14

13

12

11

10

9

1 8

10 100 1000 10000 –40 –20 0 20 40 60 80 100

ROSC [kΩ] Ta [°C]

(1) Clock frequency vs. External resistance (2) Clock frequency vs. Ambient temperature

150

0

Ta = 25°C

Ta = 25°C

VI = –5.0V

fOSC = 40kHz

100 –5

IOPR [µA]

VO [V]

fOSC =

20kHz ×2 multiplier

50 –10

fOSC = 10kHz ×3 multiplier

–15

0 0 10 20 30 40

–7 –6 –5 –4 –3 –2 –1 0

VI [V] IO [mA]

(3) Multiplier current vs. Input voltage (4) Output voltage vs. Output current

2–6 EPSON S1F70000 Series

Technical Manual

S1F76610 Series

0

0

Ta = 25°C

VI = –3.0V –1 Ta = 25°C

VI = –2.0V

×2 multiplier

–5 –2

VO [V]

Vo [V]

–3

×2 multiplier

×3 multiplier

S1F76610

–10

Series

–4

×3 multiplier

–5

–15

–6

0 10 20 30 0 1 2 3 4 5 6 7 8 9 10

IO [mA] IO [mA]

(5) Output voltage vs. Output current (6) Output voltage vs. Output current

100 100 100 60

90 90 90 54

80 80 80 48

70 Ta = 25°C 70 70 Ta = 25°C ×2 multiplier 42

VI = –5.0V VI = –3.0V Peff

60 ×2 multiplier 60 60 36

Peff [%]

Peff [%]

Peff

II [mA]

II [mA]

50 ×3 multiplier ×3 multiplier 50 50 30

×3 multiplier

II Peff

II ×3 multiplier

40 40 40 Peff 24

30 30 30 18

20 ×2 multiplier 20 20 12

II ×2 multiplier

10 10 10 II 6

0 0 0 0

0 10 20 30 40 50 0 5 10 15 20 25 30

IO [mA] IO [mA]

(7) Multiplication efficiency/input current (8) Multiplication efficiency/input current

vs. Output current vs. Output current

S1F70000 Series EPSON 2–7

Technical Manual

S1F76610 Series

500

100 40

Ta = 25°C

90 ×2 multiplier 36

Peff 400 IO = 6mA

80 32

70 Ta = 25°C ×3 multiplier 28

VI = –2.0V Peff 300

60 24

RO [Ω]

Peff [%]

II [mA]

50 20

200

40 ×3 multiplier 16

II ×3 multiplier

30 12

100 ×2 multiplier

20 ×2 multiplier 8

II

10 4

0

0 0

0 1 2 3 4 5 6 7 8 9 10 –7 –6 –5 –4 –3 –2 –1 0

IO [mA]

VI [V]

(9) Multiplication efficiency/input current (10) Output impedance vs. Input voltage

vs. Output current

500

100

Ta = 25°C

IO = 10mA IO = 2mA

400

90

IO = 5mA

300

80

RO [Ω]

Peff [%]

IO = 10mA

200 70

×3 multiplier

IO = 20mA

100 ×2 multiplier 60

IO = 30mA Ta = 25°C

0 VI = –5.0V

50

–7 –6 –5 –4 –3 –2 –1 0 1 10 100 1000

VI [V] fOSC [kHz]

(11) Output impedance vs. Input voltage (12) Multiplication efficiency vs. Clock frequency

2–8 EPSON S1F70000 Series

Technical Manual

S1F76610 Series

100 –7.850

IO = 0.5mA

IO = 1.0mA

IO = 2.0mA VO = –15V

90

Ta = 25°C

IO = 4.0mA –7.900

80

VREG [V]

Peff [%]

70

S1F76610

Series

–7.950

Ta = 25°C

60 VI = – 3.0V

50 –8.000

1 10 100 1000 0.0001 0.0010 0.0100 0.1000

fOSC [kHz] IO [V]

(13) Multiplication efficiency vs. Clock frequency (14) Output voltage vs. Output current

–5.850 –2.850

VO = –9V VO = –6V

Ta = 25°C

Ta = 25°C

–5.900 –2.900

VREG [V]

VREG [V]

–5.950 –2.950

–6.000 –3.000

0.0001 0.0010 0.0100 0.1000 0.0001 0.0010 0.0100 0.1000

IO [V] IO [V]

(15) Output voltage vs. Output current (16) Output voltage vs. Output current

S1F70000 Series EPSON 2–9

Technical Manual

S1F76610 Series

0.30 50

Ta = 25°C

100×|VREG(°C)|-|VREG(25°C)|/|VREG(25°C)| [%]

0.25

VO = –5V

0.20

VO = –10V

|VREG-VO| [V]

VO = –15V

0.15 0

CT0

0.10

CT1

0.05

CT2

0.00 –50

0 5 10 15 20 –40 –20 0 20 40 60 80 100

IO [mA] Ta [°C]

(17) Regulator voltage vs. Output current (18) Regulator output stability ratio vs.

Ambient temperature

Temperature Gradient Control

The S1F7661C0B0 offers a choice of three temperature

gradients which can be used to adjust the voltage regu-

lator output in applications such as power supplies for

driving LCDs.

Temperature

POFF TC2 TC1 Voltage

gradient CR osciliator

regulator Remarks

(%/˚C)

See note 1. output

See note 2.

1 (VDD) Low (V O) Low (VO) –0.4 ON ON

1 (VDD) Low (V O) High (VDD) –0.1 ON ON

1 (VDD) High (VDD) Low (VO) –0.6 ON ON

1 (VDD) High (VDD) High (VDD) –0.6 ON OFF Serial connection

OFF

0 (VI) Low (VO) Low (VO) — OFF

(high impedance)

OFF

0 (VI) Low (VO) High (VDD) — OFF

(high impedance)

OFF OFF

0 (VI) High (VDD) Low (VO) — (high impedance)

OFF Multiplier

0 (VI) High (VDD) High (VDD) — OFF

(high impedance) operational

Notes

1. The definition of LOW for POFF differs from that for TC1 and TC2.

2. The temperature gradient affects the voltage between VDD and VREG.

2–10 EPSON S1F70000 Series

Technical Manual

S1F76610 Series

FUNCTIONAL DESCRIPTIONS

CR Oscillator Voltage Multiplier

The on-chip CR oscillator network frequency is deter- The voltage multiplier uses the clock signal from the

mined by the external resistor, ROSC, connected be- oscillator to double or triple the input voltage. This re-

tween OSC1 and OSC2. This oscillator can be disabled quires three external capacitors–two charge-pump ca-

in favor of an external clock by leaving OSC2 open and pacitors between CAP1+ and CAP1– and CAP2+ and

applying an external clock signal to OSC1. CAP2–, respectively, and a smoothing capacitor be-

tween VI and VO.

Oscillator External clock

S1F76610

Series

OSC1 OSC1

VDD = 0 V

External clock

ROSC signal

C1 + 1 14

OSC2 OSC2

10 µF 2 13 R1 RRV

ROSC 100 kΩ

1 MΩ to

5 V C2 + 3 12 R2 1 MΩ

Reference Volatge Generator and Voltage 10 µF 4 11 + C4

10 µF

Regulator 5 10

The reference voltage generator supplies a reference 6 9

VREG = –8 V

voltage to the voltage regulator to control the output. 7 8 VO = –15 V

This voltage can be switched ON and OFF. VI = –5 V

+ C3

10 µF

VDD

POFF Control signal

RV RRV = 100 kΩ to 1 MΩ Double voltage potential levels

VREG VCC

(+5V)

VDD = 0 V

GND

VI = –5 V

(–5V)

VCAP2 – = 2VI = –10 V

Tripled voltage potential levels

VDD = 0 V

VI = –5 V

VO = 3VI = –15 V

S1F70000 Series EPSON 2–11

Technical Manual

S1F76610 Series

TYPICAL APPLICATIONS

Voltage Tripler with Regulator Converting a Voltage Tripler to a Voltage

The following figure shows the circuit required to triple Doubler

the input voltage, regulate the result and add a tempera- To convert this curcuit to a voltage doubler, remove ca-

ture gradient of –0.4%/°C. Note that the high input im- pacitor C2 and short circuit CAP2– to VO.

pedance of RV requires appropriate noise countermea-

sures.

VDD = 0 V

VDD = 0 V

C1 + 1 14

C1 + 1 14 10µF 2 13 ROSC

10 µF 2 13 R1 RRV 5 V C2 + 3 12 1 MΩ

ROSC 100 kΩ

5 V C2 + 3 12 1 MΩ R2 to 10µF 4 11

1 MΩ

10 µF 4 11 +C4 5 10

10 µF

5 10 6 9

6 9 7 8 VO = –15 V

VREG = –8 V VI = –5 V

7 8 VO = –15 V + C3

VI = –5 V =RRV VRV 10 µF

+ C3 R1

10 µF

Parallel Connection

Connecting two or more chips in parallel reduces the quired when any number of devices are connected in

output impedance by 1/n, where n is the number of de- parallel. Also, the voltage regulator in one chip is suffi-

vices used. cient to regulate the combined output.

Only the single output smoothing capacitor, C3, is re-

VDD = 0 V

1 14 1 14

C1 + C1 +

10 µF 2 13 10 µF 2 13 RRV

ROSC ROSC 100 kΩ

3 12 1 MΩ 3 12 1 MΩ to

C2 + C2 + 1 MΩ

10 µF 4 11 10 µF 4 11 + C4

5V 5 10 5 10 10 µF

6 9 6 9

VREG = –10 V

7 8 7 8 VO = –15 V

VI = –5 V

+C3

10 µF

2–12 EPSON S1F70000 Series

Technical Manual

S1F76610 Series

Serial Connection

Connecting two or more chips in series obtains a higher connection, however, this also raises the output imped-

output voltage than can be obtained using a parallel ance.

<Precautions when connecting loads>

In case of series connections, when connecting loads the first stage VDD (or other potential of the second

between the first stage VDD (or other potential of the stage VDD or up) to cause a voltage exceeding the

second stage VDD or up) and the second stage V REG as absolute maximum rating for the second stage VDD at

shown in Fig. 2-13, be cautions about the following the VREG terminal, normal operation of the IC may be

point. hampered. Consequently, When making a series

S1F76610

Series

connection, insert a diode D1 between the second

* When normal output is not occurring at the VREG ter- stage VI and VREG as shown in Fig. 2-13 so that a

minal such as at times of starting up or when turning voltage exceeding the second stage VDD or up may

the VREG off by POFF signals, if current flows into the not be applied to the VREG terminal.

second stage VREG terminal through the load from

VDD' = VI = –5V

VDD = 0V

10µF Load

1 14 + 1 14 100kΩ

+ 10µF to

– – 1MΩ

2 13 2 13

+

1MΩ 10µF

5V –

3 12 + 3 12

10µF

4 11 – 4 11

5 10 5 10

6 9 VO = –10V= VI 6 9

VREG' = –15V

7 8 7 8 VO = –20V

10µF –

VI = –5V

+

+ –

10µF

D1

Positive Voltage Conversion VDD = 0 V

Adding diodes converts a negative voltage to a positive D1

C1

10 µF

one. 1 14

To convert the voltage tripler shown earlier to a voltage +

D2 C2 2 13

doubler, remove C2 and D2, and short circuit D3. Small 10 µF ROSC

3 12 1 MΩ

Schottky diodes are recommended for all these diodes. 5V +

The resulting voltage is lowered by VF, the voltage drop 4 11

in the forward direction for each diode used. For ex- D3 5 10

ample, if VDD = 0V, VI = –5V, and VF = 0.6V, the re- 6 9

sulting voltages would be as follows. + 7 8

• For a voltage tripler, VO = 8.2 V C3

VO = 10 – (3 × 0.6) = 8.2V 10 µF

VI = –5 V

• For a voltage doubler,

VO = 5 – (2 × 0.6) = 3.8V

S1F70000 Series EPSON 2–13

Technical Manual

S1F76610 Series

Simultaneous Voltage Conversion Using an External Gradient

Combining a standard voltage tripler circuit with one The S1F7661C0B0/M0B0 offers three built-in tem-

for positive voltage conversion generates both –15 and perature gradients— –0.1, –0.4 and –0.6%/°C.

8.2V outputs from a single input, however, it also raises To set the gradient externally, place a thermistor, RT, in

the output impedance. series with the variable resistor, RRV, used to adjust the

A voltage doubler generates –10 and 3.8V outputs. output voltage.

VDD = 0 V

1 14 VDD

D1 10 µF

+

1 14 2 13 R1

+

10 µF RRV

D2 10 µF 2 13 3 12 +

+ ROSC 10 µF

3 12 1 MΩ

+

4 11

10 µF 4 11 RT RP

5V

5 10

D3 5 10

6 9 6 9 VREG

+ 10 µF VO1 = –15 V

7 8 7 8

VO2 = 8.2 V

+ 10 µF

VI = –5 V

Potential levels

VO2 = 8.2V

VDD = 0 V

VI = –5 V

VO1 = –15 V

2–14 EPSON S1F70000 Series

Technical Manual

You might also like

- R1283K001CDocument26 pagesR1283K001CdinhdtdNo ratings yet

- MC14043B, MC14044B Cmos Msi: Quad R S LatchesDocument7 pagesMC14043B, MC14044B Cmos Msi: Quad R S LatchespaulpuscasuNo ratings yet

- MC14043B, MC14044B Cmos Msi: Quad R S LatchesDocument7 pagesMC14043B, MC14044B Cmos Msi: Quad R S LatchesTony EspositoNo ratings yet

- R1283x SERIES: 2ch DC/DC For CCD & OLEDDocument26 pagesR1283x SERIES: 2ch DC/DC For CCD & OLEDarnaud.herbertNo ratings yet

- MC14046BCPDocument8 pagesMC14046BCPmrponchitoNo ratings yet

- DatasheetDocument26 pagesDatasheetpopeyeNo ratings yet

- 6000 Count AUTO DMM: Features DescriptionDocument23 pages6000 Count AUTO DMM: Features DescriptionAnonymous biMSzTyszNo ratings yet

- Green-Mode PWM Controller With High-Voltage Start-Up Circuit and Adjustable OLP Delay TimeDocument19 pagesGreen-Mode PWM Controller With High-Voltage Start-Up Circuit and Adjustable OLP Delay TimeЕвгений ПNo ratings yet

- R2A20133DDocument14 pagesR2A20133DLuiz Augusto Freitas SantosNo ratings yet

- Esquema Fonte TL494 Progetos Outros.Document13 pagesEsquema Fonte TL494 Progetos Outros.Gabriel CordeiroNo ratings yet

- DatasheetDocument9 pagesDatasheetjim campbellNo ratings yet

- Cyrustek ES51966 (Appa 505)Document25 pagesCyrustek ES51966 (Appa 505)budi0251No ratings yet

- PLL XR2212 ExarCorporationDocument20 pagesPLL XR2212 ExarCorporationHoan TranNo ratings yet

- LM5030 Application: DC - DC Converter Utilizing The Push-Pull TopologyDocument10 pagesLM5030 Application: DC - DC Converter Utilizing The Push-Pull TopologyEdoardoNo ratings yet

- Single-Channel: 6N135, 6N136, HCPL2503, HCPL4502 Dual-Channel: HCPL2530, HCPL2531 High Speed Transistor OptocouplersDocument15 pagesSingle-Channel: 6N135, 6N136, HCPL2503, HCPL4502 Dual-Channel: HCPL2530, HCPL2531 High Speed Transistor OptocouplersmortezaNo ratings yet

- NCN5150 DDocument12 pagesNCN5150 Dgoingforward77No ratings yet

- mc14043b d-1193116Document8 pagesmc14043b d-1193116cesarNo ratings yet

- FP6321A FitiDocument14 pagesFP6321A FitiJob GarciaNo ratings yet

- LMC662 CMOS Dual Operational Amplifier: General Description FeaturesDocument16 pagesLMC662 CMOS Dual Operational Amplifier: General Description FeaturesAnonymous nQ4z7PNo ratings yet

- 16096Document11 pages16096Bari ShobariNo ratings yet

- 74LV04Document12 pages74LV04mulia usmanNo ratings yet

- Sanken Backlight LED Driver bl0202b TCL Roku - Ds - enDocument26 pagesSanken Backlight LED Driver bl0202b TCL Roku - Ds - enjimmyboy111100% (1)

- 3843ANDocument8 pages3843ANinfosolutionNo ratings yet

- M62429P/FP: Serial Data Control Dual Electronic VolumeDocument8 pagesM62429P/FP: Serial Data Control Dual Electronic VolumeahmedNo ratings yet

- MC14553B 3-Digit BCD Counter: PDIP-16 P Suffix CASE 648Document12 pagesMC14553B 3-Digit BCD Counter: PDIP-16 P Suffix CASE 648suriantoNo ratings yet

- STLVD111: Programmable Low Voltage 1:10 Differential LVDS Clock DriverDocument19 pagesSTLVD111: Programmable Low Voltage 1:10 Differential LVDS Clock DriverRobert GrabekNo ratings yet

- Receptor UHF T5743P6Document41 pagesReceptor UHF T5743P6Jorge Martinez PerezNo ratings yet

- 3842a DatasheetDocument8 pages3842a DatasheetVịnh DemoNo ratings yet

- 2A20112 PFC Fuentes LG Audio PFC CRITICALDocument9 pages2A20112 PFC Fuentes LG Audio PFC CRITICALAndres AlegriaNo ratings yet

- Diodes - Inc. AP3842CMTR E1 DatasheetDocument14 pagesDiodes - Inc. AP3842CMTR E1 DatasheetEsteban Elias Marquez EscalanteNo ratings yet

- XR 2207Document24 pagesXR 2207peter3972No ratings yet

- CXD1267AN: CCD Vertical Clock DriverDocument8 pagesCXD1267AN: CCD Vertical Clock DriverTaha OpedNo ratings yet

- UC3844B, UC3845B, UC2844B, UC2845B High Performance Current Mode ControllersDocument20 pagesUC3844B, UC3845B, UC2844B, UC2845B High Performance Current Mode Controllers田忠勇No ratings yet

- Quad High-Side and Octal Low-Side Switch For Automotive: Advance InformationDocument40 pagesQuad High-Side and Octal Low-Side Switch For Automotive: Advance InformationDavid MendezNo ratings yet

- SONY,,: For The Availability of This Product, Please Contact The Sales OfficeDocument8 pagesSONY,,: For The Availability of This Product, Please Contact The Sales OfficeERNANIPARNOWNo ratings yet

- NCP81228 DDocument26 pagesNCP81228 DCleidson LimaNo ratings yet

- High-Voltage Signal Conditioning For Low-Voltage Adcs: Application ReportDocument11 pagesHigh-Voltage Signal Conditioning For Low-Voltage Adcs: Application ReportOSCAR ANDRES BERMUDEZ HERNANDEZNo ratings yet

- UC3848Document12 pagesUC3848isaiasvaNo ratings yet

- Switching From The L6561 To The L6562: AN1757 Application NoteDocument9 pagesSwitching From The L6561 To The L6562: AN1757 Application Notedeilyn rivasNo ratings yet

- 74HCT9046A: 1. General DescriptionDocument43 pages74HCT9046A: 1. General DescriptionDanielNo ratings yet

- MC14536B Programmable Timer: PDIP-16 P Suffix CASE 648Document16 pagesMC14536B Programmable Timer: PDIP-16 P Suffix CASE 648djorjuelaNo ratings yet

- Omron - MK0607-1189905Document11 pagesOmron - MK0607-1189905Pedro Tavares MurakameNo ratings yet

- Switched Capacitor Voltage Converter With Regulated Output ADP3604Document8 pagesSwitched Capacitor Voltage Converter With Regulated Output ADP3604Luís GuerreiroNo ratings yet

- General Purpose Relay: Ordering InformationDocument7 pagesGeneral Purpose Relay: Ordering Informationvalimorsk ltd.No ratings yet

- Probador de Flyback de Isaac HernandezDocument8 pagesProbador de Flyback de Isaac HernandezANTONIO PEREZNo ratings yet

- Charge Pump Dc-To-Dc Voltage ConverterDocument11 pagesCharge Pump Dc-To-Dc Voltage ConverterRicardo KraftmanNo ratings yet

- MCP413X 415X 423X 425X PDFDocument88 pagesMCP413X 415X 423X 425X PDFspotNo ratings yet

- DSAEDA000142090Document19 pagesDSAEDA000142090dangthanhlinhNo ratings yet

- SP490E/SP491E Enhanced Full Duplex RS-485 Transceivers: DescriptionDocument12 pagesSP490E/SP491E Enhanced Full Duplex RS-485 Transceivers: DescriptionCarlos AcostaNo ratings yet

- LC5910S Data Sheet: Critical Current Mode Buck LED Driver ICDocument22 pagesLC5910S Data Sheet: Critical Current Mode Buck LED Driver ICalvaro marcos manuel lopezNo ratings yet

- MCP453Document102 pagesMCP453priyanka choudhryNo ratings yet

- Charge Pump DC-to-DC Voltage Converter: Features Package TypesDocument20 pagesCharge Pump DC-to-DC Voltage Converter: Features Package TypesTomás CuetoNo ratings yet

- SN 65 HVD 33Document32 pagesSN 65 HVD 33craigslist_nNo ratings yet

- Single-Channel: 6N138, 6N139 Dual-Channel: HCPL-2730, HCPL-2731 Low Input Current High Gain Split Darlington OptocouplersDocument15 pagesSingle-Channel: 6N138, 6N139 Dual-Channel: HCPL-2730, HCPL-2731 Low Input Current High Gain Split Darlington Optocouplersdevrim.kosalNo ratings yet

- TV/VCR Tuner Ic With DC/DC Converter: FeaturesDocument21 pagesTV/VCR Tuner Ic With DC/DC Converter: FeaturesEdsel SilvaNo ratings yet

- AP4111 Manual Electronic System DesignDocument87 pagesAP4111 Manual Electronic System Designhmpudur1968No ratings yet

- MIP521A Application Note - Ver.2-5Document16 pagesMIP521A Application Note - Ver.2-5draNo ratings yet

- Daewoo CP 830FPDocument23 pagesDaewoo CP 830FPElservNo ratings yet

- f23Document3 pagesf23jaquel.kenithNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Connectrix-Ds-6600b-Switche ManualDocument6 pagesConnectrix-Ds-6600b-Switche Manualbrayerly143No ratings yet

- Philips 190cw8fb XX Chassis Hudson 8 (ET)Document94 pagesPhilips 190cw8fb XX Chassis Hudson 8 (ET)Leonardo FleiNo ratings yet

- Chapter 2 - Noise in Communication SystemDocument31 pagesChapter 2 - Noise in Communication SystemDavidNo ratings yet

- Viper 22 ADocument30 pagesViper 22 ALullaby summerNo ratings yet

- Electronic Components, Packaging and Production: Leif Halbo and Per Ohlckers University of OsloDocument12 pagesElectronic Components, Packaging and Production: Leif Halbo and Per Ohlckers University of OsloengshimaaNo ratings yet

- H-Bridge Relay User ManualDocument2 pagesH-Bridge Relay User ManualRozitarmizi MohammadNo ratings yet

- Acer Aspire m1100Document96 pagesAcer Aspire m1100Reginald SosaNo ratings yet

- Fig. 2.44 Half-Wave Rectifier.: Electronic Devices and Circuit Theory, 9eDocument160 pagesFig. 2.44 Half-Wave Rectifier.: Electronic Devices and Circuit Theory, 9eLelouch ViNo ratings yet

- DTS0068 - PER Measurement PDFDocument5 pagesDTS0068 - PER Measurement PDFDaniel AdebayoNo ratings yet

- Cisco - Understand Gpon TechnologyDocument20 pagesCisco - Understand Gpon TechnologyNwayOo YeNo ratings yet

- BP120 Upgrade InstructionDocument2 pagesBP120 Upgrade InstructionCristobal Riveros GelvesNo ratings yet

- Ads 1298Document107 pagesAds 1298Anonymous XS9jAhY1pENo ratings yet

- VcapDocument240 pagesVcapNikolay BonevNo ratings yet

- ps-1 Model Paper 2Document3 pagesps-1 Model Paper 2Kunal Dev KaushalNo ratings yet

- Agilent N9340B Handheld Spectrum Analyzer: User's GuideDocument174 pagesAgilent N9340B Handheld Spectrum Analyzer: User's GuidejmezatapiaNo ratings yet

- IoT Based Solar Energy Monitoring SystemDocument5 pagesIoT Based Solar Energy Monitoring SystemhatomiNo ratings yet

- Data Communications ReviewerDocument3 pagesData Communications ReviewermatthewbuenaNo ratings yet

- 12-00009WD - F - Audio Interface (Garmin GMA 1347D)Document11 pages12-00009WD - F - Audio Interface (Garmin GMA 1347D)Deleh GonzalezNo ratings yet

- Lesson#4 AM CompleteDocument58 pagesLesson#4 AM CompleteIan VillarojoNo ratings yet

- To Design and Implement Passive Clipper Circuit.Document5 pagesTo Design and Implement Passive Clipper Circuit.samarth dukreNo ratings yet

- Tri-Band Bandpass Filter Using Two Short Stubs and An Open Stub Loaded ResonatorDocument3 pagesTri-Band Bandpass Filter Using Two Short Stubs and An Open Stub Loaded ResonatorDuong TranNo ratings yet

- User's Manual: Professional Laptop Battery Analyzer Model: NLBADocument50 pagesUser's Manual: Professional Laptop Battery Analyzer Model: NLBAtecsupportNo ratings yet

- Robotic Hand FYP ProposalDocument13 pagesRobotic Hand FYP ProposalSajid NaseebNo ratings yet

- Mercedes 722.6 Failure To UpshiftDocument3 pagesMercedes 722.6 Failure To Upshiftirc100% (2)

- Kramer Matrix Vs-88a, vs-88v, sd-7588vDocument30 pagesKramer Matrix Vs-88a, vs-88v, sd-7588vAdrian IoanNo ratings yet

- Class17 18 IBIS Io Buffer ClassDocument66 pagesClass17 18 IBIS Io Buffer ClassdeepakNo ratings yet

- LAB2 BJT Biasing 15Document7 pagesLAB2 BJT Biasing 15hasyikinNo ratings yet

- UMTS Troubleshooting Guideline 1 02Document107 pagesUMTS Troubleshooting Guideline 1 02Ankur VermaNo ratings yet

- Chapter-5 Real Time Operating Systems Context Switching MechanismDocument8 pagesChapter-5 Real Time Operating Systems Context Switching MechanismhariNo ratings yet

- Final Report PDFDocument103 pagesFinal Report PDFsai abhsihekNo ratings yet