Professional Documents

Culture Documents

DLD MCQS

DLD MCQS

Uploaded by

zeeshan maseeh0 ratings0% found this document useful (0 votes)

21 views2 pagesThis document contains multiple choice questions related to digital circuits such as bistable multivibrators, latches, flip-flops, and integrated circuits. It tests knowledge of basic concepts and components of sequential and combinational logic circuits.

Original Description:

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document contains multiple choice questions related to digital circuits such as bistable multivibrators, latches, flip-flops, and integrated circuits. It tests knowledge of basic concepts and components of sequential and combinational logic circuits.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

0 ratings0% found this document useful (0 votes)

21 views2 pagesDLD MCQS

DLD MCQS

Uploaded by

zeeshan maseehThis document contains multiple choice questions related to digital circuits such as bistable multivibrators, latches, flip-flops, and integrated circuits. It tests knowledge of basic concepts and components of sequential and combinational logic circuits.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

You are on page 1of 2

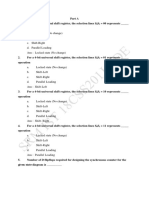

1. c) Bistable 17.

c) NOR or NAND 31. a) Q(n+1) = (S +

multivibrator gates Q(n))R’

2. b) Two stable 18. . b) Sequential 32. c) Latches has

state circuits one input but

flip-flop has two

3. c) It can store 19. a) Combinational

one bit of data circuits 33. c) 4

4. c) High output & 20. a) 2 34. b) Two

low output additional AND

21. b) Latch gates

5. a) 4

22. a) Two inverters 35. d) Invalid State

6. a) System rated 36. c) Binary storage

23. b) Reset register

7. b) 2 inputs

24. a) The trigger 37. b) When the Q

8. d) q and q’ pulse is given to output follows

9. b) label outputs change the state the input

10. c) s and r 25. a) A pulse that 38. c) The clock

starts a cycle of pulse transitions

11. c) Metastable operation from LOW to

HIGH

12. d) Cross coupling 26. c) Because of

13. c) Switch cross-coupled 39. b) No active S or

debouncer connection R input

14. c) 3 27. d) S’=0, R’=0 40. b) RESET

28. a) No change

15. c) Not change 41. a) Edge-

29. d) Both a D latch detection circuit

16. a) The Q output and an inverter

is either SET or at its input 42. d) Gated D-latch

RESET as soon as 30. a) The inputs of 43. a) S-R flip-flop

the D input goes NOR latch are 0

HIGH or LOW but 1 for NAND 44. a) Two AND

latch gates

45. d) J = 1, K = 1 inventory of the

46. b) Ones catching integrated

circuit

47. d) J = 0, K = 0

48. d) A 10 kHz 63. a) J = 0, K = 0

square wave

49. c) The letters 64. a) 00

were chosen in

honour of Jack 65. b) 2 kHz

Kilby, the

inventory of the

integrated

circuit

50. a) J = 0, K = 0

51. a) 00

52. b) 2 kHz

53. b) 5 kHz

54. c) 4

55. d) Gated D-latch

56. a) S-R flip-flop

57. a) Two AND

gates

58. d) J = 1, K = 1

59. b) Ones catching

60. d) J = 0, K = 0

61. d) A 10 kHz

square wave

62. c) The letters

were chosen in

honour of Jack

Kilby, the

You might also like

- Logic Exam - Bank Questions - Assuit UniversityDocument10 pagesLogic Exam - Bank Questions - Assuit Universityعبدالرحمن العجانNo ratings yet

- Sequential CircuitsDocument33 pagesSequential CircuitsPrasun SinghalNo ratings yet

- Me604b Question Bank MechatronicsDocument14 pagesMe604b Question Bank Mechatronicskuldip mukherjeeNo ratings yet

- Questions On Digital Electronics and MicroprocessorsDocument12 pagesQuestions On Digital Electronics and MicroprocessorsHarendra KumarNo ratings yet

- MCQ Unit 4Document14 pagesMCQ Unit 4SIVALAKSHMINo ratings yet

- Ade Unit - 4 QBDocument17 pagesAde Unit - 4 QBNithya SNo ratings yet

- Gate Mock Test1Document17 pagesGate Mock Test1Gopinathan SudheerNo ratings yet

- II Mid Bits For StudentsDocument9 pagesII Mid Bits For StudentsSurya MukeshNo ratings yet

- Unit 4Document13 pagesUnit 4AMAN SRIVASTAVA (RA2011030010057)No ratings yet

- DL 290Document3 pagesDL 290Gagan SLNo ratings yet

- MCQ-Flip FlopDocument11 pagesMCQ-Flip Flop01ABHIGYAN MAJINo ratings yet

- IES - Digital Mock Test - 2014Document9 pagesIES - Digital Mock Test - 2014Meenakshi SundaramNo ratings yet

- TECHNICAL QUIZ EceDocument7 pagesTECHNICAL QUIZ EceAnonymous eWMnRr70qNo ratings yet

- Ec 2007Document11 pagesEc 2007mallanna4blogsNo ratings yet

- Digital Electronics and CircuitsDocument12 pagesDigital Electronics and CircuitsGuruKPONo ratings yet

- APGENCO 2012 Elct SolutionsDocument15 pagesAPGENCO 2012 Elct Solutionsishak789No ratings yet

- DigitalDocument15 pagesDigitalVskm Nagarajan MuthuragavanNo ratings yet

- MCQ 3,4Document18 pagesMCQ 3,4vijayalakshmiNo ratings yet

- QbcsaDocument7 pagesQbcsaMohammad ImthiyazNo ratings yet

- NPCIL Electronics PaperDocument9 pagesNPCIL Electronics Papernetcity143No ratings yet

- Micro MCQ Unit 4,5Document20 pagesMicro MCQ Unit 4,5Abhijit KumarNo ratings yet

- Subject: Digital System Design (DSD) Sem: 3, EXTCDocument9 pagesSubject: Digital System Design (DSD) Sem: 3, EXTCPratik BhalakeNo ratings yet

- QB - Basics of Com - OrganizationDocument11 pagesQB - Basics of Com - OrganizationAarya ShilimkarNo ratings yet

- Electrical Paper II - IES 2010 Question PaperDocument24 pagesElectrical Paper II - IES 2010 Question Paperaditya_kumar_meNo ratings yet

- Logic Gates V3Document5 pagesLogic Gates V3Benito PalmaNo ratings yet

- ConsysdigitalDocument8 pagesConsysdigitalGeetha AnbazhaganNo ratings yet

- A Exit Exam Model From EPCE - EeennoooDocument19 pagesA Exit Exam Model From EPCE - Eeennoooousmi2741No ratings yet

- ModuleDocument105 pagesModuleBookMaggot100% (2)

- 153psu Isro (Ec) - 2008 QuestionsDocument11 pages153psu Isro (Ec) - 2008 QuestionsSaisekhar AyenvalliNo ratings yet

- Assistant Engineers (AE) Electrical 2012 Question Paper With KeyDocument9 pagesAssistant Engineers (AE) Electrical 2012 Question Paper With Keythivya100% (1)

- QP Even14Document2 pagesQP Even14ITI Electronic DhamalNo ratings yet

- Physics (Question Paper) AITS 24 SHIFT 2Document6 pagesPhysics (Question Paper) AITS 24 SHIFT 2Saravanan BNo ratings yet

- Gate 23-09-2013Document7 pagesGate 23-09-2013Himanshu VasisthaNo ratings yet

- Physics 2nd Year CH#18Document2 pagesPhysics 2nd Year CH#18Rashid JalalNo ratings yet

- Genco-Transco Prev PapersDocument257 pagesGenco-Transco Prev PaperssivaNo ratings yet

- Bridge Balance MCQ'S Set ADocument8 pagesBridge Balance MCQ'S Set AsakkuumhNo ratings yet

- Mock GateDocument11 pagesMock GateSandeep Guha NiyogiNo ratings yet

- Deld - Online - MCQ - DELD Online Questions Unit IVDocument5 pagesDeld - Online - MCQ - DELD Online Questions Unit IVShanti GuruNo ratings yet

- QB 2Document6 pagesQB 2shashikumarNo ratings yet

- Digital Logic Question BankDocument13 pagesDigital Logic Question Bankqntvshhw5nNo ratings yet

- DELD Online Questions Unit IVDocument5 pagesDELD Online Questions Unit IVShanti GuruNo ratings yet

- 2006Document11 pages2006simplymeashishNo ratings yet

- Comprehension: L L L L L LDocument9 pagesComprehension: L L L L L LGeetha AnbazhaganNo ratings yet

- Mahapralay DPP - Semiconductors & Logic GatesDocument9 pagesMahapralay DPP - Semiconductors & Logic GatesKOVIDH CHAUDHARYNo ratings yet

- Unit 5Document11 pagesUnit 5RajaNo ratings yet

- Work Sheet On DLDDocument7 pagesWork Sheet On DLDyisakabera123No ratings yet

- Name: Digital Logic Circuits (Common To ICE) Part A (20X2 40 Marks) Answer All QuestionsDocument2 pagesName: Digital Logic Circuits (Common To ICE) Part A (20X2 40 Marks) Answer All QuestionsAnonymous yO7rcec6vuNo ratings yet

- Question BankDocument16 pagesQuestion BankSaket GoluNo ratings yet

- Electronics Question Bank-2: Compiled by Vishnu .N .VDocument8 pagesElectronics Question Bank-2: Compiled by Vishnu .N .Virshi1983No ratings yet

- Ch-5 Thyristors (Tutorial I)Document2 pagesCh-5 Thyristors (Tutorial I)Zay Yar LinNo ratings yet

- Problem Set 2: S S S G ADocument2 pagesProblem Set 2: S S S G AThịnh Nguyễn vănNo ratings yet

- D.U. M.Sc. Entrance - 2014 (Physics) (Code - PTHS-M4)Document9 pagesD.U. M.Sc. Entrance - 2014 (Physics) (Code - PTHS-M4)Soumyashree paridaNo ratings yet

- 08ab303 Digital Logic CircuitsDocument4 pages08ab303 Digital Logic CircuitsChandru RamaswamyNo ratings yet

- RCPP QuestionSet 1Document23 pagesRCPP QuestionSet 1Siddhanth SharmaNo ratings yet

- 12.1 Virtual Lab Link and Viva Questions (MCQ) For PART ADocument6 pages12.1 Virtual Lab Link and Viva Questions (MCQ) For PART Aresham k vNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsFrom EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsNo ratings yet

- Fundamentals of Electronics 2: Continuous-time Signals and SystemsFrom EverandFundamentals of Electronics 2: Continuous-time Signals and SystemsNo ratings yet

- Power System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)From EverandPower System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)No ratings yet

- Networking McqsDocument2 pagesNetworking Mcqszeeshan maseehNo ratings yet

- Viruses McqsDocument1 pageViruses Mcqszeeshan maseehNo ratings yet

- Database MCQSDocument6 pagesDatabase MCQSzeeshan maseehNo ratings yet

- Compiler ConstructionDocument16 pagesCompiler Constructionzeeshan maseehNo ratings yet

- UntitledDocument8 pagesUntitledBiruk HabtamuNo ratings yet

- SaveFile DecryptedDocument30 pagesSaveFile Decryptedgamesguilherme384No ratings yet

- Clockwise/Spiral Rule: See AlsoDocument1 pageClockwise/Spiral Rule: See Alsohouda HaritNo ratings yet

- Pin Diagram With and GateDocument11 pagesPin Diagram With and GateZahid CoolNo ratings yet

- 2.data TypesDocument74 pages2.data TypesManoj ManuNo ratings yet

- Topic 6 Predicate LogicDocument10 pagesTopic 6 Predicate Logicعبدالرحيم اودينNo ratings yet

- Oop Assignment #2: Submitted By: Adnan Haider Reg No. Sp20-Bse-037Document7 pagesOop Assignment #2: Submitted By: Adnan Haider Reg No. Sp20-Bse-037Adnan AadiNo ratings yet

- Tut 4Document2 pagesTut 4Harshil PatelNo ratings yet

- Chapter 7 LogicDocument43 pagesChapter 7 LogicKhoa Trần0% (1)

- Vision Gate 2023 DL Chapter 2 Boolean Algebra Minimization 71Document27 pagesVision Gate 2023 DL Chapter 2 Boolean Algebra Minimization 71ayushNo ratings yet

- De Lab Manual 21-22Document46 pagesDe Lab Manual 21-22AUTHOR SOULNo ratings yet

- Dhanushka Ravishan 2023 A/L: Boolean Algebra & Logic GatesDocument6 pagesDhanushka Ravishan 2023 A/L: Boolean Algebra & Logic GatesGifari MohamedNo ratings yet

- Chapter TwoDocument35 pagesChapter TwobellaNo ratings yet

- IE1204 Exercise 2 P1 HT2022Document4 pagesIE1204 Exercise 2 P1 HT2022tom manNo ratings yet

- LAB-5 Implementation of XOR and XNOR Gates Using Basic and NAND GatesDocument11 pagesLAB-5 Implementation of XOR and XNOR Gates Using Basic and NAND GatesNaeem AtifNo ratings yet

- Kendriya Vidyalaya Physics ProjectDocument17 pagesKendriya Vidyalaya Physics ProjectPrajwal SalviNo ratings yet

- Chapter 3Document41 pagesChapter 3Izzah AmaniNo ratings yet

- chp1 Logic CircuitDocument3 pageschp1 Logic Circuitheyfiez12No ratings yet

- Unit 3Document82 pagesUnit 3gauravlodhi983No ratings yet

- MMMMMMDocument11 pagesMMMMMMTracy NadineNo ratings yet

- Chapter 2 Logic Gates2Document22 pagesChapter 2 Logic Gates2juber mullaNo ratings yet

- Experiment#11 Clocked Sequential Circuits and CountersDocument8 pagesExperiment#11 Clocked Sequential Circuits and CountersfahadNo ratings yet

- De - Experiment 1Document14 pagesDe - Experiment 1harvi.kotadiya121816No ratings yet

- PHAL Visoth E20200158Document5 pagesPHAL Visoth E20200158Visoth PhalNo ratings yet

- De 213 AOI Logic ImplementationDocument12 pagesDe 213 AOI Logic ImplementationXavier MartinezNo ratings yet

- Chapter 5 Synchronous Sequential CircuitDocument73 pagesChapter 5 Synchronous Sequential CircuitBirukNo ratings yet

- LogDocument16 pagesLogBea Amor LlamisNo ratings yet

- Print Verilog CodeDocument24 pagesPrint Verilog CodeShruthi DyavegowdaNo ratings yet

- Balogun Prolog2Document4 pagesBalogun Prolog2awboi le0% (1)

- CS210 Slides 03 03 Negating QuantifiersDocument16 pagesCS210 Slides 03 03 Negating QuantifiersEisha IslamNo ratings yet