Professional Documents

Culture Documents

R2A20052NS: Lithium-Ion Battery Charger IC With Auto Load Current Distribution

R2A20052NS: Lithium-Ion Battery Charger IC With Auto Load Current Distribution

Uploaded by

MauInfogames BancadaCopyright:

Available Formats

You might also like

- 61863ev4 PDFDocument506 pages61863ev4 PDFAntonio LucasNo ratings yet

- PHIL ARTS - Elements and PrinciplesDocument25 pagesPHIL ARTS - Elements and PrinciplesmichelleNo ratings yet

- SD6835 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage MosfetDocument9 pagesSD6835 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage MosfetАлександр КачеишвилиNo ratings yet

- SD6832 SLDocument10 pagesSD6832 SLMuhammad IchsanNo ratings yet

- AX3005 AXEliteDocument11 pagesAX3005 AXElitebibib bibibNo ratings yet

- 150Khz, 3A PWM Buck DC/DC Converter: Advanced Power Electronics CorpDocument12 pages150Khz, 3A PWM Buck DC/DC Converter: Advanced Power Electronics CorpOjahan HNo ratings yet

- 500-kHz Half-Bridge DC-DC ConverterDocument17 pages500-kHz Half-Bridge DC-DC Converteratkxyz777100% (1)

- Ax 3001Document12 pagesAx 3001cuervituNo ratings yet

- Data SheetDocument30 pagesData SheetSubhash.2084 SNo ratings yet

- UM_KCG2_002Document8 pagesUM_KCG2_002Subagyo AbimanyuNo ratings yet

- RED2501 DatasheetDocument12 pagesRED2501 DatasheetSujit ChatterjeeNo ratings yet

- BD99950MUVDocument37 pagesBD99950MUVevilplayerindoNo ratings yet

- SD6834 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage MosfetDocument10 pagesSD6834 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage Mosfetحسین مشعلNo ratings yet

- Low Power RegulatorDocument28 pagesLow Power RegulatorSagarNo ratings yet

- OB2203 On-BrightElectronicsDocument13 pagesOB2203 On-BrightElectronicsعلي محمدعبدالله الردينيNo ratings yet

- A05c 0S 000060 - Aoz2261nqi 11Document18 pagesA05c 0S 000060 - Aoz2261nqi 11Chiapin LeeNo ratings yet

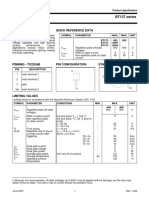

- BT137 PhiDocument6 pagesBT137 PhiJavierJBVNo ratings yet

- Wide Input Voltage, 3A, Switching Charger With NVDC Power Path Management For Single Cell Li+ BatteryDocument33 pagesWide Input Voltage, 3A, Switching Charger With NVDC Power Path Management For Single Cell Li+ Battery123No ratings yet

- EM8671ADocument13 pagesEM8671AHugo Monzon EspinosNo ratings yet

- Max 1879Document11 pagesMax 1879ВалераNo ratings yet

- Max77960 Max77961Document83 pagesMax77960 Max77961bubai karNo ratings yet

- OB2273A On BrightDocument10 pagesOB2273A On BrightHamza Abbasi AbbasiNo ratings yet

- DatasheetDocument10 pagesDatasheetDave DaveNo ratings yet

- Datasheet PDFDocument33 pagesDatasheet PDFPedro MoraNo ratings yet

- bq2031 PDFDocument21 pagesbq2031 PDFBruno PilzNo ratings yet

- Lead-Acid Fast-Charge IC: FeaturesDocument17 pagesLead-Acid Fast-Charge IC: FeaturesmoannaNo ratings yet

- BQ 2031Document21 pagesBQ 2031makerlog200No ratings yet

- Wide Input Voltage, 3A, Switching Charger With NVDC Power Path Management For Single Cell Li+ BatteryDocument33 pagesWide Input Voltage, 3A, Switching Charger With NVDC Power Path Management For Single Cell Li+ BatteryR hidayatNo ratings yet

- AP8269 AiTSemiconductorDocument11 pagesAP8269 AiTSemiconductorAlexandre Marido de AluguelNo ratings yet

- 200 KHZ, 1 A High Voltage Step-Down Switching Regulator: Data SheetDocument20 pages200 KHZ, 1 A High Voltage Step-Down Switching Regulator: Data SheetCarlos LesceNo ratings yet

- Triacs BT139 Series: General Description Quick Reference DataDocument6 pagesTriacs BT139 Series: General Description Quick Reference DataJose Luis SabinoNo ratings yet

- BM1513 EtcDocument7 pagesBM1513 EtcDimas BarretoNo ratings yet

- Acs 120Document17 pagesAcs 120Mafia BetawiNo ratings yet

- OB2362 DatasheetDocument10 pagesOB2362 DatasheetTín SmpsNo ratings yet

- Wap7 Testing DetailedDocument31 pagesWap7 Testing DetailedKrishna Mohan Chauhan100% (1)

- Max889 PDFDocument8 pagesMax889 PDFameer_jaburNo ratings yet

- General Description Features: High Performance Current Mode PWM ControllerDocument11 pagesGeneral Description Features: High Performance Current Mode PWM ControllerPhạm Tấn HảiNo ratings yet

- Sheet 12Document9 pagesSheet 12nlNo ratings yet

- KP2130 KiwiInstrumentsDocument12 pagesKP2130 KiwiInstrumentsAbab CscdNo ratings yet

- On-Bright Confidential To Bona: Quasi-Resonant Flyback PWM Controller General Description FeaturesDocument14 pagesOn-Bright Confidential To Bona: Quasi-Resonant Flyback PWM Controller General Description FeaturesFlavio Tonello TavaresNo ratings yet

- SCT12A2Document23 pagesSCT12A2ttNo ratings yet

- LNK305Document19 pagesLNK305PippoNo ratings yet

- AP8012ADocument13 pagesAP8012ASamerNo ratings yet

- BT138 SeriesDocument8 pagesBT138 SeriesYogi RuliemNo ratings yet

- 200Khz, 1.5A PWM Buck DC/DC Converter: General DescriptionDocument10 pages200Khz, 1.5A PWM Buck DC/DC Converter: General DescriptionagusnellNo ratings yet

- SOT23 Dual-Input USB/AC Adapter 1-Cell Li+ Battery Chargers: MAX1551/MAX1555Document8 pagesSOT23 Dual-Input USB/AC Adapter 1-Cell Li+ Battery Chargers: MAX1551/MAX1555123No ratings yet

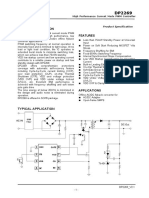

- DP2269Document7 pagesDP2269GABRIEL AMORIM ARAUJONo ratings yet

- HBG 100P (DA) SpecDocument7 pagesHBG 100P (DA) SpecmcincicNo ratings yet

- 60W Single Output With Battery Charger (UPS Function) : SeriesDocument3 pages60W Single Output With Battery Charger (UPS Function) : SeriesWafiq EidNo ratings yet

- Max 1679Document12 pagesMax 1679isaiasvaNo ratings yet

- 35553-USB Li BAT ChargerDocument34 pages35553-USB Li BAT ChargerHaidong KimNo ratings yet

- DS SG1846 Rev-1.2Document17 pagesDS SG1846 Rev-1.2Yuni MamaNo ratings yet

- Islic™: Intelligent Subscriber Line Interface CircuitDocument24 pagesIslic™: Intelligent Subscriber Line Interface CircuitMark MeiNo ratings yet

- D Data Sheet: BT131W SeriesDocument9 pagesD Data Sheet: BT131W Seriesuser_scribd54635No ratings yet

- Uc2842b-45b Uc3842b-45b STDocument15 pagesUc2842b-45b Uc3842b-45b STAлександр ФедорчукNo ratings yet

- BT137Document7 pagesBT137Gabriel RacovskyNo ratings yet

- A3959 DatasheetDocument12 pagesA3959 DatasheetOctavio ParedesNo ratings yet

- BAS19, BAS20, BAS21: Vishay SemiconductorsDocument4 pagesBAS19, BAS20, BAS21: Vishay SemiconductorsjicoelhoNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Mehra 1970Document10 pagesMehra 1970Imane IdrissiNo ratings yet

- FPGA-based System For Artificial Neural Network Arrhythmia ClassificationDocument16 pagesFPGA-based System For Artificial Neural Network Arrhythmia ClassificationGeraud Russel Goune ChenguiNo ratings yet

- FT Malcolm PDFDocument10 pagesFT Malcolm PDFHarlianNo ratings yet

- Oops in VBDocument31 pagesOops in VBMukesh sahaniNo ratings yet

- ATP Daily Report 11 September 2023Document96 pagesATP Daily Report 11 September 2023Hendra W.FNo ratings yet

- FINAAAAAL Converted3Document34 pagesFINAAAAAL Converted3Jhon larry DalisayNo ratings yet

- Presentation ON: Introduction To MicroprocessorDocument20 pagesPresentation ON: Introduction To MicroprocessorManish JangidNo ratings yet

- Basic Bot Guide Rev Part2Document41 pagesBasic Bot Guide Rev Part2tlaztec.llNo ratings yet

- Uf Sfm5020op4 Datasheet v1 0Document12 pagesUf Sfm5020op4 Datasheet v1 0Agung Arif Nur WibowoNo ratings yet

- Using Augmented Reality in Early Art Education: A Case Study in Hong Kong KindergartenDocument16 pagesUsing Augmented Reality in Early Art Education: A Case Study in Hong Kong KindergartenMohammed Mohammed Shoukry NaiemNo ratings yet

- Admin GuideDocument109 pagesAdmin GuiderodrigobarreiraNo ratings yet

- Abap TipsDocument322 pagesAbap TipsSiva SankarNo ratings yet

- Output Formats: Hematology AnalyzerDocument28 pagesOutput Formats: Hematology AnalyzerSilvio Luiz SalotiNo ratings yet

- NSO Day 3 and 4 Simple and Advanced ServicesDocument78 pagesNSO Day 3 and 4 Simple and Advanced ServicesAla JebnounNo ratings yet

- Panikian NHS FAR INSET 2022Document3 pagesPanikian NHS FAR INSET 2022Romnick PortillanoNo ratings yet

- Types of MediaDocument14 pagesTypes of MediaMary Quincy Marilao100% (1)

- BAHrain Lib SystemDocument15 pagesBAHrain Lib Systembgtes123No ratings yet

- 1997 Podlubny FO PIDDocument6 pages1997 Podlubny FO PIDfidelpaxoNo ratings yet

- A Study On Consumar Satisfaction Towords Google Pa1Document77 pagesA Study On Consumar Satisfaction Towords Google Pa1Avinash Channal100% (3)

- Fem TetrahedronDocument23 pagesFem TetrahedronvijayaragavanNo ratings yet

- Tailored Managing Safely v3.1 - ProjectDocument11 pagesTailored Managing Safely v3.1 - Projectghada gattouchNo ratings yet

- Tracking and Positioning of Mobile Systems in Telecommunication NetworksDocument15 pagesTracking and Positioning of Mobile Systems in Telecommunication NetworksLalit NayakNo ratings yet

- Three-Phase Grid-Tie Inverters: Conext CLDocument2 pagesThree-Phase Grid-Tie Inverters: Conext CLAdewale BamgbadeNo ratings yet

- 31504647-Antenna System (On Tower) Installation Standard ModelDocument27 pages31504647-Antenna System (On Tower) Installation Standard ModelBadr AmerNo ratings yet

- Component Technology Notes 3Document23 pagesComponent Technology Notes 3harsh vardhanNo ratings yet

- Eedt6usermanual PDFDocument36 pagesEedt6usermanual PDFhafiz arslanNo ratings yet

- Textbook Graph Structures For Knowledge Representation and Reasoning Madalina Croitoru Ebook All Chapter PDFDocument53 pagesTextbook Graph Structures For Knowledge Representation and Reasoning Madalina Croitoru Ebook All Chapter PDFrae.roman116100% (11)

- Plotly TutorialDocument95 pagesPlotly TutorialWeijie Chen100% (1)

R2A20052NS: Lithium-Ion Battery Charger IC With Auto Load Current Distribution

R2A20052NS: Lithium-Ion Battery Charger IC With Auto Load Current Distribution

Uploaded by

MauInfogames BancadaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

R2A20052NS: Lithium-Ion Battery Charger IC With Auto Load Current Distribution

R2A20052NS: Lithium-Ion Battery Charger IC With Auto Load Current Distribution

Uploaded by

MauInfogames BancadaCopyright:

Available Formats

Datasheet

R2A20052NS

R03DS0079EJ0200

Lithium-Ion Battery Charger IC with Auto load current distribution

Rev.2.00

May 7 ,2013

Description

R2J20052NS is a semiconductor integrated circuit designed for Lithium-ion battery charger control IC.

Built-in constant current and constant voltage control circuit suitable to charge Lithium-ion battery.

Built-in dual input (AC adaptor and USB) and dual output (system and battery) control circuit allows to supply the system

power and the battery charging power simultaneously from AC adaptor or USB power input.

The input current limitation of AC adaptor and USB can be set individually.

Built-in Low Ron MOSFET between the battery and the system realizes highly efficient power supply from the battery to

the system when both AC adaptor and USB are not connected or the system load exceeds input current limit.

Features

- Available for 1cell Li-ion Battery

- Adaptor or USB auto source selection

- Auto power path management between the system power supply and the battery charge

- Built-in Low Ron MOSFET between the system and the battery (38mohm)

- Input current limitation (ADP:2Amax, USB:100/500/900/1800mA)

- Compliance with PSE (Adjustable CC current/CV voltage by I2C)

- Charge control voltage : 4.2V+/-30mV (+/-0.7% precision)

- CC/CV charge control

- Chip temperature detection

- Thermal shutdown

- Safety timer

Application

- DSC

- Mobile phone

- PDA

- Portable audio player

- Handheld game machine

R03DS0079EJ0200 Rev.2.00 Page 1 of 20

May 7 ,2013

R2A20052NS

Block Diagram

BG

control SYS

ADP SYS

110kohm

Gate

Control 38mohm

Current

Limit BG

control

BG

control

Gate

BAT

USB Control BAT

110kohm CV

control

CC + BAT

control -

+ RICHG

-

Current

Limit

RILMTA

RICHG

Vref

BAT

Over voltage

detection

CEN1 L/S

Recharge

100kohm

detection

UCTL1 L/S Completion voltage

100kohm detection

USUSP1 L/S Trickle/Quick charge

100kohm Switch detection

LOGIC

TSD/Chip temperature detection

Reference voltage

Bias circuit

OSC ROSC

Vref

Charge start

BAT voltage

I2C

SDA

RICHG

Completion Registers SCL

Vref Current

+ detection

-

GND

At least one input of USB/ADP is needed to read/write I2C port.

R03DS0079EJ0200 Rev.2.00 Page 2 of 20

May 7 ,2013

R2A20052NS

Pin description

Pin No. Pin name I/O Description

1, 2 BAT O Battery connection terminal

5 USB I USB power input terminal

14 RILMTA I Resistor connection terminal for setting ADP input current limitation

Charge enable

7 CEN1 I

Low: Charge stop, High: Charge start (CEN2=“1”)

8 RICHG I Resistor connection terminal for setting charge current

USB input current limitation setting terminal

9 UCTL1 I

Low: 100mA max, High: 500mA max (USBMD=“0”)

13 GND - Ground

11 SCL I Serial clock input

10 SDA I/O Serial data input/output

USB suspend terminal

6 USUSP1 I

Low: USB input enable, High: USB input disable (USBMD=“0”)

12 ROSC I Resistor connection terminal for setting oscillation frequency

15 ADP I AC adaptor power input terminal

System power output (Each SYS terminal must be shortcircuited on the

17, 18 SYS O

board)

3, 4, 16 (NC) - No connection

PAD1 PAD1 O Must be connected to BAT plane

PAD2 PAD2 - Must be connected to Ground plane (for heat radiation)

Pin configuration

1 18 18 1

2 17 17 PAD1 2

3 16 16 3

4 15 15 4

5 14 14 5

6 13 13 6

PAD2

7 12 12 7

8 11 11 8

9 10 10 9

TOP VIEW BOTTOM VIEW

PKG : DFN-18 3.4mm x 4.5mm x 0.6mmt

R03DS0079EJ0200 Rev.2.00 Page 3 of 20

May 7 ,2013

R2A20052NS

Absolute maximum ratings

(Ta=25ºC, unless otherwise specified.)

Symbol Items Ratings Unit

Vmax Terminal voltage (All terminal) -0.3 ~ 6.5 V

IADPmax ADP terminal input current 2.5 A

IUSBmax USB terminal input current 2.0 A

ISYSmax SYS terminal output current 2.5 A

IBATmax BAT terminal input/output current 2.5 A

Topr Operating temperature range -30 ~ 85 ºC

Tstg Storage temperature range -40 ~ 125 ºC

Tj Maximum junction temperature 125 ºC

Pd* Power dissipation 2.67 W

*1) When using the glass epoxy board (50mm x 50mm x 1.6mm),

It is a value in the state that back die pad is connected to the board.

Ambient temperature [Ta]=25℃

Please note that Power dissipation changes on EVB condition.

3000

2750 2670mW

2500

Channel Dissipation Pch[W]

2250

2000

-26.7mW/℃

1750

1500

1250

1000 1067mW

750

500

250

0

0 25 50 75 85 100 125 150

Operating temperature Ta[℃]

Recommended operating condition

(Ta=25ºC, unless otherwise specified.)

Value

Symbol Item Unit

Min. Typ. Max.

VADP ADP input voltage 4.5 5.0 5.8 V

VUSB USB input voltage 4.5 5.0 5.8 V

VDVDD I/O voltage 1.5 - 5.5 V

IADP ADP input current - - 2.0 A

IUSB USB input current - - 1.8 A

R03DS0079EJ0200 Rev.2.00 Page 4 of 20

May 7 ,2013

R2A20052NS

Electrical Characteristics

(Ta=25ºC, VADP=5V or VUSB=5V, unless otherwise specified.)

Rated value

Item Symbol Condition Unit

Min. Typ. Max.

All

POKA(02H bit0), VBAT=3.5V

ADP input detection voltage VOKAL 4.2 4.3 4.4 V

300mV hysteresis

POKU(02H bit1), VBAT=3.5V

USB input detection voltage VOKUL 4.2 4.3 4.4 V

300mV hysteresis

ADP input circuit current ICCA Battery non-connection 2.5 mA

USB input circuit current ICCU Battery non-connection 2.5 mA

USB suspend current ICCUsus When USB input is suspended 1.8 mA

Battery discharge current ICCB When charging is completed 3 6 uA

Input high level

VINH 1.2 V

(CEN1,UCTL1, USUSP1)

Input Low level

VINL 0.5 V

(CEN1,UCTL1, USUSP1)

Input high level

VINH(I2C) 2.5 V

(SDA, SCL)

Input Low level

VINL(I2C) 0.3 V

(SDA, SCL)

SDA output Low level VOL_SDA Isource=3mA - - 0.6 V

On resistance between ADP and SYS RONA ISYS=200mA, When charging stops 0.3 0.45 ohm

On resistance between USB and SYS RONU ISYS=200mA, When charging stops 0.3 0.45 ohm

ADP current limit 1) ILIMA0 RILMTA=2.7Kohm, VSYS=4V *1 900 1000 1100 mA

RILMTA resistance range 1.3 30 kohm

ILIMU0 USB 1800mA Mode, VSYS=4V *1 1500 1710 1800 mA

ILIMU1 USB 900mA Mode, VSYS=4V *1 720 810 900 mA

USB current limit 1)

ILIMU2 USB 500mA Mode, VSYS=4V 440 470 500 mA

ILIMU3 USB 100mA Mode, VSYS=4V 80 90 100 mA

Input current soft start time 2) TSOFT *1 1.0 ms

Chip temperature detection Ttreg Chip temperature, 10ºC hysteresis *1 93 ºC

Chip temperature reset detection Ttrgrst Chip temperature *1 120 ºC

Thermal shutdown temperature Tsd Chip temperature, 10ºC hysteresis *1 150 ºC

*1 : design guarantee

1) Current limit value decreases when SYS<2.5V.

2) Soft start function doesn’t operate when switching input source (ADP/USB).

R03DS0079EJ0200 Rev.2.00 Page 5 of 20

May 7 ,2013

R2A20052NS

Electrical Characteristics

(Ta=25ºC, VADP=5V or VUSB=5V, unless otherwise specified.)

Rated value

Item Symbol Condition Unit

Min. Typ. Max.

Battery voltage detection block

Charge start voltage When battery voltage rising,

Vstart *2 1.4 1.5 1.6 V

(Overdischarge protection) 100mV hysteresis

When battery voltage rising,

Quick charge start voltage Vqchgon 2.9 3.0 3.1 V

100mV hysteresis

When battery voltage falling,

Recharge start voltage Vrechg 3.70 3.80 3.90 V

100mV hysteresis

Charge control voltage (4.00V) Vchg1 VCHG=4.00V 3.95 4.00 4.05 V

Charge control voltage (4.05V) Vchg2 VCHG=4.05V 4.00 4.05 4.10 V

Charge control voltage (4.10V) Vchg3 VCHG=4.10V 4.05 4.10 4.15 V

Charge control voltage (4.15V) Vchg4 VCHG=4.15V 4.10 4.15 4.20 V

Charge control voltage (4.20V) Vchg5 VCHG=4.20V 4.17 4.20 4.23 V

Overvoltage detection voltage Vov When battery voltage rising 4.27 4.35 4.43 V

Charge current detection block

Quick charge current (0.5C) Irapchg1 RICHG=2.7kohm, VBAT=3.5V 200 250 300 mA

Quick charge current (1.0C) Irapchg2 RICHG=2.7kohm, VBAT=3.5V 450 500 550 mA

Trickle charge current (0.1C) Iprechg RICHG=2.7kohm, VBAT=2.5V 25 50 75 mA

Charge completion current (0.1C) Ifc RICHG=2.7kohm, CV control 25 50 75 mA

Timer circuit block

Oscillation frequency Foc ROSC=110kohm 57.6 64 70.4 KHz

ROSC=110kohm, TIMER=normal

Trickle charge timer (normal) Tdchg1 Time from trickle charge start to *1 54 60 66 min

Quick charge start

ROSC=110kohm, TIMER=slow

Trickle charge timer (slow) Tdchg2 Time from trickle charge start to *1 216 240 264 min

Quick charge start

ROSC=110kohm, TIMER=normal

Quick charge timer (normal) Tchg1 Time from Quick charge start to *1 270 300 330 min

Charge completion

ROSC=110kohm, TIMER=slow

Quick charge timer (slow) Tchg2 Time from Quick charge start to *1 1080 1200 1320 min

Charge completion

*1 : design guarantee

*2 : Battery connection detection is shared

R03DS0079EJ0200 Rev.2.00 Page 6 of 20

May 7 ,2013

R2A20052NS

Electrical Characteristics

(Ta=25ºC, VADP=5V or VUSB=5V, unless otherwise specified.)

Rated value

Item Symbol Condition Unit

Min. Typ. Max.

Charge control blcok

Path SW On resistance between BAT BAT to SYS current =0.5A

Ronb1 38 mohm

and SYS VBAT=4.2V

USB 100mA mode, Isys=200mA,

Regulation voltage from BAT to SYS Vregb 100 mV

BAT=4V

R03DS0079EJ0200 Rev.2.00 Page 7 of 20

May 7 ,2013

R2A20052NS

I2C BUS Line Characteristics

Item Symbol Min. Max. Unit

SCL clock frequency fSCL 0 400 kHz

Bus free time between STOP condition and START condition tBUF 1.3 - s

START condition hold time

tHD:STA 0.6 - s

(After this period, the first clock pulse is generated)

SCL low period tLOW 1.3 - s

SCL high period tHIGH 0.6 - s

START condition setup time tSU:STA 0.6 - s

Data hold time tHD:DAT 0 0.9 s

Data setup time tSU:DAT 100 - ns

Rise time (SDA and SCL) tR - 300 ns

Fall time (SDA and SCL) tF - 300 ns

STOP condition setup time tSU:STO 0.6 - s

Bus line capacitive load Cb - 400 pF

Note : Above values are specified by VIHmin and VILmax.

I2C Timing Chart

tR, tF

tBUF

VIH

SDA

VIL

tHD:STA tSU:DAT tHD:DAT tSU:STA tSU:STO

VIH

SCL

VIL

tLOW

tHIGH

Start Start Stop Start

R03DS0079EJ0200 Rev.2.00 Page 8 of 20

May 7 ,2013

R2A20052NS

Digital Data Formats

1.Write mode: Data input from Master to R2J20052NS

FIRST LAST

S Slave address W A Register address A 8 bit data A P

2.Read mode: Data output from R2J20052NS to Master

(Master must input STOP condition without confirming Acknowledge bit when receiving last data.)

FIRST LAST

S Slave address R A Register address A 8 bit data A P

From Master to Slave(R2J20052NS)

From Slave(R2J20052NS) to Master

S : START condition

SDA goes High to Low when SCL=High.

Slave address

FIRST LAST

MSB LSB

0 0 1 1 0 1 1

W : Write (SDA=Low)

R : Read (SDA=High)

A : Acknowledge bit (Master must set SDA=Low whenever receive slave data)

*A : Master must input STOP condition without confirming Acknowledge bit when receiving last data

in read mode. (Set SDA=High)

Register Address

FIRST LAST

MSB LSB

A7 A6 A5 A4 A3 A2 A1 A0

Data

FIRST LAST

MSB LSB

D7 D6 D5 D4 D3 D2 D1 D0

P : STOP condition

SDA goes Low to High when SCL=High.

R03DS0079EJ0200 Rev.2.00 Page 9 of 20

May 7 ,2013

R2A20052NS

Timing chart when transmitting data to the I2C master from R2J20052NS

Conditions:Read [02H]

TOUT(Timeout)=H , /POKU=H(USB input voltage detect)=H

Acknowledge bit is outputted at

the rising of 8th Clk bit of the Data is transmitted synchronizing with falling of SCL.

register address .

SCL(master to slave)

Stop Bit

StartBit

Received data(master to slave) Acknowledge bit

Send data(slave to master)

Acknowledge bit

0 0 0 01 01 0

Acknowledge bit

Acknowledge bit is outputted at

th

the falling of 8 Clk bit of the

slave address .

Reception condition Reception condition Transmitting state Reception

condition

Transmitting state

R03DS0079EJ0200 Rev.2.00 Page 10 of 20

May 7 ,2013

R2A20052NS

Register Map

ADR Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

00H R/W (TEST2) (TEST1) (TEST0) VCHG ICHG

01H R/W USBMD FULMD TIMER UCTL2 CEN2

02H R VBATH NOBAT FULL TOUT TSD POKU POKA

03H R (TEST5) (TEST4) (TEST3) STAT3 STAT2 STAT1 STAT0

Note :

00H, 03H, and TEST0 ~ 6 : Must be set “0” (prohibited to use)

02H : Status Register (Read only)

0 1

POKA ADP voltage non-detection ADP voltage detection

POKU USB voltage non-detection USB voltage detection

TSD Nornal chip temperature Abnornal chip temperature(IC stop)

TOUT Timer OK Timer OUT (Charge stop)

FULL Charge non-completion Charge completion

NOBAT Battery detection Battery non-detection

VBATH Battery normal voltage Battery over voltage

Note:

- When charge stops(CEN1=L or CEN2=0), FULL and TOUT are fixed “0”.

- When USB suspend mode ([(USBMD=0 and USUSP1=H) or (USBMD=1 and USUSP2=1) ),

FULL, TOUT, and POKU are fixed “0” regardless of the charge condition.

03H : Charge status register (Read only)

STAT3 STAT2 STAT1 STAT0 Input Status

0 0 0 0 - Default

0 0 0 1 ADP Forced charge

0 0 1 0 ADP Trickle charge

0 0 1 1 ADP Quick charge

0 1 0 0 ADP High temp. charge-1

0 1 0 1 ADP High temp. charge-2

0 1 1 0 ADP Charge completion

0 1 1 1 ADP/USB Error

1 0 0 0 ADP/USB Battery non-connection

1 0 0 1 USB Forced charge

1 0 1 0 USB Trickle charge

1 0 1 1 USB Quick charge

1 1 0 0 USB High temp. charge-1

1 1 0 1 USB High temp. charge-2

1 1 1 0 USB Charge completion

R03DS0079EJ0200 Rev.2.00 Page 11 of 20

May 7 ,2013

R2A20052NS

Register setting

*:Default setting

ADR=00H ICHG Quick charge current Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

R/W * 0.5C X X X X X X X 0

1.0C X X X X X X X 1

VCHG Charge voltage Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

* 4.00V X X X X 0 0 0 X

4.05V X X X X 0 0 1 X

4.10V X X X X 0 1 0 X

4.15V X X X X 0 1 1 X

4.20V X X X X 1 0 0 X

ADR=01H CEN2 Charge enable Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

R/W Disable X X X X X X X 0

* Enable X X X X X X X 1

UCTL2 USB input current limit Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

* 100mA X X X X X 0 0 X

500mA X X X X X 0 1 X

900mA X X X X X 1 0 X

1800mA X X X X X 1 1 X

USUSP2 USB suspend control Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

* USB ENABLE X X X X 0 X X X

USB SUSPEND X X X X 1 X X X

TIMER Timer control Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

Disable(reset) X X 0 0 X X X X

* Enable(normal) X X 0 1 X X X X

Enable(slow) *2) X X 1 0 X X X X

Enable(count stop) *3) X X 1 1 X X X X

FULMD Operation after charge completion detection Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

* Stop charging X 0 X X X X X X

Continue to charge(inform FULL status) X 1 X X X X X X

USBMD USB control select Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

* Depend on UCTL1 terminal *1) 0 X X X X X X X

Depend on UCTL2 register *1) 1 X X X X X X X

*1) When USBMD=0, Terminal setting (UCTL1 and USUSP1) is valid.

When USBMD=1, Register setting (UCTL2 and SUSP2) is valid.

*2) Slow : 4 times of normal mode (Trickle charge timer=240min., Quick charge timer=1200min.)

*3) Count stop : Timer is suspended. (Not reset)

Truth table of CEN1 and CEN2 Truth table of USUSP1 and USUSP2

CEN1 CEN2 USUSP1 USUSP2 USBMD

Operation Operation

Terminal Register Terminal Register Register

Low 0 Charge disable Low - 0 USB normal

High 0 Charge disable High - 0 USB SUSPEND

Low 1 Charge disable

- 0 1 USB normal

High 1 Charge enable

- 1 1 USB SUSPEND

When ADP>VOKAL, IC operates normally regardless of USUSPx.

When USB SUSPEND, USB input is invalid.

R03DS0079EJ0200 Rev.2.00 Page 12 of 20

May 7 ,2013

R2A20052NS

Charge state diagram

Notes

All state 1) : Judged after 256ms delay time for preventing

erroneous detection. (Other is judged instantly)

ADP and USB:not detected [ADP < VOKAL and USB < VOKUL] Under line : Register

or 2) The state is not changed when VBAT>VSYS (Path

ADP:not detected, and USB:suspend SW=ON).

[ADP < VOKAL] and [(USBMD=0 and USUSP1=H) or (USBMD=1 and USUSP2=1) ] 3) Timer reset conditions

or a) When the state is changed from Error(07H) to

All state except “00H” Charge stop(CEN1=L or CEN2=0) Battery non-connection(08H)

b) When the state is changed from Error(07H) to

ADP<VOKAL and USB<VOKUL(00H)

0V < VBAT < Vstart c) All of the state change except the state change

caused by the chip temperature detection function

(inside of broken line).

Default (00H) d) Timer reset command input (ADR=01H,

DATA=xx00xxxx)

Vstart < VBAT <Vov

Battery non- 01H, 02H, 03H, 04H, 05H, and

06H state

connection(08H)

ADP:detected[ADP > [ADP input mode]

VOKAL]

and ADP:not detected[ADP < VOKAL]

VBAT < VSYS and

09H, 0AH, 0BH, 0CH, 0DH, USB:detected, and USB:valid

[USB > VOKUL] and [(USBMD=0 and USUSP1=L) or (USBMD=1 and USUSP2=0) ]

and 0EH state

and

[USB input mode] VBAT < VSYS

ADP:detected[ADP > VOKAL]

and

VBAT < VSYS

Forced charge (01H) All state Forced charge (09H)

0.3C: 64ms x 10=640ms 0.3C: 64ms x 10=640ms

Tj > Tsd

or

VBAT > Vov

Vstart < VBAT < Vqchgon Vstart < VBAT < Vqchgon

and and

VBAT < VSYS VBAT < VSYS

Vqchgon < VBAT < Vov Error(07H) Vqchgon < VBAT < Vov

and and

VBAT < VSYS VBAT < VSYS

Trickle charge (02H) Trickle charge (0AH)

Timer start Timer out[TOUT=1] Timer out[TOUT=1] Timer start

0.1C 0.1C

Vstart < VBAT < Vqchgon Vqchgon < VBAT < Vov Vstart < VBAT < Vqchgon Vqchgon < VBAT < Vov

and and and and

VBAT < VSYS VBAT < VSYS VBAT < VSYS VBAT < VSYS

Timer is not reset Timer is not reset

in the state in the state

Quick charge (03H) inside of broken line. inside of broken line. Quick charge (0BH)

Timer start Timer start

0.2C: 7.68s 0.2C: 7.68s

0.2C1.0C: 512ms x 48step=24.576s 0.2C1.0C: 512ms x 48step=24.576s

Tj < (Ttreg-Treghys) Ttrgrst < Tj < Tsd Tj < (Ttreg-Treghys) Ttrgrst < Tj < Tsd

Ttreg < Tj < Ttrgrst Tj < (Ttreg-Treghys) Ttreg < Tj < Ttrgrst Tj < (Ttreg-Treghys)

High temp. High temp. High temp. High temp.

charge1(04H) Ttrgrst < Tj < Tsd

charge2(05H) charge1(0CH) Ttrgrst < Tj < Tsd charge2(0DH)

Stop to increase 0.2C Stop to increase 0.2C

0.2C1.0C 0.2C1.0C

Ichg < Ifc Ichg < Ifc

and and

Vqchgon < VBAT < Vrechg Vrechg < VBAT < Vov Vqchgon < VBAT < Vrechg Vrechg < VBAT < Vov

and and and and

VBAT < VSYS FULMD=0 VBAT < VSYS FULMD=0

and and

VBAT < VSYS VBAT < VSYS

Vstart < VBAT < Vqchgon

Charge Charge

completion(06H) completion(0EH)

R03DS0079EJ0200 Rev.2.00 Page 13 of 20

May 7 ,2013

R2A20052NS

Recovery from Error status (07H)

Thermal shutdown

Once IC enters the error mode by thermal shutdown, IC cannot recover from the error mode automatically

even if chip temperature falls under tsd.

For recovering from the error mode, the recovery sequence is needed after chip temperature falls under tsd.

Battery over-voltage detection

Once IC enters the error mode by battery over-voltage, IC cannot recover from the error mode automatically

even if VBAT falls under Vov.

For recovering from the error mode, the recovery sequence is needed after VBAT falls under Vov.

Timer out

The recovery sequence is needed to reset timer and restart to charge after entering to the error mode by timer out.

*) The recovery sequence :

“Disconnect both ADP and USB (ADP < VOKAL and USB < VOKUL)” or

“Disconnect the battery (0V < VBAT < Vstart)”

R03DS0079EJ0200 Rev.2.00 Page 14 of 20

May 7 ,2013

R2A20052NS

Function

Power path control

Iin Iload

VSYS

SYS

ADP

USB System

Gate

Input Ichg control

Current Condition Path SW

limitation

VSYS > VBAT Off

Path

VSYS < VBAT On

CC/CV control SW Ibat

VBAT

BAT

Example of system current control

Conditions : USB=5.0V is connected, Iin_max=500mA, Ichg=350mA, Chargeable battery is connected

Current

System

Charge Input current Battery to system

current current (Iload) current

(Ichg) (Iin) (IBAT)

Iin_max

350mA

0mA

Time

VSYS

Input voltage

USB 5V

4.35V VBAT

VBAT-0.1V

Time

(1) (2) (3)

(1) IC charges the battery at Ichg=350mA and supplies the system current(Iload) within Iin_max=500mA.

(2) When the system current(Iload) increases and the total sum of Iload and Ichg reachs Iin_max,

IC reduces the charge current.. (the power not used by the system charges the battery)

(3) When the system current (Iload) increases more and Iload exceeds Iin_max,

VSYS falls to Vbat-0.1V and the battery supplies the load current to system through the Path SW.

(IC attempts to sustain the system voltage no matter what causes it to drop.)

R03DS0079EJ0200 Rev.2.00 Page 15 of 20

May 7 ,2013

R2A20052NS

Timing chart

BAT terminal voltage:

Actual battery voltage + internal resistance x charge current

4.2V

Battery voltage

3.8V

3.0V

Actual battery voltage

Quick charge

CC control CV control Re-charge

Quick charge current start

setting value(1.0C)

Charge

Charge

current

Ta=85ºC

0.3C Trickle completion

charge Ta=27 ºC current Re-charge

0.2C completion

Ta=0 ºC

Trickle charge

current(0.1C)

Charge

Forced charge

completion

Battery

Connection

detection

Trickle charge timer Timer stop

(60min.) progress flag

Quick charge timer

Timer stop Timer stop

(300min.) progress flag

Note:

During quick charge, junction temperature is monitored to limit charge current value between 0.2C-1.0C so that

the junction temperature may not exceed Ttreg.

R03DS0079EJ0200 Rev.2.00 Page 16 of 20

May 7 ,2013

R2A20052NS

Operating examination

ADP input current limit setting

ADP input current limit setting value =(Ref. voltage 1.44V/RILMTA[KΩ]) X (1800~2200*) (mA)

* coefficient changes by ADP input current limit setting value.

Standard characteristics of ADP input current limit (for reference)

RILMTA resister setting ADPinput current limit setting

(KΩ) (mA)

27.00 102

5.40 524

2.70 1024

1.80 1500

1.50 1784

1.35 1958

1.30 2035

Quick charging current setting (1.0C CC charging)

charging current 1.0C=(Ref, voltage 1.64V/RICHG[KΩ]) X (720~880*) (mA)

* coefficient changes by charging current.

Standard specification of charging current setting (for reference)

Quick charging current Ref. current RICHG resistance setting

setting(mA) (uA) value(kΩ)

1000 1280 1.28

900 1130 1.45

800 1000 1.64

700 870 1.89

600 720 2.28

500 608 2.70

400 482 3.40

300 361 4.54

200 241 6.80

Reference of ROSC setting resistance value, oscillation frequency and timer

Timer calculate value

ROSC oscillation

trickle charge trickle charge quick charge quick charge

resistance value frequency

timer60(min) timer240(min) timer300(min) timer1200(min)

(kΩ) (kHz)

(normal) (slow) (normal) (slow)

GND short 1172.0 3.3 13.1 16.4 65.5

10 419.6 9.2 36.6 45.8 183.0

20 264.0 14.5 58.2 72.7 290.9

55 116.6 32.9 131.7 164.6 658.5

110 64.0 60.0 240.0 300.0 1200.0

195 37.8 101.6 406.2 507.8 2031.0

510 15.4 249.0 995.9 1244.9 4979.5

R03DS0079EJ0200 Rev.2.00 Page 17 of 20

May 7 ,2013

R2A20052NS

Application circuit

Li-ion

Battery

pack

R2J20052NS SYS

1 BAT 18

SYSTEM

BAT SYS 17

1.28mm

2

C1 C4

2.2uF 10uF

NC

3 NC PAD1 16

ADP

C3

ADP 4.5~5.8V

4 NC 15 4.7uF

USB R3

4.5~5.8V USB RILMTA 14 2.7kohm

5

C2

4.7uF GND

6 USUSP1 13

2.78mm

7 CEN1 ROSC 12

R1 R2

2.7kohm RICHG SCL 11 110kohm

8

2.28mm

HOST SDA

9 UCTL1 PAD2

10

Note :

PAD1: Must be connected to BAT plane (Terminal-1,2)

PAD2: Must be connected to Ground plane (for heat radiation)

R03DS0079EJ0200 Rev.2.00 Page 18 of 20

May 7 ,2013

R2A20052NS

Notes on usage

1) SYS terminal must not be shortcircuited to GND. If SYS terminal is shortcircuited to GND when the battery is connected,

Large current may flow from BAT terminal to SYS terminal via Path SW(built-in 38mohm MOSFET).

If large current continues to flow, IC may be damaged seriously.

2) In case of FULMD=1, FULL register outputs “1” and IC continues to charge even if when charge current falls below 0.1C.

Host side needs to stop charging.

In this case, the safety timer is activated even if when charge current falls below 0.1C.

So charge operation is stopped after 300min quick charge timer.

But if TIMER register is set to Enable(count stop), charge operation is not stopped.

3) IC power dissipation must not exceed the package allowance power dissipation(Pd).

PAD2 must be soldered to large ground plane for heat radiation.

R03DS0079EJ0200 Rev.2.00 Page 19 of 20

May 7 ,2013

R2A20052NS

Package dimensions

UNIT:mm

R03DS0079EJ0200 Rev.2.00 Page 20 of 20

May 7 ,2013

You might also like

- 61863ev4 PDFDocument506 pages61863ev4 PDFAntonio LucasNo ratings yet

- PHIL ARTS - Elements and PrinciplesDocument25 pagesPHIL ARTS - Elements and PrinciplesmichelleNo ratings yet

- SD6835 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage MosfetDocument9 pagesSD6835 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage MosfetАлександр КачеишвилиNo ratings yet

- SD6832 SLDocument10 pagesSD6832 SLMuhammad IchsanNo ratings yet

- AX3005 AXEliteDocument11 pagesAX3005 AXElitebibib bibibNo ratings yet

- 150Khz, 3A PWM Buck DC/DC Converter: Advanced Power Electronics CorpDocument12 pages150Khz, 3A PWM Buck DC/DC Converter: Advanced Power Electronics CorpOjahan HNo ratings yet

- 500-kHz Half-Bridge DC-DC ConverterDocument17 pages500-kHz Half-Bridge DC-DC Converteratkxyz777100% (1)

- Ax 3001Document12 pagesAx 3001cuervituNo ratings yet

- Data SheetDocument30 pagesData SheetSubhash.2084 SNo ratings yet

- UM_KCG2_002Document8 pagesUM_KCG2_002Subagyo AbimanyuNo ratings yet

- RED2501 DatasheetDocument12 pagesRED2501 DatasheetSujit ChatterjeeNo ratings yet

- BD99950MUVDocument37 pagesBD99950MUVevilplayerindoNo ratings yet

- SD6834 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage MosfetDocument10 pagesSD6834 - Datasheet: Current Mode PWM+PFM Controller With Built-In High Voltage Mosfetحسین مشعلNo ratings yet

- Low Power RegulatorDocument28 pagesLow Power RegulatorSagarNo ratings yet

- OB2203 On-BrightElectronicsDocument13 pagesOB2203 On-BrightElectronicsعلي محمدعبدالله الردينيNo ratings yet

- A05c 0S 000060 - Aoz2261nqi 11Document18 pagesA05c 0S 000060 - Aoz2261nqi 11Chiapin LeeNo ratings yet

- BT137 PhiDocument6 pagesBT137 PhiJavierJBVNo ratings yet

- Wide Input Voltage, 3A, Switching Charger With NVDC Power Path Management For Single Cell Li+ BatteryDocument33 pagesWide Input Voltage, 3A, Switching Charger With NVDC Power Path Management For Single Cell Li+ Battery123No ratings yet

- EM8671ADocument13 pagesEM8671AHugo Monzon EspinosNo ratings yet

- Max 1879Document11 pagesMax 1879ВалераNo ratings yet

- Max77960 Max77961Document83 pagesMax77960 Max77961bubai karNo ratings yet

- OB2273A On BrightDocument10 pagesOB2273A On BrightHamza Abbasi AbbasiNo ratings yet

- DatasheetDocument10 pagesDatasheetDave DaveNo ratings yet

- Datasheet PDFDocument33 pagesDatasheet PDFPedro MoraNo ratings yet

- bq2031 PDFDocument21 pagesbq2031 PDFBruno PilzNo ratings yet

- Lead-Acid Fast-Charge IC: FeaturesDocument17 pagesLead-Acid Fast-Charge IC: FeaturesmoannaNo ratings yet

- BQ 2031Document21 pagesBQ 2031makerlog200No ratings yet

- Wide Input Voltage, 3A, Switching Charger With NVDC Power Path Management For Single Cell Li+ BatteryDocument33 pagesWide Input Voltage, 3A, Switching Charger With NVDC Power Path Management For Single Cell Li+ BatteryR hidayatNo ratings yet

- AP8269 AiTSemiconductorDocument11 pagesAP8269 AiTSemiconductorAlexandre Marido de AluguelNo ratings yet

- 200 KHZ, 1 A High Voltage Step-Down Switching Regulator: Data SheetDocument20 pages200 KHZ, 1 A High Voltage Step-Down Switching Regulator: Data SheetCarlos LesceNo ratings yet

- Triacs BT139 Series: General Description Quick Reference DataDocument6 pagesTriacs BT139 Series: General Description Quick Reference DataJose Luis SabinoNo ratings yet

- BM1513 EtcDocument7 pagesBM1513 EtcDimas BarretoNo ratings yet

- Acs 120Document17 pagesAcs 120Mafia BetawiNo ratings yet

- OB2362 DatasheetDocument10 pagesOB2362 DatasheetTín SmpsNo ratings yet

- Wap7 Testing DetailedDocument31 pagesWap7 Testing DetailedKrishna Mohan Chauhan100% (1)

- Max889 PDFDocument8 pagesMax889 PDFameer_jaburNo ratings yet

- General Description Features: High Performance Current Mode PWM ControllerDocument11 pagesGeneral Description Features: High Performance Current Mode PWM ControllerPhạm Tấn HảiNo ratings yet

- Sheet 12Document9 pagesSheet 12nlNo ratings yet

- KP2130 KiwiInstrumentsDocument12 pagesKP2130 KiwiInstrumentsAbab CscdNo ratings yet

- On-Bright Confidential To Bona: Quasi-Resonant Flyback PWM Controller General Description FeaturesDocument14 pagesOn-Bright Confidential To Bona: Quasi-Resonant Flyback PWM Controller General Description FeaturesFlavio Tonello TavaresNo ratings yet

- SCT12A2Document23 pagesSCT12A2ttNo ratings yet

- LNK305Document19 pagesLNK305PippoNo ratings yet

- AP8012ADocument13 pagesAP8012ASamerNo ratings yet

- BT138 SeriesDocument8 pagesBT138 SeriesYogi RuliemNo ratings yet

- 200Khz, 1.5A PWM Buck DC/DC Converter: General DescriptionDocument10 pages200Khz, 1.5A PWM Buck DC/DC Converter: General DescriptionagusnellNo ratings yet

- SOT23 Dual-Input USB/AC Adapter 1-Cell Li+ Battery Chargers: MAX1551/MAX1555Document8 pagesSOT23 Dual-Input USB/AC Adapter 1-Cell Li+ Battery Chargers: MAX1551/MAX1555123No ratings yet

- DP2269Document7 pagesDP2269GABRIEL AMORIM ARAUJONo ratings yet

- HBG 100P (DA) SpecDocument7 pagesHBG 100P (DA) SpecmcincicNo ratings yet

- 60W Single Output With Battery Charger (UPS Function) : SeriesDocument3 pages60W Single Output With Battery Charger (UPS Function) : SeriesWafiq EidNo ratings yet

- Max 1679Document12 pagesMax 1679isaiasvaNo ratings yet

- 35553-USB Li BAT ChargerDocument34 pages35553-USB Li BAT ChargerHaidong KimNo ratings yet

- DS SG1846 Rev-1.2Document17 pagesDS SG1846 Rev-1.2Yuni MamaNo ratings yet

- Islic™: Intelligent Subscriber Line Interface CircuitDocument24 pagesIslic™: Intelligent Subscriber Line Interface CircuitMark MeiNo ratings yet

- D Data Sheet: BT131W SeriesDocument9 pagesD Data Sheet: BT131W Seriesuser_scribd54635No ratings yet

- Uc2842b-45b Uc3842b-45b STDocument15 pagesUc2842b-45b Uc3842b-45b STAлександр ФедорчукNo ratings yet

- BT137Document7 pagesBT137Gabriel RacovskyNo ratings yet

- A3959 DatasheetDocument12 pagesA3959 DatasheetOctavio ParedesNo ratings yet

- BAS19, BAS20, BAS21: Vishay SemiconductorsDocument4 pagesBAS19, BAS20, BAS21: Vishay SemiconductorsjicoelhoNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Mehra 1970Document10 pagesMehra 1970Imane IdrissiNo ratings yet

- FPGA-based System For Artificial Neural Network Arrhythmia ClassificationDocument16 pagesFPGA-based System For Artificial Neural Network Arrhythmia ClassificationGeraud Russel Goune ChenguiNo ratings yet

- FT Malcolm PDFDocument10 pagesFT Malcolm PDFHarlianNo ratings yet

- Oops in VBDocument31 pagesOops in VBMukesh sahaniNo ratings yet

- ATP Daily Report 11 September 2023Document96 pagesATP Daily Report 11 September 2023Hendra W.FNo ratings yet

- FINAAAAAL Converted3Document34 pagesFINAAAAAL Converted3Jhon larry DalisayNo ratings yet

- Presentation ON: Introduction To MicroprocessorDocument20 pagesPresentation ON: Introduction To MicroprocessorManish JangidNo ratings yet

- Basic Bot Guide Rev Part2Document41 pagesBasic Bot Guide Rev Part2tlaztec.llNo ratings yet

- Uf Sfm5020op4 Datasheet v1 0Document12 pagesUf Sfm5020op4 Datasheet v1 0Agung Arif Nur WibowoNo ratings yet

- Using Augmented Reality in Early Art Education: A Case Study in Hong Kong KindergartenDocument16 pagesUsing Augmented Reality in Early Art Education: A Case Study in Hong Kong KindergartenMohammed Mohammed Shoukry NaiemNo ratings yet

- Admin GuideDocument109 pagesAdmin GuiderodrigobarreiraNo ratings yet

- Abap TipsDocument322 pagesAbap TipsSiva SankarNo ratings yet

- Output Formats: Hematology AnalyzerDocument28 pagesOutput Formats: Hematology AnalyzerSilvio Luiz SalotiNo ratings yet

- NSO Day 3 and 4 Simple and Advanced ServicesDocument78 pagesNSO Day 3 and 4 Simple and Advanced ServicesAla JebnounNo ratings yet

- Panikian NHS FAR INSET 2022Document3 pagesPanikian NHS FAR INSET 2022Romnick PortillanoNo ratings yet

- Types of MediaDocument14 pagesTypes of MediaMary Quincy Marilao100% (1)

- BAHrain Lib SystemDocument15 pagesBAHrain Lib Systembgtes123No ratings yet

- 1997 Podlubny FO PIDDocument6 pages1997 Podlubny FO PIDfidelpaxoNo ratings yet

- A Study On Consumar Satisfaction Towords Google Pa1Document77 pagesA Study On Consumar Satisfaction Towords Google Pa1Avinash Channal100% (3)

- Fem TetrahedronDocument23 pagesFem TetrahedronvijayaragavanNo ratings yet

- Tailored Managing Safely v3.1 - ProjectDocument11 pagesTailored Managing Safely v3.1 - Projectghada gattouchNo ratings yet

- Tracking and Positioning of Mobile Systems in Telecommunication NetworksDocument15 pagesTracking and Positioning of Mobile Systems in Telecommunication NetworksLalit NayakNo ratings yet

- Three-Phase Grid-Tie Inverters: Conext CLDocument2 pagesThree-Phase Grid-Tie Inverters: Conext CLAdewale BamgbadeNo ratings yet

- 31504647-Antenna System (On Tower) Installation Standard ModelDocument27 pages31504647-Antenna System (On Tower) Installation Standard ModelBadr AmerNo ratings yet

- Component Technology Notes 3Document23 pagesComponent Technology Notes 3harsh vardhanNo ratings yet

- Eedt6usermanual PDFDocument36 pagesEedt6usermanual PDFhafiz arslanNo ratings yet

- Textbook Graph Structures For Knowledge Representation and Reasoning Madalina Croitoru Ebook All Chapter PDFDocument53 pagesTextbook Graph Structures For Knowledge Representation and Reasoning Madalina Croitoru Ebook All Chapter PDFrae.roman116100% (11)

- Plotly TutorialDocument95 pagesPlotly TutorialWeijie Chen100% (1)