Professional Documents

Culture Documents

LPC1769 - 68 - 67 - 66 - 65 - 64 - 63 Product Data Sheet

LPC1769 - 68 - 67 - 66 - 65 - 64 - 63 Product Data Sheet

Uploaded by

vikkasOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

LPC1769 - 68 - 67 - 66 - 65 - 64 - 63 Product Data Sheet

LPC1769 - 68 - 67 - 66 - 65 - 64 - 63 Product Data Sheet

Uploaded by

vikkasCopyright:

Available Formats

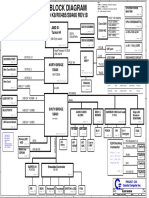

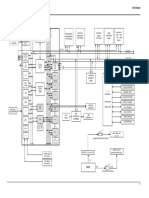

NXP Semiconductors LPC1769/68/67/66/65/64/63

32-bit ARM Cortex-M3 microcontroller

6. Block diagram

debug JTAG XTAL1

port interface RMII pins USB pins XTAL2

RESET

LPC1769/68/67/ USB PHY

TRACE MODULE

TEST/DEBUG

66/65/64/63 CLOCK

EMULATION

INTERFACE

GENERATION,

POWER CONTROL, CLKOUT

USB HOST/

ARM ETHERNET SYSTEM

MPU

DMA DEVICE/OTG

CORTEX-M3 CONTROLLER FUNCTIONS

CONTROLLER CONTROLLER

WITH DMA(1)

WITH DMA(1)

clocks and

I-code D-code system master master master controls

bus bus bus

slave

ROM

slave

MULTILAYER AHB MATRIX

SRAM 32/64 kB

FLASH

slave slave slave slave ACCELERATOR

P0 to HIGH-SPEED

P4 GPIO FLASH

AHB TO AHB TO

512/256/128 kB

APB APB

BRIDGE 0 BRIDGE 1 APB slave group 1 SCK0

SCK1 APB slave group 0

SSEL0

SSEL1 SSP0 MISO0

MISO1 SSP1

MOSI0

MOSI1

UART2/3 RXD2/3

RXD0/TXD0

UART0/1 TXD2/3

8 UART1

3 I2SRX

RD1/2

CAN1/2(1) I2S(1)

3 I2STX

TD1/2 TX_MCLK

SCL0/1 RX_MCLK

I2C0/1

SDA0/1

SCL2

SCK/SSEL I2C2

SPI0 SDA2

MOSI/MISO

2 MAT0/1 RI TIMER

TIMER 0/1 4 MAT2

2 CAP0/1

2 MAT3

WDT TIMER2/3 2 CAP2

2 CAP3

PWM1[7:0]

PWM1 EXTERNAL INTERRUPTS EINT[3:0]

PCAP1[1:0]

AD0[7:0] 12-bit ADC SYSTEM CONTROL

MCOA[2:0]

PIN CONNECT MCOB[2:0]

MOTOR CONTROL PWM

MCI[2:0]

P0, P2 MCABORT

GPIO INTERRUPT CONTROL

DAC(1) AOUT

RTCX1 32 kHz

OSCILLATOR RTC PHA, PHB

RTCX2 QUADRATURE ENCODER

INDEX

VBAT BACKUP REGISTERS

= connected to DMA

RTC POWER DOMAIN

002aad944

(1) Not available on all parts. See Table 2.

Fig 1. Block diagram

LPC1769_68_67_66_65_64_63 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2020. All rights reserved.

Product data sheet Rev. 9.10 — 8 September 2020 6 of 93

You might also like

- Elite 100 & 300 - Technical Reference Manual - (Secure) - BGX701-234-R01Document60 pagesElite 100 & 300 - Technical Reference Manual - (Secure) - BGX701-234-R01Anggara Kusuma75% (20)

- Ajax Spark Plug Installation ManualDocument16 pagesAjax Spark Plug Installation Manualzona amrullohNo ratings yet

- Heidelberg GTO Old Style PDFDocument88 pagesHeidelberg GTO Old Style PDFLuis Carlos Madera Carroll0% (1)

- 03 - Circuit DescriptionDocument37 pages03 - Circuit Descriptionkhoi vuNo ratings yet

- FM93C86A 16K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesFM93C86A 16K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- Adsp-Bf531 BF532 BF533Document64 pagesAdsp-Bf531 BF532 BF533庄仕贤No ratings yet

- FM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesFM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- Adsp 2181Document32 pagesAdsp 2181api-3774180No ratings yet

- Fm93c86an 177Document12 pagesFm93c86an 177ISAJEVS IGORSNo ratings yet

- NM93C66 4096-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesNM93C66 4096-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- Bremen 10G: MP Build (A02)Document63 pagesBremen 10G: MP Build (A02)Moh HamNo ratings yet

- NM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesNM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- Data SheetDocument52 pagesData SheetRohmad JayaNo ratings yet

- K4M563233G - F (H) N/G/L/F Mobile-SDRAMDocument12 pagesK4M563233G - F (H) N/G/L/F Mobile-SDRAMDVTNo ratings yet

- NM93C06 256-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesNM93C06 256-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)fabiansandezNo ratings yet

- Asus A8ES Laptop SchematicsDocument94 pagesAsus A8ES Laptop SchematicsftenminNo ratings yet

- SMT32F407xx System Block DiagramDocument1 pageSMT32F407xx System Block DiagramAlexander Martínez PasekNo ratings yet

- ADSP-BF592: Blackfin Embedded ProcessorDocument48 pagesADSP-BF592: Blackfin Embedded ProcessorOperador Transporte MetroviarioNo ratings yet

- Inventec Rotterdam 10AR RT10AR preMP 6050A2250801 20090409 GerberDocument66 pagesInventec Rotterdam 10AR RT10AR preMP 6050A2250801 20090409 GerberNarayana BharathyNo ratings yet

- Asus A8LeDocument94 pagesAsus A8LeAndriyNo ratings yet

- Industrial Reference Design Platform: Microcontroller CoreDocument22 pagesIndustrial Reference Design Platform: Microcontroller Coreakatyal225813No ratings yet

- STMicroelectronics STPCI2HEYCE DatasheetDocument108 pagesSTMicroelectronics STPCI2HEYCE DatasheetR4nd3lNo ratings yet

- DFT Architecture in Multimedia Design: Gil BouganimDocument17 pagesDFT Architecture in Multimedia Design: Gil BouganimDamodar Prasad SharmaNo ratings yet

- 10 - Block DiagramDocument2 pages10 - Block DiagramAivars LīpenītsNo ratings yet

- Atmel 44050 Cortex M7 Microcontroller SAM E70 XPLD Xplained User GuideDocument58 pagesAtmel 44050 Cortex M7 Microcontroller SAM E70 XPLD Xplained User Guidedomenico_leuzziNo ratings yet

- Scheme Acer Ferrari5000Document46 pagesScheme Acer Ferrari5000Fabio AntunesNo ratings yet

- DSP Microcomputer ADSP-2183Document31 pagesDSP Microcomputer ADSP-2183marcelogaztaNo ratings yet

- 01-Block DiagramDocument1 page01-Block Diagramkhoi vuNo ratings yet

- MAX 10 Nios II Embedded Evaluation Kit: Get in Touch With Your Inner NEEKDocument3 pagesMAX 10 Nios II Embedded Evaluation Kit: Get in Touch With Your Inner NEEKwroxtarNo ratings yet

- Dsa 00197882Document37 pagesDsa 00197882Raja ArumugamNo ratings yet

- UX50Document97 pagesUX50leonardo alfonsoNo ratings yet

- CHIP1Document40 pagesCHIP1Siva SreeramdasNo ratings yet

- 05 Block DiagramDocument2 pages05 Block DiagramSafi AlsafiNo ratings yet

- MCU KornilinDocument51 pagesMCU KornilinMaría SpínolaNo ratings yet

- Inventec Bremen 10 Bm10g 6050a2338401-A02 (Diagramas - Com.br)Document56 pagesInventec Bremen 10 Bm10g 6050a2338401-A02 (Diagramas - Com.br)edivan santosNo ratings yet

- A8s MB Rev-2-0Document94 pagesA8s MB Rev-2-0QuenitoLucianoJoãoNo ratings yet

- Toshiba L630 L635 Laptop Schematic PDFDocument56 pagesToshiba L630 L635 Laptop Schematic PDFcody 2No ratings yet

- MC68LC302: Low Cost Integrated Multiprotocol ProcessorDocument6 pagesMC68LC302: Low Cost Integrated Multiprotocol ProcessorYacine AlgersNo ratings yet

- Ipc3 Top Level Block DiagramDocument1 pageIpc3 Top Level Block DiagramRizqy Aulia RahmanNo ratings yet

- Platform NodeDocument5 pagesPlatform NodeCaraka TriNo ratings yet

- 06-Block DiagramDocument1 page06-Block Diagramadonay castilloNo ratings yet

- Block DiagramsDocument1 pageBlock DiagramssicmartinezNo ratings yet

- Blackfin Embedded Processor ADSP-BF534/ADSP-BF536/ADSP-BF537Document68 pagesBlackfin Embedded Processor ADSP-BF534/ADSP-BF536/ADSP-BF537mercdataNo ratings yet

- Embest S3CEV40 EVBDocument3 pagesEmbest S3CEV40 EVBChu Văn ThànhNo ratings yet

- Acer Aspire 3050 5050 - Quanta - ZF3Document37 pagesAcer Aspire 3050 5050 - Quanta - ZF3Acomputer NathonNo ratings yet

- ADSP-21060 21060L InstructionDocument47 pagesADSP-21060 21060L Instructionapi-3817711100% (4)

- Scheme Asus z99d PDFDocument94 pagesScheme Asus z99d PDFЮра ИвановNo ratings yet

- Inventec Berlin 10g Rx01 6050a2332301 SchematicsDocument67 pagesInventec Berlin 10g Rx01 6050a2332301 SchematicsGleison Gomes100% (1)

- AVRONEDocument11 pagesAVRONEmekki1No ratings yet

- 6050A2332301-MB-A02 Toshiba Satellite L650 SchematicDocument66 pages6050A2332301-MB-A02 Toshiba Satellite L650 SchematicAntonio Benitez100% (1)

- Adsp 2141LDocument39 pagesAdsp 2141Ljhon simsNo ratings yet

- Repair ManualDocument72 pagesRepair ManualsicmartinezNo ratings yet

- Acer Aspire 6920 - Inventec - Kilimanjaro - CS - RevX01Document59 pagesAcer Aspire 6920 - Inventec - Kilimanjaro - CS - RevX01Charly NitroNo ratings yet

- 1.9 Block Diagram: Philips SemiconductorsDocument1 page1.9 Block Diagram: Philips SemiconductorsutsabNo ratings yet

- Dell Inspiron 630M-XPS M140 (Wistron Barbados)Document44 pagesDell Inspiron 630M-XPS M140 (Wistron Barbados)Daniel Andres OrtegaNo ratings yet

- Adsp 2181Document32 pagesAdsp 2181api-3817711100% (3)

- MAX32520Document29 pagesMAX32520duval fortesNo ratings yet

- Sharc Processor ADSP-21369: Preliminary Technical DataDocument53 pagesSharc Processor ADSP-21369: Preliminary Technical DataWillian MarquesNo ratings yet

- Foxconn - 648m06 Rev BDocument41 pagesFoxconn - 648m06 Rev BArcangelsmNo ratings yet

- Bm94715eku RohmDocument27 pagesBm94715eku Rohmdaniel SNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Advanced Test Methods for SRAMs: Effective Solutions for Dynamic Fault Detection in Nanoscaled TechnologiesFrom EverandAdvanced Test Methods for SRAMs: Effective Solutions for Dynamic Fault Detection in Nanoscaled TechnologiesNo ratings yet

- M2017-0061 PB3S-22-26 Manual - Part IIDocument30 pagesM2017-0061 PB3S-22-26 Manual - Part IILe DuNo ratings yet

- Programming Amd'S Cmos EpromsDocument11 pagesProgramming Amd'S Cmos EpromsrwpaulaNo ratings yet

- KENR9408KENR9408 - SIS Mini JXMDocument4 pagesKENR9408KENR9408 - SIS Mini JXMLiliana Rebeca Santos santosNo ratings yet

- Aim6 Evening - 7.11.2018Document4 pagesAim6 Evening - 7.11.2018Mai UyênNo ratings yet

- L30-L75 Fixed Speed Rotary Screw Compressor BrochureDocument2 pagesL30-L75 Fixed Speed Rotary Screw Compressor BrochureSpark ElectricNo ratings yet

- ConCab Kabel GMBH Main Catalouge English 2005Document508 pagesConCab Kabel GMBH Main Catalouge English 2005Swen Braunreuter0% (1)

- N68SC-M3S 101112Document47 pagesN68SC-M3S 101112amatsuki46No ratings yet

- Woodworking Safety Unit CorrectDocument19 pagesWoodworking Safety Unit CorrectNidhinkorothNo ratings yet

- Bobcat Skid Steer 773 Parts Manual PDFDocument742 pagesBobcat Skid Steer 773 Parts Manual PDFAlejandro HernandezNo ratings yet

- Monorail SystemDocument62 pagesMonorail SystemAlisa MalaNo ratings yet

- 442Document11 pages442Najam SiddiquiNo ratings yet

- SMC Flow MeterDocument70 pagesSMC Flow MeterSagarkumar PanchalNo ratings yet

- Brochure Bac-7000 Vav Sb005cDocument2 pagesBrochure Bac-7000 Vav Sb005cAnabel Hernández DíazNo ratings yet

- The CF Engine Overview: Vehicle Engine Type Indication Performance Torque Emission Level Daf Cf65Document2 pagesThe CF Engine Overview: Vehicle Engine Type Indication Performance Torque Emission Level Daf Cf65James Kuah100% (1)

- Engineering Systems LTD.: PROJECT: 90KLPD Distillery Plant Section: Fermentation ClientDocument7 pagesEngineering Systems LTD.: PROJECT: 90KLPD Distillery Plant Section: Fermentation ClientS B DubalNo ratings yet

- Proxpro® Wiegand/Clock-And-Data: Installation GuideDocument14 pagesProxpro® Wiegand/Clock-And-Data: Installation GuideEdilma Calderón RomeroNo ratings yet

- MX921 Low Current Repeater SpecDocument5 pagesMX921 Low Current Repeater Specstato69No ratings yet

- Kaishan KT20Document1 pageKaishan KT20Машинари ПримNo ratings yet

- Shenzhen Phisung 4G Smart Dash Camera Product Catalog 202201Document9 pagesShenzhen Phisung 4G Smart Dash Camera Product Catalog 202201Minh Pham NgocNo ratings yet

- 40-Ipl32l-Pwg1xg China Psu PDFDocument3 pages40-Ipl32l-Pwg1xg China Psu PDFmarceloNo ratings yet

- Task SheetDocument10 pagesTask SheetSer Crz JyNo ratings yet

- AN108-Designing A Half Bridge Converter Using A CoreMaster E2000Q CoreDocument7 pagesAN108-Designing A Half Bridge Converter Using A CoreMaster E2000Q Coreatkxyz777No ratings yet

- Lighting Power Panel: Electrical Schematic DiagramDocument1 pageLighting Power Panel: Electrical Schematic DiagramBerlin Andrew SionNo ratings yet

- MEC v2 - MTS9000A V100R002C30 Telecom Power Installation Guide (MTS9516A-A... PDFDocument270 pagesMEC v2 - MTS9000A V100R002C30 Telecom Power Installation Guide (MTS9516A-A... PDFRodrigo Salas PizarroNo ratings yet

- Submitted by Amber Vasudeo Behre Bachelor of Engineering: Computer Science and EngineeringDocument27 pagesSubmitted by Amber Vasudeo Behre Bachelor of Engineering: Computer Science and EngineeringAnoop KeshariNo ratings yet

- Operation, Service & Parts Manual: Shaw-BoxDocument44 pagesOperation, Service & Parts Manual: Shaw-BoxwimguzNo ratings yet