Professional Documents

Culture Documents

Sri Venkateshwara College of Engineering: Usn: 1 V E IA Test-I

Sri Venkateshwara College of Engineering: Usn: 1 V E IA Test-I

Uploaded by

jaya sreeCopyright:

Available Formats

You might also like

- Sri Venkateshwara College of Engineering: Usn: 1 V E IA Test-IIDocument1 pageSri Venkateshwara College of Engineering: Usn: 1 V E IA Test-IIjaya sreeNo ratings yet

- 17ec63 Vlsi Design IIDocument1 page17ec63 Vlsi Design IIjaya sreeNo ratings yet

- Sri Venkateshwara College of EngineeringDocument1 pageSri Venkateshwara College of Engineeringjaya sreeNo ratings yet

- I) All Questions Are Compulsory. Ii) Figure To The Right Indicate Full Marks. Iii) Assume Suitable Data Wherever NecessaryDocument1 pageI) All Questions Are Compulsory. Ii) Figure To The Right Indicate Full Marks. Iii) Assume Suitable Data Wherever Necessarythamizharasi arulNo ratings yet

- JCS1029 Cga At1Document2 pagesJCS1029 Cga At1sinduja.cseNo ratings yet

- 1st Sem - ESEDocument8 pages1st Sem - ESEaditya ManhasNo ratings yet

- Model Question PaperDocument1 pageModel Question PaperV SATYA KISHORENo ratings yet

- Kamala Institute of Technology & Science, Singapur Iv B.Tech I Sem 1 Mid ExaminationDocument1 pageKamala Institute of Technology & Science, Singapur Iv B.Tech I Sem 1 Mid ExaminationKarthik NasaniNo ratings yet

- RF & MW Iat 1 QP 2019 Set1Document2 pagesRF & MW Iat 1 QP 2019 Set1formyphdNo ratings yet

- Vlsi Model Question Paper 1 (June 2021)Document3 pagesVlsi Model Question Paper 1 (June 2021)PushpalathaNo ratings yet

- Navkis College of Engineering, Hassan: Continuous Internal Evaluation - IIDocument1 pageNavkis College of Engineering, Hassan: Continuous Internal Evaluation - IImohan hsNo ratings yet

- VLSI Design Assignment-1Document1 pageVLSI Design Assignment-1educational9hubNo ratings yet

- Cadcam Iat - 2 Question PaperDocument1 pageCadcam Iat - 2 Question PaperSelvaraj GNo ratings yet

- Vlsi QB - 22-23 - Mid - NewDocument4 pagesVlsi QB - 22-23 - Mid - Newyadhardha LingalaNo ratings yet

- Vlsi Model Question Paper 3 (June 2021)Document4 pagesVlsi Model Question Paper 3 (June 2021)PushpalathaNo ratings yet

- Model CS3551 DC Set 2Document2 pagesModel CS3551 DC Set 2NambiRajaNo ratings yet

- CAE 1 & 2 PaperDocument9 pagesCAE 1 & 2 Paperlapaw11259No ratings yet

- New Horizon College of Engineering, Bangalore: 19CSE33 USNDocument12 pagesNew Horizon College of Engineering, Bangalore: 19CSE33 USNAhmad RazaNo ratings yet

- Mid Sem 1Document5 pagesMid Sem 1uttkarsh singhNo ratings yet

- DCC20063 Test 2 Dis 2020Document2 pagesDCC20063 Test 2 Dis 2020Debora Dujong Anak BelajaNo ratings yet

- EC8751 - Optical Communication - CIA 2 - S E T 1Document1 pageEC8751 - Optical Communication - CIA 2 - S E T 1xacasib574No ratings yet

- Previous Year Question PaperDocument11 pagesPrevious Year Question PaperMinuNo ratings yet

- Ec S8 - Acs 1 SeriesDocument1 pageEc S8 - Acs 1 SeriesAjay KumarNo ratings yet

- 21EC45T Control SystemDocument7 pages21EC45T Control SystemM.N.MD. FaheemNo ratings yet

- MP - Int - 2Document2 pagesMP - Int - 2MATHAN RAJ MNo ratings yet

- Kec 601 DCDocument5 pagesKec 601 DCakash kumarNo ratings yet

- BVLSI Descriptive 1st Mid 2023Document1 pageBVLSI Descriptive 1st Mid 2023N.RAMAKUMARNo ratings yet

- CT Assignment2Document1 pageCT Assignment2Asha RangaswamyNo ratings yet

- Course Instructor Course Coordinator Module Coordinator Approved by (M.Velumani) (M.Velumani) (M.Velumani) HOD/CivilDocument1 pageCourse Instructor Course Coordinator Module Coordinator Approved by (M.Velumani) (M.Velumani) (M.Velumani) HOD/CivilPrp PrpNo ratings yet

- Vlsi Model Question Paper 2 (June 2021)Document3 pagesVlsi Model Question Paper 2 (June 2021)PushpalathaNo ratings yet

- Vlsi Model 4-QPDocument2 pagesVlsi Model 4-QPsanthoshNo ratings yet

- Test 1 CMOS VLSI Design QP 11.1.22Document2 pagesTest 1 CMOS VLSI Design QP 11.1.22Chandru RamaswamyNo ratings yet

- All Sub Question Papers ETE Sem 1Document12 pagesAll Sub Question Papers ETE Sem 1aayusha766No ratings yet

- See Cmos Vlsi Jan 2020Document3 pagesSee Cmos Vlsi Jan 20201ms21ec132No ratings yet

- CAO IAT 2 QP 2019 Set 2Document2 pagesCAO IAT 2 QP 2019 Set 2formyphdNo ratings yet

- CIA - II - Cs8501 - Theory of Computation - CIA I - Set ADocument1 pageCIA - II - Cs8501 - Theory of Computation - CIA I - Set Asaran SanjayNo ratings yet

- Model Exam IVyrDocument3 pagesModel Exam IVyrsuriyakala vinothNo ratings yet

- Cadcam Iat - 3 Question PaperDocument1 pageCadcam Iat - 3 Question PaperSelvaraj GNo ratings yet

- 1.daa 2022 2Document31 pages1.daa 2022 20101191713No ratings yet

- Mohamed Sathak A J College of Engineering: Assessment - II Exam EC6701Document3 pagesMohamed Sathak A J College of Engineering: Assessment - II Exam EC6701formyphdNo ratings yet

- Ce8604 It 2Document2 pagesCe8604 It 2Bala AbimanyuNo ratings yet

- CO3 2. CO3 3. CO3 4. CO4 5. CO4:: Ce8604 - Highway Engineering Mrs. R.Anitha SelvakumariDocument2 pagesCO3 2. CO3 3. CO3 4. CO4 5. CO4:: Ce8604 - Highway Engineering Mrs. R.Anitha SelvakumariBala AbimanyuNo ratings yet

- 3 and 4 TH Unit Cloud Computing III YrDocument2 pages3 and 4 TH Unit Cloud Computing III Yrsuriyakala vinothNo ratings yet

- CS3351 - ModelDocument2 pagesCS3351 - Modelrkkumar07No ratings yet

- 18CV821 Design of Bridges Cie 2Document1 page18CV821 Design of Bridges Cie 2mohan hsNo ratings yet

- IAT 2 DSP Arch Set2Document1 pageIAT 2 DSP Arch Set2HemapriyaNo ratings yet

- Cadcam Iat - 1 Question PaperDocument2 pagesCadcam Iat - 1 Question PaperSelvaraj GNo ratings yet

- East West Institute of Technology: Department of Computer Science & EngineeringDocument2 pagesEast West Institute of Technology: Department of Computer Science & EngineeringgangambikaNo ratings yet

- UME1501Document3 pagesUME1501sk.yogesh waranNo ratings yet

- Series Test-Ii November - 2021: Ilm College of Engineering & TechnologyDocument2 pagesSeries Test-Ii November - 2021: Ilm College of Engineering & TechnologyHOD ILM aeroNo ratings yet

- 20itpc302 - Software EngineeringDocument3 pages20itpc302 - Software EngineeringHARIBABU N SEC 2020No ratings yet

- See Cmos VlsiDocument2 pagesSee Cmos Vlsi1ms21ec132No ratings yet

- Vlsi Cat 2Document2 pagesVlsi Cat 2Pradeep ravichanderNo ratings yet

- AIML_BCS302_1SCHDocument2 pagesAIML_BCS302_1SCHranjanNo ratings yet

- "Write Your Roll Number": DateDocument2 pages"Write Your Roll Number": DateWARRIOR GamingNo ratings yet

- Berm VDocument2 pagesBerm VInnocentvishwaNo ratings yet

- Iat I Set IiDocument2 pagesIat I Set IiarulsivagiriNo ratings yet

- Department of Computer Science & Engineering (Accredited by NBA)Document1 pageDepartment of Computer Science & Engineering (Accredited by NBA)Krishna Prasad BattulaNo ratings yet

- OOSE-Model Set 2Document2 pagesOOSE-Model Set 2suniesh2003No ratings yet

- Nanotechnology Commercialization: Manufacturing Processes and ProductsFrom EverandNanotechnology Commercialization: Manufacturing Processes and ProductsNo ratings yet

- Visvesvaraya Technological University Belagavi: House Price Prediction Using Machine LearningDocument9 pagesVisvesvaraya Technological University Belagavi: House Price Prediction Using Machine Learningjaya sreeNo ratings yet

- StructuresDocument15 pagesStructuresjaya sreeNo ratings yet

- Communication Systems, 5e: Chapter 6: Sampling and Pulse ModulationDocument45 pagesCommunication Systems, 5e: Chapter 6: Sampling and Pulse Modulationjaya sreeNo ratings yet

- 17ec63 Vlsi Design IIDocument1 page17ec63 Vlsi Design IIjaya sreeNo ratings yet

- Sri Venkateshwara College of Engineering: Usn: 1 V E IA Test-IIDocument1 pageSri Venkateshwara College of Engineering: Usn: 1 V E IA Test-IIjaya sreeNo ratings yet

- Sri Venkateshwara College of EngineeringDocument1 pageSri Venkateshwara College of Engineeringjaya sreeNo ratings yet

- Cmos Digital Vlsi Design: Combinational Logic Design-IVDocument14 pagesCmos Digital Vlsi Design: Combinational Logic Design-IVSrikanth PasumarthyNo ratings yet

- Tugas Vlsi: Nama: Fachmy Faizal P. Nim: 201310130311079 Kelas: T. Elektro 6BDocument11 pagesTugas Vlsi: Nama: Fachmy Faizal P. Nim: 201310130311079 Kelas: T. Elektro 6BpavelzaNo ratings yet

- Homework 1Document19 pagesHomework 1Shahin ShahNo ratings yet

- Designing of Multiplexer and De-Multiplexer Using Different Adiabatic Logic in 90nm TechnologyDocument7 pagesDesigning of Multiplexer and De-Multiplexer Using Different Adiabatic Logic in 90nm TechnologyAMIT VERMANo ratings yet

- Chapter 2 Modern CMOS Technology - IDocument20 pagesChapter 2 Modern CMOS Technology - Ifadwa badiNo ratings yet

- CG2027 0 Introduction 1 The DeviceDocument61 pagesCG2027 0 Introduction 1 The DevicePeng FeiNo ratings yet

- VLSI V Lab N-1Document20 pagesVLSI V Lab N-1Dhiraj PrakashNo ratings yet

- Mentor Graphics ProcedureDocument49 pagesMentor Graphics Proceduresai prasadNo ratings yet

- Tfss-Tf2106m-Tah C2836236Document16 pagesTfss-Tf2106m-Tah C2836236Diyan Budi SNo ratings yet

- Noc18 Ee33 Assignment5Document6 pagesNoc18 Ee33 Assignment5Hari PrasathNo ratings yet

- Low Power VLSI Circuits and Systems Prof. Ajit Pal Department of Computer Science and Engineering Indian Institute of Technology, KharagpurDocument23 pagesLow Power VLSI Circuits and Systems Prof. Ajit Pal Department of Computer Science and Engineering Indian Institute of Technology, KharagpurHimaja DasariNo ratings yet

- High-Speed Hybrid-Logic Full Adder Using High-Performance 10-T - CellDocument10 pagesHigh-Speed Hybrid-Logic Full Adder Using High-Performance 10-T - CellAnu SinghNo ratings yet

- VLSI Design Interview Questions With AnswersDocument27 pagesVLSI Design Interview Questions With AnswersNitya SiddagangappaNo ratings yet

- CMOS Static & Dynamic Logic Gates: NMOS Transistors in Series/Parallel ConnectionDocument11 pagesCMOS Static & Dynamic Logic Gates: NMOS Transistors in Series/Parallel Connectionlakshmi_innovatorNo ratings yet

- Zipper Cmos Logic CircuitDocument15 pagesZipper Cmos Logic CircuitShreerama Samartha G BhattaNo ratings yet

- Stick Diagrams and LayoutsDocument17 pagesStick Diagrams and LayoutsPraneetha InumarthiNo ratings yet

- A Comprehensive Delay Model For CMOS InvertersDocument8 pagesA Comprehensive Delay Model For CMOS InvertersSANT SARANNo ratings yet

- Design of Low Power and High Speed 4 Bit PDFDocument5 pagesDesign of Low Power and High Speed 4 Bit PDFneelima422No ratings yet

- CS/EE 5830/6830 - CAD Assignment #3Document9 pagesCS/EE 5830/6830 - CAD Assignment #3Yermakov Vadim IvanovichNo ratings yet

- 7 Logic FamiliesDocument5 pages7 Logic FamiliesWade DachNo ratings yet

- Ec1354 Vlsi by Suresh.mDocument75 pagesEc1354 Vlsi by Suresh.mSuresh Muthu100% (1)

- Dynamic CMOS Logic GateDocument14 pagesDynamic CMOS Logic GateAyush SharmaNo ratings yet

- (PPT) Noise and Matching in CMOS (Analog) CircuitsDocument49 pages(PPT) Noise and Matching in CMOS (Analog) CircuitsAdam112211No ratings yet

- CAD Tools (L-Edit) To Implement Layout DesignDocument4 pagesCAD Tools (L-Edit) To Implement Layout DesignRaja UmerNo ratings yet

- Ratioed Logic Design A Fast 6-Input AND Gate in Ea...Document4 pagesRatioed Logic Design A Fast 6-Input AND Gate in Ea...Divyansh JainNo ratings yet

- A Novel Three Transistor Sram Cell Design and AnalysisDocument9 pagesA Novel Three Transistor Sram Cell Design and AnalysisVijay UrkudeNo ratings yet

- Cmos Inverter Layout Tutorial: Prepared By: Eng. Hazem W. MararDocument12 pagesCmos Inverter Layout Tutorial: Prepared By: Eng. Hazem W. Mararkrsrajesh1No ratings yet

- Topic 3Document48 pagesTopic 3Saiful NizamNo ratings yet

- LEDITDocument18 pagesLEDITersharvanNo ratings yet

- CMOS IntroDocument45 pagesCMOS IntroNishanth Nish0% (1)

Sri Venkateshwara College of Engineering: Usn: 1 V E IA Test-I

Sri Venkateshwara College of Engineering: Usn: 1 V E IA Test-I

Uploaded by

jaya sreeOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sri Venkateshwara College of Engineering: Usn: 1 V E IA Test-I

Sri Venkateshwara College of Engineering: Usn: 1 V E IA Test-I

Uploaded by

jaya sreeCopyright:

Available Formats

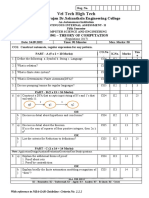

Format No ACD50

Date 01/08/2016

Sri Venkateshwara College of Engineering

INTERNAL ASSESSMENT TEST QUESTION PAPER Rev No. 01

Page 1 of 1

USN: 1 V E

CBCS SCHEME 2017

IA Test- I

Term: April-2021 to August-2021

Programme: Electronics & Communication Engineering Semester& Section: 6 - ‘A’ & ‘B’

Course Title : VLSI Design Date: 25/05/2021

Course Code: 17EC63 Time: 9.15 AM to 10.45 AM

Duration: 90 Minutes Maximum Marks: 30

Instructions: Answer THREE full questions, choosing ONE full question from each part. Use A4

sheets only.

Kx,

SL.NO Question Marks

COx

PART – I (20 Marks)

K2, Explain with a neat diagram enhancement mode transistor action of nMOS

a) CO363.1 transistor. 10

1 K2,

b) CO363.1

Describe the fabrication steps for nMOS transistor using a neat diagram 10

OR

K3, Derive the expression for drain to source current of nMOSFET

a) CO363.1 10

2 K3, With a neat circuit and sketch explain CMOS inverter DC characteristics by

b) CO363.1 mentioning all the operating regions 10

PART – II (10 Marks)

Using CMOS logic draw schematic and stick diagram for

K3, 10

3 a) (i) Y=

CO363.2

(ii) F =

OR

K3, Draw the design rule for pMOS, nMOS and CMOS 5

a) CO363.2

4

K3, Draw the schematic diagram and layout diagram for two input CMOS NOR 5

b) CO363.2 gate

COx- course outcome (1to5) Kx- blooms knowledge Level (K1, K2, K3, K4, K5, K6)

K1 – Remember K2 – Understand K3 – Apply K4 – Analyze K5 – Evaluate K6 – Create

CO No. Knowledge Max

COURSE OUTCOMES

XYZ.I Level Marks

C363.1 Understand the MOS transistor theory analyse the CMOS fabrication flow and

K2 40

technology scaling.

C363.2 Understand the stick and layout diagrams with the knowledge of physical design

aspects. K2 20

TOTAL 60

CXYZ.I : C – Course; X – YEAR; Y – SEMESTER; Z – Course Order; I- Order of CO

Scrutinizer Signature

You might also like

- Sri Venkateshwara College of Engineering: Usn: 1 V E IA Test-IIDocument1 pageSri Venkateshwara College of Engineering: Usn: 1 V E IA Test-IIjaya sreeNo ratings yet

- 17ec63 Vlsi Design IIDocument1 page17ec63 Vlsi Design IIjaya sreeNo ratings yet

- Sri Venkateshwara College of EngineeringDocument1 pageSri Venkateshwara College of Engineeringjaya sreeNo ratings yet

- I) All Questions Are Compulsory. Ii) Figure To The Right Indicate Full Marks. Iii) Assume Suitable Data Wherever NecessaryDocument1 pageI) All Questions Are Compulsory. Ii) Figure To The Right Indicate Full Marks. Iii) Assume Suitable Data Wherever Necessarythamizharasi arulNo ratings yet

- JCS1029 Cga At1Document2 pagesJCS1029 Cga At1sinduja.cseNo ratings yet

- 1st Sem - ESEDocument8 pages1st Sem - ESEaditya ManhasNo ratings yet

- Model Question PaperDocument1 pageModel Question PaperV SATYA KISHORENo ratings yet

- Kamala Institute of Technology & Science, Singapur Iv B.Tech I Sem 1 Mid ExaminationDocument1 pageKamala Institute of Technology & Science, Singapur Iv B.Tech I Sem 1 Mid ExaminationKarthik NasaniNo ratings yet

- RF & MW Iat 1 QP 2019 Set1Document2 pagesRF & MW Iat 1 QP 2019 Set1formyphdNo ratings yet

- Vlsi Model Question Paper 1 (June 2021)Document3 pagesVlsi Model Question Paper 1 (June 2021)PushpalathaNo ratings yet

- Navkis College of Engineering, Hassan: Continuous Internal Evaluation - IIDocument1 pageNavkis College of Engineering, Hassan: Continuous Internal Evaluation - IImohan hsNo ratings yet

- VLSI Design Assignment-1Document1 pageVLSI Design Assignment-1educational9hubNo ratings yet

- Cadcam Iat - 2 Question PaperDocument1 pageCadcam Iat - 2 Question PaperSelvaraj GNo ratings yet

- Vlsi QB - 22-23 - Mid - NewDocument4 pagesVlsi QB - 22-23 - Mid - Newyadhardha LingalaNo ratings yet

- Vlsi Model Question Paper 3 (June 2021)Document4 pagesVlsi Model Question Paper 3 (June 2021)PushpalathaNo ratings yet

- Model CS3551 DC Set 2Document2 pagesModel CS3551 DC Set 2NambiRajaNo ratings yet

- CAE 1 & 2 PaperDocument9 pagesCAE 1 & 2 Paperlapaw11259No ratings yet

- New Horizon College of Engineering, Bangalore: 19CSE33 USNDocument12 pagesNew Horizon College of Engineering, Bangalore: 19CSE33 USNAhmad RazaNo ratings yet

- Mid Sem 1Document5 pagesMid Sem 1uttkarsh singhNo ratings yet

- DCC20063 Test 2 Dis 2020Document2 pagesDCC20063 Test 2 Dis 2020Debora Dujong Anak BelajaNo ratings yet

- EC8751 - Optical Communication - CIA 2 - S E T 1Document1 pageEC8751 - Optical Communication - CIA 2 - S E T 1xacasib574No ratings yet

- Previous Year Question PaperDocument11 pagesPrevious Year Question PaperMinuNo ratings yet

- Ec S8 - Acs 1 SeriesDocument1 pageEc S8 - Acs 1 SeriesAjay KumarNo ratings yet

- 21EC45T Control SystemDocument7 pages21EC45T Control SystemM.N.MD. FaheemNo ratings yet

- MP - Int - 2Document2 pagesMP - Int - 2MATHAN RAJ MNo ratings yet

- Kec 601 DCDocument5 pagesKec 601 DCakash kumarNo ratings yet

- BVLSI Descriptive 1st Mid 2023Document1 pageBVLSI Descriptive 1st Mid 2023N.RAMAKUMARNo ratings yet

- CT Assignment2Document1 pageCT Assignment2Asha RangaswamyNo ratings yet

- Course Instructor Course Coordinator Module Coordinator Approved by (M.Velumani) (M.Velumani) (M.Velumani) HOD/CivilDocument1 pageCourse Instructor Course Coordinator Module Coordinator Approved by (M.Velumani) (M.Velumani) (M.Velumani) HOD/CivilPrp PrpNo ratings yet

- Vlsi Model Question Paper 2 (June 2021)Document3 pagesVlsi Model Question Paper 2 (June 2021)PushpalathaNo ratings yet

- Vlsi Model 4-QPDocument2 pagesVlsi Model 4-QPsanthoshNo ratings yet

- Test 1 CMOS VLSI Design QP 11.1.22Document2 pagesTest 1 CMOS VLSI Design QP 11.1.22Chandru RamaswamyNo ratings yet

- All Sub Question Papers ETE Sem 1Document12 pagesAll Sub Question Papers ETE Sem 1aayusha766No ratings yet

- See Cmos Vlsi Jan 2020Document3 pagesSee Cmos Vlsi Jan 20201ms21ec132No ratings yet

- CAO IAT 2 QP 2019 Set 2Document2 pagesCAO IAT 2 QP 2019 Set 2formyphdNo ratings yet

- CIA - II - Cs8501 - Theory of Computation - CIA I - Set ADocument1 pageCIA - II - Cs8501 - Theory of Computation - CIA I - Set Asaran SanjayNo ratings yet

- Model Exam IVyrDocument3 pagesModel Exam IVyrsuriyakala vinothNo ratings yet

- Cadcam Iat - 3 Question PaperDocument1 pageCadcam Iat - 3 Question PaperSelvaraj GNo ratings yet

- 1.daa 2022 2Document31 pages1.daa 2022 20101191713No ratings yet

- Mohamed Sathak A J College of Engineering: Assessment - II Exam EC6701Document3 pagesMohamed Sathak A J College of Engineering: Assessment - II Exam EC6701formyphdNo ratings yet

- Ce8604 It 2Document2 pagesCe8604 It 2Bala AbimanyuNo ratings yet

- CO3 2. CO3 3. CO3 4. CO4 5. CO4:: Ce8604 - Highway Engineering Mrs. R.Anitha SelvakumariDocument2 pagesCO3 2. CO3 3. CO3 4. CO4 5. CO4:: Ce8604 - Highway Engineering Mrs. R.Anitha SelvakumariBala AbimanyuNo ratings yet

- 3 and 4 TH Unit Cloud Computing III YrDocument2 pages3 and 4 TH Unit Cloud Computing III Yrsuriyakala vinothNo ratings yet

- CS3351 - ModelDocument2 pagesCS3351 - Modelrkkumar07No ratings yet

- 18CV821 Design of Bridges Cie 2Document1 page18CV821 Design of Bridges Cie 2mohan hsNo ratings yet

- IAT 2 DSP Arch Set2Document1 pageIAT 2 DSP Arch Set2HemapriyaNo ratings yet

- Cadcam Iat - 1 Question PaperDocument2 pagesCadcam Iat - 1 Question PaperSelvaraj GNo ratings yet

- East West Institute of Technology: Department of Computer Science & EngineeringDocument2 pagesEast West Institute of Technology: Department of Computer Science & EngineeringgangambikaNo ratings yet

- UME1501Document3 pagesUME1501sk.yogesh waranNo ratings yet

- Series Test-Ii November - 2021: Ilm College of Engineering & TechnologyDocument2 pagesSeries Test-Ii November - 2021: Ilm College of Engineering & TechnologyHOD ILM aeroNo ratings yet

- 20itpc302 - Software EngineeringDocument3 pages20itpc302 - Software EngineeringHARIBABU N SEC 2020No ratings yet

- See Cmos VlsiDocument2 pagesSee Cmos Vlsi1ms21ec132No ratings yet

- Vlsi Cat 2Document2 pagesVlsi Cat 2Pradeep ravichanderNo ratings yet

- AIML_BCS302_1SCHDocument2 pagesAIML_BCS302_1SCHranjanNo ratings yet

- "Write Your Roll Number": DateDocument2 pages"Write Your Roll Number": DateWARRIOR GamingNo ratings yet

- Berm VDocument2 pagesBerm VInnocentvishwaNo ratings yet

- Iat I Set IiDocument2 pagesIat I Set IiarulsivagiriNo ratings yet

- Department of Computer Science & Engineering (Accredited by NBA)Document1 pageDepartment of Computer Science & Engineering (Accredited by NBA)Krishna Prasad BattulaNo ratings yet

- OOSE-Model Set 2Document2 pagesOOSE-Model Set 2suniesh2003No ratings yet

- Nanotechnology Commercialization: Manufacturing Processes and ProductsFrom EverandNanotechnology Commercialization: Manufacturing Processes and ProductsNo ratings yet

- Visvesvaraya Technological University Belagavi: House Price Prediction Using Machine LearningDocument9 pagesVisvesvaraya Technological University Belagavi: House Price Prediction Using Machine Learningjaya sreeNo ratings yet

- StructuresDocument15 pagesStructuresjaya sreeNo ratings yet

- Communication Systems, 5e: Chapter 6: Sampling and Pulse ModulationDocument45 pagesCommunication Systems, 5e: Chapter 6: Sampling and Pulse Modulationjaya sreeNo ratings yet

- 17ec63 Vlsi Design IIDocument1 page17ec63 Vlsi Design IIjaya sreeNo ratings yet

- Sri Venkateshwara College of Engineering: Usn: 1 V E IA Test-IIDocument1 pageSri Venkateshwara College of Engineering: Usn: 1 V E IA Test-IIjaya sreeNo ratings yet

- Sri Venkateshwara College of EngineeringDocument1 pageSri Venkateshwara College of Engineeringjaya sreeNo ratings yet

- Cmos Digital Vlsi Design: Combinational Logic Design-IVDocument14 pagesCmos Digital Vlsi Design: Combinational Logic Design-IVSrikanth PasumarthyNo ratings yet

- Tugas Vlsi: Nama: Fachmy Faizal P. Nim: 201310130311079 Kelas: T. Elektro 6BDocument11 pagesTugas Vlsi: Nama: Fachmy Faizal P. Nim: 201310130311079 Kelas: T. Elektro 6BpavelzaNo ratings yet

- Homework 1Document19 pagesHomework 1Shahin ShahNo ratings yet

- Designing of Multiplexer and De-Multiplexer Using Different Adiabatic Logic in 90nm TechnologyDocument7 pagesDesigning of Multiplexer and De-Multiplexer Using Different Adiabatic Logic in 90nm TechnologyAMIT VERMANo ratings yet

- Chapter 2 Modern CMOS Technology - IDocument20 pagesChapter 2 Modern CMOS Technology - Ifadwa badiNo ratings yet

- CG2027 0 Introduction 1 The DeviceDocument61 pagesCG2027 0 Introduction 1 The DevicePeng FeiNo ratings yet

- VLSI V Lab N-1Document20 pagesVLSI V Lab N-1Dhiraj PrakashNo ratings yet

- Mentor Graphics ProcedureDocument49 pagesMentor Graphics Proceduresai prasadNo ratings yet

- Tfss-Tf2106m-Tah C2836236Document16 pagesTfss-Tf2106m-Tah C2836236Diyan Budi SNo ratings yet

- Noc18 Ee33 Assignment5Document6 pagesNoc18 Ee33 Assignment5Hari PrasathNo ratings yet

- Low Power VLSI Circuits and Systems Prof. Ajit Pal Department of Computer Science and Engineering Indian Institute of Technology, KharagpurDocument23 pagesLow Power VLSI Circuits and Systems Prof. Ajit Pal Department of Computer Science and Engineering Indian Institute of Technology, KharagpurHimaja DasariNo ratings yet

- High-Speed Hybrid-Logic Full Adder Using High-Performance 10-T - CellDocument10 pagesHigh-Speed Hybrid-Logic Full Adder Using High-Performance 10-T - CellAnu SinghNo ratings yet

- VLSI Design Interview Questions With AnswersDocument27 pagesVLSI Design Interview Questions With AnswersNitya SiddagangappaNo ratings yet

- CMOS Static & Dynamic Logic Gates: NMOS Transistors in Series/Parallel ConnectionDocument11 pagesCMOS Static & Dynamic Logic Gates: NMOS Transistors in Series/Parallel Connectionlakshmi_innovatorNo ratings yet

- Zipper Cmos Logic CircuitDocument15 pagesZipper Cmos Logic CircuitShreerama Samartha G BhattaNo ratings yet

- Stick Diagrams and LayoutsDocument17 pagesStick Diagrams and LayoutsPraneetha InumarthiNo ratings yet

- A Comprehensive Delay Model For CMOS InvertersDocument8 pagesA Comprehensive Delay Model For CMOS InvertersSANT SARANNo ratings yet

- Design of Low Power and High Speed 4 Bit PDFDocument5 pagesDesign of Low Power and High Speed 4 Bit PDFneelima422No ratings yet

- CS/EE 5830/6830 - CAD Assignment #3Document9 pagesCS/EE 5830/6830 - CAD Assignment #3Yermakov Vadim IvanovichNo ratings yet

- 7 Logic FamiliesDocument5 pages7 Logic FamiliesWade DachNo ratings yet

- Ec1354 Vlsi by Suresh.mDocument75 pagesEc1354 Vlsi by Suresh.mSuresh Muthu100% (1)

- Dynamic CMOS Logic GateDocument14 pagesDynamic CMOS Logic GateAyush SharmaNo ratings yet

- (PPT) Noise and Matching in CMOS (Analog) CircuitsDocument49 pages(PPT) Noise and Matching in CMOS (Analog) CircuitsAdam112211No ratings yet

- CAD Tools (L-Edit) To Implement Layout DesignDocument4 pagesCAD Tools (L-Edit) To Implement Layout DesignRaja UmerNo ratings yet

- Ratioed Logic Design A Fast 6-Input AND Gate in Ea...Document4 pagesRatioed Logic Design A Fast 6-Input AND Gate in Ea...Divyansh JainNo ratings yet

- A Novel Three Transistor Sram Cell Design and AnalysisDocument9 pagesA Novel Three Transistor Sram Cell Design and AnalysisVijay UrkudeNo ratings yet

- Cmos Inverter Layout Tutorial: Prepared By: Eng. Hazem W. MararDocument12 pagesCmos Inverter Layout Tutorial: Prepared By: Eng. Hazem W. Mararkrsrajesh1No ratings yet

- Topic 3Document48 pagesTopic 3Saiful NizamNo ratings yet

- LEDITDocument18 pagesLEDITersharvanNo ratings yet

- CMOS IntroDocument45 pagesCMOS IntroNishanth Nish0% (1)