Professional Documents

Culture Documents

Incet 2021

Incet 2021

Uploaded by

Raga SinghOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Incet 2021

Incet 2021

Uploaded by

Raga SinghCopyright:

Available Formats

Hybrid Symmetrical Cascaded Multilevel Inverter having reduced number of

Switches and DC Sources

Abstract – Research in several new topologies of Multilevel It has two voltage sources V1 and V2 along with two

inverter(MLI) has been carried ou t rapidly day by day. capacitors C1 and C2 which act like voltage divider circuit[6].

Recently several topologies have been introduced achieving If the values of V1 =V2 it is treated as symmetrical otherwise

higher levels with reduced device counts and DC sources .In asymmetrical. Existing Topology produces 7/9/11 levels with

this paper a new hybrid symmetric MLI is proposed .This certain voltage combinations[10].

topology has reduced number of controlled switches, DC sources

and numbers of capacitors which are very less compared to all S3

the conventional topologies existed before. It reduces

cost,size,complexity and hence enhances inverter efficiency. S5

S1

C1

Index Terms – Symmetric MLI, Asymmetric MLI ,Hybrid D1 D2

topology, THD, Modulation Index(MI)

V1 S7 LOAD V2

I. INTRODUCTION

D3 D4

As the MLI has less THD and less switching losses it C1 S2 S6

receives demanding popularity in terms of topology and in

control scheme in the field of medium voltage, high power

Dc/Ac conversion system[1].The traditional MLIs are of S4

various types and many of the literature are published with Fig. 1. Existing Topology

respect to their advantages and disadvantages [2].Among all

the existing topologies cascaded Multilevel inverter(CMLI)is For 7 level asymmetrical V1=2V, V2=V and Vdc=V.

popular because of its simplicity but it requires a number of For 9 level symmetrical V1=V2=V.For 11 level

isolated Dc sources[3].On the basis of the Dc source voltages asymmetrical V1=4V, V2=V in this existing topology

the CMLI are of two types i.e Symmetrical MLI and

Asymmetrical MLI[4].From last few years different B. Modified Topology

topologies have been developed by utilizing unidirectional The existing topology shown in fig.1 produces upto 11

and bidirectional switches [5]-[7].Though by the levels only. To generate higher levels this fig. 2 is not at all

implementation of asymmetrical MLI the number of levels suitable. Hence in order to generate higher levels fig. 2 has

increases giving reduced THD ,asymmetric converter is not been proposed. It is a modified topology having two voltage

really appreciated because they are not suitable for high sources, four capacitors, two bi directional switches and six

voltage industrial application for its variable DC sources.[8]- unidirectional switches.

[9].However the proposed topology can be hybridized further

to achieve higher levels[10]. .

II. RESEARCH METHOD

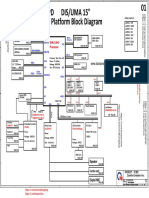

A. Existing Topology

S7

S1 S3

C1 C2

D1 D2 D5 D7

V1 S5 LOAD S6 V2

S7 D3 D4 D6 D8

C1 S4 S2 C2

S1 S3

C1 C2 S8

S77

D1 D2 D5 D7

S11 S33

C1 C2

V1 S5 LOAD S6 V2 D11 D22 D55 D77

S55 S66 V2

D3 D4 D6 D8

V1 D33 D44 D66 D88

C1 S4 S2 C2

C1 S44 S22 C2

S88

S8

Fig.2 Modified Topology

Table 1.Switching States

Fig 3. Hybrid Topology

Table 2. Switching States

Output voltages Conducting switches

Vdc S5,S8,S2,S44,S88,S22

2Vdc S8,S4,S44,S88,S22,S3

3Vdc S5,S8,S44,S88,S22,S3

4Vdc S8,S1,S44,S88,S22,S3

5Vdc S8,S11,S55,S88,S22,S3

6Vdc S8,S1,S44,S88,S33,S3

7Vdc S8,S1,S55,S88,S33,S3

8Vdc S8,S1,S11,S88,S33,S3

The modified topology produces switching states as 0 S4,S8,S2,S44,S88,S22

mentioned in table 1. This section of the paper represents -Vdc S5,S7,S3,S11,S77,S33

various switching states of proposed asymmetrical cascaded -2Vdc S1,S7,S2,S11,S77,S33

MLI. It shows V 1=V/2, V2=V where V dc =V/4 to generate -3Vdc S5,S7,S2,S11,S77,S33

13 levels which is called as binary asymmetrical configuration -4Vdc S4,S7,S2,S11,S77,S33

and V1=V, V2=3V w h i c h i s c a l l e d a s t r i n a r y

a s y m m e t r i c a l c o n f i g u r a t i o n where V dc =V/2, to -5Vdc S4,S7,S2,S55,S77,S33

-6Vdc S4,S7,S2,S11,S77,S22

generate 17 levels..

-7Vdc S4,S7,S2,S55,S77,S22

C. Hybrid Topology -8Vdc S4,S7,S2,S44,S77,S22

Two or more basic units can be added as shown in fig.3 to A MLI produces a stepped output voltage by additive or

achieve higher levels.The switching states of the topology has subtractive combination of input DC source voltages. Thus

been represented in Table 2.It represents the symmetrical the voltage wave form consists of multiple levels with both

configuration where all the source voltages are same in positive and negative polarities. The proposed topology can

magnitude.V1=V2=V and Vdc=V/2.In his case all he voltage be applied in higher voltage application by reducing the

sources are equal in magnitude giving symmetrical problem of voltage stress across the switch.

configuration of cascaded multilevel inverter.

D. Equations For Hybrid Topology

If N=No. of levels,

Total number of controlled switches required=(N-1)

(1)

Total numbers of diodes required=(5/4) х (N-1)

(2)

Total number of DC sources required=(1/4) х (N-1) shown in fig. 5. Fig. 6 and Fig.7 represents the voltage

(3) and current THD of the hybrid topology.

Total number of capacitors required=(1/2) х (N-1)

(4)

III. MATLAB SIMULATION

A.MODIFIED TOPOLOGY

(a) and (b)

Fig.4. (a) Out put voltage and current for 13 level Fig 5(a) Output voltage and current in R-Load

and Fig.5(b) Output voltage and current in RL-Load

Fig.4 (b)Out put voltage and current for 17 level

The levels have been simulated in MATLAB 13

version.The output voltage and current are obtained as

mentioned in fig.4.As the number of levels increases due to

unsymmetrical voltage combination the waveforms become

more sinusoidal reducing THD.Load is RL load having

R=10Ω and L=25mHwhere carrier frequency is 10KHz.

Table 3. Current THD for 13 level and 17 level

Carrier Frequency ITHD(13 level) ITHD(17 level)

in KHz

1 1.91 1.1 Fig.6(a)Voltage THD

3 1.45 0.98

5 1.05 0.91

7 0.94 0.82

10 0.81 0.74

B.Hybrid Topology

Same load is also connected with the hybrid topology in

symmetrical configuration .The results are obtained as

Fig. 6(b)Current THD

Table 4. Carrier Frequencies vs THDs

Carrier V O/P in IO/P in VTHD ITHD Fig.7(b)VTHD vs Modulation Index

frequency Volt Ampere .

in KHz IV. CONCLUSION

1 37.29 2.93 7.05 1.61 In this paper a hybrid topology and again how it can be

3 37.5 2.91 7.81 1.34 analyzed has been discussed. The hybrid topology has been

5 37.67 2.96 8.15 0.96 compared with other topologies mentioned in the literature

survey. It has been concluded that with other existed

7 37.68 2.95 9.2 0.76 topologies it has less number of DC sources and

10 38 2.94 7.27 0.61 semiconductor switches to achieve the same level. Also it has

The Table 4. represents that with increase in carrier been observed that with increase in levels THD reduces.For

frequencies the output voltage and current remain nearly same carrier frequency and same load with increase in

same but the voltage THD increases and current THD Modulation index THD also reduces.These features are

reduces.Therefore more sinusoidal current waveform has remarkable in hybrid topology.However this topology can be

been achieved. tested in unsymmetrical condition also.

Table.5.Modulation Index vs VTHD REFERENCES

MODULATION INDEX VTHD

0.6 13.5 [1] José Rodríguez, Jih-Sheng Lai, And Fang Zheng Peng, “

0.7 11.7 Multilevel Inverters: A Survey Of Topologies, Controls,

0.8 9.8 And Applications”,IEEE Transactions On Industrial

0.9 8.4 Electronics, Vol. 49, No. 4, August 2002.

1 7.27 [2] De,S.,Banerjee,D.,Sivakumar,K.,Gopakumar,K.,Ramchan

It has been observed that in a same carrier frequency the d,R.Patel,C.:’Multilevel inverter for low power

voltage THD reduces as we go on increasing the Modulation application’,IET Power Electron.,2011,4,(4),pp. 384-

Index. 392.

[3] ShalchiAlishan,R.,Nazarpour,D.,Hosseini,S.H.,Sabahi,M.:

”Novel topologies for symmetric ,asymmetricand

cascaded switched –diode multilevel converter with

minimum number of power electronic componts”,IEEE

Trans.Ind.Electron.,2014,61,(10),pp. 5300-5310.

[4] Mokhberdoran,A.,Ajami,A.:”Symmetric and asymmetric

design and implementation of new cascaded multilevel

inverter topology”,IEEE Trans.Power Electron.,2014,29,

(12),pp.6712-6724.

[5] Babaei,E.Hossini,S.H.,Gharehpetian,G.B.,Haque,M.T.,Sab

ahi,M.:”Reduction of dc voltage sources and switches in

asymmetrical multilevel converters using a novel

topology.”,J.Electr.Power Syst.Res.,2007,77,(8),pp.1073-

Fig .7(a) VTHD and ITHD vs Carrier Frequencies 1085.

[6] Gupta ,K.K.,Jain,S.:”Topology for multilevel inverters to

attain maximum number of levels from given DC

sources”,IET Power Elecron.,2012,5,(9),pp.1748-1753

[7] Abdul Halim Mohamed Yatim, and Ehsan Najafi,Design

and Implementation of a New Multilevel Inverter

Topology, IEEE transactions on industrial electronics,

vol. 59, no. 11, november 2012.

[8] G. Prakash M., et al., “A new multilevel inverter with

reduced number of switches,” International journal of

Power Electronics and Drives system, vol/issue: 5(1), pp.

63-70, 2014.

[9] Shivam prakash Gautam,Lalit Kumar, Shubhrata

Gupta,’Hybrid topology of symmetrical multilevel

inverter using less number of devices’,IET Power

Electron.,2015,8,(11),pp. 2125-2135.

[10] Lipika Nanda, A. Dasgupta, U. K. Rout ,”A Comparative

Studies of Cascaded Multilevel Inverters Having

Reduced Number of Switches with R and RL-Load”,

International journal of Power Electronics and Drives

system Vol. 8, No. 1, March 2017, pp. 40~50

You might also like

- Instructional Strategies and Practices Towards The Enhancement of Cookery-Related Skills of The Grade 7 and 9 Students of Titay National High SchoolDocument20 pagesInstructional Strategies and Practices Towards The Enhancement of Cookery-Related Skills of The Grade 7 and 9 Students of Titay National High SchoolPilar Galvano Ancheta80% (15)

- KX-TS3282BXW CIRCUIT BOARD (Operation) Componet ViewDocument1 pageKX-TS3282BXW CIRCUIT BOARD (Operation) Componet ViewkorodijNo ratings yet

- DG211, DG212: SPST 4-Channel Analog Switches FeaturesDocument7 pagesDG211, DG212: SPST 4-Channel Analog Switches Featuresjuan perezNo ratings yet

- Datasheet Search Site PDFDocument5 pagesDatasheet Search Site PDFchawkigenieNo ratings yet

- DG Incomer 1 - 1Document1 pageDG Incomer 1 - 1Limosh BsNo ratings yet

- Costruzioni Elettroniche: Mod. KL 500 Linar AmplifierDocument3 pagesCostruzioni Elettroniche: Mod. KL 500 Linar AmplifierNihat Çelik0% (1)

- PZO9099 Dance of The Damned - Interactive Maps 2112Document4 pagesPZO9099 Dance of The Damned - Interactive Maps 2112CanjulNo ratings yet

- Hell's Rebels - 03 - Dance of The Damned Interactive MapsDocument4 pagesHell's Rebels - 03 - Dance of The Damned Interactive MapsGina GuoNo ratings yet

- Ciclo Diseño de ProcesosDocument1 pageCiclo Diseño de ProcesosjoelNo ratings yet

- RG1 RG2 RG3 RG4: PCB - Gonio - PCB Page 1 oDocument1 pageRG1 RG2 RG3 RG4: PCB - Gonio - PCB Page 1 oIrvin Abraham Jackson GarciaNo ratings yet

- Mjoy AVR USB JoystickDocument9 pagesMjoy AVR USB Joystickmauricio alfonsoNo ratings yet

- DG201 ABK DatasheetDocument7 pagesDG201 ABK DatasheetcoronaqcNo ratings yet

- Wa0012 PDFDocument1 pageWa0012 PDFAnjo MolinaNo ratings yet

- Ao Ao: Errors in The Book: "High Performance Control of AC Drives With Matlab/Simulink Models"Document4 pagesAo Ao: Errors in The Book: "High Performance Control of AC Drives With Matlab/Simulink Models"Jignesh DesaiNo ratings yet

- 19-May-17 5:31 PM F 1.80 C:/Users/Asus/Desktop/smp112.brdDocument1 page19-May-17 5:31 PM F 1.80 C:/Users/Asus/Desktop/smp112.brdArmeanu TeodoraNo ratings yet

- Semester Project Report: Department of Electrical Electronic EngineeringDocument4 pagesSemester Project Report: Department of Electrical Electronic EngineeringNabeel MuqarrabNo ratings yet

- Seg MRD1Document1 pageSeg MRD1Larry ThorneNo ratings yet

- Chapter 3Document26 pagesChapter 3rushimunde1212No ratings yet

- Drive of 8-Digit 7-Segment DisplayDocument2 pagesDrive of 8-Digit 7-Segment Displayabba123No ratings yet

- Drilling Reaming TappingDocument1 pageDrilling Reaming TappingPeter ThomasNo ratings yet

- Sensor 1 Sensor 3 Sensor 2 Sensor 4Document1 pageSensor 1 Sensor 3 Sensor 2 Sensor 4Angie García RíosNo ratings yet

- Circuito Sumador RestadorDocument1 pageCircuito Sumador RestadorAnali HernandezNo ratings yet

- Reduced Switch Count Multi-Level Unidirectional Rectifiers: AbstractDocument8 pagesReduced Switch Count Multi-Level Unidirectional Rectifiers: AbstractBadal PatnaikNo ratings yet

- DatasheetDocument6 pagesDatasheetMuhammad Yasir KhanNo ratings yet

- EG-6 Stick Electric DiagramDocument2 pagesEG-6 Stick Electric DiagramAqil NewNo ratings yet

- ServiceManual RM KL351 ENG ITADocument2 pagesServiceManual RM KL351 ENG ITAATOM atomNo ratings yet

- New Correlation Equationsfor Finned Tube HeatexchangersDocument12 pagesNew Correlation Equationsfor Finned Tube HeatexchangerssergioteroNo ratings yet

- TCD1103GFG-Rev2-090115 DatasheetDocument17 pagesTCD1103GFG-Rev2-090115 DatasheetbocarocaNo ratings yet

- Title: Multiplexer Instruction AimsDocument5 pagesTitle: Multiplexer Instruction Aimssuv_fame100% (1)

- Reference Design - 1 STR-A6151 Universal-Input, 10 W Power SupplyDocument2 pagesReference Design - 1 STR-A6151 Universal-Input, 10 W Power Supplygary omanaNo ratings yet

- EG-12 Stick Electric DiagramDocument2 pagesEG-12 Stick Electric DiagramAqil NewNo ratings yet

- Solutions For: ExcavatorsDocument24 pagesSolutions For: ExcavatorsMasterr100% (1)

- Energies 12 00207 PDFDocument15 pagesEnergies 12 00207 PDFSathiya NathanNo ratings yet

- Mod. KLV 350 Linear Amplifier Costruzioni Elettroniche: Di Marchioni Davide & Daniele S.N.C. Schematic DiagramDocument3 pagesMod. KLV 350 Linear Amplifier Costruzioni Elettroniche: Di Marchioni Davide & Daniele S.N.C. Schematic DiagramPisu Miau Pisu MiauNo ratings yet

- Ahmed A Hussain, EE Dept., PMU - Nov. 2022: 4x1 MUX D D D D S S Q B B 0 1 XDocument3 pagesAhmed A Hussain, EE Dept., PMU - Nov. 2022: 4x1 MUX D D D D S S Q B B 0 1 Xhessa 2001No ratings yet

- TCS3200 Color SensorColor Detector Schematics PDFDocument1 pageTCS3200 Color SensorColor Detector Schematics PDFsiogNo ratings yet

- Frame D: Chapter 1 IntroductionDocument1 pageFrame D: Chapter 1 IntroductionAldairNo ratings yet

- 9591-102-102-PVM-F-010-03 Cold AirDocument3 pages9591-102-102-PVM-F-010-03 Cold AirVijay PalNo ratings yet

- Piano ArduinoDocument1 pagePiano ArduinoElda NoviantiNo ratings yet

- New High Voltage Gain DC-DC Converter Based On Modified Quasi Z-Source NetworkDocument6 pagesNew High Voltage Gain DC-DC Converter Based On Modified Quasi Z-Source NetworkHussain K. SayedNo ratings yet

- Circuit Diagram bh1415fDocument1 pageCircuit Diagram bh1415fNihat Çelik0% (1)

- KLV400 Manual20410Document3 pagesKLV400 Manual20410Zaphod100% (1)

- Voice Switch (Reset) : Ekt Katrangi ElectronicsDocument1 pageVoice Switch (Reset) : Ekt Katrangi ElectronicsSaiid Abi FarrajNo ratings yet

- Schematic - 4017 Kademeli Led - 2021-12-29Document1 pageSchematic - 4017 Kademeli Led - 2021-12-29Luis Eduardo RibeiroNo ratings yet

- SIM900 (Imran)Document1 pageSIM900 (Imran)TALENT TRICKS TechnologiesNo ratings yet

- Schematic - TX FM VALVULADO - 2024 03 14Document1 pageSchematic - TX FM VALVULADO - 2024 03 14Doni SouzaNo ratings yet

- 74HC273 74HCT273: 1. General DescriptionDocument18 pages74HC273 74HCT273: 1. General DescriptionMarquinho SilvaNo ratings yet

- Schematic - INPUT BALLANCE - 2024 05 22Document1 pageSchematic - INPUT BALLANCE - 2024 05 22orlandofedrikNo ratings yet

- Asymmetric Dual N-Channel Trench MOSFET 30V: General Description FeaturesDocument9 pagesAsymmetric Dual N-Channel Trench MOSFET 30V: General Description Featureschristian romoNo ratings yet

- Panasonic VCR Power Supply PDFDocument1 pagePanasonic VCR Power Supply PDFsa920189No ratings yet

- TL Cruiser Manual OgDocument23 pagesTL Cruiser Manual OgHyH ConstructoresNo ratings yet

- Panasonic VCR PowerDocument1 pagePanasonic VCR PowerDipakNo ratings yet

- Circuit Access ControlDocument5 pagesCircuit Access Controlejim johnNo ratings yet

- Day 7Document24 pagesDay 7NAVEEN MNo ratings yet

- Research On Totem - Pole Bridgeless PFC Based On Synchronous Reference FrameDocument6 pagesResearch On Totem - Pole Bridgeless PFC Based On Synchronous Reference FrameTedNo ratings yet

- Elastically Coupled Beam Apparatus: Instructional ManualDocument9 pagesElastically Coupled Beam Apparatus: Instructional ManualMr. Danish SaeedNo ratings yet

- Schematic Receptor Valvulado Regen 2024-01-28Document1 pageSchematic Receptor Valvulado Regen 2024-01-28Doni SouzaNo ratings yet

- General Description: 4-Bit Bidirectional Universal Shift RegisterDocument14 pagesGeneral Description: 4-Bit Bidirectional Universal Shift RegisterFadwa alhaderieNo ratings yet

- 13tr-t4d 40m SSBDocument1 page13tr-t4d 40m SSBfox7878No ratings yet

- Laboratory Exercices For Analog and Digital Circuits Using NI ELVIS II NI Multisim 2Document150 pagesLaboratory Exercices For Analog and Digital Circuits Using NI ELVIS II NI Multisim 2zohas13No ratings yet

- Krishna File 2Document18 pagesKrishna File 2Ali AhmadNo ratings yet

- Electric Submersible Pump New Design For Zug-10 Offshore North West JavaDocument9 pagesElectric Submersible Pump New Design For Zug-10 Offshore North West JavaLarasati K SadewiNo ratings yet

- Steel Final Project: Prepared By: Siva Soran Supervised By: Mr. Shuaaib A. MohammedDocument25 pagesSteel Final Project: Prepared By: Siva Soran Supervised By: Mr. Shuaaib A. Mohammedsiva soranNo ratings yet

- Dialogue Questionnaire-3rd SessionDocument3 pagesDialogue Questionnaire-3rd SessionMiguel HernandezNo ratings yet

- Base 1Document14 pagesBase 1ANAS MANSOORNo ratings yet

- DLL-Q3-W6 - Mam LouDocument9 pagesDLL-Q3-W6 - Mam LouChello Ann Pelaez AsuncionNo ratings yet

- Getting StartedDocument17 pagesGetting StartedManuel Jesus Vera Duran100% (1)

- Information Technology Laboratory: NIST Special Publication 800-17Document153 pagesInformation Technology Laboratory: NIST Special Publication 800-17Bhanu SivaNo ratings yet

- Line Balancing Line Balancing: Pemp Emm515Document56 pagesLine Balancing Line Balancing: Pemp Emm515vehlajattNo ratings yet

- The Systems Game Oct 2011 - CorrectedDocument2 pagesThe Systems Game Oct 2011 - CorrectedReos PartnersNo ratings yet

- Master Thesis Literature Review ExampleDocument5 pagesMaster Thesis Literature Review Examplebethanyrodriguezmanchester100% (2)

- Ilide - Info Details of Mobile Repairing Course PRDocument5 pagesIlide - Info Details of Mobile Repairing Course PRLoki VistNo ratings yet

- Lenovo IdeaPad U510 LA-8971p Rev 0.1Document58 pagesLenovo IdeaPad U510 LA-8971p Rev 0.1Jhon GonzalesNo ratings yet

- Honda Motorcycle & Scooter India Pvt. LTD.: MH010402PA001:10-Mar-2022 04:46:20 PMDocument128 pagesHonda Motorcycle & Scooter India Pvt. LTD.: MH010402PA001:10-Mar-2022 04:46:20 PMpzy84628870No ratings yet

- HP 15-CS 1016ur Quanta G7BD DAG7BDMB8F0 Rev 1ADocument49 pagesHP 15-CS 1016ur Quanta G7BD DAG7BDMB8F0 Rev 1AJuan Carlos Huaman HuertaNo ratings yet

- Week 10 - Continuing Education Programs On Ethico-Moral Practice in NursingDocument4 pagesWeek 10 - Continuing Education Programs On Ethico-Moral Practice in NursingAmori Studios0% (1)

- Color PsychologyDocument2 pagesColor PsychologyAmalla KuttyNo ratings yet

- Eng - Manage - Syst - Disc 060125Document12 pagesEng - Manage - Syst - Disc 060125greenNo ratings yet

- Fairchild Display Power SolutionDocument58 pagesFairchild Display Power SolutionFrancisco Antonio100% (1)

- How To Impress A GirlDocument2 pagesHow To Impress A GirlAnkit MehtaNo ratings yet

- Differentiation by TrockersDocument47 pagesDifferentiation by TrockersRodney Takundanashe Mandizvidza100% (1)

- David PlotkinDocument41 pagesDavid PlotkinArk GroupNo ratings yet

- 305-Understanding The Operation of Pumps Missing Pages 139-140Document162 pages305-Understanding The Operation of Pumps Missing Pages 139-140ataguca100% (1)

- Metal-Organic Frameworks and Their Postsynthetic ModificationDocument60 pagesMetal-Organic Frameworks and Their Postsynthetic ModificationDean HidayatNo ratings yet

- DatabaseDocument326 pagesDatabaseFurukawa SaiNo ratings yet

- DFSORTDocument1 pageDFSORTSrikanth TalasuNo ratings yet

- Gym Membership Application PDF Format DownloadDocument4 pagesGym Membership Application PDF Format DownloadFranco Evale YumulNo ratings yet

- Ventron EngineeringDocument2 pagesVentron EngineeringXiangyue ZhangNo ratings yet