Professional Documents

Culture Documents

Stn3Nf06L: N-Channel 60 V, 0.07 Ω Typ., 4 A Stripfet™ Ii Power Mosfet In A Sot-223 Package

Stn3Nf06L: N-Channel 60 V, 0.07 Ω Typ., 4 A Stripfet™ Ii Power Mosfet In A Sot-223 Package

Uploaded by

ramesh sahukhalOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Stn3Nf06L: N-Channel 60 V, 0.07 Ω Typ., 4 A Stripfet™ Ii Power Mosfet In A Sot-223 Package

Stn3Nf06L: N-Channel 60 V, 0.07 Ω Typ., 4 A Stripfet™ Ii Power Mosfet In A Sot-223 Package

Uploaded by

ramesh sahukhalCopyright:

Available Formats

STN3NF06L

N-channel 60 V, 0.07 Ω typ., 4 A STripFET™ II

Power MOSFET in a SOT-223 package

Datasheet - production data

Features

Order code VDS RDS(on) max. ID

STN3NF06L 60 V 0.1 Ω 4A

Exceptional dv/dt capability

100% avalanche tested

Low threshold drive

Applications

Switching applications

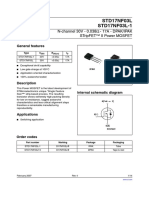

Figure 1: Internal schematic diagram

Description

This Power MOSFET series realized with

STMicroelectronics unique STripFET™ process

is specifically designed to minimize input

capacitance and gate charge. It is therefore ideal

as a primary switch in advanced high-efficiency

isolated DC-DC converters for Telecom and

Computer applications. It is also suitable for any

application with low gate charge drive

requirements.

Table 1: Device summary

Order code Marking Package Packing

STN3NF06L 3NF06L SOT-223 Tape and reel

July 2017 DocID7798 Rev 9 1/12

This is information on a product in full production. www.st.com

Contents STN3NF06L

Contents

1 Electrical ratings ............................................................................. 3

2 Electrical characteristics ................................................................ 4

2.1 Electrical characteristics (curves) ...................................................... 6

3 Test circuits ..................................................................................... 8

4 Package information ....................................................................... 9

4.1 SOT-223 package information .......................................................... 9

5 Revision history ............................................................................ 11

2/12 DocID7798 Rev 9

STN3NF06L Electrical ratings

1 Electrical ratings

Table 2: Absolute maximum ratings

Symbol Parameter Value Unit

VDS Drain-source voltage 60 V

VGS Gate-source voltage ±16 V

ID(1) Drain current (continuous) at Tc = 25 °C 4 A

ID Drain current (continuous) at Tc = 100 °C 2.9 A

IDM(2) Drain current (pulsed) 16 A

PTOT Total dissipation at Tpcb = 25 °C 3.3 W

(3)

dv/dt Peak diode recovery voltage slope 10 V/ns

EAS(4) Single pulse avalanche energy 200 mJ

Tj Operating junction temperature range

- 55 to 150 °C

Tstg Storage temperature range

Notes:

(1)Current limited by the package.

(2)Pulse width limited by safe operating area.

(3)I

SD ≤ 3 A, di/dt ≤ 150 A/μs, VDD ≤ V(BR)DSS

(4)Starting Tj = 25 °C, ID = 4 A, VDD = 30 V

Table 3: Thermal data

Symbol Parameter Value Unit

(1)

Rthj-pcb Thermal resistance junction-pcb 38 °C/W

Rthj-pcb Thermal resistance junction-pcb(2) 100 °C/W

Notes:

(1)When Mounted on FR-4 board 1 inch2 pad, 2 oz. of Cu and t <10 s.

(2)When mounted on minimum recommended footprint.

DocID7798 Rev 9 3/12

Electrical characteristics STN3NF06L

2 Electrical characteristics

TC = 25 °C unless otherwise specified

Table 4: On/off-state

Symbol Parameter Test conditions Min. Typ. Max. Unit

Drain-source breakdown

V(BR)DSS VGS = 0 V, ID = 250 μA 60 V

voltage

VGS = 0 V, VDS = 60 V 1 µA

Zero gate voltage drain

IDSS VGS = 0 V, VDS = 60 V

current 10 µA

TC = 125 °C(1)

IGSS Gate body leakage current VDS = 0 V, VGS = ±16 V ±100 nA

VGS(th) Gate threshold voltage VDS = VGS, ID = 250 µA 1 2.8 V

Static drain-source VGS= 10 V, ID= 1.5 A 0.07 0.10 Ω

RDS(on)

on-resistance VGS= 5 V, ID= 1.5 A 0.085 0.12 Ω

Notes:

(1)Defined by design, not subject to production test.

Table 5: Dynamic

Symbol Parameter Test conditions Min. Typ. Max. Unit

Ciss Input capacitance - 340 pF

Coss Output capacitance - 63 pF

VDS =25 V, f=1 MHz, VGS=0 V

Reverse transfer

Crss - 30 pF

capacitance

Qg Total gate charge VDD = 48 V, ID = 3 A - 7 9 nC

Qgs Gate-source charge VGS= 0 to 5 V - 1.5 nC

(see Figure 14: "Test circuit for

Qgd Gate-drain charge gate charge behavior") - 2.8 nC

Table 6: Switching times

Symbol Parameter Test conditions Min. Typ. Max. Unit

td(on) Turn-on delay time VDD= 30 V, ID = 1.5 A, - 9 - ns

RG = 4.7 Ω

tr Rise time - 25 - ns

VGS = 5 V

td(off) Turn-off delay time - 20 - ns

(see Figure 13: "Test circuit for

resistive load switching times"

tf Fall time and Figure 18: "Switching time - 10 - ns

waveform")

4/12 DocID7798 Rev 9

STN3NF06L Electrical characteristics

Table 7: Source-drain diode

Symbol Parameter Test conditions Min. Typ. Max. Unit

VSD(1) Forward on voltage ISD= 4 A, VGS=0 V - 1.5 V

trr Reverse recovery time - 50 ns

ISD= 4 A, di/dt = 100 A/μs,

Reverse recovery VDD=25 V, Tj=150 °C

Qrr - 88 nC

charge (see Figure 15: "Test circuit for

inductive load switching and

Reverse recovery diode recovery times")

IRRM - 3.5 A

current

Notes:

(1)Pulsed: pulse duration = 300 µs, duty cycle 1.5%

DocID7798 Rev 9 5/12

Electrical characteristics STN3NF06L

2.1 Electrical characteristics (curves)

Figure 2: Safe operating area Figure 3: Thermal impedance

Figure 4: Output characteristics Figure 5: Transfer characteristics

GC91920a

Figure 6: Static drain-source on-resistance Figure 7: Gate charge vs. gate-source voltage

GC91940a GC91950a

6/12 DocID7798 Rev 9

STN3NF06L Electrical characteristics

Figure 8: Capacitance variations Figure 9: Normalized gate threshold voltage vs

temperature

Figure 10: Normalized on-resistance vs Figure 11: Normalized V(BR)DSS vs temperature

temperature

GC91980a GC93240

Figure 12: Source-drain diode forward characteristics

DocID7798 Rev 9 7/12

Test circuits STN3NF06L

3 Test circuits

Figure 13: Test circuit for resistive load Figure 14: Test circuit for gate charge

switching times behavior

Figure 15: Test circuit for inductive load Figure 16: Unclamped inductive load test

switching and diode recovery times circuit

Figure 17: Unclamped inductive waveform Figure 18: Switching time waveform

8/12 DocID7798 Rev 9

STN3NF06L Package information

4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK® packages, depending on their level of environmental compliance. ECOPACK ®

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK® is an ST trademark.

4.1 SOT-223 package information

Figure 19: SOT-223 package outline

DocID7798 Rev 9 9/12

Package information STN3NF06L

Table 8: SOT-223 package mechanical data

mm

Dim.

Min. Typ. Max.

A 1.8

A1 0.02 0.1

B 0.6 0.7 0.85

B1 2.9 3 3.15

c 0.24 0.26 0.35

D 6.3 6.5 6.7

e 2.3

e1 4.6

E 3.3 3.5 3.7

H 6.7 7.0 7.3

V 10º

Figure 20: SOT-223 recommended footprint (dimensions are in mm)

10/12 DocID7798 Rev 9

STN3NF06L Revision history

5 Revision history

Table 9: Document revision history

Date Revision Changes

21-Jun-2004 5 Complete version.

04-Oct-2006 6 New template, no content change.

01-Feb-2007 7 Typo mistake on Table 2.

12-Jun-2008 8 Corrected marking on Table 1

Modified internal schematic diagram on cover page.

03-Jul-2017 9 Updated Section 4: "Package information".

Minor text changes.

DocID7798 Rev 9 11/12

STN3NF06L

IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and

improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST

products before placing orders. ST products are sold pursuant to ST’s terms and conditions of sale in place at the time of order

acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the

design of Purchasers’ products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

12/12 DocID7798 Rev 9

You might also like

- Riya Ranjan: Education CertificationDocument1 pageRiya Ranjan: Education CertificationAayush Kumar KumarNo ratings yet

- 4NF20L STMicroelectronics PDFDocument12 pages4NF20L STMicroelectronics PDFTiago eletrônicaNo ratings yet

- Stp130N6F7: N-Channel 60 V, 4.2 Mω Typ., 80 A Stripfet™ F7 Power Mosfet In A To-220 PackageDocument12 pagesStp130N6F7: N-Channel 60 V, 4.2 Mω Typ., 80 A Stripfet™ F7 Power Mosfet In A To-220 PackageOsmir MonteiroNo ratings yet

- F10NK50Z STMicroelectronicsDocument13 pagesF10NK50Z STMicroelectronicsCandraBuanaNo ratings yet

- STP100NF04Document20 pagesSTP100NF04Schueler TecnologiaNo ratings yet

- Stn1Nk60Zl: N-Channel 600 V, 10.4 Ω Typ., 0.44 A Supermesh™ Power Mosfet In A Sot-223 PackageDocument12 pagesStn1Nk60Zl: N-Channel 600 V, 10.4 Ω Typ., 0.44 A Supermesh™ Power Mosfet In A Sot-223 PackageMarcos SilvaNo ratings yet

- stl66dn3llh5Document15 pagesstl66dn3llh5mhd.mousaNo ratings yet

- STD 95 P 3 LLH 6 AgDocument16 pagesSTD 95 P 3 LLH 6 AgjkircsiNo ratings yet

- std18nf03lDocument15 pagesstd18nf03lmhd.mousaNo ratings yet

- STD3N62K3, STF3N62K3, Stu3n62k3Document27 pagesSTD3N62K3, STF3N62K3, Stu3n62k3David Alberto Lotero AlvarezNo ratings yet

- STP310N10F7Document13 pagesSTP310N10F7Lu HoaNo ratings yet

- Std6N52K3: N-Channel 525 V, 1 Ω Typ., 6.5 A Mdmesh™ K3 Power Mosfet In Dpak PackageDocument18 pagesStd6N52K3: N-Channel 525 V, 1 Ω Typ., 6.5 A Mdmesh™ K3 Power Mosfet In Dpak PackageErkanNo ratings yet

- Stl36Dn6F7: Dual N-Channel 60 V, 23 Mω Typ., 33 A Stripfet™ F7 Power Mosfet In A Powerflat™ 5X6 Double Island PackageDocument16 pagesStl36Dn6F7: Dual N-Channel 60 V, 23 Mω Typ., 33 A Stripfet™ F7 Power Mosfet In A Powerflat™ 5X6 Double Island PackageKunal sawantNo ratings yet

- Std12Nf06L-1: N-Channel 60 V, 0.07 Typ.,12 A, Stripfet™ Ii Power Mosfet in An Ipak PackageDocument14 pagesStd12Nf06L-1: N-Channel 60 V, 0.07 Typ.,12 A, Stripfet™ Ii Power Mosfet in An Ipak PackageClaudinei JankeNo ratings yet

- Stmicroelectronics - SGST S A0007382382 1 1681241Document18 pagesStmicroelectronics - SGST S A0007382382 1 1681241MatNo ratings yet

- STP 120 NF 10Document19 pagesSTP 120 NF 10Paun LiviuNo ratings yet

- N-Channel 600 V, 0.255 Ω Typ., 13 A Mdmesh M2 Power Mosfet In A To-220Fp PackageDocument12 pagesN-Channel 600 V, 0.255 Ω Typ., 13 A Mdmesh M2 Power Mosfet In A To-220Fp PackageErasmo Franco SNo ratings yet

- Moffet Stfu10nk60zDocument13 pagesMoffet Stfu10nk60zOmar ChirinoNo ratings yet

- N-Channel 650 V, 0.60 Ω Typ., 7 A Mdmesh M2 Power Mosfet In A To-220Fp PackageDocument12 pagesN-Channel 650 V, 0.60 Ω Typ., 7 A Mdmesh M2 Power Mosfet In A To-220Fp PackagejefjronNo ratings yet

- STF 13 NM 60 NDDocument12 pagesSTF 13 NM 60 NDlejojoel321No ratings yet

- STP62NS04Z: N-Channel Clamped 12.5 M, 62 A, TO-220 Fully Protected MESH OVERLAY™ Power MOSFETDocument12 pagesSTP62NS04Z: N-Channel Clamped 12.5 M, 62 A, TO-220 Fully Protected MESH OVERLAY™ Power MOSFETmartinNo ratings yet

- N-Channel 525 V, 1.25 Ω Typ., 4.4 A, Ultrafastmesh™ Power Mosfet In A Dpak PackageDocument17 pagesN-Channel 525 V, 1.25 Ω Typ., 4.4 A, Ultrafastmesh™ Power Mosfet In A Dpak PackageSmarttech ParobeNo ratings yet

- Stw20Nk50Z: N-Channel 500 V, 0.23 Ω, 20 A Supermesh™ Power Mosfet Zener-Protected In To-247 PackageDocument12 pagesStw20Nk50Z: N-Channel 500 V, 0.23 Ω, 20 A Supermesh™ Power Mosfet Zener-Protected In To-247 PackagemonikaNo ratings yet

- STF 3 NK 80 ZDocument12 pagesSTF 3 NK 80 ZGheorghe DavidNo ratings yet

- STD35NF06L: N-channel 60 V, 0.014 Ω, 35 A Stripfet™ Ii Power Mosfet in a DPAK packageDocument14 pagesSTD35NF06L: N-channel 60 V, 0.014 Ω, 35 A Stripfet™ Ii Power Mosfet in a DPAK packagecobrax100No ratings yet

- 12NK90Document13 pages12NK90Iwan YogyaNo ratings yet

- STL3N10F7Document14 pagesSTL3N10F7angel uriel silvaNo ratings yet

- N-Channel 100 V, 0.0036 Typ., 110 A, Stripfet™ F7 Power Mosfet in A To-220 PackageDocument13 pagesN-Channel 100 V, 0.0036 Typ., 110 A, Stripfet™ F7 Power Mosfet in A To-220 PackageCarautotronica LaboratorioNo ratings yet

- Stp9Nk65Z Stp9Nk65Zfp: N-Channel 650 V, 1 Ω, 6.4 A, To-220, To-220Fp Zener-Protected Supermesh™ Power MosfetDocument16 pagesStp9Nk65Z Stp9Nk65Zfp: N-Channel 650 V, 1 Ω, 6.4 A, To-220, To-220Fp Zener-Protected Supermesh™ Power MosfetAndyMahataraNo ratings yet

- 43NM60ND Mos PDFDocument13 pages43NM60ND Mos PDFHưng HQNo ratings yet

- STB85NF55L STP85NF55L: N-Channel 55 V, 0.0060, 80 A, TO-220, D PAK Stripfet™ Ii Power MosfetDocument14 pagesSTB85NF55L STP85NF55L: N-Channel 55 V, 0.0060, 80 A, TO-220, D PAK Stripfet™ Ii Power Mosfetmobil benerNo ratings yet

- Stw48Nm60N: N-Channel 600 V, 0.055 Ω Typ., 44 A Mdmesh™ Ii Power Mosfet In A To-247 PackageDocument13 pagesStw48Nm60N: N-Channel 600 V, 0.055 Ω Typ., 44 A Mdmesh™ Ii Power Mosfet In A To-247 PackageАлексей АндрияшNo ratings yet

- STL40DN3LLH5Document15 pagesSTL40DN3LLH5angel uriel silvaNo ratings yet

- 20N60M2EP Mark STP20N60M2-EP 600V 13A FETDocument14 pages20N60M2EP Mark STP20N60M2-EP 600V 13A FETRuslanNo ratings yet

- stq1nk80zr ApDocument16 pagesstq1nk80zr ApPaun LiviuNo ratings yet

- Stw48N60M2: N-Channel 600 V, 0.06 Typ., 42 A Mdmesh™ M2 Power Mosfet in A To-247 PackageDocument12 pagesStw48N60M2: N-Channel 600 V, 0.06 Typ., 42 A Mdmesh™ M2 Power Mosfet in A To-247 PackageshivguptaNo ratings yet

- STP80NF12Document12 pagesSTP80NF12vanuzalopeslopes1No ratings yet

- Std5N52U Stf5N52U: N-Channel 525 V, 1.28, 4.4 A, Dpak, To-220Fp Ultrafastmesh™ Power MosfetDocument15 pagesStd5N52U Stf5N52U: N-Channel 525 V, 1.28, 4.4 A, Dpak, To-220Fp Ultrafastmesh™ Power Mosfetmeri_horvatNo ratings yet

- stw26nm60n 957021Document13 pagesstw26nm60n 957021saikumarNo ratings yet

- STB33N60DM2 STMicroelectronicsDocument20 pagesSTB33N60DM2 STMicroelectronicsMateus BelettiNo ratings yet

- STD 17 NF 25Document15 pagesSTD 17 NF 25Sinon Amv'sNo ratings yet

- STF 13 NM 60 NDocument12 pagesSTF 13 NM 60 Nrafaelmattos2015No ratings yet

- STB 120 N 4 LF 6Document18 pagesSTB 120 N 4 LF 6Manuel QuirozNo ratings yet

- IRF640TDocument12 pagesIRF640TDATTNIRANJAN JAMBOTKARNo ratings yet

- STP 80 NF 10Document14 pagesSTP 80 NF 10Mateus BelettiNo ratings yet

- STN 3 NF 06Document12 pagesSTN 3 NF 06ribeiro220No ratings yet

- A2t20h160w04n 1517293Document12 pagesA2t20h160w04n 1517293PalmNo ratings yet

- Sty112N65M5: N-Channel 650 V, 0.019 Ω, 96 A, Mdmesh™ V Power Mosfet In Max247 PackageDocument12 pagesSty112N65M5: N-Channel 650 V, 0.019 Ω, 96 A, Mdmesh™ V Power Mosfet In Max247 PackageErkanNo ratings yet

- Datasheet PDFDocument15 pagesDatasheet PDFomar mijaresNo ratings yet

- 60N3L STMicroelectronics Elenota - PLDocument15 pages60N3L STMicroelectronics Elenota - PLNana CianchettaNo ratings yet

- stf13nm60n HDocument13 pagesstf13nm60n HMatheus Alves MendesNo ratings yet

- Data SheetDocument17 pagesData SheetVagner SilvaNo ratings yet

- STH310N0F7Document19 pagesSTH310N0F7Lu HoaNo ratings yet

- STW 34 NM 60 NDocument12 pagesSTW 34 NM 60 NSujit KumarNo ratings yet

- Infineon IPA60R360P7 DataSheet v02 - 03 ENDocument14 pagesInfineon IPA60R360P7 DataSheet v02 - 03 ENcostelcnNo ratings yet

- STB12NK80Z STP12NK80Z - STW12NK80ZDocument16 pagesSTB12NK80Z STP12NK80Z - STW12NK80ZMAKERNo ratings yet

- STD1LNK60Z-1 Stq1Nk60Zr-Ap - Stn1Nk60ZDocument16 pagesSTD1LNK60Z-1 Stq1Nk60Zr-Ap - Stn1Nk60ZThanh ChelseabunNo ratings yet

- D50N03LDocument16 pagesD50N03LO'PrimeNo ratings yet

- STD17NF03L STD17NF03L-1: N-Channel 30V - 0.038 - 17A - Dpak/Ipak Stripfet™ Ii Power MosfetDocument14 pagesSTD17NF03L STD17NF03L-1: N-Channel 30V - 0.038 - 17A - Dpak/Ipak Stripfet™ Ii Power MosfetSudais AkbarNo ratings yet

- STP 16 NF 06 FPDocument14 pagesSTP 16 NF 06 FPjoverjover1No ratings yet

- Analog Dialogue Volume 46, Number 1: Analog Dialogue, #5From EverandAnalog Dialogue Volume 46, Number 1: Analog Dialogue, #5Rating: 5 out of 5 stars5/5 (1)

- High Performance 802.11ac Wave 2 (Wi-Fi 5) Access PointDocument4 pagesHigh Performance 802.11ac Wave 2 (Wi-Fi 5) Access PointCromNo ratings yet

- Harga TV LCDDocument2 pagesHarga TV LCDYohandi YahyaNo ratings yet

- Nokia Lte Layering Strategy Pa 14 DraftDocument32 pagesNokia Lte Layering Strategy Pa 14 DraftMuhammad Haris100% (1)

- Winning In: UBB Network Infrastructure Driven by Applications, Cloud and ExperiencesDocument22 pagesWinning In: UBB Network Infrastructure Driven by Applications, Cloud and ExperiencesChin Xian PohNo ratings yet

- Numaker-Pfm-M487 User ManualDocument37 pagesNumaker-Pfm-M487 User Manualvikas babuNo ratings yet

- VLSI Design and Implementation of Low Power MAC Unit With Block Enabling TechniqueDocument5 pagesVLSI Design and Implementation of Low Power MAC Unit With Block Enabling TechniqueShruthi H Naik0% (1)

- AG9311 DatasheetDocument22 pagesAG9311 DatasheetUser PcNo ratings yet

- Special Cells Required For Multi-Voltage Design - Magic Blue SmokeDocument8 pagesSpecial Cells Required For Multi-Voltage Design - Magic Blue SmokesrajeceNo ratings yet

- Data DictionaryDocument7 pagesData Dictionaryクマー ヴィーンNo ratings yet

- HP EliteBook 840 G4 Notebook PC Service and Maintenance ManualDocument116 pagesHP EliteBook 840 G4 Notebook PC Service and Maintenance ManualisamuslackerNo ratings yet

- Technology For Teaching and Learning 2 Second SemesterDocument35 pagesTechnology For Teaching and Learning 2 Second SemesterKimboy Gentapanan100% (1)

- KPI Formulae Change Approval 1Document5 pagesKPI Formulae Change Approval 1nathaniel07No ratings yet

- Multi-Functional TesterDocument7 pagesMulti-Functional TesterDaniel ZeballosNo ratings yet

- A733PDocument4 pagesA733PabolfazlNo ratings yet

- Service Guide SpecificationDocument36 pagesService Guide SpecificationtongshadowNo ratings yet

- Stereo Cassette Deck: TC-WE675 TC-WE475Document24 pagesStereo Cassette Deck: TC-WE675 TC-WE475marsan1708No ratings yet

- LQ-MD800P LQ-MD800E: Operating InstructionsDocument44 pagesLQ-MD800P LQ-MD800E: Operating InstructionsAriana Lucia Rocha MendezNo ratings yet

- Radio-Data CommunicationDocument83 pagesRadio-Data CommunicationEvansNo ratings yet

- Antenna Installation ProceduresDocument6 pagesAntenna Installation ProceduresOKORIE ChikezieNo ratings yet

- Communication Switching System PDFDocument2 pagesCommunication Switching System PDFShayNo ratings yet

- Supplement For Web Control-V1.00EDocument104 pagesSupplement For Web Control-V1.00EChakphanu KomasathitNo ratings yet

- Service Manual: HCD-RG88Document76 pagesService Manual: HCD-RG88pesyrNo ratings yet

- KV Az212m61Document155 pagesKV Az212m61DeddyThungNo ratings yet

- Unit 3 Network Security and Authentication: StructureDocument19 pagesUnit 3 Network Security and Authentication: StructureMr. MANTRANo ratings yet

- Manual-Dynamite EnglishDocument40 pagesManual-Dynamite EnglishSERVICE CENTER PABX 085289388205No ratings yet

- Unit 2 Basics of Communication Technology: 2.0 ObjectivesDocument19 pagesUnit 2 Basics of Communication Technology: 2.0 ObjectivesJoffin JosephNo ratings yet

- Harman Kardon AVR 132-EnDocument36 pagesHarman Kardon AVR 132-EnPascalau GeorgeNo ratings yet

- Remote Patient Health Monitoring Using IoTDocument3 pagesRemote Patient Health Monitoring Using IoTInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Configure Single-Area OSPFv2Document12 pagesConfigure Single-Area OSPFv2Mohammed AkeelNo ratings yet