Professional Documents

Culture Documents

256-Bit Serial Nonvolatile CMOS Static RAM: CAT24C44

256-Bit Serial Nonvolatile CMOS Static RAM: CAT24C44

Uploaded by

vspuriOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

256-Bit Serial Nonvolatile CMOS Static RAM: CAT24C44

256-Bit Serial Nonvolatile CMOS Static RAM: CAT24C44

Uploaded by

vspuriCopyright:

Available Formats

CAT24C44

256-Bit Serial Nonvolatile CMOS Static RAM

FEATURES

■ Single 5V Supply ■ JEDEC Standard Pinouts:

■ Infinite EEPROM to RAM Recall –8-lead DIP

–8-lead SOIC

■ CMOS and TTL Compatible I/O

■ 100,000 Program/Erase Cycles (EEPROM)

■ Low CMOS Power Consumption:

–Active: 3mA Max. ■ Auto Recall on Power-up

–Standby: 30µA Max. ■ Commercial, Industrial and Automotive

■ Power Up/Down Protection Temperature Ranges

■ 10 Year Data Retention

DESCRIPTION

The CAT24C44 Serial NVRAM is a 256-bit nonvolatile store protection circuitry prohibits STORE operations

memory organized as 16 words x 16 bits. The high when VCC is less than 3.5V (typical) ensuring EEPROM

speed Static RAM array is bit for bit backed up by a data integrity.

nonvolatile EEPROM array which allows for easy trans-

The CAT24C44 is manufactured using Catalyst’s ad-

fer of data from RAM array to EEPROM (STORE) and

vanced CMOS floating gate technology. It is designed to

from EEPROM to RAM (RECALL). STORE operations

endure 100,000 program/erase cycles (EEPROM) and

are completed in 10ms max. and RECALL operations

has a data retention of 10 years. The device is available

typically within 1.5µs. The CAT24C44 features unlim-

in JEDEC approved 8-lead plastic DIP and SOIC

ited RAM write operations either through external RAM

packages.

writes or internal recalls from EEPROM. Internal false

PIN CONFIGURATION PIN FUNCTIONS

Pin Name Function

DIP Package (L) SOIC Package ( V) SK Serial Clock

CE 1 8 VCC CE 1 8 VCC DI Serial Input

SK 2 7 STORE SK 2 7 STORE DO Serial Data Output

DI 3 6 RECALL DI 3 6 RECALL

DO 4 5 VSS DO 4 5 VSS CE Chip Enable

RECALL Recall

STORE Store

VCC +5V

VSS Ground

© 2008 SCILLC. All rights reserved. Doc. No. MD-1083, Rev. T

Characteristics subject to change without notice 1

CAT24C44

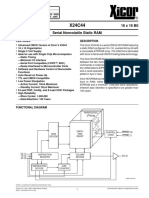

BLOCK DIAGRAM

EEPROM ARRAY

RECALL

ROW STATIC RAM

STORE

DECODE ARRAY STORE

256-BIT CONTROL

LOGIC RECALL

CE

INSTRUCTION COLUMN

DI DO

REGISTER DECODE

SK VCC

VSS

INSTRUCTION 4-BIT

DECODE COUNTER

MODE SELECTION(1)(2)

Software Write Enable Previous Recall

Mode STORE RECALL Instruction Latch Latch

Hardware Recall(3) 1 0 NOP X X

Software Recall 1 1 RCL X X

Hardware Store(3) 0 1 NOP SET TRUE

Software Store 1 1 STO SET TRUE

X = Don’t Care

POWER-UP TIMING(4)

Symbol Parameter Min. Max. Units

VCCSR VCC Slew Rate 0.5 0.005 V/m

tpur Power-Up to Read Operations 200 µs

tpuw Power-Up to Write or Store Operation 5 ms

Note:

(1) The store operation has priority over all the other operations.

(2) The store operation is inhibited when VCC is below ≈ 3.5V.

(3) NOP designates that the device is not currently executing an instruction.

(4) This parameter is tested initially and after a design or process change that affects the parameter.

© 2008 SCILLC. All rights reserved.

Doc. No. MD-1083, Rev. T 2 Characteristics subject to change without notice

CAT24C44

ABSOLUTE MAXIMUM RATINGS* *COMMENT

Temperature Under Bias ................. –55°C to +125°C Stresses above those listed under “Absolute Maximum

Storage Temperature ....................... –65°C to +150°C Ratings” may cause permanent damage to the device.

These are stress ratings only, and functional operation

Voltage on Any Pin with of the device at these or any other conditions outside of

Respect to Ground(2) ............. –2.0 to +VCC +2.0V those listed in the operational sections of this specifica-

VCC with Respect to Ground ............... –2.0V to +7.0V tion is not implied. Exposure to any absolute maximum

rating for extended periods may affect device perfor-

Package Power Dissipation mance and reliability.

Capability (Ta = 25°C) ................................... 1.0W

Lead Soldering Temperature (10 secs) ............ 300°C

Output Short Circuit Current(3) ........................ 100 mA

RELIABILITY CHARACTERISTICS

Symbol Parameter Min. Typ. Max. Units

NEND(1) Endurance 100,000 Cycles/Byte

TDR(1) Data Retention 10 Years

VZAP(1) ESD Susceptibility 2000 Volts

ILTH(1)(4) Latch-up 100 mA

D.C. OPERATING CHARACTERISTICS

VCC = 5V ±10%, unless otherwise specified.

Limits

Symbol Parameter Min. Typ. Max. Unit Conditions

ICCO Current Consumption (Operating) 3 mA Inputs = 5.5V, TA = 0°C

All Outputs Unloaded

ISB Current Consumption (Standby) 30 µA CE = VIL

ILI Input Current 2 µA 0 ≤ VIN ≤ 5.5V

ILO Output Leakage Current 10 µA 0 ≤ VOUT ≤ 5.5V

VIH High Level Input Voltage 2 VCC V

VIL Low Level Input Voltage 0 0.8 V

VOH High Level Output Voltage 2.4 V IOH = –2mA

VOL Low Level Output Voltage 0.4 V IOL = 4.2mA

CAPACITANCE TA = 25°C, f = 1.0 MHz, VCC = 5V

Symbol Parameter Max. Unit Conditions

CI/O (1) Input/Output Capacitance 10 pF VI/O = 0V

CIN(1) Input Capacitance 6 pF VIN = 0V

Note:

(1) These parameter are tested initially and after a design or process change that affects the parameter according to appropriate AEC-Q100

and JEDEC test methods.

(2) The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns.

Maximum DC voltage on output pins is VCC +0.5V, which may overshoot to VCC +2.0V for periods of less than 20 ns.

(3) Output shorted for no more than one second. No more than one output shorted at a time.

(4) Latch-up protection is provided for stresses up to 100 mA on address and data pins from –1V to VCC +1V.

© 2008 SCILLC. All rights reserved. Doc. No. MD-1083, Rev. T

Characteristics subject to change without notice 3

CAT24C44

A.C. CHARACTERISTICS

VCC = 5V ±10%, unless otherwise specified.

Symbol Parameter Min. Max. Units Conditions

FSK SK Frequency DC 1 MHz

tSKH SK Positive Pulse Width 400 ns

tSKL SK Negative Pulse Width 400 ns CL = 100pF + 1TTL gate

tDS Data Setup Time 400 ns VOH = 2.2V, VOL = 0.65V

tDH Data Hold Time 80 ns VIH = 2.2V, VIL = 0.65V

tPD SK Data Valid Time 375 ns Input rise and fall times = 10ns

tZ CE Disable Time 1 µs

tCES CE Enable Setup Time 800 ns

tCEH CE Enable Hold Time 400 ns

tCDS CE De-Select Time 800 ns

A.C. CHARACTERISTICS, Store Cycle

VCC = 5V ±10%, unless otherwise specified.

Limits

Symbol Parameter Min. Max. Units Conditions

tST Store Time 10 ms CL = 100pF + 1TTL gate

tSTP Store Pulse Width 200 ns VOH = 2.2V, VOL = 0.65V

tSTZ Store Disable Time 100 ns VIH = 2.2V, VIL = 0.65V

A.C. CHARACTERISTICS, Recall Cycle

VCC = 5V ±10%, unless otherwise specified.

Symbol Parameter Min. Max. Units Conditions

tRCC Recall Cycle Time 2.5 µs

tRCP Recall Pulse Width 500 ns CL = 100pF + 1TTL gate

tRCZ Recall Disable Time 500 ns VOH = 2.2V, VOL = 0.65V

tORC Recall Enable Time 10 ns VIH = 2.2V, VIL = 0.65V

tARC Recall Data Access Time 1.5 µs

INSTRUCTION SET

Format

Instruction Start Bit Address OP Code Operation

WRDS 1 XXXX 000 Reset Write Enable Latch (Disables, Writes and Stores)

STO 1 XXXX 001 Store RAM Data in EEPROM

WRITE 1 AAAA 011 Write Data into RAM Address AAAA

WREN 1 XXXX 100 Set Write Enable Latch (Enables, Writes and Stores)

RCL 1 XXXX 101 Recall EEPROM Data into RAM

READ 1 AAAA 11X Read Data From RAM Address AAAA

X = Don’t care

A = Address bit

© 2008 SCILLC. All rights reserved.

Doc. No. MD-1083, Rev. T 4 Characteristics subject to change without notice

CAT24C44

DEVICE OPERATION from the device: If the CE pin is prematurely deselected

while shifting in an instruction, that instruction will not be

The CAT24C44 is intended for use with standard micro- executed, and the shift register internal to the CAT24C44

processors. The CAT24C44 is organized as 16 registers will be cleared. If there are more than or less than 16

by 16 bits. Seven 8-bit instructions control the device’s clocks during a memory data transfer, an improper data

operating modes, the RAM reading and writing, and the transfer will result. The SK clock is completely static

EEPROM storing and recalling. It is also possible to allowing the user to stop the clock and restart it to

control the EEPROM store and recall functions in hard- resume shifting of data.

ware with the STORE and RECALL pins. The CAT24C44

operates on a single 5V supply and will generate, on Read

chip, the high voltage required during a RAM to EEPROM Upon receiving a start bit, 4 address bits, and the 3-bit

storing operation. read command (clocked into the DI pin), the DO pin of

the CAT24C44 will come out of the high impedance state

Instructions, addresses and write data are clocked into

and the 16 bits of data, located at the address specified

the DI pin on the rising edge of the clock (SK). The DO

in the instructions, will be clocked out of the device.

pin remains in a high impedance state except when

When clocking data from the device, the first bit clocked

outputting data from the device. The CE (Chip Enable)

out (DO) is timed from the falling edge of the 8th clock,

pin must remain high during the entire data transfer.

all succeeding bits (D1–D15) are timed from the rising

The format for all instructions sent to the CAT24C44 is edge of the clock.

a logical ‘1’ start bit, 4 address bits (data read or write

Write

operations) or 4 “Don’t Care” bits (device mode opera-

tions), and a 3-bit op code (see Instruction Set). For data After receiving a start bit, 4 address bits, and the 3-bit

write operations, the 8-bit instruction is followed by 16 WRITE command, the 16-bit word is clocked into the

bits of data. For data read instructions, DO will come out device for storage into the RAM memory location speci-

of the high impedance state and enable 16 bits of data fied. The CE pin must remain high during the entire write

to be clocked from the device. The 8th bit of the read operation.

instruction is a “Don’t Care” bit. This is to eliminate any

bus contention that would occur in applications where

the DI and DO pins are tied together to form a common

DI/DO line. A word of caution while clocking data to and

Figure 1. RAM Read Cycle Timing

CE

1 2 3 4 5 6 7 8 9 10 11 12 22 23 24

SK

(1)

(8)

DI 1 A A A AX 1 1

HIGH-Z

DO D0 D1 D2 D3 D14 D15 D0

Figure 2. RAM Write Cycle Timing

CE

1 2 3 4 5 6 7 8 9 10 11 12 22 23 24

SK

DI 1 A A A A1 0 1 D0 D1 D2 D3 D13 D14 D15

Note:

(1) Bit 8 of READ instruction is “Don’t Care”.

© 2008 SCILLC. All rights reserved. Doc. No. MD-1083, Rev. T

Characteristics subject to change without notice 5

CAT24C44

WREN/WRDS The WRDS (write/store disable) can be used to disable

The CAT24C44 powers up in the program disable state all CAT24C44 programming functions, and will prevent

(the “write enable latch” is reset). Any programming after any accidental writing to the RAM, or storing to the

power-up or after a WRDS (RAM write/EEPROM store EEPROM.

disable) instruction must first be preceded by the WREN Data can be read normally from the CAT24C44 regard-

(RAM write/EEPROM store enable) instruction. Once less of the “write enable latch” status.

writing/storing is enabled, it will remain enabled until

power to the device is removed, the WRDS instruction is

sent, or an EEPROM store has been executed (STO).

Figure 3. Read Cycle Timing

SK CYCLE # 6 7 8 9 10 11

SK

VIH

CE

tPD

DI

tPD tZ

HIGH-Z HIGH-Z

DO D0 D1 Dn

Figure 4. Write Cycle Timing

1/FSK

tSKH tSKL

SK x 1 2 n

tCES tCEH tCDS

CE

tDS tDH

DI

© 2008 SCILLC. All rights reserved.

Doc. No. MD-1083, Rev. T 6 Characteristics subject to change without notice

CAT24C44

RECALL

RCL/RECALL

inadvertent store operations, the following conditions

Data is transferred from the EEPROM data memory to must each be met before data can be transferred into

RAM by either sending the RCL instruction or by pulling nonvolatile storage:

the RECALL input pin low. A recall operation must be

performed before the EEPROM store, or RAM write • The “previous recall” latch must be set (either a

operations can be executed. Either a hardware or soft- software or hardware recall operation).

ware recall operation will set the “previous recall” latch

• The “write enable” latch must be set (WREN

internal to the CAT24C44.

instruction issued).

POWER-ON RECALL • STO instruction issued or STORE input low.

The CAT24C44 has a power-on recall function that During the store operation, all other CAT24C44 func-

transfers the EEPROM data to the RAM. After Power- tions are inhibited. Upon completion of the store opera-

up, all functions are inhibited for at least 200ns (Tpur) tion, the “write enable” latch is reset. The device also

from stable Vcc. provides false store protection whenever VCC falls below

a 3.5V level. If VCC falls below this level, the store

STORE

STO/STORE operation is disabled and the “write enable” latch is

Data in the RAM memory area is stored in the EEPROM reset.

memory either by sending the STO instruction or by

pulling the STORE input pin low. As security against any

Figure 5. Recall Cycle Timing

tRCC

tRCP

RECALL

tRCZ tARC

HIGH-Z

DO VALID DATA

tORC UNDEFINED DATA

Figure 6. Hardware Store Cycle Timing

tST

tSTP

STORE

tSTZ

HIGH-Z

DO

© 2008 SCILLC. All rights reserved. Doc. No. MD-1083, Rev. T

Characteristics subject to change without notice 7

CAT24C44

Figure 7. Non-Data Operations

CE

1 2 3 4 5 6 7 8

SK

DI 1 X X X X

OP-CODE

ORDERING INFORMATION

Prefix Device # Suffix

CAT 24C44 V I – G T3

Company ID Product Number Temperature Range T: Tape & Reel

24C44 I = Industrial (-40°C to +85°C) 3: 3,000/Reel

E = Extended (-40°C to +125°C)(4)

Package Lead Finish

L: PDIP G: NiPdAu

V: SOIC, JEDEC Blank: Matte-Tin

Notes:

(1) All packages are RoHS-compliant (Lead-free, Halogen-free).

(2) The device used in the above example is a CAT24C44VI-GT3 (SOIC, Industrial Temperature, NiPdAu, Tape & Reel, 3,000/Reel).

(3) For additional package option please contact your nearest ON Semiconductor Sales office.

(4) Extended Temperature available upon request.

© 2008 SCILLC. All rights reserved.

Doc. No. MD-1083, Rev. T 8 Characteristics subject to change without notice

CAT24C44

REVISION HISTORY

Date Revision Description

17-Apr-04 O Add Lead Free Logo

Update Features

Update Pin Configuration

Update Block Diagram

Update Instruction Set

Update Device Operation

Update Ordering Information

Add Revision History

Update Rev Number

16-Nov-04 P Update Pin Configuration

Update Ordering Information

17-Apr-04 Q Update Ordering Information

03-Aug-05 R Update Pin Configuration

Update Reliability Characteristics

Update Ordering Information

24-Jun-08 S Update Pin Configuration

Update Example of Ordering Information

04-Dec-08 T Change logo and fine print to ON Semiconductor

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to

any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising

out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All

operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights

of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications

intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should

Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,

and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal

Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: N. American Technical Support: 800-282-9855 ON Semiconductor Website: www.onsemi.com

Literature Distribution Center for ON Semiconductor Toll Free

P.O. Box 5163, Denver, Colorado 80217 USA USA/Canada Order Literature: http://www.onsemi.com/orderlit

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Phone: 421 33 790 2910 For additional information, please contact your local

Email: orderlit@onsemi.com Japan Customer Focus Center: Sales Representative

Phone: 81-3-5773-3850

© 2008 SCILLC. All rights reserved. Doc. No. MD-1083, Rev. T

Characteristics subject to change without notice 9

You might also like

- Solar Assisted Electric Bicycle Project ReportDocument40 pagesSolar Assisted Electric Bicycle Project ReportAnkit Das100% (3)

- SR 332 TOC.i01Document5 pagesSR 332 TOC.i01vspuriNo ratings yet

- Chapter 1-Introduction To The Semiconductor Industry-NEWDocument28 pagesChapter 1-Introduction To The Semiconductor Industry-NEWhrrameshhrNo ratings yet

- Type MCAG 14, 34: High Stability Circulating Current RelaysDocument30 pagesType MCAG 14, 34: High Stability Circulating Current Relaysrenjithas2005100% (2)

- CAT24C44: 256-Bit Serial Nonvolatile CMOS Static RAMDocument8 pagesCAT24C44: 256-Bit Serial Nonvolatile CMOS Static RAMvanmarteNo ratings yet

- 24C44Document8 pages24C44Dr.HlaNo ratings yet

- 8K/16K 5.0V Microwire Serial EEPROM: FeaturesDocument12 pages8K/16K 5.0V Microwire Serial EEPROM: FeaturesStephensonNo ratings yet

- X24C44 256 Bit 16 X 16 Bit: Features DescriptionDocument15 pagesX24C44 256 Bit 16 X 16 Bit: Features DescriptionJosé FariaNo ratings yet

- X24C44 256 Bit 16 X 16 Bit: Features DescriptionDocument16 pagesX24C44 256 Bit 16 X 16 Bit: Features DescriptionAgustin AndrokaitesNo ratings yet

- X24C44 256 Bit 16 X 16 Bit: Features DescriptionDocument16 pagesX24C44 256 Bit 16 X 16 Bit: Features DescriptionMarinaBogaoNo ratings yet

- 8K/16K 5.0V Microwire Serial EEPROM: Features: Package TypesDocument20 pages8K/16K 5.0V Microwire Serial EEPROM: Features: Package Typesfarhood ranjbarkhanghahNo ratings yet

- 8K/16K 5.0V I C Serial Eeproms: Features Package TypesDocument13 pages8K/16K 5.0V I C Serial Eeproms: Features Package Typesarunan55No ratings yet

- 93C86Document20 pages93C86cgmannerheimNo ratings yet

- Bus Serial EEPROMDocument12 pagesBus Serial EEPROMMatiasNo ratings yet

- 93C66Document12 pages93C66Alex AlvarezNo ratings yet

- NM24C04/05 - 4K-Bit Standard 2-Wire Bus Interface Serial EEPROMDocument14 pagesNM24C04/05 - 4K-Bit Standard 2-Wire Bus Interface Serial EEPROMAbel RodriguezNo ratings yet

- 24C16 FairchildSemiconductorDocument14 pages24C16 FairchildSemiconductorRavi ChavhanNo ratings yet

- 2K 5.0V Automotive Temperature Microwire Serial EEPROM: Features Package TypeDocument12 pages2K 5.0V Automotive Temperature Microwire Serial EEPROM: Features Package TypeDanielNo ratings yet

- Item 11 X24C16PDocument15 pagesItem 11 X24C16Pdifa20061168No ratings yet

- CAT25C32/64: 32K/64K-Bit SPI Serial CMOS E Prom FeaturesDocument9 pagesCAT25C32/64: 32K/64K-Bit SPI Serial CMOS E Prom FeaturesTeyfik koyuncuNo ratings yet

- FM24C08U/09U - 8K-Bit Standard 2-Wire Bus Interface Serial EEPROMDocument15 pagesFM24C08U/09U - 8K-Bit Standard 2-Wire Bus Interface Serial EEPROMlord_beast2.05No ratings yet

- 24AA00/24LC00/24C00: 128 Bit I C™ Bus Serial EEPROMDocument12 pages24AA00/24LC00/24C00: 128 Bit I C™ Bus Serial EEPROMmacepaNo ratings yet

- 24C320-EP MicrochipTechnologyDocument12 pages24C320-EP MicrochipTechnologyMateus CorrêaNo ratings yet

- TC58NS256DCDocument33 pagesTC58NS256DCFreddy AmayaNo ratings yet

- 1K/2K/4K 5.0V CMOS Serial EEPROM: Features Package TypeDocument8 pages1K/2K/4K 5.0V CMOS Serial EEPROM: Features Package TypeHarris RaoNo ratings yet

- IS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos EepromDocument16 pagesIS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos EepromPablo Diego Cecere CasadoNo ratings yet

- IS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos EepromDocument16 pagesIS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos EepromPablo Diego Cecere CasadoNo ratings yet

- CAT93C4611J-25TE13 To CAT93C8634UI-45TE13Document11 pagesCAT93C4611J-25TE13 To CAT93C8634UI-45TE13rolandseNo ratings yet

- NM93C06 256-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesNM93C06 256-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)fabiansandezNo ratings yet

- Datasheet PDFDocument26 pagesDatasheet PDFNicoli LourençoNo ratings yet

- At25128b 5eb PDFDocument22 pagesAt25128b 5eb PDFMurat BaybükeNo ratings yet

- S25fl512sagbhia13 Fab024Document145 pagesS25fl512sagbhia13 Fab024中井一朗No ratings yet

- NM93C66 4096-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesNM93C66 4096-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- 000 1 Ak93c75Document14 pages000 1 Ak93c75Leiden O'SullivanNo ratings yet

- DS83C530 DS87C530Document47 pagesDS83C530 DS87C530api-3728874No ratings yet

- X24C04 4K 512 X 8 Bit: 3839 FHD F01Document19 pagesX24C04 4K 512 X 8 Bit: 3839 FHD F01Legna80No ratings yet

- Spansion S25FL256S - 32MB SPI FlashromDocument149 pagesSpansion S25FL256S - 32MB SPI FlashromcockNo ratings yet

- Product Obsolete or Under Obsolescence: Xc1700E, Xc1700El, and Xc1700L Series Configuration PromsDocument13 pagesProduct Obsolete or Under Obsolescence: Xc1700E, Xc1700El, and Xc1700L Series Configuration PromsLaboratorio GTO Perú S.A.C.No ratings yet

- 25AA640/25LC640: 64K Spi Bus Serial EEPROMDocument12 pages25AA640/25LC640: 64K Spi Bus Serial EEPROMinsomnium86No ratings yet

- Datasheet 25c040Document22 pagesDatasheet 25c040Perona PabloNo ratings yet

- 25AA160/25LC160/25C160: 16K Spi Bus Serial EEPROMDocument23 pages25AA160/25LC160/25C160: 16K Spi Bus Serial EEPROMЕвгенийNo ratings yet

- 24AA256/24LC256: 256K I C Cmos Serial EepromDocument12 pages24AA256/24LC256: 256K I C Cmos Serial EepromWelleyNo ratings yet

- 42 45S32200LDocument59 pages42 45S32200LNelson Pimiento SerranoNo ratings yet

- Atmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetDocument20 pagesAtmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetalaitsevNo ratings yet

- TMC93LC46Document15 pagesTMC93LC46Agustin AndrokaitesNo ratings yet

- NM93CS66 (MICROWIRE™ Bus Interface) 4096-Bit Serial EEPROM With Data Protect and Sequential ReadDocument16 pagesNM93CS66 (MICROWIRE™ Bus Interface) 4096-Bit Serial EEPROM With Data Protect and Sequential Readinsomnium86No ratings yet

- CAT24WC32/64: 32K/64K-Bit I C Serial Cmos EepromDocument11 pagesCAT24WC32/64: 32K/64K-Bit I C Serial Cmos EepromAdnen GuedriaNo ratings yet

- 25AA320/25LC320/25C320: 32K Spi Bus Serial EEPROMDocument24 pages25AA320/25LC320/25C320: 32K Spi Bus Serial EEPROMHebertAlexMamaniSalomaNo ratings yet

- 256 Bit/1K 5.0V CMOS Serial EEPROM: Features Package TypeDocument8 pages256 Bit/1K 5.0V CMOS Serial EEPROM: Features Package TypeAgustin AndrokaitesNo ratings yet

- 64 Kbit (8 K X 8) Autostore Nvsram: Features Functional DescriptionDocument23 pages64 Kbit (8 K X 8) Autostore Nvsram: Features Functional DescriptionAmine EmineNo ratings yet

- T89C51RD2Document86 pagesT89C51RD2Julio CabralNo ratings yet

- 24AA02/24LC02B: 2KI C Serial EEPROMDocument32 pages24AA02/24LC02B: 2KI C Serial EEPROMhanifNo ratings yet

- MCP79410/MCP79411/MCP79412: I C™ Real-Time Clock/Calendar With EEPROM, SRAM, Unique ID and Battery SwitchoverDocument38 pagesMCP79410/MCP79411/MCP79412: I C™ Real-Time Clock/Calendar With EEPROM, SRAM, Unique ID and Battery SwitchoverDaniel CortelettiNo ratings yet

- Tc58dvm92a5ta00 ToshibaDocument38 pagesTc58dvm92a5ta00 ToshibaLorenzo TorresNo ratings yet

- 93LC66A/B: 4K 2.5V Microwire Serial EEPROMDocument12 pages93LC66A/B: 4K 2.5V Microwire Serial EEPROMinsomnium86No ratings yet

- 1K/2K 5.0V I C Serial EEPROM: Obsolete DeviceDocument10 pages1K/2K 5.0V I C Serial EEPROM: Obsolete DevicesixtodeathNo ratings yet

- AK93C45A / 55A / 65A / 75A: 1K / 2K / 4K / 8kbit Serial CMOS EEPROMDocument14 pagesAK93C45A / 55A / 65A / 75A: 1K / 2K / 4K / 8kbit Serial CMOS EEPROMmansoorhayatNo ratings yet

- Three-Wire Serial EEPROM: 1. FeaturesDocument17 pagesThree-Wire Serial EEPROM: 1. FeatureskppsadiNo ratings yet

- Logic Powered Serial Eeproms: Parameter ConditionsDocument11 pagesLogic Powered Serial Eeproms: Parameter ConditionsadilNo ratings yet

- X28C64 64K 8K X 8 Bit: Plastic Dip Cerdip Flat Pack Soic Tsop LCC PLCCDocument26 pagesX28C64 64K 8K X 8 Bit: Plastic Dip Cerdip Flat Pack Soic Tsop LCC PLCCEdson CostaNo ratings yet

- 32K 5.0V I C Smart Serial EEPROM: Features Package TypesDocument12 pages32K 5.0V I C Smart Serial EEPROM: Features Package TypesRamon LopezNo ratings yet

- 28F256 AdvancedMicroDevicesDocument35 pages28F256 AdvancedMicroDevicessara mehdipourNo ratings yet

- 24aa08 - 24lc08 Eeprom PDFDocument40 pages24aa08 - 24lc08 Eeprom PDFEdgar DauzonNo ratings yet

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- Adc 3g AP-fcxxxxm0nxx-2tx Spec Rev1.1Document16 pagesAdc 3g AP-fcxxxxm0nxx-2tx Spec Rev1.1vspuriNo ratings yet

- Audiocodes Enabling Technology Products Smartworks™ LD SeriesDocument2 pagesAudiocodes Enabling Technology Products Smartworks™ LD SeriesvspuriNo ratings yet

- Ner 65lc Nit 15sep15Document4 pagesNer 65lc Nit 15sep15vspuriNo ratings yet

- Expanded: Conductive Polymer Aluminum Solid Electrolytic CapacitorsDocument3 pagesExpanded: Conductive Polymer Aluminum Solid Electrolytic CapacitorsvspuriNo ratings yet

- Ner 65lc 15sep15Document73 pagesNer 65lc 15sep15vspuriNo ratings yet

- Tender Document: Installation of 20 KWP Stand Alone SPV SOLAR Power Plant at SBBJ STC BikanerDocument19 pagesTender Document: Installation of 20 KWP Stand Alone SPV SOLAR Power Plant at SBBJ STC BikanervspuriNo ratings yet

- Brief Note On Guidelines Under DERC (Net Metering For Renewable Energy) Regulations, 2014Document1 pageBrief Note On Guidelines Under DERC (Net Metering For Renewable Energy) Regulations, 2014vspuriNo ratings yet

- Application Guide: ESD ProtectionDocument28 pagesApplication Guide: ESD ProtectionvspuriNo ratings yet

- Halogen-Free FK: Aluminum Electrolytic Capacitors V Surface Mount TypeDocument10 pagesHalogen-Free FK: Aluminum Electrolytic Capacitors V Surface Mount TypevspuriNo ratings yet

- Tektronix TFS3031 1Document4 pagesTektronix TFS3031 1vspuri100% (1)

- Ceramic Transient Voltage Suppressors, CTVS: Protection Standards For Electromagnetic Compatibility (EMC)Document9 pagesCeramic Transient Voltage Suppressors, CTVS: Protection Standards For Electromagnetic Compatibility (EMC)vspuriNo ratings yet

- EEE 514 Power ElectronicsDocument4 pagesEEE 514 Power ElectronicsJoshua ObedNo ratings yet

- A Simple Method To Detect The Displacement Current in The CapacitorDocument3 pagesA Simple Method To Detect The Displacement Current in The Capacitorandy1144552No ratings yet

- Tiny TR5001Document2 pagesTiny TR5001Arthur Demah BardosNo ratings yet

- Small Clone Chorus (Heladito02) PDFDocument2 pagesSmall Clone Chorus (Heladito02) PDFjoaco565100% (1)

- Curriculum Manual Chapter: IT02 Temperature Measurement 4Document24 pagesCurriculum Manual Chapter: IT02 Temperature Measurement 4Rizda OktavianaNo ratings yet

- The Bias Condition For A Transistor To Be Used As A Linear Amplifier Is CalledDocument10 pagesThe Bias Condition For A Transistor To Be Used As A Linear Amplifier Is CalledMansoor AslamNo ratings yet

- Exit PreparationDocument92 pagesExit PreparationERMIAS AmanuelNo ratings yet

- Routine Tests For Oil Immersed TransformersDocument14 pagesRoutine Tests For Oil Immersed TransformersFreddie Asiedu LarbiNo ratings yet

- 1200 PDFDocument9 pages1200 PDFeidelsayedNo ratings yet

- MAX485 DatasheetDocument19 pagesMAX485 DatasheetShubra DebNo ratings yet

- RS1117Document10 pagesRS1117asismamenNo ratings yet

- 150Khz, 3A PWM Buck DC/DC Converter: (Top View)Document14 pages150Khz, 3A PWM Buck DC/DC Converter: (Top View)Syed Ejaz Hussain AbidiNo ratings yet

- Chapter 6 - Electrostatic Boundary - Value ProblemsDocument38 pagesChapter 6 - Electrostatic Boundary - Value ProblemsMarc Rivera100% (1)

- Assignment 2 - NTK PDFDocument2 pagesAssignment 2 - NTK PDFnigus hailuNo ratings yet

- Hardware QuestionsDocument3 pagesHardware QuestionsFaisal RahimNo ratings yet

- 1500watts Power Amp.Document27 pages1500watts Power Amp.Dinah Nicole88% (16)

- Micro Electronic PillDocument2 pagesMicro Electronic PillDevendra Singh RajpurohitNo ratings yet

- Irf 5305 PBFDocument9 pagesIrf 5305 PBFGuillermoNo ratings yet

- 2019 VLSI Fully Integrated Coherent LiDAR in 3D-Integrated Silicon Photonics65nm CMOS PDFDocument2 pages2019 VLSI Fully Integrated Coherent LiDAR in 3D-Integrated Silicon Photonics65nm CMOS PDFnxp HeNo ratings yet

- HDHW Mcq-Ar Current Electricity Xii 2024Document10 pagesHDHW Mcq-Ar Current Electricity Xii 2024Shashwat SinghNo ratings yet

- Electricalindia - in Our MagazinesDocument6 pagesElectricalindia - in Our MagazinesDILEPNo ratings yet

- Ect02 2Document30 pagesEct02 2Ralph Jayson SilangNo ratings yet

- Siem Spareparts MasterDrDocument8 pagesSiem Spareparts MasterDrMuhdiNo ratings yet

- Ad5260 5262Document24 pagesAd5260 5262DHIRENNo ratings yet

- Amd 64 3000 PDFDocument21 pagesAmd 64 3000 PDFMelody CottonNo ratings yet

- SSR in DFIG SystemsDocument49 pagesSSR in DFIG SystemsHossein_jujujuNo ratings yet

- Synchronous Rectification For Forward ConvertersDocument19 pagesSynchronous Rectification For Forward ConvertersfabianoaddorNo ratings yet