Professional Documents

Culture Documents

SedraSmith8e Chapter 11 SpiceProblemGuide

SedraSmith8e Chapter 11 SpiceProblemGuide

Uploaded by

Fahrettin Beyazıt TokatCopyright:

Available Formats

You might also like

- Certified Secure Computer User Exam Question PrepareDocument5 pagesCertified Secure Computer User Exam Question Preparekouassi joel100% (2)

- Microelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetDocument20 pagesMicroelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetharithNo ratings yet

- Non-Isolated Buck APFC Offline LED Driver Description FeaturesDocument9 pagesNon-Isolated Buck APFC Offline LED Driver Description FeaturesEsmailNo ratings yet

- CIS Community Defense Model v2.0Document50 pagesCIS Community Defense Model v2.0darkblade310No ratings yet

- Chap 05 HMWK SolDocument72 pagesChap 05 HMWK Solapi-3841575No ratings yet

- PG - Manual - MNIT JaipurDocument60 pagesPG - Manual - MNIT JaipurmanaliamitNo ratings yet

- Microelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetDocument7 pagesMicroelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetBadawath NareshNo ratings yet

- RAC-ASM-VOTING DISK Interview Questions & AnswerDocument18 pagesRAC-ASM-VOTING DISK Interview Questions & AnswerNuhu Magwai100% (1)

- Microelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetDocument7 pagesMicroelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetBadawath NareshNo ratings yet

- Microelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetDocument14 pagesMicroelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. Gaudetgain xing GuoNo ratings yet

- VLSI Lab ManualDocument77 pagesVLSI Lab ManualSriramNo ratings yet

- Sedra8e Solvedproblems ch09-2 PDFDocument24 pagesSedra8e Solvedproblems ch09-2 PDFJoh CheNo ratings yet

- Premium EmbeddedDocument61 pagesPremium EmbeddedthehickNo ratings yet

- A Guide To Reduce The Phase Noise Effect in FMCW RadarsDocument4 pagesA Guide To Reduce The Phase Noise Effect in FMCW RadarsAndreea IonescuNo ratings yet

- Chenming Hu Ch8Document34 pagesChenming Hu Ch8Roberto Rojas PizarroNo ratings yet

- Fingerprint Based Electronic Voting MachineDocument20 pagesFingerprint Based Electronic Voting MachineAnjali yadavNo ratings yet

- Hi-Tech Picc-18 STDDocument490 pagesHi-Tech Picc-18 STDSandro BassNo ratings yet

- B. P. Lathi, Zhi Ding - Modern Digital and Analog Communication Systems-Oxford University Press (2009) PDFDocument927 pagesB. P. Lathi, Zhi Ding - Modern Digital and Analog Communication Systems-Oxford University Press (2009) PDFMyDude IsHungryNo ratings yet

- Symmetrical Fault in Power SystemDocument14 pagesSymmetrical Fault in Power Systemstudents answerNo ratings yet

- Frequency Locked Loop DC Motor Speed Control and Monitoring SystemDocument98 pagesFrequency Locked Loop DC Motor Speed Control and Monitoring SystemCHILUKA CHANDRAKANTHNo ratings yet

- Ece 311Document2 pagesEce 311MEHEDI HASANNo ratings yet

- 9781292038957Document5 pages9781292038957123r0% (1)

- 0 - MPMC Lab Manual A.Y. 2020-21 R-18Document53 pages0 - MPMC Lab Manual A.Y. 2020-21 R-18Karthik BoggarapuNo ratings yet

- Pss Lab Manual NewDocument128 pagesPss Lab Manual NewchandrakanthNo ratings yet

- Introduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)Document27 pagesIntroduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)TygerYashanshuNo ratings yet

- Intensity ModulationDocument3 pagesIntensity Modulationanon-323096100% (1)

- Digital Voltmeter Using PIC MicrocontrollerDocument7 pagesDigital Voltmeter Using PIC MicrocontrollerbecemNo ratings yet

- Upgrading Embedded Design Firmware Via USBDocument5 pagesUpgrading Embedded Design Firmware Via USBreemaroy08100% (1)

- 11 - Comparator Based Analog To Digital ConvertersDocument80 pages11 - Comparator Based Analog To Digital ConvertersjoshNo ratings yet

- Valliammai Engineering College: Question BankDocument18 pagesValliammai Engineering College: Question Banksivamani CHINNASWAMYNo ratings yet

- Wearable Oscilloscope Smart WatchDocument2 pagesWearable Oscilloscope Smart Watchالمخترع الصغير2100% (1)

- ns-3: Open Source Simulator For Wireless Network Performance EvaluationDocument86 pagesns-3: Open Source Simulator For Wireless Network Performance EvaluationAli IbraheemNo ratings yet

- CS3391 OOPS UNIT 4 NOTES EduEnggDocument27 pagesCS3391 OOPS UNIT 4 NOTES EduEnggAravind SamyNo ratings yet

- Sample 7668Document11 pagesSample 7668Chintapalli Ramesh KumarNo ratings yet

- Implementation of Wireless LAN Using Cisco Packet TracerDocument5 pagesImplementation of Wireless LAN Using Cisco Packet TracerN KNo ratings yet

- Microprocessors and Microsystems: V.J. Arulkarthick, Abinaya Rathinaswamy, K. SrihariDocument9 pagesMicroprocessors and Microsystems: V.J. Arulkarthick, Abinaya Rathinaswamy, K. SrihariRamesh NairNo ratings yet

- LPC 2129Document44 pagesLPC 2129Pra ReddyNo ratings yet

- CH 6 Fundamental of MIcroelectronics Bahzad Razavi Chapter 6 Solution ManualDocument55 pagesCH 6 Fundamental of MIcroelectronics Bahzad Razavi Chapter 6 Solution ManualSumra MaqboolNo ratings yet

- Ip Lab ManualDocument52 pagesIp Lab Manualanuj1166No ratings yet

- Ee225 Lab 2Document10 pagesEe225 Lab 2Sherlin Chand100% (1)

- EEEB273 N05 - Diff Amp BJT x6 PDFDocument7 pagesEEEB273 N05 - Diff Amp BJT x6 PDFNur AdhiraaNo ratings yet

- Current Mode SignallingDocument2 pagesCurrent Mode SignallingThomas JosephNo ratings yet

- Project Report DPM 07202020150504Document45 pagesProject Report DPM 07202020150504Adharsh R nairNo ratings yet

- Samsung 940FN PDFDocument66 pagesSamsung 940FN PDFsupriyo110No ratings yet

- Tmote Sky DatasheetDocument28 pagesTmote Sky Datasheetshiva_59_59No ratings yet

- UbiSense User ManualDocument5 pagesUbiSense User ManualAshok Kumar100% (1)

- Unmanned Petrol Bunk ProjectDocument90 pagesUnmanned Petrol Bunk ProjectNaveenSvNo ratings yet

- Chapter13 - Memory and Programmable LogicDocument26 pagesChapter13 - Memory and Programmable LogicSrasVelNo ratings yet

- Emb Lab Manual FinalDocument142 pagesEmb Lab Manual FinalSatheesh Kumar100% (1)

- Curso Pic24j60Document173 pagesCurso Pic24j60Diojan Torres100% (1)

- RFID Based Attendance System With Storing Data On Google SpreadsheetDocument39 pagesRFID Based Attendance System With Storing Data On Google SpreadsheetKing YadavNo ratings yet

- Zxevo User Manual Revc EngDocument19 pagesZxevo User Manual Revc EngConrad RussoNo ratings yet

- Installing Network Card & Its Driver: TheoryDocument14 pagesInstalling Network Card & Its Driver: Theorymrcopy xeroxNo ratings yet

- Esa Mcbesa Mcb51 User Manual 51Document28 pagesEsa Mcbesa Mcb51 User Manual 51abcdNo ratings yet

- Lab 10 NSGDocument3 pagesLab 10 NSGMuhammad Awais ShahNo ratings yet

- IPDP BookDocument25 pagesIPDP BookkenilNo ratings yet

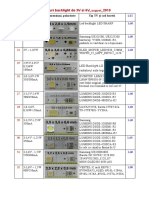

- Oferta Leduri Backlight de 3V Si 6V - August - 2019 PDFDocument19 pagesOferta Leduri Backlight de 3V Si 6V - August - 2019 PDFleontindemeterNo ratings yet

- ELTU3014Document2 pagesELTU3014王睿琛No ratings yet

- Tiva C Series LaunchPadDocument13 pagesTiva C Series LaunchPadVivek ShrigiriNo ratings yet

- SedraSmith8e Chapter 09 SpiceProblemGuideDocument15 pagesSedraSmith8e Chapter 09 SpiceProblemGuideEva LoNo ratings yet

- SedraSmith8xe Chapter9 SpiceProblemGuideDocument7 pagesSedraSmith8xe Chapter9 SpiceProblemGuidea28726996No ratings yet

- 0ebc543a-e9f5-4c31-8fb5-69a3ef1a537eDocument6 pages0ebc543a-e9f5-4c31-8fb5-69a3ef1a537eWilliam WadeNo ratings yet

- Fireclass Prec En13 User - 0Document13 pagesFireclass Prec En13 User - 0axwellNo ratings yet

- March 16 - IM Processors DigiTimesDocument5 pagesMarch 16 - IM Processors DigiTimesRyanNo ratings yet

- A Quick and Dirty History: Computer Operating System Command Line InterfaceDocument5 pagesA Quick and Dirty History: Computer Operating System Command Line InterfaceSaleem WaniNo ratings yet

- FusionCompute V100R005C00 Storage Virtualization PDFDocument46 pagesFusionCompute V100R005C00 Storage Virtualization PDFHelder FernandoNo ratings yet

- 2.5 Azure Management InterfacesDocument14 pages2.5 Azure Management Interfacesazhar aliNo ratings yet

- Cisco VTP Notes Part 2 Cheat Sheet Network WalksDocument1 pageCisco VTP Notes Part 2 Cheat Sheet Network WalksJon Carlo R. ChavezNo ratings yet

- Bca III Nov2016 Computer OrganizationDocument2 pagesBca III Nov2016 Computer OrganizationneiceNo ratings yet

- 003 RF Power ModulesDocument6 pages003 RF Power ModulesPaola DiazNo ratings yet

- Adaptive Server Enterprise: Performance and Tuning Series: Monitoring TablesDocument66 pagesAdaptive Server Enterprise: Performance and Tuning Series: Monitoring TableslocutoNo ratings yet

- STG sg2Document162 pagesSTG sg2Radwa EL-MahdyNo ratings yet

- Parallel SysplexDocument4 pagesParallel SysplexJasiekNo ratings yet

- SAP How To Step by Step Guide With Screen ShotDocument16 pagesSAP How To Step by Step Guide With Screen ShotPriyesh ET100% (1)

- Dsa File by AksDocument44 pagesDsa File by AksDeepakNo ratings yet

- V320BJ2 P01 Cmimei PDFDocument27 pagesV320BJ2 P01 Cmimei PDFLuis MezaNo ratings yet

- Smart Energy Monitoring System and Optimization of Energy ConsumptionDocument141 pagesSmart Energy Monitoring System and Optimization of Energy ConsumptionSelim KhanNo ratings yet

- Data Preprocessing - Ipynb - ColaboratoryDocument7 pagesData Preprocessing - Ipynb - ColaboratorySuresh KumarNo ratings yet

- Dvcpro FormatDocument80 pagesDvcpro FormatOlga EscaurizaNo ratings yet

- Mitsubishi FX1N Yj ManualDocument124 pagesMitsubishi FX1N Yj ManualSandi PratamaNo ratings yet

- Arm Cortex r52 Technical Reference Manual 100026 0102 00 en PDFDocument633 pagesArm Cortex r52 Technical Reference Manual 100026 0102 00 en PDFanomin89No ratings yet

- Installing Linux - The Easy WayDocument13 pagesInstalling Linux - The Easy WayVinay HegdeNo ratings yet

- Operation Manual: Digital Ultrasonic Flaw DetectorDocument70 pagesOperation Manual: Digital Ultrasonic Flaw DetectorJonathan MeloNo ratings yet

- Iot Tech NeoDocument177 pagesIot Tech Neokarunesh.shivade100% (1)

- 2015 08 SoMa PS en MaxWeb XPDocument2 pages2015 08 SoMa PS en MaxWeb XPEligius MartinezNo ratings yet

- EXPERIMENT NO 4 Circuits1l Wps PDFDocument9 pagesEXPERIMENT NO 4 Circuits1l Wps PDFMiguel VillarroelNo ratings yet

- Request Stock & Price July 23Document35 pagesRequest Stock & Price July 23Rafael RogelNo ratings yet

- PR Interfaces ID1078628 enDocument40 pagesPR Interfaces ID1078628 enEdwars GuerreroNo ratings yet

- IAUA120N04S5N014 InfineonDocument12 pagesIAUA120N04S5N014 InfineonLatthawitSanNo ratings yet

- Get-VBRServer - Veeam Backup PowerShell ReferenceDocument3 pagesGet-VBRServer - Veeam Backup PowerShell ReferenceAnderson SilvaNo ratings yet

SedraSmith8e Chapter 11 SpiceProblemGuide

SedraSmith8e Chapter 11 SpiceProblemGuide

Uploaded by

Fahrettin Beyazıt TokatCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SedraSmith8e Chapter 11 SpiceProblemGuide

SedraSmith8e Chapter 11 SpiceProblemGuide

Uploaded by

Fahrettin Beyazıt TokatCopyright:

Available Formats

Microelectronic Circuits

8th Edition

A. Sedra, K.C. Smith

T. Chan Carusone, V. Gaudet

Spice Problems Solutions

Chapter 11

Prepared by: Nijwm Wary

2019

© Oxford University Press, 2020

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

Problem: 11.37

1. The schematic with the feedback loop opened at the gate of 𝑄𝑄2 is shown below.

2. Run the netlist and perform operating point analysis. The node voltages are given below.

3. The currents, overdrive voltage (VDSAT), g m , and r o (1/g ds ) of the transistors are tabulated by

the operating point analysis below.

4. Plot V(VSIG) and V(VO) as shown below and find the gain.

1 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

5. The gain is -28.7 V/V. This confirms that the feedback is negative.

6. The value of R o can be calculated from g m5 and g ds5 . It is 1/g m5 ||1/g ds5 =640 Ω.

7. The schematic for part (e) of this problem is shown below

2 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

8. Perform a transient analysis and plot V(VO) and V(VSIG) to find the gain. Note that in this case

I4 has zero current amplitude.

9. The gain is 0.96 V/V.

10. To calculate the output impedance, make the AC amplitude of I4 1Aac and run an AC simulation.

Plot V(VO)/I(I4), as shown below

11. The output impedance is 20.66 Ω

3 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

12. The schematic for part (f) of this problem is shown below

13. Perform the transient analysis and plot V(VO) and V(VSIG) and find out the new gain.

4 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

14. The gain is 5.13 V/V.

15. To calculate the output impedance, run the AC simulation and plot V(VO)/I(I4)

16. The output impedance is 108.57 Ω.

Netlist:

For part (b) and (c), copy the netlist given below and paste it into a text file and save it with *.cir

extension.

********Problem: P11_37(b),(c) and (d) ***************

******* Main circuit begins here**************

V_DD VDD 0 1Vdc

I3 VO VSS DC 100uAdc

I2 VD4 VSS DC 300uAdc

I1 VS12 VSS DC 200uAdc

V_SS 0 VSS 1Vdc

M1 VD1 0 VS12 0 NMOS0P18

+ L=0.36u

+ W=8u

+ M=1

M2 VDD VSIG VS12 0 NMOS0P18

+ L=0.36u

+ W=8u

+ M=1

M3 VD1 VD1 VDD VDD PMOS0P18

+ L=0.36u

5 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

+ W=32u

+ M=1

M4 VD4 VD1 VDD VDD PMOS0P18

+ L=0.36u

+ W=96u

+ M=1

M5 VDD VD4 VO 0 NMOS0P18

+ L=0.36u

+ W=8u

+ M=1

V2 VSIG 0 AC 10m

+SIN 0 10m 1k 0 0 0

******* Main circuit ends here***************

***************** PMOS model begins here ******************************

* Level-1 Model for PMOS in model 0.18um CMOS Technology

.model PMOS0P18 PMOS(Level=1 VTO=-0.35 GAMMA=0.3 PHI=0.8

+ LD=0 WD=0 UO=118 LAMBDA=0.28 TOX=4.08E-9 PB=0.9)

***************** PMOS model ends here *****************************************

***************** NMOS model begins here ******************************

* Level-1 Model for NMOS in model 0.18um CMOS Technology

.model NMOS0P18 NMOS(Level=1 VTO=0.35 GAMMA=0.3 PHI=0.84

+ LD=0 WD=0 UO=473 LAMBDA=0.28 TOX=4.08E-9 PB=0.9)

***************** NMOS model ends here *****************************************

******** Analysis begins here****************

.OP

.TRAN 0.01mS 2mS

.PROBE

.END

******** Analysis ends here****************

For part (e), copy the netlist given below and paste it into a text file and save it with *.cir extension.

********Problem: P11_37(e) ***************

******* Main circuit begins here**************

V_DD VDD 0 1Vdc

I3 VO VSS DC 100uAdc

I2 VD4 VSS DC 300uAdc

I1 VS12 VSS DC 200uAdc

V_SS 0 VSS 1Vdc

M1 VD1 VSIG VS12 0 NMOS0P18

+ L=0.36u

+ W=8u

+ M=1

M2 VDD VO VS12 0 NMOS0P18

+ L=0.36u

+ W=8u

+ M=1

M3 VD1 VD1 VDD VDD PMOS0P18

+ L=0.36u

+ W=32u

+ M=1

M4 VD4 VD1 VDD VDD PMOS0P18

+ L=0.36u

+ W=96u

+ M=1

M5 VDD VD4 VO 0 NMOS0P18

+ L=0.36u

+ W=8u

+ M=1

V1 VSIG 0 AC 0

6 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

+SIN 0 10m 1k 0 0 0

I4 VO 0 DC 0Adc AC 1Aac

+SIN 0 0 1k 0 0 0

******* Main circuit ends here***************

***************** PMOS model begins here ******************************

* Level-1 Model for PMOS in model 0.18um CMOS Technology

.model PMOS0P18 PMOS(Level=1 VTO=-0.35 GAMMA=0.3 PHI=0.8

+ LD=0 WD=0 UO=118 LAMBDA=0.28 TOX=4.08E-9 PB=0.9)

***************** PMOS model ends here *****************************************

***************** NMOS model begins here ******************************

* Level-1 Model for NMOS in model 0.18um CMOS Technology

.model NMOS0P18 NMOS(Level=1 VTO=0.35 GAMMA=0.3 PHI=0.84

+ LD=0 WD=0 UO=473 LAMBDA=0.28 TOX=4.08E-9 PB=0.9)

***************** NMOS model ends here *****************************************

******** Analysis begins here****************

.OP

.TRAN 0.01mS 2mS

*.AC DEC 20 1 100K

.PROBE

.END

******** Analysis ends here****************

For part (f), copy the netlist given below and paste it into a text file and save it with *.cir extension.

********Problem: P11_37(f) ***************

******* Main circuit begins here*************

V_DD VDD 0 1Vdc

I3 VO VSS DC 100uAdc

I2 VD4 VSS DC 300uAdc

I1 VS12 VSS DC 200uAdc

V_SS 0 VSS 1Vdc

M1 VD1 VSIG VS12 0 NMOS0P18

+ L=0.36u

+ W=8u

+ M=1

M2 VDD VG2 VS12 0 NMOS0P18

+ L=0.36u

+ W=8u

+ M=1

M3 VD1 VD1 VDD VDD PMOS0P18

+ L=0.36u

+ W=32u

+ M=1

M4 VD4 VD1 VDD VDD PMOS0P18

+ L=0.36u

+ W=96u

+ M=1

M5 VDD VD4 VO 0 NMOS0P18

+ L=0.36u

+ W=8u

+ M=1

V1 VSIG 0 AC 0

+SIN 0 10m 1k 0 0 0

I4 VO 0 DC 0Adc AC 0Aac

+SIN 0 0 1k 0 0 0

R1 0 VG2 1MEG TC=0,0

R2 VO VG2 5.39MEG TC=0,0

******* Main circuit ends here***************

***************** PMOS model begins here ******************************

7 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

* Level-1 Model for PMOS in model 0.18um CMOS Technology

.model PMOS0P18 PMOS(Level=1 VTO=-0.35 GAMMA=0.3 PHI=0.8

+ LD=0 WD=0 UO=118 LAMBDA=0.28 TOX=4.08E-9 PB=0.9)

***************** PMOS model ends here *****************************************

***************** NMOS model begins here ******************************

* Level-1 Model for NMOS in model 0.18um CMOS Technology

.model NMOS0P18 NMOS(Level=1 VTO=0.35 GAMMA=0.3 PHI=0.84

+ LD=0 WD=0 UO=473 LAMBDA=0.28 TOX=4.08E-9 PB=0.9)

***************** NMOS model ends here *****************************************

******** Analysis begins here****************

.OP

.TRAN 0.01mS 2mS

*.AC DEC 20 1 100K

.PROBE

.END

******** Analysis ends here****************

8 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

Problem: 11.58

1. The schematic for this problem is shown below.

2. For part (a), run the netlist and perform operating point analysis and find out the node voltages

and currents.

3. For part (c), perform AC analysis and plot I(VOUT)/V(VIN) as shown below.

9 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

4. So, A f is 99 µA/V.

5. For part (d) to calculate the Rout, make the AC amplitude of VS zero and that of VOUT 1Vac as

shown below.

VS VIN 0 AC 0Vac

.

.

VOUT OUT 0 AC 1Vac

6. Perform an AC analysis and plot V(OUT) /I(VOUT) as shown below.

7. So, Rout is 214.4 MΩ.

10 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

8. The schematic for part (e) is shown below

9. Run the netlist and plot the DB(V(OUT)/ V(VIN)) in dB.

10. The gain is 0.98 V/V

11 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

11. Now make the AC amplitude of VS zero and the AC amplitude of I3 as 1. Then run the AC

simulation again and plot V(OUT)/I(I3) as shown below

12. The output impedance is 1.07 Ω.

Netlist:

Copy the netlist given below and paste it into a text file and save it with *.cir extension.

********Problem: P11_58***************

******* Main circuit begins here**************

M1 VD1 VG1 VS12 VS12 NMOS0P5

+ L=0.5u

+ W=14u

+ M=1

M2 VD2 VG2 VS12 VS12 NMOS0P5

+ L=0.5u

+ W=14u

+ M=1

M3 VD1 VD1 VDD VDD PMOS0P5

+ L=0.5u

+ W=55u

+ M=1

M4 VD2 VD1 VDD VDD PMOS0P5

+ L=0.5u

+ W=55u

+ M=1

I1 VS12 VSS DC 0.2mAdc

M5 OUT VD2 VG2 VG2 NMOS0P5

+ L=0.5u

+ W=105u

+ M=1

I2 VG2 VSS DC 0.8mAdc

12 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

V1 VDD 0 1.2Vdc

V2 0 VSS 1.2Vdc

VS VIN 0 AC 1Vac

+SIN 0 10m 1k 0 0 0

R1 0 VG2 10k TC=0,0

R2 VG1 VIN 10k TC=0,0

VOUT OUT 0 AC 0Vac

+SIN 1.2 0 1k 0 0 0

******* Main circuit ends here***************

***************** PMOS model begins here ******************************

.model PMOS0P5 PMOS(Level=1 VTO=-0.4 GAMMA=0.05 PHI=0.8

+ LD=0 WD=0 UO=115 LAMBDA=0.05 TOX=9.5E-9 PB=0.9)

***************** PMOS model ends here *****************************************

***************** NMOS model begins here ******************************

.model NMOS0P5 NMOS(Level=1 VTO=0.4 GAMMA=0.05 PHI=0.8

+ LD=0 WD=0 UO=460 LAMBDA=0.05 TOX=9.5E-9 PB=0.9)

***************** NMOS model ends here *****************************************

******** Analysis begins here****************

.OP

.AC DEC 20 1 100K

.PROBE

.END

******** Analysis ends here****************

Copy the netlist given below for part (e) and paste it into a text file and save it with *.cir extension.

********Problem: P11_58 (e)***************

******* Main circuit begins here*************

M1 VD1 VG1 VS12 0 NMOS0P5

+ L=0.5u

+ W=14u

+ M=1

M2 VD2 OUT VS12 0 NMOS0P5

+ L=0.5u

+ W=14u

+ M=1

M3 VD1 VD1 VDD VDD PMOS0P5

+ L=0.5u

+ W=55u

+ M=1

M4 VD2 VD1 VDD VDD PMOS0P5

+ L=0.5u

+ W=55u

+ M=1

I1 VS12 VSS DC 0.2mAdc

M5 N16841 VD2 OUT 0 NMOS0P5

+ L=0.5u

+ W=105u

+ M=1

I2 OUT VSS DC 0.8mAdc

V1 VDD 0 1.2Vdc

V2 0 VSS 1.2Vdc

VS VIN 0 AC 1Vac

+SIN 0 10m 1k 0 0 0

R1 0 OUT 10k TC=0,0

13 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

R2 VG1 VIN 10k TC=0,0

V3 N16841 0 1.2Vdc

I3 OUT 0 DC 0Adc AC 0

+SIN 0 0 1 0 0 0

******* Main circuit ends here***************

***************** PMOS model begins here ******************************

.model PMOS0P5 PMOS(Level=1 VTO=-0.4 GAMMA=0.05 PHI=0.8

+ LD=0 WD=0 UO=115 LAMBDA=0.05 TOX=9.5E-9 PB=0.9)

***************** PMOS model ends here *****************************************

***************** NMOS model begins here ******************************

.model NMOS0P5 NMOS(Level=1 VTO=0.4 GAMMA=0.05 PHI=0.8

+ LD=0 WD=0 UO=460 LAMBDA=0.05 TOX=9.5E-9 PB=0.9)

***************** NMOS model ends here *****************************************

******** Analysis begins here****************

.AC DEC 20 1 100K

.PROBE

.END

******** Analysis ends here****************

14 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

Problem: 11.79

1. The schematic for this problem is shown below

2. The node voltages are

3. The operating conditions of the transistors are

4. Run the transient simulation and plot V(VO) and V(VSIG) to get the gain

15 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

5. The gain is 3.3 V/V.

6. Plot V(N1)/I(RS) to calculate the input resistance.

7. The input resistance is 322 Ω.

16 © Oxford University Press, 2020 Chapter 11

Sedra/Smith, Microelectronic Circuits, Eighth Edition, Spice solutions

Netlist:

For part (b) and (c), copy the netlist given below and paste it into a text file and save it with *.cir

extension.

********Problem: P11_79 ***************

******* Main circuit begins here**************

RS VSIG N1 10k

RF N1 Q2E 10k

RE 0 Q2E 140

I1 VCC Q1C DC 200uAdc

RL VO VCC 500

V_CC VCC 0 15Vdc

Q1 Q1C N1 0 QECL

Q2 VO Q1C Q2E QECL

VS VSIG 0 AC 50m

+SIN 0 50m 1k 0 0 0

******* Main circuit ends here***************

************ Model for ECL BJT begins here*******************************

.model QECL NPN(Is=6.734f Xti=3 Eg=1.11 Vaf=100 Bf=100 Ne=1.259

+ Ise=6.734f Ikf=66.78m Xtb=1.5 Br=.7371 Nc=2 Isc=0 Ikr=0 Rc=1

+ Cjc=3.638p Mjc=.3085 Vjc=0.70 Fc=.5 Cje=4.493p Mje=.2593 Vje=0.70

+ Tr=239.5n Tf=301.2p Itf=.4 Vtf=4 Xtf=2 Rb=10)

************ Model for ECL BJT begins here*******************************

******** Analysis begins here****************

.OP

.TRAN 0.01mS 2mS

*.AC DEC 20 1 100K

.PROBE

.END

******** Analysis ends here****************

17 © Oxford University Press, 2020 Chapter 11

You might also like

- Certified Secure Computer User Exam Question PrepareDocument5 pagesCertified Secure Computer User Exam Question Preparekouassi joel100% (2)

- Microelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetDocument20 pagesMicroelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetharithNo ratings yet

- Non-Isolated Buck APFC Offline LED Driver Description FeaturesDocument9 pagesNon-Isolated Buck APFC Offline LED Driver Description FeaturesEsmailNo ratings yet

- CIS Community Defense Model v2.0Document50 pagesCIS Community Defense Model v2.0darkblade310No ratings yet

- Chap 05 HMWK SolDocument72 pagesChap 05 HMWK Solapi-3841575No ratings yet

- PG - Manual - MNIT JaipurDocument60 pagesPG - Manual - MNIT JaipurmanaliamitNo ratings yet

- Microelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetDocument7 pagesMicroelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetBadawath NareshNo ratings yet

- RAC-ASM-VOTING DISK Interview Questions & AnswerDocument18 pagesRAC-ASM-VOTING DISK Interview Questions & AnswerNuhu Magwai100% (1)

- Microelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetDocument7 pagesMicroelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetBadawath NareshNo ratings yet

- Microelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetDocument14 pagesMicroelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. Gaudetgain xing GuoNo ratings yet

- VLSI Lab ManualDocument77 pagesVLSI Lab ManualSriramNo ratings yet

- Sedra8e Solvedproblems ch09-2 PDFDocument24 pagesSedra8e Solvedproblems ch09-2 PDFJoh CheNo ratings yet

- Premium EmbeddedDocument61 pagesPremium EmbeddedthehickNo ratings yet

- A Guide To Reduce The Phase Noise Effect in FMCW RadarsDocument4 pagesA Guide To Reduce The Phase Noise Effect in FMCW RadarsAndreea IonescuNo ratings yet

- Chenming Hu Ch8Document34 pagesChenming Hu Ch8Roberto Rojas PizarroNo ratings yet

- Fingerprint Based Electronic Voting MachineDocument20 pagesFingerprint Based Electronic Voting MachineAnjali yadavNo ratings yet

- Hi-Tech Picc-18 STDDocument490 pagesHi-Tech Picc-18 STDSandro BassNo ratings yet

- B. P. Lathi, Zhi Ding - Modern Digital and Analog Communication Systems-Oxford University Press (2009) PDFDocument927 pagesB. P. Lathi, Zhi Ding - Modern Digital and Analog Communication Systems-Oxford University Press (2009) PDFMyDude IsHungryNo ratings yet

- Symmetrical Fault in Power SystemDocument14 pagesSymmetrical Fault in Power Systemstudents answerNo ratings yet

- Frequency Locked Loop DC Motor Speed Control and Monitoring SystemDocument98 pagesFrequency Locked Loop DC Motor Speed Control and Monitoring SystemCHILUKA CHANDRAKANTHNo ratings yet

- Ece 311Document2 pagesEce 311MEHEDI HASANNo ratings yet

- 9781292038957Document5 pages9781292038957123r0% (1)

- 0 - MPMC Lab Manual A.Y. 2020-21 R-18Document53 pages0 - MPMC Lab Manual A.Y. 2020-21 R-18Karthik BoggarapuNo ratings yet

- Pss Lab Manual NewDocument128 pagesPss Lab Manual NewchandrakanthNo ratings yet

- Introduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)Document27 pagesIntroduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)TygerYashanshuNo ratings yet

- Intensity ModulationDocument3 pagesIntensity Modulationanon-323096100% (1)

- Digital Voltmeter Using PIC MicrocontrollerDocument7 pagesDigital Voltmeter Using PIC MicrocontrollerbecemNo ratings yet

- Upgrading Embedded Design Firmware Via USBDocument5 pagesUpgrading Embedded Design Firmware Via USBreemaroy08100% (1)

- 11 - Comparator Based Analog To Digital ConvertersDocument80 pages11 - Comparator Based Analog To Digital ConvertersjoshNo ratings yet

- Valliammai Engineering College: Question BankDocument18 pagesValliammai Engineering College: Question Banksivamani CHINNASWAMYNo ratings yet

- Wearable Oscilloscope Smart WatchDocument2 pagesWearable Oscilloscope Smart Watchالمخترع الصغير2100% (1)

- ns-3: Open Source Simulator For Wireless Network Performance EvaluationDocument86 pagesns-3: Open Source Simulator For Wireless Network Performance EvaluationAli IbraheemNo ratings yet

- CS3391 OOPS UNIT 4 NOTES EduEnggDocument27 pagesCS3391 OOPS UNIT 4 NOTES EduEnggAravind SamyNo ratings yet

- Sample 7668Document11 pagesSample 7668Chintapalli Ramesh KumarNo ratings yet

- Implementation of Wireless LAN Using Cisco Packet TracerDocument5 pagesImplementation of Wireless LAN Using Cisco Packet TracerN KNo ratings yet

- Microprocessors and Microsystems: V.J. Arulkarthick, Abinaya Rathinaswamy, K. SrihariDocument9 pagesMicroprocessors and Microsystems: V.J. Arulkarthick, Abinaya Rathinaswamy, K. SrihariRamesh NairNo ratings yet

- LPC 2129Document44 pagesLPC 2129Pra ReddyNo ratings yet

- CH 6 Fundamental of MIcroelectronics Bahzad Razavi Chapter 6 Solution ManualDocument55 pagesCH 6 Fundamental of MIcroelectronics Bahzad Razavi Chapter 6 Solution ManualSumra MaqboolNo ratings yet

- Ip Lab ManualDocument52 pagesIp Lab Manualanuj1166No ratings yet

- Ee225 Lab 2Document10 pagesEe225 Lab 2Sherlin Chand100% (1)

- EEEB273 N05 - Diff Amp BJT x6 PDFDocument7 pagesEEEB273 N05 - Diff Amp BJT x6 PDFNur AdhiraaNo ratings yet

- Current Mode SignallingDocument2 pagesCurrent Mode SignallingThomas JosephNo ratings yet

- Project Report DPM 07202020150504Document45 pagesProject Report DPM 07202020150504Adharsh R nairNo ratings yet

- Samsung 940FN PDFDocument66 pagesSamsung 940FN PDFsupriyo110No ratings yet

- Tmote Sky DatasheetDocument28 pagesTmote Sky Datasheetshiva_59_59No ratings yet

- UbiSense User ManualDocument5 pagesUbiSense User ManualAshok Kumar100% (1)

- Unmanned Petrol Bunk ProjectDocument90 pagesUnmanned Petrol Bunk ProjectNaveenSvNo ratings yet

- Chapter13 - Memory and Programmable LogicDocument26 pagesChapter13 - Memory and Programmable LogicSrasVelNo ratings yet

- Emb Lab Manual FinalDocument142 pagesEmb Lab Manual FinalSatheesh Kumar100% (1)

- Curso Pic24j60Document173 pagesCurso Pic24j60Diojan Torres100% (1)

- RFID Based Attendance System With Storing Data On Google SpreadsheetDocument39 pagesRFID Based Attendance System With Storing Data On Google SpreadsheetKing YadavNo ratings yet

- Zxevo User Manual Revc EngDocument19 pagesZxevo User Manual Revc EngConrad RussoNo ratings yet

- Installing Network Card & Its Driver: TheoryDocument14 pagesInstalling Network Card & Its Driver: Theorymrcopy xeroxNo ratings yet

- Esa Mcbesa Mcb51 User Manual 51Document28 pagesEsa Mcbesa Mcb51 User Manual 51abcdNo ratings yet

- Lab 10 NSGDocument3 pagesLab 10 NSGMuhammad Awais ShahNo ratings yet

- IPDP BookDocument25 pagesIPDP BookkenilNo ratings yet

- Oferta Leduri Backlight de 3V Si 6V - August - 2019 PDFDocument19 pagesOferta Leduri Backlight de 3V Si 6V - August - 2019 PDFleontindemeterNo ratings yet

- ELTU3014Document2 pagesELTU3014王睿琛No ratings yet

- Tiva C Series LaunchPadDocument13 pagesTiva C Series LaunchPadVivek ShrigiriNo ratings yet

- SedraSmith8e Chapter 09 SpiceProblemGuideDocument15 pagesSedraSmith8e Chapter 09 SpiceProblemGuideEva LoNo ratings yet

- SedraSmith8xe Chapter9 SpiceProblemGuideDocument7 pagesSedraSmith8xe Chapter9 SpiceProblemGuidea28726996No ratings yet

- 0ebc543a-e9f5-4c31-8fb5-69a3ef1a537eDocument6 pages0ebc543a-e9f5-4c31-8fb5-69a3ef1a537eWilliam WadeNo ratings yet

- Fireclass Prec En13 User - 0Document13 pagesFireclass Prec En13 User - 0axwellNo ratings yet

- March 16 - IM Processors DigiTimesDocument5 pagesMarch 16 - IM Processors DigiTimesRyanNo ratings yet

- A Quick and Dirty History: Computer Operating System Command Line InterfaceDocument5 pagesA Quick and Dirty History: Computer Operating System Command Line InterfaceSaleem WaniNo ratings yet

- FusionCompute V100R005C00 Storage Virtualization PDFDocument46 pagesFusionCompute V100R005C00 Storage Virtualization PDFHelder FernandoNo ratings yet

- 2.5 Azure Management InterfacesDocument14 pages2.5 Azure Management Interfacesazhar aliNo ratings yet

- Cisco VTP Notes Part 2 Cheat Sheet Network WalksDocument1 pageCisco VTP Notes Part 2 Cheat Sheet Network WalksJon Carlo R. ChavezNo ratings yet

- Bca III Nov2016 Computer OrganizationDocument2 pagesBca III Nov2016 Computer OrganizationneiceNo ratings yet

- 003 RF Power ModulesDocument6 pages003 RF Power ModulesPaola DiazNo ratings yet

- Adaptive Server Enterprise: Performance and Tuning Series: Monitoring TablesDocument66 pagesAdaptive Server Enterprise: Performance and Tuning Series: Monitoring TableslocutoNo ratings yet

- STG sg2Document162 pagesSTG sg2Radwa EL-MahdyNo ratings yet

- Parallel SysplexDocument4 pagesParallel SysplexJasiekNo ratings yet

- SAP How To Step by Step Guide With Screen ShotDocument16 pagesSAP How To Step by Step Guide With Screen ShotPriyesh ET100% (1)

- Dsa File by AksDocument44 pagesDsa File by AksDeepakNo ratings yet

- V320BJ2 P01 Cmimei PDFDocument27 pagesV320BJ2 P01 Cmimei PDFLuis MezaNo ratings yet

- Smart Energy Monitoring System and Optimization of Energy ConsumptionDocument141 pagesSmart Energy Monitoring System and Optimization of Energy ConsumptionSelim KhanNo ratings yet

- Data Preprocessing - Ipynb - ColaboratoryDocument7 pagesData Preprocessing - Ipynb - ColaboratorySuresh KumarNo ratings yet

- Dvcpro FormatDocument80 pagesDvcpro FormatOlga EscaurizaNo ratings yet

- Mitsubishi FX1N Yj ManualDocument124 pagesMitsubishi FX1N Yj ManualSandi PratamaNo ratings yet

- Arm Cortex r52 Technical Reference Manual 100026 0102 00 en PDFDocument633 pagesArm Cortex r52 Technical Reference Manual 100026 0102 00 en PDFanomin89No ratings yet

- Installing Linux - The Easy WayDocument13 pagesInstalling Linux - The Easy WayVinay HegdeNo ratings yet

- Operation Manual: Digital Ultrasonic Flaw DetectorDocument70 pagesOperation Manual: Digital Ultrasonic Flaw DetectorJonathan MeloNo ratings yet

- Iot Tech NeoDocument177 pagesIot Tech Neokarunesh.shivade100% (1)

- 2015 08 SoMa PS en MaxWeb XPDocument2 pages2015 08 SoMa PS en MaxWeb XPEligius MartinezNo ratings yet

- EXPERIMENT NO 4 Circuits1l Wps PDFDocument9 pagesEXPERIMENT NO 4 Circuits1l Wps PDFMiguel VillarroelNo ratings yet

- Request Stock & Price July 23Document35 pagesRequest Stock & Price July 23Rafael RogelNo ratings yet

- PR Interfaces ID1078628 enDocument40 pagesPR Interfaces ID1078628 enEdwars GuerreroNo ratings yet

- IAUA120N04S5N014 InfineonDocument12 pagesIAUA120N04S5N014 InfineonLatthawitSanNo ratings yet

- Get-VBRServer - Veeam Backup PowerShell ReferenceDocument3 pagesGet-VBRServer - Veeam Backup PowerShell ReferenceAnderson SilvaNo ratings yet