Professional Documents

Culture Documents

Tle 4269

Tle 4269

Uploaded by

Edinaldo RamosOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Tle 4269

Tle 4269

Uploaded by

Edinaldo RamosCopyright:

Available Formats

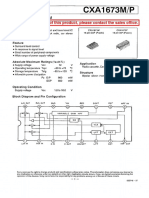

TLE 4269

5-V Low-Drop Fixed Voltage Regulator TLE 4269

Features

● Output voltage tolerance ≤ ± 2 %

● Very low current consumption

● Early warning

● Reset output low doown to VQ = 1 V

● Overtemperature protection

● Reverse polarity proof P-DIP-8-4

● Settable reset threshold

● Very low drop voltage

● Wide temperature range

● Integrated pull up resistor at logic outputs

Type Ordering Code Package

TLE 4269 A Q67000-A9190 P-DIP-8-4

TLE 4269 G Q67006-A9173 P-DSO-8-1 (SMD) P-DSO-8-1

▼ TLE 4269 GM Q67006-A9288 P-DSO-14-4 (SMD)

TLE 4269 GL Q67006-A9192 P-DSO-20-6 (SMD)

▼ New type

Functional Description

This device is a voltage regulator with a fixed 5-V

output, e.g. in a P-DSO-8-1 package. The maximum

P-DSO-20-6

operating voltage is 45 V. The output is able to drive a

150 mA load. It is short circuit protected and the

thermal shutdown switches the output off if the junction

temperature is in excess of 150 °C. A reset signal is

generated for an output voltage of VQ < 4.6 V. The

reset threshold voltage can be decreased by external

connection of a voltage divider. The reset delay time

can be set by an external capacitor. Reset and sense

output have integrated pull up resistors. If the P-DSO-14-4

integrated resistors are not desired TLE 4279 can be

used. It is also possible to supervise the input voltage

by using an integrated comparator to give a low voltage

warning.

Semiconductor Group 1 1998-11-01

TLE 4269

Pin Configuration

(top view)

P-DIP-8-4 P-DSO-8-1

Ι 1 8 Q

Ι 1 8 Q

SΙ 2 7 SO

SΙ 2 7 SO RE 3 6 R

D 4 5 GND

RE 3 6 R AEP01668

D 4 5 GND

AEP01813

Pin Definitions and Functions (TLE 4269 A and TLE 4269 G)

Pin No. Symbol Function

1 I Input; block directly to GND on the IC with a ceramic capacitor.

2 SI Sense Input; if not needed connect to Q.

3 RE Reset Threshold; if not needed connect to ground.

4 D Reset Delay; to select delay time, connect to GND via external

capacitor.

5 GND Ground

6 R Reset Output; the open-collector output is internally linked to Q

via a 20 kΩ pull-up resistor.

7 SO Sense Output; the open-collector output is internally linked to the

output via a 20 kΩ pull-up resistor.

8 Q 5-V Output; connect to GND with a 10 µF capacitor, ESR < 10 Ω.

Semiconductor Group 2 1998-11-01

TLE 4269

Pin Configuration

(top view)

P-DSO-14-4

RE 1 14 SI

D 2 13 Ι

GND 3 12 GND

GND 4 11 GND

GND 5 10 GND

GND 6 9 Q

R 7 8 SO

AEP02248

Pin Definitions and Functions (TLE 4269 GM)

Pin No. Symbol Function

1 RE Reset Threshold; if not needed connect to GND.

2 D Reset Delay; connect to GND via external delay capacitor for

setting delay time.

3, 4, 5, 6 GND Ground

7 R Reset Output; open-collector output, internally connected to Q

via a pull-up resistor of 20 kΩ.

8 SO Sense Output; open-collector output, internally connected to Q

via a 20 kΩ pull-up resistor.

9 Q 5-V Output; connect to GND with a 10 µF capacitor, ESR < 10 Ω.

10, 11, 12 GND Ground

13 I Input; block to GND directly at the IC by a ceramic capacitor.

14 SI Sense Input; if not needed connect to Q.

Semiconductor Group 3 1998-11-01

TLE 4269

Pin Configuration

(top view)

P-DSO-20-6

RE 1 20 SΙ

D 2 19 Ι

N.C. 3 18 N.C.

GND 4 17 GND

GND 5 16 GND

GND 6 15 GND

GND 7 14 GND

N.C. 8 13 N.C.

N.C. 9 12 Q

R 10 11 SO

AEP01802

Pin Definitions and Functions (TLE 4269 GL)

Pin No. Symbol Function

1 RE Reset Threshold; if not needed connect to GND.

2 D Reset Delay; to select delay time connect to GND via external

capacitor.

4-7, 14-17 GND Ground

10 R Reset Output; the open-collector output is internally linked to

Q via 20 kΩ pull-up resistor.

11 SO Sense Output; the open-collector output is internally linked to

Q via 20 kΩ pull-up resistor.

12 Q Output; connect to GND with a 10 µF capacitor, ESR < 10 Ω.

19 I Input; block directly to GND at the IC by a ceramic capacitor.

20 SI Sense Input; if not needed connect to Q.

Semiconductor Group 4 1998-11-01

TLE 4269

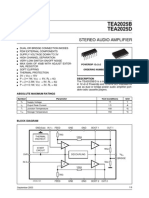

Circuit Description

The control amplifier compares a reference voltage, made highly accurate by resistance

balancing, with a voltage proportional to the output voltage and drives the base of the

series PNP transistor via a buffer. Saturation control as a function of the load current

prevents any over-saturation of the power element.

In the reset generator block a comparator compares a reference voltage independent of

the input voltage with the scaled-down output voltage. If the output voltage reaches 4.6 V

the reset delay capacitor is discharged and the reset output is set to low. This low is

guaranteed down to an output voltage of 1 V. As the output voltage increases again,

from 4.6 V onward the reset delay capacitor is charged with constant current. When the

capacitor voltage reaches the upper switching threshold VdT, the reset returns to high. By

choosing the value of this capacitor, the reset delay time can be selected over a wide

range. With the reset threshold input RE it is possible to lower the reset threshold Vrt. If

pin RE is connected to pin Q via a voltage divider, for example, the reset condition is

reached when this voltage is decreased below the switching threshold Vre of 1.35 V.

Another comparator compares the signal of the pin SI, normally fed by a voltage divider

from the input voltage, with the reference and gives an early warning on the pin SO. It is

also possible to superwise an other voltage e.g. of a second regulator, or to build a

watchdog circuit with few external components.

Application Description

The input capacitor CI is necessary for compensating line influences. Using a resistor of

approx. 1 Ω in series with CI, the oscillating circuit consisting of input inductivity and input

capacitance can be damped. The output capacitor CQ is necessary for the stability of the

regulating circuit. Stability is guaranteed at values ≥ 10 µF and an ESR ≤ 10 Ω within the

operating temperature range. For small tolerances of the reset delay the spread of the

capacitance of the delay capacitor and its temperature coefficient should be noted.

Semiconductor Group 5 1998-11-01

TLE 4269

Ι Q

Error 20 kΩ 20 k Ω

Amplifier

Reference Current and

Saturation

Control

Trimming

D R

RE Reference

SO

SI

AEB01669

Block Diagram

Semiconductor Group 6 1998-11-01

TLE 4269

Absolute Maximum Ratings

Tj = – 40 to 150 °C

Parameter Symbol Limit Values Unit Notes

min. max.

Input

Input voltage VI – 40 45 V –

Input current II – – – internal limited

Sense Input

Input voltage VSI – 0.3 45 V –

Input current ISI 1 1 mA –

Reset Threshold

Voltage VRE – 0.3 7 V –

Current IRE – 10 10 mA –

Reset Delay

Voltage VD – 0.3 7 V –

Current ID – – – internal limited

Ground

Current IGND 50 – mA –

Reset Output

Voltage VR – 0.3 7 V –

Current IR – – – internal limited

Semiconductor Group 7 1998-11-01

TLE 4269

Absolute Maximum Ratings (cont’d)

Tj = – 40 to 150 °C

Parameter Symbol Limit Values Unit Notes

min. max.

Sense Output

Voltage VSO – 0.3 7 V –

Current ISO – – – internal limited

5-V Output

Output voltage VQ – 0.3 7 V –

Output current IQ –5 – mA –

Temperature

Junction temperature Tj – 150 °C –

Storage temperature TStg – 50 150 °C –

Operating Range

Input voltage VI – 45 V –

Junction temperature Tj – 40 150 °C –

Thermal Data

Junction-ambient Rthja – 100 K/W P-DIP-8-4

200 K/W P-DSO-8-1

70 K/W P-DSO-14-4

70 K/W P-DSO-20-6

Rthjc – 60 K/W P-DIP-8-4

60 K/W P-DSO-8-1

30 K/W P-DSO-14-4

30 K/W P-DSO-20-6

Semiconductor Group 8 1998-11-01

TLE 4269

Characteristics

VI = 13.5 V; Tj = – 40 °C < Tj < 125 °C

Parameter Symbol Limit Values Unit Measuring

Condition

min. typ. max.

Output voltage VQ 4.90 5.00 5.10 V 1 mA ≤ IQ ≤ 100 mA

6 V ≤ VI ≤ 16 V

Current limit IQ 150 200 500 mA –

Current consumption; Iq – 150 300 µA IQ ≤ 1 mA, Tj < 85 °C

Iq = II – IQ

Current consumption; Iq – 250 700 µA IQ = 10 mA

Iq = II – IQ

Current consumption; Iq – 2 8 mA IQ = 50 mA

Iq = II – IQ

Drop voltage Vdr – 0.25 0.5 V IQ = 100 mA1)

Load regulation ∆VQ – 10 30 mV IQ = 5 mA to 100 mA

Line regulation ∆VQ – 10 40 mV VI = 6 V to 26 V

IQ = 1 mA

Reset Generator

Switching threshold Vrt 4.50 4.60 4.80 V –

Reset pull up – 10 20 40 kΩ –

Reset low voltage VR – 0.1 0.4 V Rintern

Delay switching Vdt 1.4 1.8 2.2 V –

threshold

Switching threshold Vst 0.3 0.45 0.60 V –

Reset delay low voltage VD – 0.1 V VQ < VRT

Charge current Id 3.0 6.5 9.5 µA VD = 1 V

1) Drop voltage = VI – VQ (measured when the output voltage has dropped 100 mV from the

nominal value obtained at 13.5 V input.)

Semiconductor Group 9 1998-11-01

TLE 4269

Characteristics (cont’d)

VI = 13.5 V; Tj = – 40 °C < Tj < 125 °C

Parameter Symbol Limit Values Unit Measuring

Condition

min. typ. max.

Delay time L → H td 17 28 – ms CD = 100 nF

Delay time H → L tt – 1 – µs CD = 100 nF

Switching voltage Vre 1.26 1.35 1.44 V VQ > 3.5 V

Input Voltage Sense

Sense threshold high Vsi, high 1.24 1.31 1.38 V –

Sense threshold low Vsi, low 1.16 1.20 1.28 V –

Sense output VSO, low – 0.1 0.4 V VSI < 1.20 V;

low voltage Vi > 3 V

Rintern

Sense pull up – 10 20 40 kΩ –

Sense input current ISI –1 0.1 1 µA –

Semiconductor Group 10 1998-11-01

TLE 4269

ΙΙ ΙQ

1 8

CΙ CQ

1000 µF TLE 4269

470 nF 22 µF

Ι SΙ Ι RE

VΙ 2 3 VQ

4 5 6 7

VSΙ ΙD Ι GND VR VSO VRE

CD VD

100 nF

AES01670

Measuring Circuit (P-DIP-8-4/P-DSO-8-1)

VΙ

< t RR

V RT

VQ

dV Ι d

= VDT

dt C D

VST

VD

t RR

td

V RO

Power-on-Reset Thermal Voltage Dip Undervoltage Secondary Overload

Shutdown at Input Spike at Output AED01542

Reset Timing Diagram

Semiconductor Group 11 1998-11-01

TLE 4269

Sense

Input

Voltage

VSI, High

VSI, Low

Sense

Output

High

Low

t

AED02559

Sence Timing Diagram

Semiconductor Group 12 1998-11-01

TLE 4269

Charge Current Id versus Switching Voltage Vdt and Vst versus

Temperature Tj Temperature Tj

AED01803 AED01804

16 3.2

Ιd µA VD V

14 2.8

V Ι = 13.5 V

V Ι = 13.5 V

V C = 1.0 V

12 2.4

10 2.0 Vdt

8 1.6

6 1.2

4 0.8

Vst

2 0.4

0 0

-40 0 40 80 120 C 160 -40 0 40 80 120 C 160

Tj Tj

Drop Voltage Vdr versus Reset Switching Threshold Vre

Output Current IQ versus Temperature Tj

AED01805 AED01806

500 1.7

V dr Vre V

mV

1.6

400

1.5

1.4

300

Tj = 125 C 1.3

200

1.2

Tj = 25 C

1.1

100

1.0

0 0.9

0 30 60 90 120 mA 180 -40 0 40 80 120 C 160

ΙQ Tj

Semiconductor Group 13 1998-11-01

TLE 4269

Current Consumption IQ versus Output Voltage VQ versus

Input Voltage VI Input Voltage VI

AED01807 AED01808

30 12

Ι q mA VQ

V

25 10

20 8

RL = 33 Ω

15 6

RL = 50 Ω

10 4

RL = 50 Ω

5 RL = 100 Ω 2

RL = 200 Ω

0 0

0 10 20 30 40 V 50 0 2 4 6 8 V 10

VΙ VΙ

Sense Threshold Vsi Output Voltage VQ versus

versus Temperature Tj Temperature Tj

AED01809 AED01671

1.6 5.2

V si VQ V

V

V Ι = 13.5 V

1.5 5.1

V Ι = 13.5 V

1.4 5.0

Sense Output High

1.3 4.9

Sense Output Low

1.2 4.8

1.1 4.7

1.0 4.6

-40 0 40 80 120 C 160 -40 0 40 80 120 C 160

Tj Tj

Semiconductor Group 14 1998-11-01

TLE 4269

Output Current IQ versus Current Consumption Iq versus

Input Voltage VI Output Current IQ

AED01810 AED01811

350 12

Ι Q mA Ι q mA

300

10

V Ι = 13.5 V

250 Tj = 25 C

Tj = 25 C 8

200

6

Tj = 125 C

150

4

100

50 2

0 0

0 10 20 30 40 V 50 0 20 40 60 80 mA 120

VΙ ΙQ

Current Consumption Iq versus

Output Current IQ

AED01812

1.6

Ιq mA

1.4

V Ι = 13.5 V

Tj = 25 C

1.2

1.0

0.8

0.6

0.4

0.2

0

0 10 20 30 40 mA 50

ΙQ

Semiconductor Group 15 1998-11-01

TLE 4269

Package Outlines

P-DIP-8-4

(Plastic Dual In-line)

GPD05583

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information” Dimensions in mm

Semiconductor Group 16 1998-11-01

TLE 4269

P-DSO-14-4 (SMD)

(Plastic Dual Small Outline)

0.35 x 45˚

1.75 max

4 -0.2 1)

1.45 -0.2

0.19 +0.06

0.2 -0.1

8˚ max.

1.27

0.1 0.4 +0.8

0.35 +0.15 2)

0.2 14x

6 ±0.2

14 8

1 7

8.75 -0.21)

Index Marking

1) Does not include plastic or metal protrusion of 0.15 max. per side

2) Does not include dambar protrusion of 0.05 max. per side GPS05093

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information” Dimensions in mm

SMD = Surface Mounted Device

Semiconductor Group 17 1998-11-01

TLE 4269

P-DSO-8-1 (SMD)

(Plastic Dual Small Outline)

GPS05121

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”

SMD = Surface Mounted Device Dimensions in mm

Semiconductor Group 18 1998-11-01

TLE 4269

P-DSO-20-6 (SMD)

(Plastic Dual Small Outline)

0.35 x 45˚

2.65 max

2.45 -0.2

7.6 -0.2 1)

0.2 -0.1

9

0.23 +0.0

x

8˚ ma

1.27 0.4 +0.8

+0.15 2)

0.35

0.2 24x 0.1 10.3 ±0.3

20 11

GPS05094

1 12.8 1) 10

-0.2

Index Marking

1) Does not include plastic or metal protrusions of 0.15 max per side

2) Does not include dambar protrusion of 0.05 max per side

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information” Dimensions in mm

SMD = Surface Mounted Device

Semiconductor Group 19 1998-11-01

You might also like

- Antenna 6503 PDFDocument2 pagesAntenna 6503 PDFOliver Pantoja Cassola100% (1)

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- LED Strip Light Power Supply CalculatorDocument3 pagesLED Strip Light Power Supply CalculatorNadeem Muhammad NadzNo ratings yet

- TLE4279 SiemensSemiconductorGroupDocument19 pagesTLE4279 SiemensSemiconductorGroupLuis MezaNo ratings yet

- TLE4470Document24 pagesTLE4470ricahard61No ratings yet

- 5-V Low-Drop Voltage Regulator TLE 4263: FeaturesDocument17 pages5-V Low-Drop Voltage Regulator TLE 4263: FeaturesWelleyNo ratings yet

- TLE4205Document13 pagesTLE4205tigras6010No ratings yet

- Infineon TLE6209R DS v03 02 enDocument30 pagesInfineon TLE6209R DS v03 02 enRoger SegoNo ratings yet

- Data Sheet TLE4262G Regulador 5v 20 PinesDocument16 pagesData Sheet TLE4262G Regulador 5v 20 Pinesaagreco73No ratings yet

- Regulador de Tension TLE4267-DS-v02 - 51-EnDocument23 pagesRegulador de Tension TLE4267-DS-v02 - 51-EnJorge Martinez PerezNo ratings yet

- 7 A H-Bridge For DC-Motor Applications TLE 6209 R: 1 1.1 FeaturesDocument29 pages7 A H-Bridge For DC-Motor Applications TLE 6209 R: 1 1.1 Featureswtn2013No ratings yet

- Control de Garganta TACDocument15 pagesControl de Garganta TACmario rosasNo ratings yet

- 7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetDocument4 pages7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetallisonNo ratings yet

- TLE7209 R InfineonDocument16 pagesTLE7209 R Infineonmobil benerNo ratings yet

- 7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetDocument32 pages7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetMecaSoftwareNo ratings yet

- FT 28Document3 pagesFT 28joako garciaNo ratings yet

- Datasheet 4269Document19 pagesDatasheet 4269Alexandre Da Silva PintoNo ratings yet

- Repeater Interface: Technical SpecificationDocument2 pagesRepeater Interface: Technical SpecificationThanh Kieu TienNo ratings yet

- A2C33648Document27 pagesA2C33648mohhizbar100% (1)

- Data SheetDocument19 pagesData SheetDiego CaceresNo ratings yet

- Dual Low Drop Voltage Regulator TLE 7469: FeaturesDocument22 pagesDual Low Drop Voltage Regulator TLE 7469: FeaturesPabloLabruneNo ratings yet

- 1 Tle5206 2 - 1Document23 pages1 Tle5206 2 - 1Fran CastanoNo ratings yet

- TLE6208-3G InfineonDocument21 pagesTLE6208-3G InfineonMarcin StankiewiczNo ratings yet

- Tle5205 2Document23 pagesTle5205 2Richard MachadoNo ratings yet

- TLE42766 Siemens Elenota - PLDocument16 pagesTLE42766 Siemens Elenota - PLAnuar Angrac Lopez CruzNo ratings yet

- PCB DiagramDocument6 pagesPCB Diagramfreitastsp9166No ratings yet

- RT9018ADocument12 pagesRT9018Abusamawan wayanNo ratings yet

- Ne5521 Sa5521 2Document11 pagesNe5521 Sa5521 2José AdelinoNo ratings yet

- 2-Phase Stepper-Motor Driver TLE 4728 G: Bipolar-IC FeaturesDocument26 pages2-Phase Stepper-Motor Driver TLE 4728 G: Bipolar-IC FeaturesMohammad RanjbarNo ratings yet

- NE/SA/SE5521 LVDT Signal Conditioner: Description Pin ConfigurationsDocument5 pagesNE/SA/SE5521 LVDT Signal Conditioner: Description Pin ConfigurationsAriel SanusiNo ratings yet

- Oscilador de PFC Fuente Toshiba 2A20112SPDocument8 pagesOscilador de PFC Fuente Toshiba 2A20112SPAntonio ChavezNo ratings yet

- Datasheet SN3218Document12 pagesDatasheet SN3218Daniel SilvaNo ratings yet

- MHC-GT5D (SA-WGT5D) Diagrama-11912Document33 pagesMHC-GT5D (SA-WGT5D) Diagrama-11912palomoreparacionesNo ratings yet

- L6203 Chip InfoDocument20 pagesL6203 Chip InfoShane PentzNo ratings yet

- SY8208Document1 pageSY8208zoompcpainkillerNo ratings yet

- TPS7101Q PDFDocument40 pagesTPS7101Q PDFlittledropNo ratings yet

- An5092 Ais328dq Highperformance Ultralowpower 3axis Digital Output Accelerometer For Automotive Nonsafety Applications StmicroelectronicsDocument30 pagesAn5092 Ais328dq Highperformance Ultralowpower 3axis Digital Output Accelerometer For Automotive Nonsafety Applications Stmicroelectronicstomislav_darlicNo ratings yet

- Infineon TLE4299V33 DS v01 - 01 enDocument25 pagesInfineon TLE4299V33 DS v01 - 01 enStelian DobreNo ratings yet

- SONY,,: For The Availability of This Product, Please Contact The Sales OfficeDocument8 pagesSONY,,: For The Availability of This Product, Please Contact The Sales OfficeERNANIPARNOWNo ratings yet

- Richtek Tech R7731AGE C250411Document14 pagesRichtek Tech R7731AGE C250411Игорь ПочепаNo ratings yet

- Consonance: 4A, Standalone Li-Ion Battery Charger IC With Photovoltaic Cell MPPT Function CN3791Document11 pagesConsonance: 4A, Standalone Li-Ion Battery Charger IC With Photovoltaic Cell MPPT Function CN3791gpreviatoNo ratings yet

- DatasheetDocument16 pagesDatasheetAndres GuerreroNo ratings yet

- Sensor Less Speed Control of BLDC Motor - Rev 2Document12 pagesSensor Less Speed Control of BLDC Motor - Rev 2sureshNo ratings yet

- 5-V Low-Drop Fixed Voltage Regulator TLE 4271: FeaturesDocument20 pages5-V Low-Drop Fixed Voltage Regulator TLE 4271: FeaturesPablo CervantesNo ratings yet

- 2576 LDocument9 pages2576 LclanonNo ratings yet

- NCR320PAS / NCR321PAS: 1. Product ProfileDocument18 pagesNCR320PAS / NCR321PAS: 1. Product ProfileЕвгений ИвановNo ratings yet

- AL8862QDocument17 pagesAL8862QIvo MatosNo ratings yet

- Tea 2025Document9 pagesTea 2025Duong HusterNo ratings yet

- Data Sheet Se5004L: 5 GHZ, 26Dbm Power Amplifier With Power Detector Applications Product DescriptionDocument9 pagesData Sheet Se5004L: 5 GHZ, 26Dbm Power Amplifier With Power Detector Applications Product DescriptionashfaqNo ratings yet

- Description Features: Current Mode PWM ControllerDocument9 pagesDescription Features: Current Mode PWM ControllerAlex GerasimenkoNo ratings yet

- Semiconductor Technical Data: 16-Lead Soic Package CASE 751B-05Document7 pagesSemiconductor Technical Data: 16-Lead Soic Package CASE 751B-05Hiba YasirNo ratings yet

- SP490E/SP491E Enhanced Full Duplex RS-485 Transceivers: DescriptionDocument12 pagesSP490E/SP491E Enhanced Full Duplex RS-485 Transceivers: DescriptionCarlos AcostaNo ratings yet

- System Basis Chip T L E 6 2 6 6 G: Integrated LS CAN, LDO and LS - HS SwitchesDocument50 pagesSystem Basis Chip T L E 6 2 6 6 G: Integrated LS CAN, LDO and LS - HS Switchescork_ieNo ratings yet

- Dse CN3791Document12 pagesDse CN3791Jaime Andres Aranguren CardonaNo ratings yet

- Infineon TLE4275V50 DS v01 - 07 en PDFDocument17 pagesInfineon TLE4275V50 DS v01 - 07 en PDFjoseNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsFrom EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsNo ratings yet

- 1.1.2.L Investigating Basic CircuitsDocument21 pages1.1.2.L Investigating Basic CircuitsBilly bobsNo ratings yet

- BlokCam & BlokAlert - BrochureDocument20 pagesBlokCam & BlokAlert - BrochureCKNo ratings yet

- Yoga Book: Safety, Warranty & Quick Start GuideDocument14 pagesYoga Book: Safety, Warranty & Quick Start GuideBorislavaSavovaNo ratings yet

- Philips Delta Power Supplies TrainingDocument33 pagesPhilips Delta Power Supplies Trainingloc_jvc2825100% (9)

- BUG-O Welding and CuttingDocument264 pagesBUG-O Welding and Cuttingtanase_v100% (1)

- Akatsuki 2015Document6 pagesAkatsuki 2015Dhruv MalhotraNo ratings yet

- B.E III. Sem Curriculum & Syllabus 2020 Batch Pages 51 67Document17 pagesB.E III. Sem Curriculum & Syllabus 2020 Batch Pages 51 67Sharath Chandan SNo ratings yet

- EE8352 Principles of Electrical and Electronics Engineering: by Mrs.T.Santhiya Dept of EEEDocument12 pagesEE8352 Principles of Electrical and Electronics Engineering: by Mrs.T.Santhiya Dept of EEESanthiya T100% (1)

- AN03 Getting Started With QuartusDocument10 pagesAN03 Getting Started With QuartusÎQbãl HãikãmNo ratings yet

- How To Design Solar PV SystemDocument3 pagesHow To Design Solar PV SystemMeena DhillonNo ratings yet

- Products Catalogue: G01040L0M00041 - LINK ASS'Y SALTDocument1 pageProducts Catalogue: G01040L0M00041 - LINK ASS'Y SALTGilberto D'LeãoNo ratings yet

- DUW PresentationDocument64 pagesDUW PresentationOnjanohasoavina MANANJARASOANo ratings yet

- DC Machines1.1 1Document19 pagesDC Machines1.1 1Janaka Chathuranga AbeywardenaNo ratings yet

- Timer 0: Laboratory Activity 3Document6 pagesTimer 0: Laboratory Activity 3Jerome ColicoNo ratings yet

- 16-02 Low Speed Warning DeviceDocument3 pages16-02 Low Speed Warning Devicetweety874No ratings yet

- ProjectDocument28 pagesProjectSatyanarayana GurramNo ratings yet

- Cassettes Foour WayDocument12 pagesCassettes Foour Wayboudiba lotfiNo ratings yet

- 74HC1G14 74HCT1G14: 1. General DescriptionDocument16 pages74HC1G14 74HCT1G14: 1. General DescriptionИльнур ТагировNo ratings yet

- Extendable Bidirectional DC-DC Converter With Improved Voltage Transfer Ratio and Reduced Switch CountDocument11 pagesExtendable Bidirectional DC-DC Converter With Improved Voltage Transfer Ratio and Reduced Switch CountMarwan SamirNo ratings yet

- Basic of Timing Analysis in Physical Design - VLSI ConceptsDocument5 pagesBasic of Timing Analysis in Physical Design - VLSI ConceptsIlaiyaveni IyanduraiNo ratings yet

- It Syllabus For Kuk Btech 558460e806008Document72 pagesIt Syllabus For Kuk Btech 558460e806008joyNo ratings yet

- GT Series ManualDocument66 pagesGT Series ManualskyddNo ratings yet

- Datakom-D300 MK2 DataDocument4 pagesDatakom-D300 MK2 DataMinn Thet NaingNo ratings yet

- Questions On Electric Motors With AnswersDocument2 pagesQuestions On Electric Motors With Answersanil1216kumar100% (2)

- Plant: Siemens Building TechnologiesDocument26 pagesPlant: Siemens Building TechnologiesbluesierNo ratings yet

- GoodKnight® 425ST - Service ManualDocument56 pagesGoodKnight® 425ST - Service ManualmpalenaNo ratings yet

- DFT Interview QuestionsDocument9 pagesDFT Interview QuestionsNaga Nithesh100% (1)

- UCI224EDocument12 pagesUCI224ESaeid MirNo ratings yet