Professional Documents

Culture Documents

NI PXIe-6544 - Specifications

NI PXIe-6544 - Specifications

Uploaded by

차지형Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

NI PXIe-6544 - Specifications

NI PXIe-6544 - Specifications

Uploaded by

차지형Copyright:

Available Formats

SPECIFICATIONS

NI PXIe-6544/6545/6547/6548

100/200 MHz Digital Waveform Generator/Analyzer

̭͈Ρ΅νιϋΠ͉ͅȂུࢊβȜΐ̳̞̀ͦ͘͘͜܄ȃ

This document provides the specifications for the NI PXIe-6544 (NI 6544), NI PXIe-6545

(NI 6545), NI PXIe-6547 (NI 6547), and NI PXIe-6548 (NI 6548).

Maximum and minimum specifications are warranted not to exceed these values within certain

operating conditions and include the effects of temperature and uncertainty unless otherwise noted.

Typical specifications are unwarranted values that are representative of a majority (3σ) of units

within certain operating conditions and include the effects of temperature and uncertainty unless

otherwise noted.

Characteristic specifications are unwarranted values that are representative of an average unit

operating at room temperature.

Nominal specifications are unwarranted values that are relevant to the use of the product and

convey the expected performance of the product.

All specifications are Typical unless otherwise noted. These specifications are valid within the

operating temperature range. Specifications are subject to change without notice. For the most

recent NI 6544/6545/6547/6548 specifications, visit ni.com/manuals. To access the

NI 6544/6545/6547/6548 documentation, including the NI Digital Waveform Generator/

Analyzer Getting Started Guide, which contains functional descriptions of the NI 6544/6545/

6547/6548 signals and the connector pinouts, navigate to Start»Programs»National

Instruments»NI-HSDIO»Documentation.

Hot Surface If the NI 6544/6545/6547/6548 has been in use, it may exceed safe

handling temperatures and cause burns. Allow time to cool before removing the

NI 6544/6545/6547/6548 from the chassis.

Note All values were obtained using a 1 m cable (SHC68-C68-D4 recommended).

Performance specifications are not guaranteed when using longer cables.

Contents

Channel Specifications ............................................................................................................. 3

Generation Channels (Data, DDC CLK OUT, and PFI <0..3>)....................................... 4

Acquisition Channels (Data, STROBE, and PFI <0..3>) ................................................. 6

Timing Specifications ............................................................................................................... 7

Sample Clock .................................................................................................................... 7

Generation Timing (Data, DDC CLK OUT, and PFI <0..3> Channels) .......................... 9

Generation Provided Setup and Hold Times .................................................................... 13

Acquisition Timing (Data, STROBE, and PFI <0..3> Channels)..................................... 16

CLK IN (SMA Jack Connector) ....................................................................................... 19

STROBE (DDC Connector) ............................................................................................. 21

CLK OUT (SMA Jack Connector) ................................................................................... 22

DDC CLK OUT (DDC Connector) .................................................................................. 22

Reference Clock (PLL) ..................................................................................................... 23

Waveform Specifications.......................................................................................................... 24

Memory and Scripting ...................................................................................................... 24

Triggers (Inputs to the NI 6544/6545/6547/6548) ...........................................................27

Events (Generated from the NI 6544/6545/6547/6548) ................................................... 28

Miscellaneous ................................................................................................................... 29

Power ................................................................................................................................29

Physical ............................................................................................................................. 29

I/O Panel Connectors ........................................................................................................ 30

Software ............................................................................................................................ 30

Environment...................................................................................................................... 31

Safety, Electromagnetic Compatibility, and CE Compliance........................................... 32

2 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Channel Specifications

Specification Value Comments

Number of data NI 6544/6545 NI 6547/6548 Data rate

channels multiplier is

32 single data rate (SDR) 32 single data rate (SDR) software

channels channels selectable to be

or SDR or DDR.

16 double data rate (DDR) Using SDR,

channels per direction data is clocked

using the rising

or

or falling edge

24 channels when configured of the Sample

for extended data mode. clock.

This mode is used for

Using DDR,

hardware comparison and

data is clocked

cycle-to-cycle tristate

using both

operations.

edges of the

Note: Generation and Sample clock.

acquisition sessions may be

independently configured for

DDR operation on either the

lower data channels (<0..15>)

or the upper data channels

(<16..31>).

Direction Per channel, per operation Per channel, per cycle Per cycle

control of data direction

channels control is

supported when

in extended

data mode.

Time to tristate 6.2 ns Nominal into a

(tPZ) 2 kΩ and 15 pF

load.

Number of 4 Refer to the

programmable Waveform

function Specifications

interface (PFI) section for

channels more details.

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 3

Specification Value Comments

Direction Per channel —

control of PFI

channels

Number of 2 input Refer to

clock terminals 2 output the Timing

Specifications

section for

more details.

Generation Channels (Data, DDC CLK OUT,

and PFI <0..3>)

Specification Value Comments

Generation Single-ended —

signal type

Number of 1 Voltage high level (VOH) NI 6547/

programmable 6548 only;

Generation Voltage Low Level (VOL) is always set to 0 V.

generation for all data,

voltage levels Note: Generation and acquisition sessions share a common PFI, and

programmable voltage resource. For simultaneous operations, clock

acquisition thresholds must be set to half of the Generation Voltage channels.

High Level setting.

Generation 1.2 V to 3.3 V

voltage range

Generation 100 mV

voltage

resolution

DC generation Typical Maximum Into 1 MΩ;

voltage does not

accuracy ±35 mV ±200 mV include

system

crosstalk.

4 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Specification Value Comments

Generation 1.2V, 1.5V, 1.8V, 2.5V, 3.3V Logic Families All devices;

logic families for all data,

Generation and acquisition sessions share a common voltage

resource. Simultaneous operations must be set to the same logic PFI, and

clock

family.

channels.

Generation Voltage Low Levels Voltage High Levels Nominal

voltage levels Logic

Family Nominal Max Min Nominal values have

±35 mV

1.2V 0.0 V 0.2 V 1V 1.2 V typical

(VOH = 1.2 V) accuracy

with a

1.5V 0.0 V 0.2 V 1.3 V 1.5 V 1 MΩ load.

(VOH = 1.5 V)

Does not

1.8V 0.0 V 0.2 V 1.6 V 1.8 V include

(VOH = 1.8 V) system

crosstalk.

2.5V 0.0 V 0.2 V 2.3 V 2.5 V

(VOH = 2.5 V)

3.3V 0.0 V 0.2 V 3.1 V 3.3 V

(VOH = 3.3 V)

Output 50 Ω Nominal.

impedance

Maximum Maximum Allowed DC Nominal.

allowed DC Logic Family Drive Strength

drive strength

per channel 1.2V ±12 mA

1.5V ±15 mA

1.8V ±18 mA

2.5V ±25 mA

3.3V ±33 mA

Data channel Per channel Software-

driver enable/ selectable.

disable control

Channel Drivers disabled, 50 kΩ nominal input impedance —

power-on state

Output The device can indefinitely sustain a short to any voltage between —

protection 0 V and 5 V.

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 5

Acquisition Channels (Data, STROBE, and PFI <0..3>)

Specification Value Comments

Acquisition Single-ended —

signal type

Number of 1 voltage threshold (VIH = VIL) NI 6547/654

programmable 8 only; for

Note: Generation and acquisition sessions share a common

acquisition programmable voltage resource. For simultaneous operations, all data, PFI,

thresholds and clock

Generation Voltage High Level must be set to twice the Acquisition

channels.

Voltage Threshold.

Acquisition 0.6 V to 1.65 V

Voltage

Threshold

range

Acquisition 50 mV

Voltage

Threshold

resolution

DC Acquisition Typical Maximum Does not

Voltage include

Threshold ±150 mV ±30% system

accuracy crosstalk.

Acquisition 1.2V, 1.5V, 1.8V, 2.5V, 3.3V Logic Families All devices;

logic families Note: Generation and acquisition sessions share a common voltage

for all data,

PFI, and

resource. Simultaneous operations must be set to the same logic

clock

family.

channels.

Acquisition Voltage Voltage Does not

Voltage Thresholds Low Thresholds High include

Thresholds system

Logic Family Min Typical Typical Max

crosstalk.

1.2V 420 mV 450 mV 750 mV 780 mV

(VIH, VIL= 0.60 V)

1.5V 525 mV 600 mV 900 mV 975 mV

(VIH, VIL= 0.75 V)

1.8V 630 mV 750 mV 1.05 V 1.17 V

(VIH, VIL= 0.90 V)

2.5V 875 mV 1.10 V 1.40 V 1.625 V

(VIH, VIL= 1.25 V)

3.3V 1.155 V 1.50 V 1.80 V 2.145 V

(VIH, VIL= 1.65 V)

6 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Specification Value Comments

Input High-impedance (50 kΩ) Nominal.

impedance

Input protection -1 V to 5 V Internal

diode clamps

may begin

conduction

outside the

-0.5 V to

3.5 V range.

Timing Specifications

Sample Clock

Specification Value Comments

Sample clock 1. On Board Clock (internal 800 MHz VCO with 32-bit DDS) —

sources 2. CLK IN (SMA jack connector)

3. STROBE (Digital Data & Control (DDC) connector;

acquisition only)

On Board NI 6544, NI 6547: 100 Hz to 100 MHz —

Clock

NI 6545, NI 6548: 100 Hz to 200 MHz

frequency

range

On Board 0.2 Hz maximum NI-HSDIO may

Clock Note: Varies with Sample clock frequency.

be queried for

frequency the

resolution programmed

frequency

value.

On Board ±150 ppm + 5 ppm per year Accuracy may

Clock be increased by

frequency using a higher

accuracy performance

external

Reference

clock.

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 7

Specification Value Comments

CLK IN NI 6544, NI 6547: 20 kHz to 100 MHz Refer to the

frequency CLK IN

NI 6545, NI 6548: 20 kHz to 200 MHz

range (SMA Jack

Connector)

section for

restrictions

based on

waveform type.

STROBE NI 6544, NI 6547: 100 Hz to 100 MHz Refer to the

frequency STROBE (DDC

NI 6545, NI 6548: 100 Hz to 200 MHz

range Connector)

section.

Sample clock 0.0 to 1.0 Sample clock period (acquisition sessions) You can apply a

relative delay delay or phase

0.0 ns to 5.0 ns (generation sessions)

adjustment adjustment to

range the On Board

Clock to align

Sample clock 0.5 ps multiple

relative delay devices.

adjustment

resolution

Exported 1. DDC CLK OUT (DDC connector) Internal Sample

Sample clock 2. CLK OUT (SMA jack connector) clocks with

destinations sources other

than STROBE

can be

exported.

Exported 0.0 to 1.0 Sample clock periods Resolution is

Sample clock nonlinearly

delay range dependent

on clock

Exported 117 ps to 143 ps, nominal frequency and

Sample clock may be queried

delay for by using

resolution (δC) NI-HSDIO.

Exported On Board Clock External Clock

Sample Clock

delay All supported frequencies Frequencies ≥ 20 MHz

frequency

Exported Period Jitter Cycle-to-Cycle Jitter Characteristic;

Sample clock using On Board

jitter 24 psrms 43 psrms Clock.

8 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Figure 1. Characteristic Period Jitter (RMS) vs. Frequency

25p

22.5p

20p

RMS Period Jitter (s)

17.5p

15p

12.5p

10p

7.5p

0 °C

5p

25 °C

2.5p 55 °C

0

75 M 100 M 125 M 150 M 175 M 200 M

Frequency (Hz)

Specification Value Comments

Exported Sample DDC Clock Out NI 6545/6548 at

clock duty cycle maximum clock

Logic Family Min Max rate (200 MHz).

1.2V 37% 50% Not including the

effects of system

1.5V 41% 53% crosstalk.

1.8V 42% 55%

2.5V 45% 57%

3.3V 48% 58%

Generation Timing (Data, DDC CLK OUT, and

PFI <0..3> Channels)

Specification Value Comments

Data ±300 ps Maximum

channel-to- skew across all

channel skew data channels,

PFI channels,

and voltage

levels when

using the same

data position or

data delay

bank.

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 9

Specification Value Comments

Maximum SDR: 100 Mbps Includes

data rate per NI 6544 maximum data

Supported for all logic families.

channel channel-to-

SDR: 200 Mbps channel skew

NI 6545 and typical

Supported for all logic families.

crosstalk.

SDR: 100 Mbps NI 6547/6548

DDR: 200 Mbps devices

NI 6547 generate two

Supported for all logic families and selectable

samples per

voltage levels.

clock cycle in

Logic Family SDR DDR DDR mode.

3.3V 200 Mbps 400 Mbps

2.5V 400 Mbps

1.8V 375 Mbps

1.5V 350 Mbps

NI 6548 1.2V 300 Mbps

Voltage Levels SDR DDR

2.5 V to 3.3 V 200 Mbps 400 Mbps

1.8 V to 2.4 V 375 Mbps

1.5 V to 1.7 V 350 Mbps

1.2 V to 1.4 V 300 Mbps

10 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Figure 2 shows an eye diagram of a 400 Mbps pseudorandom bit sequence (PRBS) waveform

in DDR mode at 3.3 V. This waveform was captured on DIO 0 at room temperature into high

impedance.

Figure 2. Characteristic Eye Diagram (high impedance)

3.5

2.5

Delay Accuracy (s)

1.5

0.5

–0.5

–2.5ns –2ns –1.5ns –1ns –0.5ns 0ns –0.5ns –1ns –1.5ns –2ns –2.5ns

Figure 3 shows an eye diagram of a 400 Mbps PRBS waveform in DDR mode at 3.3 V. This

waveform was captured on DIO 0 at room temperature into 50 Ω termination.

Figure 3. Characteristic Eye Diagram (50 Ω Termination)

1.8

1.6

1.4

1.2

Delay Accuracy (s)

0.8

0.6

0.4

0.2

–0.2

–2.5ns –2ns –1.5ns –1ns –0.5ns 0ns –0.5ns –1ns –1.5ns –2ns –2.5ns

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 11

Specification Value Comments

Data position Sample clock rising edge, Sample clock falling edge, or —

modes Delay from Sample clock rising edge

Data delay NI 6544/6545: 1 bank for all channels and PFI lines Multibank data

banks delay is

NI 6547/6548: 3 banks

supported

Bank 0: DIO<0..3>, DIO<16..19>, DIO<28..31>, PFI <0..3> only in

Bank 1: DIO<4..7>, DIO<20..23> NI-HSDIO 1.7

and later.

Bank 2: DIO<8..15>, DIO<24..27>

Generation data 0.0 to 1.0 Sample clock periods Resolution is

delay range nonlinearly

(δG) dependent

on clock

Generation data 117 ps to 143 ps, nominal frequency and

delay may be queried

resolution (δG) for using

NI-HSDIO.

Generation data On Board Clock External Clock

delay

frequency All supported frequencies Frequencies ≥ 20 MHz

Figure 4. Characteristic Data Delay Accuracy

500p

400p

300p

Delay Accuracy (s)

200p

100p

0

–100p

–200p

Frequency = 200.00 MHz

–300p

Frequency = 101.00 MHz

–400p Frequency = 174.00 MHz

–500p

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

Delay Setting

12 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Specification Value Comments

Exported 0.0 ns or 1.65 ns (default) Nominal;

Sample clock Software-

offset (tCO) selectable for

DDC_CLK_

OUT.

Time delay 8.1 ns Characteristic;

from Sample Exported

clock (internal) Sample clock

to DDC offset = 0 ns

connector

(tSCDDC)

Generation Provided Setup and Hold Times

Exported Sample Clock Minimum Provided Setup Minimum Provided Hold

Offset (tPCO) Time (tPSU) Time (tPH)

1.65 ns tp - 2.15 ns 1.15 ns

0.0 ns tp - 500 ps -500 ps

Compare the setup and hold times from the datasheet of your device under test (DUT) to the values in

the table above. The provided setup and hold times must be greater than the setup and hold times required

for the DUT. If you require more setup time, configure your exported Sample clock mode to Inverted

and/or delay your clock or data relative to the Sample clock.

Refer to Figure 5 for a diagram illustrating the relationship between the exported Sample clock mode

and the provided setup and hold times.

Notes: This table assumes the data position is set to Sample clock rising edge and the noninverted

Sample clock is exported to the DDC connector.

This table includes worst-case effects of channel-to-channel skew and intersymbol interference.

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 13

Figure 5. Generation Provided Setup and Hold Times Timing Diagram

tP

Exported

Sample Clock

tPCO

DATA CHANNELS tPH

tPSU

Sample Clock Rising Edge

Data Position

(Noninverted Clock,

tCO = 1.65 ns) tSKEW

tPCO

Sample Clock Rising Edge

Data Position

(Inverted Clock,

tCO = 0 ns) tPH tPSU

tP = 1 = Sample Clock Period

f

tPH = Minimum Provided Hold Time

tPSU = Minimum Provided Set-Up Time

tPCO =Time from Rising Clock Edge to Data Transition (Provided Clock to Out Time)

tCO = Exported Sample Clock Offset

tSKEW = Maximum Channel-to-Channel Skew and Clock Uncertainty

Note Provided setup and hold times account for maximum channel-to-channel

skew and jitter.

14 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Figure 6. Generation Timing Diagram

Sample Clock

tSCDDC tP

δC

tCO

DATA CHANNELS

Data Position Rising Edge Sample n Sample n+1

Data Position Falling Edge Sample n Sample n+1

Data Position Delayed δG Sample n Sample n+1

tSCDDC : Time Delay from Sample Clock (Internal) to DDC Connector

0 ≤ δC ≤ 1 : Exported Sample Clock Delay (Fraction of tP)

0 ≤ δG ≤ 1 : Pattern Generation Data Delay (Fraction of tP)

tP = 1 = Period of Sample Clock

ƒ

tCO = Exported Sample Clock Offset; 1.65 ns, Software-Selectable

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 15

Acquisition Timing (Data, STROBE, and PFI <0..3>

Channels)

Specification Value Comments

Channel-to- ±350 ps Maximum

channel skew skew across all

data channels,

PFI channels,

and voltage

levels when

using the same

data position or

data delay

bank.

Maximum SDR: 100 Mbps Includes

data rate per NI 6544 maximum data

Supported for all logic families.

channel channel-to-

SDR: 200 Mbps channel skew

NI 6545 and typical

Supported for all logic families.

crosstalk.

SDR: 100 Mbps NI 6547/6548

DDR: 200 Mbps devices

NI 6547 acquires

Supported for all logic families and selectable

two samples

voltage levels.

per clock cycle

Logic Family SDR DDR in DDR mode.

3.3V 200 Mbps 300 Mbps

2.5V 300 Mbps

1.8V 250 Mbps

1.5V 225 Mbps

1.2V 200 Mbps

NI 6548

Voltage

Threshold SDR DDR

1.25 V to 1.65 V 200 Mbps 300 Mbps

0.90 V to 1.20 V 250 Mbps

0.75 V to 0.85 V 225 Mbps

0.60 V to 0.70 V 200 Mbps

16 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Specification Value Comments

Setup and Hold Time (ths) Setup Times (tsus) Characteristic

Hold Times to Voltage includes

STROBE Threshold <20 MHz ≥20 MHz <20 MHz ≥20 MHz maximum

1.25 V to 2.4 ns 900 ps 2.8 ns 1.15 ns data

1.65 V channel-to-

channel skew

0.90 V to 1.00 ns 1.20 ns and

1.20 V uncertainty,

but does not

0.75 V to 1.10 ns 1.40 ns include

0.85 V system

crosstalk.

0.60 V to 1.25 ns 1.75 ns

Performance

0.70 V

may vary

with system

crosstalk

performance.

Data position Sample clock rising edge, Sample clock falling edge, or Delay from —

modes Sample clock rising edge.

Data delay NI 6544/6545: 1 bank for all channels and PFI lines Multibank

banks data delay is

NI 6547/6548: 3 banks

supported

Bank 0: DIO<0..3>, DIO<16..19>, DIO<28..31>, PFI <0..3> only in

Bank 1: DIO<4..7>, DIO<20..23> NI-HSDIO

1.7 and later.

Bank 2: DIO<8..15>, DIO<24..27>

Acquisition 0.0 to 1.0 Sample clock periods Resolution is

data delay nonlinearly

range dependent on

clock

Acquisition 117 ps to 143 ps, nominal frequency

data delay and may be

resolution queried for

by using

Acquisition On Board Clock External Clock and STROBE

data delay NI-HSDIO.

frequency All supported frequencies Frequencies ≥ 20 MHz

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 17

Specification Value Comments

Setup time to 900 ps Nominal;

sample clock does not

(tsusc) include

channel-to-

Hold time to 425 ps channel

sample clock skew, tDDCSC,

(tHSC) or tSCDDC.

Time delay 6.8 ns Nominal.

from DDC

connector to

internal

sample clock

Figure 7. Acquisition Timing Diagram Using STROBE as the Sample Clock

STROBE

STROBE (corrected)*

DATA CHANNELS tSUS

Data Position Rising Edge

tSUS

Data Position Falling Edge

tHS tSU

Data Position Delayed

tP tHS

δA

tSUS = Set-Up Time to STROBE

tHS = Hold Time from STROBE

0 ≤ δA ≤ 1 : Acquisition Data Delay (fraction of tP)

tP = 1 = Sample Clock Period

ƒ

*Note: When using an external Sample clock greater than 20 MHz, the duty cycle

is corrected to 50%.

18 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Figure 8. Acquisition Timing Diagram with Sample Clock Sources Other than STROBE

tP

Internal Sample Clock

Virtual Sample Clock

Projected to DDC

Connector

DATA CHANNELS

Sample Clock Rising Edge tHS

Data Position

tSUSC tHSC

Sample Clock Falling Edge

Data Position

tSUSC tHSC

δA

Virtual Sample Clock

Projected to DDC

Connector

DATA CHANNELS

Delayed from Sample Clock

Rising Edge Data Position

tSUSC tHSC

tDDCSC : Time Delay from DDC Connector to Internal Sample Clock

0 ≤ δA ≤ 1 : Acquisition Data Delay (fraction of tP)

1

tP = = Period of Sample Clock

ƒ

tSUSC = Set-Up Time to Sample Clock

tHSC = Hold Time to Sample Clock

CLK IN (SMA Jack Connector)

Specification Value Comments

Direction Input to device —

Destinations 1. Reference clock—for the phase lock loop (PLL) —

2. Sample clock

Input coupling AC —

Input ±10 VDC Nominal.

protection

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 19

Specification Value Comments

Input 50 Ω (default) or 1 kΩ Software-

impedance selectable;

Nominal.

Minimum 2 ns Nominal.

detectable

pulse width

Clock Clock must be continuous and free-running. —

requirements

Voltage ranges Square Waves —

0.65 Vpp to 5.0 Vpp

Sine Waves —

Voltage 0.65 Vpp 1.0 Vpp to 1.3 Vpp to 2.6 Vpp to

range to 5.0 Vpp 5.0 Vpp 5.0 Vpp 5.0 Vpp

Frequency 20 MHz 13 MHz 10 MHz 5 MHz to Supported by

range to to to 100 MHz NI 6544 and

100 MHz 100 MHz 100 MHz 6547 only.

20 MHz 13 MHz 10 MHz 5 MHz to Supported by

to to to 200 MHz NI 6545 and

200 MHz 200 MHz 200 MHz 6548 only.

20 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Specification Value Comments

As Sample Clock

Frequency NI 6544 and NI 6547: 20 kHz to 100 MHz Nominal

range 3 dB cutoff

NI 6545 and NI 6548: 20 kHz to 200 MHz

point at

100 MHz

when using

1 kΩ input

impedance.

Duty cycle f < 20 MHz: 25% to 75% —

range f ≥ 20 MHz: 40% to 60%

As Reference Clock

Reference 5 MHz to 100 MHz (Integer multiples of 1 MHz) —

clock

frequency

range

Reference ± 0.1% Required

clock accuracy of

frequency the external

accuracy Reference

clock source.

Reference 25% to 75% —

clock duty

cycle

STROBE (DDC Connector)

Specification Value Comments

Direction Input to device —

Destinations Sample clock (acquisition only) —

STROBE NI 6544, NI 6547: 100 Hz to 100 MHz —

frequency range

NI 6545, NI 6548: 100 Hz to 200 MHz

STROBE duty 40% to 60% for clock frequencies ≥ 20 MHz Duty cycle

cycle range at the

25% to 75% for clock frequencies < 20 MHz

programmed

Note: STROBE duty cycle is corrected to 50% at frequencies threshold.

≥ 20 MHz.

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 21

Specification Value Comments

Minimum 2 ns Nominal;

detectable pulse required at

width acquisition

voltage

thresholds.

Voltage Refer to the Acquisition Timing (Data, STROBE, and PFI <0..3> —

thresholds Channels) specifications in the Channel Specifications section.

Clock Clock must be continuous and free-running. —

requirements

Input 50 kΩ Nominal.

impedance

CLK OUT (SMA Jack Connector)

Specification Value Comments

Direction Output from device —

Sources 1. Sample clock (excluding STROBE) —

2. Reference clock (PLL)

Output 50 Ω Nominal.

impedance

Electrical Refer to the Generation Channels (Data, DDC CLK OUT, —

characteristics and PFI <0..3>) specifications in the Channel Specifications

section.

Logic type Matched with generation and acquisition sessions. —

DDC CLK OUT (DDC Connector)

Specification Value Comments

Direction Output from device —

Sources Sample clock (generation only) STROBE and

acquisition

Sample clock

cannot be

routed to DDC

CLK OUT.

Electrical Refer to the Generation Channels (Data, DDC CLK OUT, —

characteristics and PFI <0..3>) specifications in the Channel Specifications

section.

22 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Reference Clock (PLL)

Specification Value Comments

Reference 1. PXI_CLK100 (PXI Express backplane) Provides the

clock sources 2. CLK IN (SMA jack connector) reference

3. None (internal oscillator locked to an internal reference) frequency for

the PLL.

Lock time 150 ms Maximum,

not including

software

latency.

Reference 5 MHz to 100 MHz (integer multiple of 1 MHz) 0.1% required

clock accuracy.

frequencies

Reference 25% to 75% —

clock duty

cycle range

Reference CLK OUT (SMA jack connector) —

clock

destinations

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 23

Waveform Specifications

Memory and Scripting

Specification Value Comments

Memory The NI 6544/6545/6547/6548 uses the Synchronization and Refer to the

architecture Memory Core (SMC) technology in which waveforms and Onboard

instructions share onboard memory. Parameters such as number of Memory

script instructions, maximum number of waveforms in memory, section

and number of samples (S) available for waveform storage are in the

flexible and user-defined. NI Digital

Waveform

Generator/

Analyzer Help

for more

information.

Onboard 1 Mbit/channel 8 Mbit/channel 64 Mbit/channel Maximum

memory size limit for

(generation generation

and sessions

acquisition) assumes no

scripting

instructions.

Generation Single-waveform mode —

modes Generate a single waveform once, n times, or continuously.

Scripted mode

Generate a simple or complex sequence of waveforms. Use scripts

to describe the waveforms to be generated, the order in which the

waveforms are generated, how many times the waveforms are

generated, and how the device responds to Script triggers.

24 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Specification Value Comments

Generation Sample Rate Sample rate

minimum dependent.

waveform size 200 MHz Increasing

in samples (S) (NI 6545/6548 sample rate

Configuration Only) 100 MHz

increases

Single waveform 1S 1S minimum

waveform size

Continuous 128 S 64 S requirement.

waveform For

information

Stepped sequence 128 S 64 S on these

Burst sequence 1056 S 512 S configurations,

refer to

Common

Scripting Use

Cases in the

NI Digital

Waveform

Generator/

Analyzer Help.

Generation 1 to 16,777,216 —

finite repeat

count

Generation Data Width = 4 Data Width = 2 DDR mode

waveform sets data

quantum 1 sample 2 samples width to 2.

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 25

Specification Value Comments

Generation Data width = 4 Data width = 2 —

waveform

block size 32 samples 64 samples

(in physical

memory)

Acquisition 1S Regardless of

minimum waveform

record size size,

NI-HSDIO

allocates

at least

640 bytes for a

record.

Acquisition 1S —

record

quantum

Acquisition 2,147,483,647 Session should

maximum fetch fast

number of enough so that

records unfetched data

is not

overwritten.

Acquisition 0 up to full record —

number of

pre-Reference

trigger

samples

Acquisition 0 up to full record —

number of

post-

Reference

trigger

samples

26 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Triggers (Inputs to the NI 6544/6545/6547/6548)

Specification Value Comments

Trigger types 1. Start trigger —

2. Pause trigger

3. Script trigger <0..3> (generation sessions only)

4. Reference trigger (acquisition sessions only)

5. Advance trigger (acquisition sessions only)

6. Stop Trigger (generation sessions only)

Sources 1. PFI 0 (SMA jack connector) —

2. PFI <1..3> (DDC connector)

3. PXI_TRIG<0..7> (PXI Express backplane)

4. Pattern match (acquisition sessions only)

5. Software (user function call)

6. Disabled (do not wait for a trigger)

Trigger 1. Start trigger (edge detection: rising or falling) —

detection 2. Pause trigger (level detection: high or low)

3. Script trigger <0..3> (edge detection: rising or falling;

level detection: high or low)

4. Reference trigger (edge detection: rising or falling)

5. Advance trigger (edge detection: rising or falling)

6. Stop Trigger (edge detection: rising or falling)

Minimum 15 ns —

required

trigger pulse

width

Destinations 1. PFI 0 (SMA jack connectors) Each trigger

2. PFI <1..3> (DDC connector) can be routed

3. PXI_TRIG<0..6> (PXI Express backplane) to any

destination

except the

Pause trigger.

The Pause

trigger cannot

be exported.

Trigger rearm Reference Maximum

time Start to Start to Advance to to number of

Reference Advance Advance Reference samples.

Trigger Trigger Trigger Trigger

150 s 220 s 220 s 220 s

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 27

Specification Value Comments

Delay from Generation Sessions Acquisition Sessions Maximum;

Pause trigger Use the Data

to Pause state 50 Sample clock Synchronous with the data Active event

and Stop periods + 300 ns during

trigger to Done generation to

state determine on

a sample by

sample basis

when the

device enters

the Pause or

Done states.

Delay from 3 Sample clock periods + 600 ns Maximum;

trigger to Start trigger

digital data and Script

output triggers.

Events (Generated from the NI 6544/6545/6547/6548)

Specification Value Comments

Event type 1. Marker <0..2> (generation sessions only) —

2. Data Active event (generation sessions only)

3. Ready for Start event

4. Ready for Advance event (acquisition sessions only)

5. End of Record event (acquisition sessions only)

Destinations 1. PFI 0 (SMA jack connectors) Each event

2. PFI <1..3> (DDC connector) can be routed to

any destination,

3. PXI_TRIG<0..6> (PXI Express backplane)

except the Data

Active event.

The Data

Active event

can only be

routed to the

PFI channels.

Marker time Markers can be placed at any sample when using SDR mode. —

resolution Markers must be placed at an integer multiple of two samples

(placement)

when using DDR mode.

28 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Miscellaneous

Specification Value Comments

Warm-up time 15 minutes —

On Board Clock characteristics (valid when PLL reference source is set to None)

Frequency ±150 ppm Typical,

accuracy including

temperature

effects.

Aging ±5 ppm first year Nominal.

Power

Value

Specification Characteristic Maximum Comments

+3.3 VDC 1.75 A 1.77 A Characteristic

results are

+12 VDC 2.2 A 2.3 A commensurate

with an average

Total power 32.2 W 33.5 W

user application

using all data

channels into

high impedance

load. Maximum

results include

worst case data

pattern.

Physical

Specification Value Comments

Dimensions 21.6 × 2.0 × 13.0 cm —

Single 3U CompactPCI Express slot; PXI Express compatible

Weight 18.3 oz (519 g) —

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 29

I/O Panel Connectors

Connector

Label Function(s) Type

CLK IN External Sample clock, external Reference clock. SMA jack

PFI 0 Events, triggers. SMA jack

CLK OUT External Sample clock, exported Reference clock. SMA jack

Digital Data & Digital data channels, exported Sample clock, STROBE, events, 68pin VHDCI

Control (DDC) triggers.

Software

Specification Value Comments

Driver software NI-HSDIO driver software 1.6 or later. NI-HSDIO allows you to —

configure and control the NI 6544/6545/6547/6548. NI-HSDIO

provides application interfaces for many development

environments. NI-HSDIO follows IVI application programming

interface (API) guidelines.

Hardware compare, per cycle tristate, and multibank data delay

are supported only in NI-HSDIO 1.7 or later.

Application NI-HSDIO provides programming interfaces for the following Refer to the

software application development environments (ADEs): NI-HSDIO

• National Instruments LabVIEW Instrument

Driver Readme

• National Instruments LabWindows™/CVI™

for more

• Microsoft Visual C/C++ information

about

supported ADE

versions.

Test panel National Instruments Measurement & Automation Explorer —

(MAX) provides test panels with basic acquisition and

generation functionality for the NI 6544/6545/6547/6548.

MAX is included on the NI-HSDIO driver CD.

30 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Environment

Note To ensure that the NI 6544/6545/6547/6548 cools effectively, follow the

guidelines in the Maintain Forced Air Cooling Note to Users included with the

NI 6544/6545/6547/6548. The NI 6544/6545/6547/6548 is intended for indoor use

only.

Specification Value Comments

Operating 0 to 55 ºC in all NI PXI Express and hybrid NI PXI Express —

temperature chassis.

Storage -20 to 70 ºC —

temperature

Operating 10% to 90% relative humidity, noncondensing —

relative (Meets IEC 60068-2-56.)

humidity

Storage 5% to 95% relative humidity, noncondensing —

relative (Meets IEC 60068-2-56.)

humidity

Operating 30 g, half-sine, 11 ms pulse —

shock (Meets IEC 60068-2-27. Test profile developed in accordance

with MIL-PRF-28800F.)

Storage shock 50 g, half-sine, 11 ms pulse —

(Meets IEC 60068-2-27. Test profile developed in accordance

with MIL-PRF-28800F.)

Operating 5 Hz to 500 Hz, 0.31 grms —

vibration (Meets IEC 60068-2-64.)

Storage 5 Hz to 500 Hz, 2.46 grms —

vibration (Meets IEC 60068-2-64. Test profile exceeds requirements of

MIL-PRF-28800F, Class B.)

Altitude 0 m to 2,000 m above sea level (at 25º C ambient temperature) —

Pollution 2 —

Degree

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 31

Safety, Electromagnetic Compatibility, and CE

Compliance

Specification Value Comments

Safety The NI 6544/6545/6547/6548 meets the requirements of For UL and

the following standards of safety for electrical equipment other safety

for measurement, control, and laboratory use: certifications, refer

• IEC 61010-1, EN 61010-1 to the product label

• UL 61010-1, CSA 61010-1 or visit ni.com/

certification,

search by model

number or product

line, and click the

appropriate link in

the Certification

column.

Electromagnetic The NI 6544/6545/6547/6548 meets the requirements of To meet EMC

Compatibility the following EMC standards for electrical equipment for compliance the

measurement, control, and laboratory use: following cautions

EN 61326-1 (IEC 61326-1): Class A emissions, Basic apply.

immunity

EN 55011 (CISPR 11): Group 1, Class A emissions

AS/NZS CISPR 11: Group 1, Class A emissions

FCC 47 CFR Part 15B: Class A emissions

ICES-001: Class A emissions

For the standards applied to assess the EMC of this product,

refer to the Online Product Certification section below.

Note: SHC68-C68-D4 or SHC68-C68-D2 shielded cable and provided cable ferrites must be used when

operating the NI 6544/6545/6547/6548.

Note: EMI filler panels (NI P/N 778700-01) must be installed in all empty slots of the

NI 6544/6545/6547/6548.

CE Compliance This product meets the essential requirements of applicable —

European Directives, as amended for

CE marking, as follows:

2006/95/EC; Low-Voltage Directive (safety)

2004/108/EC; Electromagnetic Compatibility

Directive (EMC)

Online Product Refer to the product Declaration of Conformity (DoC) for —

Certification additional regulatory compliance information. To obtain

product certifications and the DoC for this product, visit

ni.com/certification, search by model number or

product line, and click the appropriate link in the

Certification column.

32 | ni.com | NI PXIe-6544/6545/6547/6548 Specifications

Environmental NI is committed to designing and manufacturing products —

Management in an environmentally responsible manner. NI recognizes

that eliminating certain hazardous substances from our

products is beneficial to the environment and to NI

customers.

For additional environmental information, refer to the

Minimize Our Environmental Impact web page at

ni.com/environment. This page contains the

environmental regulations and directives with which NI

complies, as well as other environmental information not

included in this document.

Waste Electrical EU Customers: At the end of the product life cycle, all

and Electronic products must be sent to a WEEE recycling center.

Equipment For more information about WEEE recycling centers,

(WEEE) National Instruments WEEE initiatives, and compliance

with WEEE Directive 2002/96/EC on Waste and Electronic

Equipment, visit ni.com/environment/weee.

⬉ᄤֵᙃѻક∵ᶧࠊㅵ⧚ࡲ⊩ ˄Ё RoHS˅

Ёᅶ᠋ National Instruments ヺড়Ё⬉ᄤֵᙃѻકЁ䰤ࠊՓ⫼ᶤѯ᳝ᆇ⠽䋼ᣛҸ

(RoHS)DŽ݇Ѣ National Instruments Ё RoHS ড়㾘ᗻֵᙃˈ䇋ⱏᔩ ni.com/

environment/rohs_chinaDŽ (For information about China RoHS compliance,

go to ni.com/environment/rohs_china.)

NI PXIe-6544/6545/6547/6548 Specifications | © National Instruments | 33

Refer to the NI Trademarks and Logo Guidelines at ni.com/trademarks for more information on National Instruments trademarks. Other

product and company names mentioned herein are trademarks or trade names of their respective companies. For patents covering National

Instruments products/technology, refer to the appropriate location: Help»Patents in your software, the patents.txt file on your media, or the

National Instruments Patents Notice at ni.com/patents. You can find information about end-user license agreements (EULAs) and third-party

legal notices in the readme file for your NI product. Refer to the Export Compliance Information at ni.com/legal/export-compliance

for the National Instruments global trade compliance policy and how to obtain relevant HTS codes, ECCNs, and other import/export data.

© 2009–2014 National Instruments. All rights reserved.

374962E Mar14

You might also like

- Test 2 Study Guide PhysicsDocument11 pagesTest 2 Study Guide PhysicsKerry Roberts Jr.No ratings yet

- Sample BQ 1Document76 pagesSample BQ 1marani_rahmat100% (2)

- Sculi Operating DescriptionDocument4 pagesSculi Operating DescriptionMACHINERY101GEAR100% (1)

- Modern Digital and Analog Communication Systems 4th Edition by LathiDocument926 pagesModern Digital and Analog Communication Systems 4th Edition by Lathimhmd_4u82% (11)

- Debug and Testability Features For Multi-Protocol 10G SerdesDocument5 pagesDebug and Testability Features For Multi-Protocol 10G SerdesvelusnNo ratings yet

- High Speed Clock and Data Recovery For SERDES Applications: October 2012Document6 pagesHigh Speed Clock and Data Recovery For SERDES Applications: October 2012S. Suman Kumar ReddyNo ratings yet

- CH 5 PDFDocument6 pagesCH 5 PDFBijoy BanerjeeNo ratings yet

- OPTIMIZATIONDocument33 pagesOPTIMIZATIONIslam BarakatNo ratings yet

- ePMP Understanding Throughput CapacityV1.0 PDFDocument9 pagesePMP Understanding Throughput CapacityV1.0 PDFtrsghstrhsNo ratings yet

- UMTS-RNO-0005 - Drive Test AnalysisDocument30 pagesUMTS-RNO-0005 - Drive Test AnalysiskpreetnarendraNo ratings yet

- 3G Technology StudyDocument9 pages3G Technology StudyAbhay SharmaNo ratings yet

- Huawei UTRAN Dual Carrier Implementation GuideDocument11 pagesHuawei UTRAN Dual Carrier Implementation GuideSajid Saleem0% (1)

- Vlsi Impimentation of OfdmDocument13 pagesVlsi Impimentation of Ofdmprashanth68760100% (1)

- Vlsi Imlememt of OdfmDocument10 pagesVlsi Imlememt of OdfmShrey MalikNo ratings yet

- 5G NR Modulation Analysis (89601BHNC)Document25 pages5G NR Modulation Analysis (89601BHNC)sandeep yadavNo ratings yet

- D Agent - 1 - Work 310 S Upload 172179AE1Document36 pagesD Agent - 1 - Work 310 S Upload 172179AE1Mor BenNo ratings yet

- Lte BibleDocument307 pagesLte BibleNik100% (3)

- Wcdma School of TechDocument27 pagesWcdma School of TechSomnath DiwakarNo ratings yet

- ADRE DatasheetDocument16 pagesADRE DatasheetAhmad Musaddiq MohammadNo ratings yet

- GX 5296 DsDocument8 pagesGX 5296 Dsapi-531921481No ratings yet

- Asic DDR PhyDocument1 pageAsic DDR PhylmlululuNo ratings yet

- General Elspec Meter ShortDocument30 pagesGeneral Elspec Meter ShortCampus Pass OfficeNo ratings yet

- 5G PHY Layer ProcessingDocument24 pages5G PHY Layer ProcessingveereshNo ratings yet

- EC 603 (A) - Data Comm Lab ManualDocument23 pagesEC 603 (A) - Data Comm Lab ManualRishi JhaNo ratings yet

- ADRE DatasheetDocument31 pagesADRE DatasheetEduard RamosNo ratings yet

- LTE New 1Document10 pagesLTE New 1Rupesh SharmaNo ratings yet

- Workshop For Optical Transmission, DCN and OthersDocument65 pagesWorkshop For Optical Transmission, DCN and OthersGopal BiswasNo ratings yet

- UMTS Network Planning and HSDPA Theory Optimization ProceduresDocument35 pagesUMTS Network Planning and HSDPA Theory Optimization ProceduresRizwan YousufNo ratings yet

- ITC2014 Poster02Document2 pagesITC2014 Poster02Keyur MahantNo ratings yet

- Wcdma Drive Test Using Tems & Some Basic of WCDMA Before DriveDocument65 pagesWcdma Drive Test Using Tems & Some Basic of WCDMA Before DriveAgni Kumar MohanandaNo ratings yet

- RAN Dim v8.0 User ManualDocument116 pagesRAN Dim v8.0 User ManualTruong PhatNo ratings yet

- VE464Document6 pagesVE464Timofte Relu50% (2)

- Beta Counter Perkin BrochureDocument4 pagesBeta Counter Perkin BrochureFranklin VrNo ratings yet

- 5G Questions Nabawy V1Document35 pages5G Questions Nabawy V1أبوعمر الفاروق عبدالرحمنNo ratings yet

- DC HSDPA PrerequisitesDocument12 pagesDC HSDPA Prerequisitesoptim_paulNo ratings yet

- Infomar SBP Data User GuideDocument9 pagesInfomar SBP Data User GuideAmmar DanialNo ratings yet

- Designing and Testing Cdma2000 Base StationsDocument40 pagesDesigning and Testing Cdma2000 Base StationsPavel SchukinNo ratings yet

- 5G Toolbox Model, Simulate, DesignDocument21 pages5G Toolbox Model, Simulate, Designarekpanjen0% (1)

- Iskraemeco - Data Sheet P2LPC-Koncentrator AngDocument4 pagesIskraemeco - Data Sheet P2LPC-Koncentrator AngSuttisak SuriyachanhomNo ratings yet

- Calibration and Testing of Phasor Measurement UnitDocument13 pagesCalibration and Testing of Phasor Measurement UnitSalvador ArcosNo ratings yet

- 310SV+TurboSafe Rev.3Document2 pages310SV+TurboSafe Rev.3Demetri M. ScytheNo ratings yet

- Low Cost Gigabit Rate Transmit/Receive Chip Set With TTL I/OsDocument40 pagesLow Cost Gigabit Rate Transmit/Receive Chip Set With TTL I/OsZak zsNo ratings yet

- 5G NR - Personal ReadingDocument28 pages5G NR - Personal ReadingAngela BarrNo ratings yet

- This Section Will Summarize The Basic Parameters of The LTEDocument28 pagesThis Section Will Summarize The Basic Parameters of The LTEAshirbad PandaNo ratings yet

- GTDS AggregatorTAP CopperHighDensity010119Document2 pagesGTDS AggregatorTAP CopperHighDensity010119Nirmal KNo ratings yet

- Measurements On 3GPP Base Station Transmitter Signals: Subject To Change - Josef Wolf 08/01 - 1EF44 - 1EDocument26 pagesMeasurements On 3GPP Base Station Transmitter Signals: Subject To Change - Josef Wolf 08/01 - 1EF44 - 1EAnonymous 5yosdd6WUBNo ratings yet

- 1140 Data SheetDocument6 pages1140 Data SheetYsidro MundarainNo ratings yet

- WCDMA / HSDPA Signalling Mode: R&S CMU300 Radio Communication Tester For 2G/3G Base StationsDocument17 pagesWCDMA / HSDPA Signalling Mode: R&S CMU300 Radio Communication Tester For 2G/3G Base StationsRahul KumarNo ratings yet

- CDMA Overview & BSNL PlansDocument39 pagesCDMA Overview & BSNL PlansAkash AnjanNo ratings yet

- 5G NR (New Radio) X-Series MeasurementDocument20 pages5G NR (New Radio) X-Series MeasurementCharles JenNo ratings yet

- A 500 MHZ GaAs Digital RF' Memory Modulator ICDocument4 pagesA 500 MHZ GaAs Digital RF' Memory Modulator ICAjinkya KaleNo ratings yet

- MD1230ADocument16 pagesMD1230AramonNo ratings yet

- Evo Controller 8200 RNCDocument51 pagesEvo Controller 8200 RNCIbrahim AlabiNo ratings yet

- Unit 1: Fundamentals of Programmable DSPS: Bhooshan HumaneDocument60 pagesUnit 1: Fundamentals of Programmable DSPS: Bhooshan HumaneFirozNo ratings yet

- 5G TLW FinalDocument49 pages5G TLW FinalSatyavaraprasad Balla100% (1)

- C264 BCU Brochure EN 2018 08 Grid GA 0828 PDFDocument8 pagesC264 BCU Brochure EN 2018 08 Grid GA 0828 PDFAkinbode Sunday OluwagbengaNo ratings yet

- Positioning Techniques in 3G Networks: Independent Study PresentationDocument47 pagesPositioning Techniques in 3G Networks: Independent Study PresentationRuchira ChinthakaNo ratings yet

- Innovations Improve LNG: Terminal Efficiency and SafetyDocument3 pagesInnovations Improve LNG: Terminal Efficiency and SafetyL0NE DruidNo ratings yet

- HLD RRCDocument166 pagesHLD RRCafroxxxNo ratings yet

- Practical Data Acquisition for Instrumentation and Control SystemsFrom EverandPractical Data Acquisition for Instrumentation and Control SystemsNo ratings yet

- Single Carrier FDMA: A New Air Interface for Long Term EvolutionFrom EverandSingle Carrier FDMA: A New Air Interface for Long Term EvolutionNo ratings yet

- Lower 6 - Tutorial 17Document2 pagesLower 6 - Tutorial 17ronese augustusNo ratings yet

- Ned Graphics Color ManagementDocument13 pagesNed Graphics Color ManagementmariosagastumeNo ratings yet

- Hydrogen FuelDocument18 pagesHydrogen FuelSreevatsanadigNo ratings yet

- Pneumatic Auto Feed Sheet Cutting MachineDocument5 pagesPneumatic Auto Feed Sheet Cutting MachineVigneshwaran Srinivasan100% (1)

- Materials System SpecificationDocument12 pagesMaterials System SpecificationFlorante NoblezaNo ratings yet

- Watershed PresentationDocument19 pagesWatershed Presentationmamta19sharma100% (1)

- Data Sheet 3VM1225-4EE32-0AA0: ModelDocument7 pagesData Sheet 3VM1225-4EE32-0AA0: ModelChristian A LCNo ratings yet

- Chapter - 1: 1.0 Over View of ProjectDocument10 pagesChapter - 1: 1.0 Over View of ProjectsunilkumareceNo ratings yet

- Soil Mech Soil Classification UscsDocument18 pagesSoil Mech Soil Classification UscsZach GarciaNo ratings yet

- CS 25 RockfillDocument3 pagesCS 25 Rockfillraduga_fb100% (1)

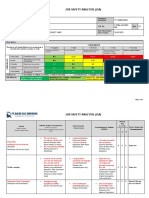

- Jsa Cutting PileDocument6 pagesJsa Cutting Pilehilmi hilmiNo ratings yet

- Airex C70: Universal Structural FoamDocument3 pagesAirex C70: Universal Structural FoamBaris senelNo ratings yet

- ,MLMKMDocument81 pages,MLMKMfareesyaNo ratings yet

- Explanation TextDocument3 pagesExplanation TextaajunaidiiNo ratings yet

- ReadmeDocument16 pagesReadmeLuzMaríaSotoNo ratings yet

- Kvs PGT Computer Science Mock Test 06Document10 pagesKvs PGT Computer Science Mock Test 06Happy RajputNo ratings yet

- IPCop With DansGuardian Installation and ConfigurationDocument6 pagesIPCop With DansGuardian Installation and ConfigurationnopeiccoNo ratings yet

- Gypsum Blocks - Definitions, Requirements and Test Methods: British Standard Bs en 12859:2001Document38 pagesGypsum Blocks - Definitions, Requirements and Test Methods: British Standard Bs en 12859:2001AA0809No ratings yet

- Gah Lord Wisdom ID: 10686216 AREN 304: Assignment 4Document8 pagesGah Lord Wisdom ID: 10686216 AREN 304: Assignment 4Wisdom LordNo ratings yet

- 6922-520-XZ-DS-6019 - Rev ADocument1 page6922-520-XZ-DS-6019 - Rev AkanchithalaiNo ratings yet

- Common Emitter Amplifier PDFDocument2 pagesCommon Emitter Amplifier PDFTodd0% (1)

- Scripting MetaFrameDocument82 pagesScripting MetaFrameMamex SusuNo ratings yet

- Impeller Trim For PumpDocument9 pagesImpeller Trim For PumpkasiNo ratings yet

- Parts Guide Manual: HD-514 A1RmDocument17 pagesParts Guide Manual: HD-514 A1RmmemetNo ratings yet

- LT-636 FA-200 Installation and Operation Manual1Document52 pagesLT-636 FA-200 Installation and Operation Manual1Ksmart1973No ratings yet

- Exam 3: Cadt 150 - SurveyingDocument2 pagesExam 3: Cadt 150 - SurveyingDasie LabuguenNo ratings yet