Professional Documents

Culture Documents

HT24LC02: CMOS 2K 2-Wire Serial EEPROM

HT24LC02: CMOS 2K 2-Wire Serial EEPROM

Uploaded by

hcarcaroOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HT24LC02: CMOS 2K 2-Wire Serial EEPROM

HT24LC02: CMOS 2K 2-Wire Serial EEPROM

Uploaded by

hcarcaroCopyright:

Available Formats

HT24LC02

CMOS 2K 2-Wire Serial EEPROM

Features

· Operating voltage · Automatic erase-before-write operation

- 2.2V~5.5V for temperature 0°C to +70°C · Partial page write allowed

- 2.4V~5.5V for temperature -40°C to +85°C · 8-byte Page write modes

· Low power consumption · Write operation with built-in timer

- Operation: 5mA max. · Hardware controlled write protection

- Standby: 5mA max. · 40-year data retention

· Internal organization: 256´8

· 106 erase/write cycles per word

· 2-wire serial interface

· Commercial temperature range (-40°C to +85°C)

· Write cycle time: 5ms max.

· 8-pin DIP/SOP/TSSOP package

General Description

The HT24LC02 is a 2K-bit serial read/write non-volatile low power and low voltage operation are essential. Up

memory device using the CMOS floating gate process. to eight HT24LC02 devices may be connected to the

Its 2048 bits of memory are organized into 256 words same 2-wire bus. The HT24LC02 is guaranteed for 1M

and each word is 8 bits. The device is optimized for use erase/write cycles and 40-year data retention.

in many industrial and commercial applications where

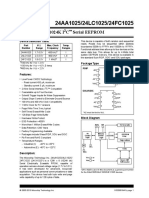

Block Diagram Pin Assignment

A 0 1 8 V C C

S C L I/O H V P u m p

C o n tro l A 1 2 7 W P

S D A L o g ic

A 2 3 6 S C L

X

V S S 4 5 S D A

D E E P R O M

M e m o ry E A rra y H T 2 4 L C 0 2

W P C o n tro l C

L o g ic 8 D IP -A /S O P -A /T S S O P -A

P a g e B u f

Y D E C

A d d re s s

A 0 ~ A 2 S e n s e A M P

C o u n te r

R /W C o n tro l

V C C

V S S

Pin Description

Pin Name I/O Description

A0~A2 I Address inputs

SDA I/O Serial data inputs/output

SCL I Serial clock data input

WP I Write protect

VSS ¾ Negative power supply, ground

VCC ¾ Positive power supply

Rev. 1.30 1 June 27, 2007

HT24LC02

Absolute Maximum Ratings

Supply Voltage ..........................VSS-0.3V to VSS+6.0V Storage Temperature ............................-50°C to 125°C

Input Voltage .............................VSS-0.3V to VCC+0.3V Operating Temperature...........................-40°C to 85°C

Note: These are stress ratings only. Stresses exceeding the range specified under ²Absolute Maximum Ratings² may

cause substantial damage to the device. Functional operation of this device at other conditions beyond those

listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliabil-

ity.

D.C. Characteristics

Test Conditions

Symbol Parameter Min. Typ. Max. Unit

VCC Conditions

0°C to +70°C 2.2 ¾ 5.5 V

VCC Operating Voltage ¾

-40°C to +85°C 2.4 ¾ 5.5 V

ICC1 Operating Current 5V Read at 100kHz ¾ ¾ 2 mA

ICC2 Operating Current 5V Write at 100kHz ¾ ¾ 5 mA

VIL Input Low Voltage ¾ ¾ -1 ¾ 0.3VCC V

VIH Input High Voltage ¾ ¾ 0.7VCC ¾ VCC+0.5 V

VOL Output Low Voltage 2.4V IOL=2.1mA ¾ ¾ 0.4 V

ILI Input Leakage Current 5V VIN=0 or VCC ¾ ¾ 1 mA

ILO Output Leakage Current 5V VOUT=0 or VCC ¾ ¾ 1 mA

ISTB1 Standby Current 5V VIN=0 or VCC ¾ ¾ 5 mA

ISTB2 Standby Current 2.4V VIN=0 or VCC ¾ ¾ 4 mA

CIN Input Capacitance (See Note) ¾ f=1MHz 25°C ¾ ¾ 6 pF

COUT Output Capacitance (See Note) ¾ f=1MHz 25°C ¾ ¾ 8 pF

Note: These parameters are periodically sampled but not 100% tested

Rev. 1.30 2 June 27, 2007

HT24LC02

A.C. Characteristics

Standard Mode* VCC=5V±10%

Symbol Parameter Remark Unit

Min. Max. Min. Max.

fSK Clock Frequency ¾ ¾ 100 ¾ 400 kHz

tHIGH Clock High Time ¾ 4000 ¾ 600 ¾ ns

tLOW Clock Low Time ¾ 4700 ¾ 1200 ¾ ns

tr SDA and SCL Rise Time Note ¾ 1000 ¾ 300 ns

tf SDA and SCL Fall Time Note ¾ 300 ¾ 300 ns

After this period the

tHD:STA START Condition Hold Time first clock pulse is 4000 ¾ 600 ¾ ns

generated

Only relevant for

tSU:STA START Condition Setup Time repeated START 4000 ¾ 600 ¾ ns

condition

tHD:DAT Data Input Hold Time ¾ 0 ¾ 0 ¾ ns

tSU:DAT Data Input Setup Time ¾ 200 ¾ 100 ¾ ns

tSU:STO STOP Condition Setup Time ¾ 4000 ¾ 600 ¾ ns

tAA Output Valid from Clock ¾ ¾ 3500 ¾ 900 ns

Time in which the bus

must be free before a

tBUF Bus Free Time 4700 ¾ 1200 ¾ ns

new transmission can

start

Input Filter Time Constant Noise suppression

tSP ¾ 100 ¾ 50 ns

(SDA and SCL Pins) time

tWR Write Cycle Time ¾ ¾ 5 ¾ 5 ms

Note: These parameters are periodically sampled but not 100% tested

* The standard mode means VCC= 2.2V to 5.5V at Ta= 0°C to +70°C, VCC= 2.4V to 5.5V at Ta= -40°C to +85°C

For relative timing, refer to timing diagrams

Rev. 1.30 3 June 27, 2007

HT24LC02

Functional Description

· Serial clock (SCL) · Acknowledge

The SCL input is used for positive edge clock data into All addresses and data words are serially transmitted

each EEPROM device and negative edge clock data to and from the EEPROM in 8-bit words. The

out of each device. EEPROM sends a zero to acknowledge that it has re-

ceived each word. This happens during the ninth clock

· Serial data (SDA)

cycle.

The SDA pin is bidirectional for serial data transfer.

The pin is open-drain driven and may be wired-OR D a ta a llo w e d

with any number of other open-drain or open collector to c h a n g e

S D A

devices.

· A0, A1, A2

S C L

The A2, A1 and A0 pins are device address inputs that

S ta rt A d d re s s o r N o A C K S to p

are hard wired for the HT24LC02. As many as eight c o n d itio n a c k n o w le d g e s ta te c o n d itio n

2K devices may be addressed on a single bus system v a lid

(the device addressing is discussed in detail under the

Device Addressing section). Device Addressing

· Write protect (WP) The 2K EEPROM devices all require an 8-bit device ad-

The HT24LC02 has a write protect pin that provides dress word following a start condition to enable the chip

hardware data protection. The write protect pin allows for a read or write operation. The device address word

normal read/write operations when connected to the consist of a mandatory one, zero sequence for the first

VSS. When the write protect pin is connected to Vcc, four most significant bits (refer to the diagram showing

the write protection feature is enabled and operates the Device Address). This is common to all the

as shown in the following table. EEPROM device.

WP Pin The next three bits are the A2, A1 and A0 device ad-

Protect Array

Status

dress bits for the 2K EEPROM. These three bits must

At VCC Full Array (2K) compare to their corresponding hard-wired input pins.

At VSS Normal Read/Write Operations The 8th bit of device address is the read/write operation

select bit. A read operation is initiated if this bit is high

and a write operation is initiated if this bit is low.

Memory Organization

If the comparison of the device address succeed the

· HT24LC02, 2K Serial EEPROM

EEPROM will output a zero at ACK bit. If not, the chip will

Internally organized with 256 8-bit words, the 2K re-

return to a standby state.

quires an 8-bit data word address for random word ad-

dressing.

1 0 1 0 A 2 A 1 A 0 R /W

Device Operations

D e v ic e A d d r e s s

· Clock and data transition

Data transfer may be initiated only when the bus is not Write Operations

busy. During data transfer, the data line must remain

· Byte write

stable whenever the clock line is high. Changes in

data line while the clock line is high will be interpreted A write operation requires an 8-bit data word address

as a START or STOP condition. following the device address word and acknowledg-

ment. Upon receipt of this address, the EEPROM will

· Start condition again respond with a zero and then clock in the first

A high-to-low transition of SDA with SCL high is a start 8-bit data word. After receiving the 8-bit data word, the

condition which must precede any other command EEPROM will output a zero and the addressing de-

(refer to Start and Stop Definition Timing diagram). vice, such as a microcontroller, must terminate the

· Stop condition write sequence with a stop condition. At this time the

A low-to-high transition of SDA with SCL high is a stop EEPROM enters an internally-timed write cycle to the

condition. After a read sequence, the stop command non-volatile memory. All inputs are disabled during

will place the EEPROM in a standby power mode (re- this write cycle and EEPROM will not respond until the

fer to Start and Stop Definition Timing Diagram). write is completed (refer to Byte write timing).

Rev. 1.30 4 June 27, 2007

HT24LC02

· Page write

S e n d W r ite C o m m a n d

The 2K EEPROM is capable of an 8-byte page write.

A page write is initiated the same as byte write, but the

S e n d S to p C o n d itio n

microcontroller does not send a stop condition after to In itia te W r ite C y c le

the first data word is clocked in. Instead, after the

EEPROM acknowledges the receipt of the first data

S e n d S ta rt

word, the microcontroller can transmit up to seven

more data words. The EEPROM will respond with a

zero after each data word received. The S e n d C o tr o ll B y te

w ith R /W = 0

microcontroller must terminate the page write se-

quence with a stop condition.

The data word address lower three (2K) bits are inter-

(A C K = 0 )? N o

nally incremented following the receipt of each data

word. The higher data word address bits are not incre-

mented, retaining the memory page row location (re- Y e s

fer to Page write timing). N e x t O p e r a tio n

· Acknowledge polling

Acknowledge Polling Flow

To maximise bus throughput, one technique is to allow

· Current address read

the master to poll for an acknowledge signal after the

start condition and the control byte for a write com- The internal data word address counter maintains the

mand have been sent. If the device is still busy imple- last address accessed during the last read or write op-

menting its write cycle, then no ACK will be returned. eration, incremented by one. This address stays valid

The master can send the next read/write command between operations as long as the chip power is main-

when the ACK signal has finally been received. tained. The address roll over during read from the last

byte of the last memory page to the first byte of the first

· Write protect

page. The address roll over during write from the last

The HT24LC02 has a write-protect function and pro- byte of the current page to the first byte of the same

gramming will then be inhibited when the WP pin is page. Once the device address with the read/write se-

connected to VCC. Under this mode, the HT24LC02 is lect bit set to one is clocked in and acknowledged by

used as a serial ROM. the EEPROM, the current address data word is seri-

· Read operations ally clocked out. The microcontroller should respond a

The HT24LC02 supports three read operations, No ACK (High) signal and following stop condition (re-

namely, current address read, random address read fer to Current read timing).

and sequential read. During read operation execution,

the read/write select bit should be set to ²1².

B y te W r ite T im in g

D e v ic e a d d r e s s W o rd a d d re s s D A T A

S D A S A 2 A 1 A 0 P

S ta rt R /W A C K A C K

A C K

S to p

P a g e W r ite T im in g

D e v ic e a d d r e s s W o rd a d d re s s D A T A n D A T A n + 1 D A T A n + x

S D A S P

S ta rt A C K A C K A C K A C K

S to p

C u r r e n t R e a d T im in g

D e v ic e a d d r e s s D A T A

S to p

S D A S A 2 A 1 A 0 P

S ta rt A C K N o A C K

Rev. 1.30 5 June 27, 2007

HT24LC02

· Random read · Sequential read

A random read requires a dummy byte write sequence Sequential reads are initiated by either a current ad-

to load in the data word address which is then clocked dress read or a random address read. After the

in and acknowledged by the EEPROM. The microcontroller receives a data word, it responds with an

microcontroller must then generate another start con- acknowledgment. As long as the EEPROM receives an

dition. The microcontroller now initiates a current ad- acknowledgment, it will continue to increment the data

dress read by sending a device address with the word address and serially clock out sequential data

read/write select bit high. The EEPROM acknowl- words. When the memory address limit is reached, the

edges the device address and serially clocks out the data word address will roll over and the sequential read

data word. The microcontroller should respond with a continues. The sequential read operation is terminated

²no ACK² signal (high) followed by a stop condition. when the microcontroller responds with a ²no ACK² sig-

(refer to Random read timing). nal (high) followed by a stop condition.

R a n d o m R e a d T im in g

D e v ic e a d d r e s s W o rd a d d re s s D e v ic e a d d r e s s D A T A

S to p

S D A S A 2 A 1 A 0 S P

A C K A C K A C K N o A C K

S ta rt S ta rt

S e q u e n tia l R e a d T im in g

D e v ic e a d d r e s s D A T A n D A T A n + 1 D A T A n + x

S to p

S D A S P

S ta rt A C K A C K N o A C K

Timing Diagrams

tf tr tH IG H

tL O W

S C L

tS U :S T A tH D :S T A tS U :D A T tS U :S T O

tH D :D A T

S D A tS P

tB U F

tA A

S D A

V a lid V a lid

O U T

S C L

S D A 8 th b it A C K

W o rd n tW R

S to p S ta rt

C o n d itio n C o n d itio n

Note: The write cycle time tWR is the time from a valid stop condition of a write sequence to the end of the valid start

condition of sequential command.

Rev. 1.30 6 June 27, 2007

HT24LC02

Package Information

8-pin DIP (300mil) Outline Dimensions

8 5

B

1 4

D

= I

E G

Dimensions in mil

Symbol

Min. Nom. Max.

A 355 ¾ 375

B 240 ¾ 260

C 125 ¾ 135

D 125 ¾ 145

E 16 ¾ 20

F 50 ¾ 70

G ¾ 100 ¾

H 295 ¾ 315

I 335 ¾ 375

a 0° ¾ 15°

Rev. 1.30 7 June 27, 2007

HT24LC02

8-pin SOP (150mil) Outline Dimensions

8 5

A B

1 4

C '

G

D H

E F =

Dimensions in mil

Symbol

Min. Nom. Max.

A 228 ¾ 244

B 149 ¾ 157

C 14 ¾ 20

C¢ 189 ¾ 197

D 53 ¾ 69

E ¾ 50 ¾

F 4 ¾ 10

G 22 ¾ 28

H 4 ¾ 12

a 0° ¾ 10°

Rev. 1.30 8 June 27, 2007

HT24LC02

8-pin TSSOP Outline Dimensions

8 5

E 1

1 4

E

D

L

A A 2

C G

e B A 1 L 1

R 0 .1 0 y

(4 C O R N E R S )

Dimensions in mm

Symbol

Min. Nom. Max.

A 1.05 ¾ 1.20

A1 0.05 ¾ 0.15

A2 0.95 ¾ 1.05

B ¾ 0.25 ¾

C 0.11 ¾ 0.15

D 2.90 ¾ 3.10

E 6.20 ¾ 6.60

E1 4.30 ¾ 4.50

e ¾ 0.65 ¾

L 0.50 ¾ 0.70

L1 0.90 ¾ 1.10

y ¾ ¾ 0.10

q 0° ¾ 8°

Rev. 1.30 9 June 27, 2007

HT24LC02

Product Tape and Reel Specifications

Reel Dimensions

D

T 2

A B C

T 1

SOP 8N

Symbol Description Dimensions in mm

A Reel Outer Diameter 330±1.0

B Reel Inner Diameter 62±1.5

13.0+0.5

C Spindle Hole Diameter

-0.2

D Key Slit Width 2.0±0.15

12.8+0.3

T1 Space Between Flange

-0.2

T2 Reel Thickness 18.2±0.2

TSSOP 8L

Symbol Description Dimensions in mm

A Reel Outer Diameter 330±1.0

B Reel Inner Diameter 62±1.5

13.0+0.5

C Spindle Hole Diameter

-0.2

D Key Slit Width 2.0±0.5

12.8+0.3

T1 Space Between Flange

-0.2

T2 Reel Thickness 18.2±0.2

Rev. 1.30 10 June 27, 2007

HT24LC02

Carrier Tape Dimensions

P 0 P 1

D t

F

W

B 0

C

D 1 P

K 0

A 0

SOP 8N

Symbol Description Dimensions in mm

12.0+0.3

W Carrier Tape Width

-0.1

P Cavity Pitch 8.0±0.1

E Perforation Position 1.75±0.1

F Cavity to Perforation (Width Direction) 5.5±0.1

D Perforation Diameter 1.55±0.1

D1 Cavity Hole Diameter 1.5+0.25

P0 Perforation Pitch 4.0±0.1

P1 Cavity to Perforation (Length Direction) 2.0±0.1

A0 Cavity Length 6.4±0.1

B0 Cavity Width 5.20±0.1

K0 Cavity Depth 2.1±0.1

t Carrier Tape Thickness 0.3±0.05

C Cover Tape Width 9.3

TSSOP 8L

Symbol Description Dimensions in mm

12.0+0.3

W Carrier Tape Width

-0.1

P Cavity Pitch 8.0±0.1

E Perforation Position 1.75±0.1

F Cavity to Perforation (Width Direction) 5.5±0.5

D Perforation Diameter 1.5+0.1

D1 Cavity Hole Diameter 1.5+0.1

P0 Perforation Pitch 4.0±0.1

P1 Cavity to Perforation (Length Direction) 2.0±0.1

A0 Cavity Length 7.0±0.1

B0 Cavity Width 3.6±0.1

K0 Cavity Depth 1.6±0.1

t Carrier Tape Thickness 0.3±0.013

C Cover Tape Width 9.3

Rev. 1.30 11 June 27, 2007

HT24LC02

Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science Park, Hsinchu, Taiwan

Tel: 886-3-563-1999

Fax: 886-3-563-1189

http://www.holtek.com.tw

Holtek Semiconductor Inc. (Taipei Sales Office)

4F-2, No. 3-2, YuanQu St., Nankang Software Park, Taipei 115, Taiwan

Tel: 886-2-2655-7070

Fax: 886-2-2655-7373

Fax: 886-2-2655-7383 (International sales hotline)

Holtek Semiconductor Inc. (Shanghai Sales Office)

7th Floor, Building 2, No.889, Yi Shan Rd., Shanghai, China 200233

Tel: 86-21-6485-5560

Fax: 86-21-6485-0313

http://www.holtek.com.cn

Holtek Semiconductor Inc. (Shenzhen Sales Office)

5/F, Unit A, Productivity Building, Cross of Science M 3rd Road and Gaoxin M 2nd Road, Science Park, Nanshan District,

Shenzhen, China 518057

Tel: 86-755-8616-9908, 86-755-8616-9308

Fax: 86-755-8616-9722

Holtek Semiconductor Inc. (Beijing Sales Office)

Suite 1721, Jinyu Tower, A129 West Xuan Wu Men Street, Xicheng District, Beijing, China 100031

Tel: 86-10-6641-0030, 86-10-6641-7751, 86-10-6641-7752

Fax: 86-10-6641-0125

Holtek Semiconductor Inc. (Chengdu Sales Office)

709, Building 3, Champagne Plaza, No.97 Dongda Street, Chengdu, Sichuan, China 610016

Tel: 86-28-6653-6590

Fax: 86-28-6653-6591

Holtek Semiconductor (USA), Inc. (North America Sales Office)

46729 Fremont Blvd., Fremont, CA 94538

Tel: 1-510-252-9880

Fax: 1-510-252-9885

http://www.holtek.com

Copyright Ó 2007 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek as-

sumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used

solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable

without further modification, nor recommends the use of its products for application that may present a risk to human life

due to malfunction or otherwise. Holtek¢s products are not authorized for use as critical components in life support devices

or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information,

please visit our web site at http://www.holtek.com.tw.

Rev. 1.30 12 June 27, 2007

You might also like

- Dart by Example - Sample ChapterDocument27 pagesDart by Example - Sample ChapterPackt PublishingNo ratings yet

- The Elements of C++ Style PDFDocument188 pagesThe Elements of C++ Style PDFfikretgulsoyNo ratings yet

- HT24LC02: CMOS 2K 2-Wire Serial EEPROMDocument12 pagesHT24LC02: CMOS 2K 2-Wire Serial EEPROMvetchboyNo ratings yet

- HT24LC02: 2K 2-Wire CMOS Serial EEPROMDocument8 pagesHT24LC02: 2K 2-Wire CMOS Serial EEPROMvetchboyNo ratings yet

- 2-Wire Serial EEPROM: FeaturesDocument19 pages2-Wire Serial EEPROM: FeaturesAgustin AndrokaitesNo ratings yet

- 24C1 Memoria Eeprom SankeyDocument11 pages24C1 Memoria Eeprom Sankeyjavier venturaNo ratings yet

- 24C32Document12 pages24C32SilviuCocoloșNo ratings yet

- 24aa512 Mic PDFDocument28 pages24aa512 Mic PDFkt2018No ratings yet

- 24C01SCDocument12 pages24C01SCaprilila5555No ratings yet

- VHC32Document7 pagesVHC32quangNo ratings yet

- 24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMDocument34 pages24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMKhalid BenaribaNo ratings yet

- 24AA02/24LC02B: 2KI C Serial EEPROMDocument32 pages24AA02/24LC02B: 2KI C Serial EEPROMhanifNo ratings yet

- Atmel 4 Wire Serial EepromsDocument13 pagesAtmel 4 Wire Serial Eeproms轮摇No ratings yet

- 2-Wire Serial Eeprom: FeaturesDocument20 pages2-Wire Serial Eeprom: FeaturesAgustin AndrokaitesNo ratings yet

- 24FC1025 EepromDocument28 pages24FC1025 EepromAnirudh ReddyNo ratings yet

- 32K 5.0V I C Serial EEPROM: Features Package TypesDocument12 pages32K 5.0V I C Serial EEPROM: Features Package Typesinsomnium86No ratings yet

- 74VHC244 Octal Buffer/Line Driver With 3-STATE Outputs: General Description FeaturesDocument8 pages74VHC244 Octal Buffer/Line Driver With 3-STATE Outputs: General Description FeaturesSero StivNo ratings yet

- 24aa515, 24LC515, 24FC515Document20 pages24aa515, 24LC515, 24FC515dorudNo ratings yet

- 2-Wire Serial Eeprom: FeaturesDocument11 pages2-Wire Serial Eeprom: FeaturesRomel Ranin CalangNo ratings yet

- 2-Wire Serial Eeprom: FeaturesDocument10 pages2-Wire Serial Eeprom: FeaturesPablo Diego Cecere CasadoNo ratings yet

- A. Atmel ProductsDocument16 pagesA. Atmel ProductsJuan Jose MendozaNo ratings yet

- 74VHC244 Octal Buffer/Line Driver With 3-STATE Outputs: General Description FeaturesDocument8 pages74VHC244 Octal Buffer/Line Driver With 3-STATE Outputs: General Description FeaturesrzvNo ratings yet

- 24Lc08B/16B Modules: 8K/16K I C Serial Eeproms in Iso MicromodulesDocument12 pages24Lc08B/16B Modules: 8K/16K I C Serial Eeproms in Iso MicromodulesarminNo ratings yet

- 24AA64/24LC64/24FC64: 64K I C Serial EEPROMDocument28 pages24AA64/24LC64/24FC64: 64K I C Serial EEPROMJuan Luis Pineda GonzálezNo ratings yet

- 1K 5.0V I C™ Serial EEPROM: Features: DescriptionDocument36 pages1K 5.0V I C™ Serial EEPROM: Features: DescriptionDanna PerezNo ratings yet

- Datasheet PDFDocument26 pagesDatasheet PDFNicoli LourençoNo ratings yet

- 2-Wire Serial Eeproms: FeaturesDocument16 pages2-Wire Serial Eeproms: FeaturesTuan Pham AnhNo ratings yet

- 2-Wire Serial EEPROM: FeaturesDocument21 pages2-Wire Serial EEPROM: Featuresuwbg.ycion44No ratings yet

- Two-Wire Serial EEPROM 2K: Wuhan Eshine Technology Co., LTDDocument20 pagesTwo-Wire Serial EEPROM 2K: Wuhan Eshine Technology Co., LTDgrufNo ratings yet

- Write Protect Pin For Hardware Data ProtectionDocument16 pagesWrite Protect Pin For Hardware Data Protectionisc44242100% (2)

- 24C256Document14 pages24C256Việt Thảo TrầnNo ratings yet

- 24AA1025/24LC1025/24FC1025: 1024K I C Serial EEPROMDocument29 pages24AA1025/24LC1025/24FC1025: 1024K I C Serial EEPROMSudhagarSubbiyanNo ratings yet

- At 25080Document21 pagesAt 25080sabNo ratings yet

- Atmel 24c02 PDFDocument30 pagesAtmel 24c02 PDFMAX GNo ratings yet

- SPI Serial Eeproms: FeaturesDocument15 pagesSPI Serial Eeproms: FeaturesMarcus SilvaNo ratings yet

- Two-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ADocument21 pagesTwo-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64Anordio2No ratings yet

- At25f512a 844895Document19 pagesAt25f512a 844895mirage0706No ratings yet

- 24l1026i Memoria EEPROM 1024kDocument28 pages24l1026i Memoria EEPROM 1024kMarta_d_eNo ratings yet

- 2-Wire Serial EEPROM Smart Card Module: FeaturesDocument12 pages2-Wire Serial EEPROM Smart Card Module: FeaturesMaikol DominguezNo ratings yet

- Two-Wire Serial Eeprom: FeaturesDocument19 pagesTwo-Wire Serial Eeprom: FeaturesVikrant SharmaNo ratings yet

- 74VHC541 Octal Buffer/Line Driver With 3-STATE Outputs: General DescriptionDocument7 pages74VHC541 Octal Buffer/Line Driver With 3-STATE Outputs: General Descriptionprdp_666No ratings yet

- 1K/2K 5.0V I C Serial EEPROM: Obsolete DeviceDocument10 pages1K/2K 5.0V I C Serial EEPROM: Obsolete DevicesixtodeathNo ratings yet

- M48Z02 M48Z12: 16 Kbit (2Kb X 8) ZEROPOWER SramDocument12 pagesM48Z02 M48Z12: 16 Kbit (2Kb X 8) ZEROPOWER SramUzair SajidNo ratings yet

- Features: Two-Wire Serial Electrically Erasable and Programmable Read-Only MemoryDocument23 pagesFeatures: Two-Wire Serial Electrically Erasable and Programmable Read-Only MemoryLi JamesNo ratings yet

- I C-Compatible Serial E Prom: General DescriptionDocument20 pagesI C-Compatible Serial E Prom: General Descriptionsajjad_pirzadaNo ratings yet

- 24AA1025 24LC1025 24FC1025 1024 Kbit I2C Serial EE-2853738Document32 pages24AA1025 24LC1025 24FC1025 1024 Kbit I2C Serial EE-2853738İbrahim DemircioğluNo ratings yet

- SPI Serial Memory: FeaturesDocument17 pagesSPI Serial Memory: Featuresyuni supriatinNo ratings yet

- SLC 7015Document1 pageSLC 7015Дмитрий КопышевNo ratings yet

- Atmlh034 Atmel PDFDocument12 pagesAtmlh034 Atmel PDFAlexander RinconNo ratings yet

- Datasheet 7404 NOTDocument9 pagesDatasheet 7404 NOTLucianamxsNo ratings yet

- At24c02a 04a 08aDocument16 pagesAt24c02a 04a 08aretno.endah ekowatiNo ratings yet

- 74VHC132Document8 pages74VHC132Anonymous oEoCVNhu7HNo ratings yet

- 2-Wire Serial EEPROM: FeaturesDocument22 pages2-Wire Serial EEPROM: FeaturesNikolay MikolkinNo ratings yet

- CAT24C32: 32-Kb I C Cmos Serial Eeprom Features Device DescriptionDocument18 pagesCAT24C32: 32-Kb I C Cmos Serial Eeprom Features Device DescriptionPierpaolo GustinNo ratings yet

- Triple Schmitt Inverter: Order CodesDocument7 pagesTriple Schmitt Inverter: Order CodeselieNo ratings yet

- AT24C16BDocument20 pagesAT24C16Blucio perezNo ratings yet

- 24AA02/24LC02B: 2KI C Serial EEPROMDocument24 pages24AA02/24LC02B: 2KI C Serial EEPROMMayk OzNo ratings yet

- Three-Wire Serial EEPROM: 1. FeaturesDocument17 pagesThree-Wire Serial EEPROM: 1. FeatureskppsadiNo ratings yet

- 24c1024 Ic DatasheetDocument20 pages24c1024 Ic DatasheetVikas AttardeNo ratings yet

- 24C02BN Su18Document26 pages24C02BN Su18Dwp BhaskaranNo ratings yet

- DOC001021684Document21 pagesDOC001021684Dmitriy SavelyevNo ratings yet

- Corner CubeDocument6 pagesCorner CubehcarcaroNo ratings yet

- M24C16-x M24C08-x M24C04-x M24C02-x M24C01-x: 16 Kbit, 8 Kbit, 4 Kbit, 2 Kbit and 1 Kbit Serial I C Bus EEPROMDocument38 pagesM24C16-x M24C08-x M24C04-x M24C02-x M24C01-x: 16 Kbit, 8 Kbit, 4 Kbit, 2 Kbit and 1 Kbit Serial I C Bus EEPROMhcarcaroNo ratings yet

- 16K I C Serial EEPROM Extended (M) Operating Temperatures: Number V Range Max. Clock Frequency Temp. RangesDocument22 pages16K I C Serial EEPROM Extended (M) Operating Temperatures: Number V Range Max. Clock Frequency Temp. RangeshcarcaroNo ratings yet

- PBC-3800 3.5x3.5x13.5 Paperboard BoxDocument3 pagesPBC-3800 3.5x3.5x13.5 Paperboard BoxhcarcaroNo ratings yet

- DL205 User Manual Vol1 PDFDocument415 pagesDL205 User Manual Vol1 PDFLoloy NorybNo ratings yet

- Image Guide of OpenstackDocument101 pagesImage Guide of OpenstackAbdou MfopaNo ratings yet

- VyOS CommandDocument293 pagesVyOS CommandNguyễn Quốc BảoNo ratings yet

- Huawei Server Portfolio-V5-EnglishDocument1 pageHuawei Server Portfolio-V5-EnglishAdhu AdharshNo ratings yet

- AWSDevDay - Five Design Patterns To Build More Resilient ApplicationsDocument29 pagesAWSDevDay - Five Design Patterns To Build More Resilient ApplicationsВладислав ФранчукNo ratings yet

- VLSI Lab ManualDocument77 pagesVLSI Lab ManualSriramNo ratings yet

- Mx341 Automatic Voltage Regulator (Avr) : Specification, Installation and AdjustmentsDocument4 pagesMx341 Automatic Voltage Regulator (Avr) : Specification, Installation and AdjustmentsJuanPabloCastilloRojasNo ratings yet

- TSX Input ModuleDocument25 pagesTSX Input ModuleSahidahHaryantoNo ratings yet

- Beyond The 12-Factor App PivotalDocument72 pagesBeyond The 12-Factor App Pivotal백예균No ratings yet

- AnilKumar ProfileDocument4 pagesAnilKumar Profileankul kumarNo ratings yet

- Computer Marking Scheme f2Document7 pagesComputer Marking Scheme f2Duke GetumaNo ratings yet

- Series Fast Operation Manual (7.0) 1Document29 pagesSeries Fast Operation Manual (7.0) 1danielNo ratings yet

- Alcatel 1660SM OperationDocument71 pagesAlcatel 1660SM OperationSukri Ansar100% (1)

- Naukri VivekanandKumar (13y 0m)Document6 pagesNaukri VivekanandKumar (13y 0m)ashu.mahendruNo ratings yet

- Microprocessor: Motorola 6800Document19 pagesMicroprocessor: Motorola 6800Anupam SinghNo ratings yet

- Multimedia Devices: in This Chapter You Will LearnDocument69 pagesMultimedia Devices: in This Chapter You Will LearnJakim LopezNo ratings yet

- Proforma InvoiceDocument1 pageProforma InvoiceAppliance Zone Ghana limitedNo ratings yet

- Use The Standard ProgramDocument23 pagesUse The Standard ProgramsudhakpNo ratings yet

- Csc505 Computer-Architecture-And-Organization TH 1.10 Ac26Document2 pagesCsc505 Computer-Architecture-And-Organization TH 1.10 Ac26netgalaxy2010No ratings yet

- Start Up MacrosDocument4 pagesStart Up MacrosFrancesco TrivelliNo ratings yet

- Saep 150Document13 pagesSaep 150Abdullah100% (1)

- Communication Engineering 6Document8 pagesCommunication Engineering 6Azza24 Azize24No ratings yet

- Typical Wiring Diagram: Function ActionDocument2 pagesTypical Wiring Diagram: Function ActionMH..2023No ratings yet

- C Amit Siemens GE ComparisonsDocument13 pagesC Amit Siemens GE ComparisonsNaveen KumarNo ratings yet

- DVR Fast Operation User Manual V3.1Document107 pagesDVR Fast Operation User Manual V3.1akhilNo ratings yet

- Snake Game DocumentationDocument13 pagesSnake Game DocumentationBhavya Pratap singh 076No ratings yet

- VHDL Processes: Cwru Eecs 318Document24 pagesVHDL Processes: Cwru Eecs 318KarThikNo ratings yet

- Practice of Network Administation Setting 2Document4 pagesPractice of Network Administation Setting 2Ntirnyuy LeenaNo ratings yet