Professional Documents

Culture Documents

TEA1795T: 1. General Description

TEA1795T: 1. General Description

Uploaded by

Esau DiazOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

TEA1795T: 1. General Description

TEA1795T: 1. General Description

Uploaded by

Esau DiazCopyright:

Available Formats

TEA1795T

GreenChip synchronous rectifier controller

Rev. 1 — 4 November 2010 Product data sheet

1. General description

The TEA1795T is a member of the new generation of Synchronous Rectifier (SR)

controller ICs for switched mode power supplies. Its high level of integration enables the

design of a cost-effective power supply with a minimum number of external components.

The TEA1795T is a dedicated controller IC for synchronous rectification on the secondary

side of resonant converters. It has two driver stages for driving the SR MOSFETs, which

are rectifying the outputs of the central tap secondary transformer windings.

The two gate driver stages have their own sensing inputs and operate independently of

each other.

The TEA1795T is fabricated in a Silicon On Insulator (SOI) process.

2. Features and benefits

2.1 Distinctive features

Accurate synchronous rectification functionality

Wide supply voltage range (8.5 V to 38 V)

Separate sense inputs for sensing the drain and source voltage of each SR MOSFET

High level of integration, resulting in a minimum external component count

High driver output voltage of 10 V to drive all MOSFET brands to the lowest RDSon

2.2 Green features

Low current consumption

High system efficiency from no load to full load

2.3 Protection features

UnderVoltage Protection (UVP)

3. Applications

The TEA1795T is intended for resonant power supplies. In such applications, it can drive

two external synchronous rectifier MOSFETs which replace diodes for the rectification of

the voltages on the two secondary windings of the transformer. It can be used in

applications such as:

Adapters

ATX power supplies

Downloaded from Arrow.com.

NXP Semiconductors TEA1795T

GreenChip synchronous rectifier controller

Server power supplies

LCD television

Plasma television

4. Ordering information

Table 1. Ordering information

Type number Package

Name Description Version

TEA1795T/N1 SO8 plastic small outline package; 8 leads; body width 3.9 mm SOT96-1

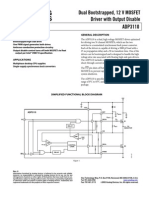

5. Block diagram

VCC

SUPPLY

UVLO AND

BIAS

control A

TIMER

4 0.4 μs R Q TIMER

DSA 3

0.5 μs GDA

& S Q

DRIVER

−25 mV −12 mV −220 mV

1

SSA

TEA1795T

control B

TIMER

5 0.4 μs R Q TIMER

DSB 6

0.5 μs GDB

& S Q

DRIVER

−25 mV −12 mV −220 mV

8

SSB

GND 001aal796

Fig 1. Block diagram

TEA1795T All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 1 — 4 November 2010 2 of 14

Downloaded from Arrow.com.

NXP Semiconductors TEA1795T

GreenChip synchronous rectifier controller

6. Pinning information

6.1 Pinning

SSA 1 8 SSB

GND 2 7 VCC

TEA1795T

GDA 3 6 GDB

DSA 4 5 DSB

014aaa976

Fig 2. Pin configuration

6.2 Pin description

Table 2. Pin description

Symbol Pin Description

SSA 1 source sense input MOSFET A

GND 2 ground

GDA 3 gate driver output MOSFET A

DSA 4 drain sense input for synchronous timing MOSFET A

DSB 5 drain sense input for synchronous timing MOSFET B

GDB 6 gate driver output MOSFET B

VCC 7 supply voltage

SSB 8 source sense input MOSFET B

7. Functional description

7.1 Introduction

The TEA1795T is a controller for synchronous rectification to be used in resonant

applications. It can drive two synchronous rectifier MOSFETs on the secondary side of the

central tap transformer winding. A typical configuration is shown in Figure 3.

TEA1795T All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 1 — 4 November 2010 3 of 14

Downloaded from Arrow.com.

NXP Semiconductors TEA1795T

GreenChip synchronous rectifier controller

Vin

Qprim1

PRIMARY CHB

TR

SIDE

Qprim2

CONTROLLER

Vout

Cout

RDRNSENSE1 RDRNSENSE2

Qsec1 IC1 VCC Qsec2

DSA DSB

GDA GDB

TEA1795T

SSA SSB

GND

001aal797

Fig 3. TEA1795T: typical configuration

7.2 Start-up and UnderVoltage LockOut (UVLO)

The IC leaves the UVLO state and activates the synchronous rectifier circuitry when the

voltage on the VCC pin is above Vstartup (8.5 V typical). When the voltage drops below

8.0 V (typical), the UVLO state is reentered and the SR MOSFET gate driver outputs are

actively kept low.

7.3 Supply management

All (internal) reference voltages are derived from a temperature compensated, on-chip

band gap circuit.

7.4 Synchronous rectification (DSA, SSA, DSB and SSB pins)

The voltages present between the drain and source terminals of the SR MOSFETs are

used to derive the timing for the gate drive signal. The IC senses the voltage difference

between the drain sense (pins DSA and DSB) and the source sense (pins SSA and SSB)

connections. When this voltage difference is lower than Vact(drv) (−220 mV typical), the

corresponding gate driver output voltage is driven high and the external SR MOSFET is

switched on.

When the external SR MOSFET is switched on, the input signals on the drain sense pins

and source sense pins are ignored during the minimum synchronous rectification active

time (tact(sr)(min), 520 ns typical). This minimizes false switch-off due to the sensing of high

frequency ringing signals at the start of the conduction phase.

Once this minimum synchronous rectification active time has ended, the IC monitors the

difference between the drain sense inputs and the source sense inputs. When the

difference is higher than Vreg(drv) (−25 mV typical), the gate driver output voltage is

regulated to maintain this −25 mV difference between the drain sense pins and the source

sense pins. As a result, the SR MOSFET can be switched off quickly when the current

through the external SR MOSFET reaches zero.

TEA1795T All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 1 — 4 November 2010 4 of 14

Downloaded from Arrow.com.

NXP Semiconductors TEA1795T

GreenChip synchronous rectifier controller

The zero current is detected by sensing a Vdeact(drv) (−12 mV typical) difference between

the drain sense pins and the source sense pins (see Figure 4). A synchronous

rectification off-timer (toff(sr)(min), 400 ns typical) is started and the next switching cycle can

only be started when the synchronous rectification off-timer has finished.

secondary

current 0A

drain sense-

source sense 0V

voltage

Vdeact(drv)

Vreg(drv)

Vact(drv)

gate driver 0V

blanking

windows t

tact(sr)(min) toff(sr)(min)

001aal798

Fig 4. Synchronous rectification signals

7.5 Gate driver (GDA and GDB pins)

The gate driver circuit to the gate of the external SR MOSFET has a source capability of

typically 400 mA and a sink capability of typically 2.7 A. This allows fast turn-on and

turn-off of the external SR MOSFET for efficient operation. The source stage is coupled to

the timer (see Figure 1). When the timer has finished, the source capability is reduced to a

small current (4 mA typical) capable of keeping the driver output voltage at its level.

The output voltage of the driver is limited to 10 V (typical). This high output voltage drives

all MOSFET brands to the minimum on-state resistance.

During start-up conditions (VCC < Vstartup) and UVLO the driver output voltage is actively

pulled low.

7.6 Source sense (SSA and SSB pins)

The IC is equipped with additional source sense pins (SSA and SSB). These pins are

used for the measurement of the drain-to-source voltage of the external SR MOSFET.

This drain-to-source voltage determines the timing of the gate driver. The source sense

input should be connected as close as possible to the source pin of the external

SR MOSFET to minimize timing errors, caused by voltage difference on PCB tracks, due

to parasitic inductance in combination with large dI/dt values.

TEA1795T All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 1 — 4 November 2010 5 of 14

Downloaded from Arrow.com.

NXP Semiconductors TEA1795T

GreenChip synchronous rectifier controller

8. Limiting values

Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). All voltages are measured

with respect to ground (pin 2); positive currents flow into the chip. Voltage ratings are valid provided

other ratings are not violated; current ratings are valid provided the other ratings are not violated.

Symbol Parameter Conditions Min Max Unit

Voltages

VCC supply voltage continuous −0.4 +38 V

Vsense(D)A drain sense voltage A continuous - 120 V

Vsense(D)B drain sense voltage B continuous - 120 V

Currents

Idrv(G)A gate driver current A δ < 10 % −0.8 +3.0 A

Idrv(G)B gate driver current B δ < 10 % −0.8 +3.0 A

II(DSA) input current on pin DSA −3 - mA

II(DSB) input current on pin DSB −3 - mA

II(SSA) input current on pin SSA −1 +1 mA

II(SSB) input current on pin SSB −1 +1 mA

General

Ptot total power dissipation Tamb < 80 °C - 0.45 W

Tstg storage temperature −55 +150 °C

Tj junction temperature −40 +150 °C

ElectroStatic Discharge voltage (ESD)

VESD electrostatic discharge class 2

voltage human body [1] - 2000 V

model

machine model [2] - 200 V

charged device - 500 V

model

[1] Equivalent to discharging a 100 pF capacitor through a 1.5 kΩ series resistor.

[2] Equivalent to discharging a 200 pF capacitor through a 0.75 μH coil and a 10 Ω resistor.

9. Thermal characteristics

Table 4. Thermal characteristics

Symbol Parameter Conditions Typ Unit

Rth(j-a) thermal resistance from junction JEDEC test board 150 K/W

to ambient

Rth(j-c) thermal resistance from junction JEDEC test board 100 K/W

to case

TEA1795T All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 1 — 4 November 2010 6 of 14

Downloaded from Arrow.com.

NXP Semiconductors TEA1795T

GreenChip synchronous rectifier controller

10. Characteristics

Table 5. Characteristics

Tamb = 25 °C; VCC = 20 V; all voltages are measured with respect to ground (pin 2); currents are positive when flowing into

the IC; unless otherwise specified.

Symbol Parameter Conditions Min Typ Max Unit

Supply voltage management (pin VCC)

Vstartup start-up voltage 8.2 8.5 8.8 V

Vhys hysteresis voltage [1] - 0.5 - V

ICC(oper) operating supply current VCC = 8 V (VCC < Vstartup) - 0.35 - mA

fsw = 200 kHz; - 1.85 - mA

no load on pins GDA and GDB

Synchronous rectification sense input (pins DSA/SSA and pins DSB/SSB)

Vact(drv) driver activation voltage Vsense(S)A = 0 V; Vsense(S)B = 0 V −260 −220 −180 mV

Vreg(drv) driver regulation voltage Vsense(S)A = 0 V; Vsense(S)B = 0 V −33 −25 −17 mV

Vdeact(drv) driver deactivation voltage Vsense(S)A = 0 V; Vsense(S)B = 0 V [2] - −12 - mV

VI(cm) common-mode input voltage pins SSA and SSB −0.7 - +0.7 V

td(act)(drv) driver activation delay time Vsense(S)A = 0 V; Vsense(S)B = 0 V; - 100 - ns

Vsense(D)A = falling from +0.5 V to −0.5 V;

Vsense(D)B = falling from +0.5 V to −0.5 V

td(deact)(drv) driver deactivation delay Vsense(S)A = 0 V; Vsense(S)B = 0 V; - 35 - ns

time Vsense(D)A = rising from −0.35 V to +0.5 V;

Vsense(D)B = rising from −0.35 V to +0.5 V

tact(sr)(min) minimum synchronous 415 520 625 ns

rectification active time

toff(sr)(min) minimum synchronous 310 400 490 ns

rectification off-time

Gate driver (pins GDA/GDB)

Isource source current VCC = 15 V; pins GDA/GDB = 2 V; during −0.46 −0.4 −0.34 A

minimum synchronous rectification active

time

VCC = 15 V; pins GDA/GDB = 5 V; - −4 - mA

minimum synchronous rectification active

time has ended

Isink sink current VCC = 15 V

pins GDA/GDB = 2 V 1 1.4 - A

pins GDA/GDB = 9.5 V 2.2 2.7 - A

Vo(max) maximum output voltage VCC = 15 V - 10 12 V

Switching

fsw(max) maximum switching 500 - - kHz

frequency

[1] The VCC stop voltage is Vstartup − Vhys.

[2] The Vdeact(drv) level is always above the Vreg(drv) level.

TEA1795T All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 1 — 4 November 2010 7 of 14

Downloaded from Arrow.com.

NXP Semiconductors TEA1795T

GreenChip synchronous rectifier controller

11. Application information

A switched mode power supply with the TEA1795T consists of a primary side half bridge,

a transformer, a resonant capacitor and an output stage. In the output stage

SR MOSFETs are used to obtain low conduction loss rectification. These SR MOSFETs

are controlled by the TEA1795T.

The timing for the synchronous rectifier switch is derived from the voltage difference

between the corresponding drain sense and source sense pins. The resistor in the drain

sense connection is needed to protect the TEA1795T against excessive voltages. These

resistors should typically be 1 kΩ. Higher values might impair correct timing, lower values

may not provide sufficient protection.

Special attention should be paid to the connection of the drain sense and source sense

pins. The voltages measured on these pins are used for the timing of the gate driver

output. Wrong measurement results in wrong timing. The connections to these pins

should not interfere with the power wiring. The power wiring conducts currents with high

dI/dt values. This can easily cause measurement errors resulting from induced voltages

due to parasitic inductances. The separate source sense pins make it possible to sense

the source voltage of the external MOSFETs directly, without having to use the current

carrying power ground tracks for this.

11.1 Application diagram resonant application

Vin

Qprim1

PRIMARY CHB

TR

SIDE

Qprim2

CONTROLLER

Vout

RDRNSENSE1 RDRNSENSE2 Cout

1 kΩ 1 kΩ

Qsec1 IC1 VCC Qsec2

DSA DSB

GDA GDB

TEA1795T

SSA SSB

GND

001aal799

Fig 5. Typical resonant application with TEA1795T

TEA1795T All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 1 — 4 November 2010 8 of 14

Downloaded from Arrow.com.

NXP Semiconductors TEA1795T

GreenChip synchronous rectifier controller

11.2 Application diagram multi-output flyback application

TR Vout2

Vin

Cout2

Vout1

RDRNSENSE1 RDRNSENSE2 Cout1

1 kΩ 1 kΩ

Qprim Qsec1 IC1 VCC Qsec2

DSA DSB

PRIMARY

GDA GDB

SIDE TEA1795T

CONTROLLER SSA SSB

GND

001aal800

Fig 6. Multi-output flyback application with TEA1795T

TEA1795T All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 1 — 4 November 2010 9 of 14

Downloaded from Arrow.com.

NXP Semiconductors TEA1795T

GreenChip synchronous rectifier controller

12. Package outline

SO8: plastic small outline package; 8 leads; body width 3.9 mm SOT96-1

D E A

X

y HE v M A

8 5

Q

A2

(A 3) A

A1

pin 1 index

θ

Lp

1 4 L

e w M detail X

bp

0 2.5 5 mm

scale

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

A

UNIT max. A1 A2 A3 bp c D (1) E (2) e HE L Lp Q v w y Z (1) θ

0.25 1.45 0.49 0.25 5.0 4.0 6.2 1.0 0.7 0.7

mm 1.75 0.25 1.27 1.05 0.25 0.25 0.1 o

0.10 1.25 0.36 0.19 4.8 3.8 5.8 0.4 0.6 0.3 8

o

0.010 0.057 0.019 0.0100 0.20 0.16 0.244 0.039 0.028 0.028 0

inches 0.069 0.01 0.05 0.041 0.01 0.01 0.004

0.004 0.049 0.014 0.0075 0.19 0.15 0.228 0.016 0.024 0.012

Notes

1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

2. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC JEITA PROJECTION

99-12-27

SOT96-1 076E03 MS-012

03-02-18

Fig 7. Package outline SOT096-1 (SO8)

TEA1795T All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 1 — 4 November 2010 10 of 14

Downloaded from Arrow.com.

NXP Semiconductors TEA1795T

GreenChip synchronous rectifier controller

13. Revision history

Table 6. Revision history

Document ID Release date Data sheet status Change notice Supersedes

TEA1795T v.1 20101104 Product data sheet - -

TEA1795T All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 1 — 4 November 2010 11 of 14

Downloaded from Arrow.com.

NXP Semiconductors TEA1795T

GreenChip synchronous rectifier controller

14. Legal information

14.1 Data sheet status

Document status[1][2] Product status[3] Definition

Objective [short] data sheet Development This document contains data from the objective specification for product development.

Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.

Product [short] data sheet Production This document contains the product specification.

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term ‘short data sheet’ is explained in section “Definitions”.

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status

information is available on the Internet at URL http://www.nxp.com.

14.2 Definitions malfunction of an NXP Semiconductors product can reasonably be expected

to result in personal injury, death or severe property or environmental

damage. NXP Semiconductors accepts no liability for inclusion and/or use of

Draft — The document is a draft version only. The content is still under

NXP Semiconductors products in such equipment or applications and

internal review and subject to formal approval, which may result in

therefore such inclusion and/or use is at the customer’s own risk.

modifications or additions. NXP Semiconductors does not give any

representations or warranties as to the accuracy or completeness of Applications — Applications that are described herein for any of these

information included herein and shall have no liability for the consequences of products are for illustrative purposes only. NXP Semiconductors makes no

use of such information. representation or warranty that such applications will be suitable for the

specified use without further testing or modification.

Short data sheet — A short data sheet is an extract from a full data sheet

with the same product type number(s) and title. A short data sheet is intended Customers are responsible for the design and operation of their applications

for quick reference only and should not be relied upon to contain detailed and and products using NXP Semiconductors products, and NXP Semiconductors

full information. For detailed and full information see the relevant full data accepts no liability for any assistance with applications or customer product

sheet, which is available on request via the local NXP Semiconductors sales design. It is customer’s sole responsibility to determine whether the NXP

office. In case of any inconsistency or conflict with the short data sheet, the Semiconductors product is suitable and fit for the customer’s applications and

full data sheet shall prevail. products planned, as well as for the planned application and use of

customer’s third party customer(s). Customers should provide appropriate

Product specification — The information and data provided in a Product design and operating safeguards to minimize the risks associated with their

data sheet shall define the specification of the product as agreed between applications and products.

NXP Semiconductors and its customer, unless NXP Semiconductors and

customer have explicitly agreed otherwise in writing. In no event however, NXP Semiconductors does not accept any liability related to any default,

shall an agreement be valid in which the NXP Semiconductors product is damage, costs or problem which is based on any weakness or default in the

deemed to offer functions and qualities beyond those described in the customer’s applications or products, or the application or use by customer’s

Product data sheet. third party customer(s). Customer is responsible for doing all necessary

testing for the customer’s applications and products using NXP

Semiconductors products in order to avoid a default of the applications and

14.3 Disclaimers the products or of the application or use by customer’s third party

customer(s). NXP does not accept any liability in this respect.

Limited warranty and liability — Information in this document is believed to Limiting values — Stress above one or more limiting values (as defined in

be accurate and reliable. However, NXP Semiconductors does not give any the Absolute Maximum Ratings System of IEC 60134) will cause permanent

representations or warranties, expressed or implied, as to the accuracy or damage to the device. Limiting values are stress ratings only and (proper)

completeness of such information and shall have no liability for the operation of the device at these or any other conditions above those given in

consequences of use of such information. the Recommended operating conditions section (if present) or the

Characteristics sections of this document is not warranted. Constant or

In no event shall NXP Semiconductors be liable for any indirect, incidental,

repeated exposure to limiting values will permanently and irreversibly affect

punitive, special or consequential damages (including - without limitation - lost

the quality and reliability of the device.

profits, lost savings, business interruption, costs related to the removal or

replacement of any products or rework charges) whether or not such Terms and conditions of commercial sale — NXP Semiconductors

damages are based on tort (including negligence), warranty, breach of products are sold subject to the general terms and conditions of commercial

contract or any other legal theory. sale, as published at http://www.nxp.com/profile/terms, unless otherwise

Notwithstanding any damages that customer might incur for any reason agreed in a valid written individual agreement. In case an individual

whatsoever, NXP Semiconductors’ aggregate and cumulative liability towards agreement is concluded only the terms and conditions of the respective

customer for the products described herein shall be limited in accordance agreement shall apply. NXP Semiconductors hereby expressly objects to

with the Terms and conditions of commercial sale of NXP Semiconductors. applying the customer’s general terms and conditions with regard to the

purchase of NXP Semiconductors products by customer.

Right to make changes — NXP Semiconductors reserves the right to make

changes to information published in this document, including without No offer to sell or license — Nothing in this document may be interpreted or

limitation specifications and product descriptions, at any time and without construed as an offer to sell products that is open for acceptance or the grant,

notice. This document supersedes and replaces all information supplied prior conveyance or implication of any license under any copyrights, patents or

to the publication hereof. other industrial or intellectual property rights.

Suitability for use — NXP Semiconductors products are not designed, Export control — This document as well as the item(s) described herein

authorized or warranted to be suitable for use in life support, life-critical or may be subject to export control regulations. Export might require a prior

safety-critical systems or equipment, nor in applications where failure or authorization from national authorities.

TEA1795T All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 1 — 4 November 2010 12 of 14

Downloaded from Arrow.com.

NXP Semiconductors TEA1795T

GreenChip synchronous rectifier controller

Non-automotive qualified products — Unless this data sheet expressly own risk, and (c) customer fully indemnifies NXP Semiconductors for any

states that this specific NXP Semiconductors product is automotive qualified, liability, damages or failed product claims resulting from customer design and

the product is not suitable for automotive use. It is neither qualified nor tested use of the product for automotive applications beyond NXP Semiconductors’

in accordance with automotive testing or application requirements. NXP standard warranty and NXP Semiconductors’ product specifications.

Semiconductors accepts no liability for inclusion and/or use of

non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in 14.4 Trademarks

automotive applications to automotive specifications and standards, customer

Notice: All referenced brands, product names, service names and trademarks

(a) shall use the product without NXP Semiconductors’ warranty of the

are the property of their respective owners.

product for such automotive applications, use and specifications, and (b)

whenever customer uses the product for automotive applications beyond GreenChip — is a trademark of NXP B.V.

NXP Semiconductors’ specifications such use shall be solely at customer’s

15. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

TEA1795T All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 1 — 4 November 2010 13 of 14

Downloaded from Arrow.com.

NXP Semiconductors TEA1795T

GreenChip synchronous rectifier controller

16. Contents

1 General description . . . . . . . . . . . . . . . . . . . . . . 1

2 Features and benefits . . . . . . . . . . . . . . . . . . . . 1

2.1 Distinctive features . . . . . . . . . . . . . . . . . . . . . . 1

2.2 Green features . . . . . . . . . . . . . . . . . . . . . . . . . 1

2.3 Protection features . . . . . . . . . . . . . . . . . . . . . . 1

3 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

4 Ordering information . . . . . . . . . . . . . . . . . . . . . 2

5 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 2

6 Pinning information . . . . . . . . . . . . . . . . . . . . . . 3

6.1 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

6.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 3

7 Functional description . . . . . . . . . . . . . . . . . . . 3

7.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

7.2 Start-up and UnderVoltage LockOut (UVLO) . . 4

7.3 Supply management. . . . . . . . . . . . . . . . . . . . . 4

7.4 Synchronous rectification (DSA, SSA, DSB

and SSB pins). . . . . . . . . . . . . . . . . . . . . . . . . . 4

7.5 Gate driver (GDA and GDB pins) . . . . . . . . . . . 5

7.6 Source sense (SSA and SSB pins) . . . . . . . . . 5

8 Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 6

9 Thermal characteristics . . . . . . . . . . . . . . . . . . 6

10 Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 7

11 Application information. . . . . . . . . . . . . . . . . . . 8

11.1 Application diagram resonant application . . . . . 8

11.2 Application diagram multi-output flyback

application . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

12 Package outline . . . . . . . . . . . . . . . . . . . . . . . . 10

13 Revision history . . . . . . . . . . . . . . . . . . . . . . . . 11

14 Legal information. . . . . . . . . . . . . . . . . . . . . . . 12

14.1 Data sheet status . . . . . . . . . . . . . . . . . . . . . . 12

14.2 Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

14.3 Disclaimers . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

14.4 Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . 13

15 Contact information. . . . . . . . . . . . . . . . . . . . . 13

16 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Please be aware that important notices concerning this document and the product(s)

described herein, have been included in section ‘Legal information’.

© NXP B.V. 2010. All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 4 November 2010

Document identifier: TEA1795T

Downloaded from Arrow.com.

You might also like

- Leadchip-Lc2127cb5tr C571475Document6 pagesLeadchip-Lc2127cb5tr C571475Oscar Andres Ramirez AmayaNo ratings yet

- The Design and Implementation of A SONAR PowerDocument6 pagesThe Design and Implementation of A SONAR PowerKiranNo ratings yet

- Tea1995t (Lta1716)Document18 pagesTea1995t (Lta1716)Adilson SilvérioNo ratings yet

- TEA1791AT: 1. General DescriptionDocument13 pagesTEA1791AT: 1. General DescriptionhussainArifNo ratings yet

- Diseño Output Ripple en DCDCDocument10 pagesDiseño Output Ripple en DCDCherraezjorge8No ratings yet

- AL8812Document11 pagesAL8812julio cesar calveteNo ratings yet

- Description Features: Ait Semiconductor IncDocument8 pagesDescription Features: Ait Semiconductor Incteranet tbtNo ratings yet

- TEA1733Document21 pagesTEA1733Juan SosaNo ratings yet

- STF16N65M5, Sti16n65m5 STP16N65M5, Stu16n65m5, STW16N65M5Document20 pagesSTF16N65M5, Sti16n65m5 STP16N65M5, Stu16n65m5, STW16N65M5ErkanNo ratings yet

- LM1117-N/LM1117I 800ma Low-Dropout Linear Regulator: Features DescriptionDocument33 pagesLM1117-N/LM1117I 800ma Low-Dropout Linear Regulator: Features DescriptionPravin MevadaNo ratings yet

- LM1117-N/LM1117I 800ma Low-Dropout Linear Regulator: Features DescriptionDocument32 pagesLM1117-N/LM1117I 800ma Low-Dropout Linear Regulator: Features DescriptionAndres PaezNo ratings yet

- TEA1708TDocument12 pagesTEA1708Tbisoxo3394No ratings yet

- STF16N50M2Document22 pagesSTF16N50M2Fabio de FeoNo ratings yet

- HIP6302CBDocument18 pagesHIP6302CBrjbordaNo ratings yet

- Mosfet: Powermanagement&MultimarketDocument15 pagesMosfet: Powermanagement&MultimarketMaikel Borges IglesiasNo ratings yet

- Isl 88731 ADocument24 pagesIsl 88731 AIon PetruscaNo ratings yet

- LM2672 Simple Switcher Power Converter High Efficiency 1A Step-Down Voltage Regulator With FeaturesDocument25 pagesLM2672 Simple Switcher Power Converter High Efficiency 1A Step-Down Voltage Regulator With FeaturesAdamNo ratings yet

- Stf7N60M2: N-Channel 600 V, 0.86 Typ., 5 A Mdmesh Ii Plus™ Low Q Power Mosfet in To-220Fp PackageDocument13 pagesStf7N60M2: N-Channel 600 V, 0.86 Typ., 5 A Mdmesh Ii Plus™ Low Q Power Mosfet in To-220Fp PackageElflaco FlacoNo ratings yet

- N-Channel 650 V, 0.43 Ω Typ., 9 A Mdmesh™ M5 Power Mosfets In A Dpak, D²Pak, To-220Fp And To-220 PackagesDocument30 pagesN-Channel 650 V, 0.43 Ω Typ., 9 A Mdmesh™ M5 Power Mosfets In A Dpak, D²Pak, To-220Fp And To-220 Packagesmcantraks17No ratings yet

- National Semiconductor Is Now Part of Texas InstrumentsDocument37 pagesNational Semiconductor Is Now Part of Texas InstrumentsMahde KtepNo ratings yet

- Current Mode Controller: FeaturesDocument20 pagesCurrent Mode Controller: FeaturesJune SendaydiegoNo ratings yet

- STF 15 NM 65 NDocument15 pagesSTF 15 NM 65 NErkanNo ratings yet

- LM2 670 PDFDocument23 pagesLM2 670 PDFMain UddinNo ratings yet

- LM 5574Document31 pagesLM 5574KholilNo ratings yet

- REN Isl6308 DST 20080807Document28 pagesREN Isl6308 DST 20080807DiegoTavaresNo ratings yet

- TEA1733P: 1. General DescriptionDocument22 pagesTEA1733P: 1. General DescriptionDiegoD'AmbrosioNo ratings yet

- 2.75V To 17V, 6A, 1.2Mhz, Synchronous, Ultra-Thin Power Module Description FeaturesDocument22 pages2.75V To 17V, 6A, 1.2Mhz, Synchronous, Ultra-Thin Power Module Description FeaturesEugene FlexNo ratings yet

- LM117/LM217/LM317: 1.2 V To 37 V Adjustable Voltage RegulatorsDocument25 pagesLM117/LM217/LM317: 1.2 V To 37 V Adjustable Voltage RegulatorsrubenNo ratings yet

- Lm2700 600Khz/1.25Mhz, 2.5A, Step-Up PWM DC/DC Converter: Features DescriptionDocument27 pagesLm2700 600Khz/1.25Mhz, 2.5A, Step-Up PWM DC/DC Converter: Features DescriptionAbdul RahmanNo ratings yet

- LM2596 DatasheetDocument31 pagesLM2596 DatasheetJorge Vázquez NuñoNo ratings yet

- Datasheet PDFDocument18 pagesDatasheet PDFSửa Tivi Tại NhàNo ratings yet

- General Description: Level Translating I C-Bus RepeaterDocument19 pagesGeneral Description: Level Translating I C-Bus RepeatersreekanthNo ratings yet

- REN Isl8121 DST 20060811Document26 pagesREN Isl8121 DST 20060811blackorgonNo ratings yet

- Description: HEX-Reg For Hex Attenuator DriversDocument2 pagesDescription: HEX-Reg For Hex Attenuator DriverskkaranagNo ratings yet

- ALD810026Document6 pagesALD810026Juan GaleanoNo ratings yet

- 3A, 28V, 385Khz Step-Down Converter: The Future of Analog Ic TechnologyDocument13 pages3A, 28V, 385Khz Step-Down Converter: The Future of Analog Ic TechnologyIoan TivgaNo ratings yet

- Dual Bootstrapped, 12 V MOSFET Driver With Output Disable ADP3110Document12 pagesDual Bootstrapped, 12 V MOSFET Driver With Output Disable ADP3110arttech13No ratings yet

- 8900 DsDocument14 pages8900 DsSergei OssifNo ratings yet

- FAN7382 Half-Bridge Gate Driver: Features DescriptionDocument14 pagesFAN7382 Half-Bridge Gate Driver: Features DescriptionEriflonaNo ratings yet

- AS3842Document14 pagesAS3842alex castroNo ratings yet

- DS 2857FG 02 PDFDocument12 pagesDS 2857FG 02 PDFJohan GuanchezNo ratings yet

- TEA1733LT: 1. General DescriptionDocument21 pagesTEA1733LT: 1. General DescriptionAndryNo ratings yet

- 2.4Ghz Monolithic Voltage-Controlled Oscillators: General Description FeaturesDocument6 pages2.4Ghz Monolithic Voltage-Controlled Oscillators: General Description FeaturesGerard PabloNo ratings yet

- 3 A Low Drop Positive Voltage Regulator: Adjustable and FixedDocument27 pages3 A Low Drop Positive Voltage Regulator: Adjustable and FixedTT DVNo ratings yet

- Para FontesDocument8 pagesPara FontesegmtreinamentosNo ratings yet

- M2303ADNDocument15 pagesM2303ADNffyddNo ratings yet

- TEA1620P: 1. General DescriptionDocument16 pagesTEA1620P: 1. General DescriptionJose BenavidesNo ratings yet

- Driver de Motor Paso A PasoDocument4 pagesDriver de Motor Paso A PasoRoberto GonzalesNo ratings yet

- LMV111 Operational Amplifier With Bias Network: General Description FeaturesDocument11 pagesLMV111 Operational Amplifier With Bias Network: General Description FeaturesJose Ramon ArayNo ratings yet

- Fdd8780 Mosfet Malo de Placa PC MariaDocument6 pagesFdd8780 Mosfet Malo de Placa PC MariadojiligNo ratings yet

- 1765 FDDocument20 pages1765 FDJoonki YunNo ratings yet

- Stp5Nk80Z Stp5Nk80Zfp: N-Channel 800V - 1.9 - 4.3A - To-220/To-220Fp Zener-Protected Supermesh™ Power MosfetDocument15 pagesStp5Nk80Z Stp5Nk80Zfp: N-Channel 800V - 1.9 - 4.3A - To-220/To-220Fp Zener-Protected Supermesh™ Power MosfetMarcilio AlmeidaNo ratings yet

- MOSFET P7NK80ZFP DatasheetDocument17 pagesMOSFET P7NK80ZFP DatasheetYuridia De la RosaNo ratings yet

- STB11NM80, STF11NM80 Sti11nm80, STP11NM80, STW11NM80Document22 pagesSTB11NM80, STF11NM80 Sti11nm80, STP11NM80, STW11NM80Alexandre OliveiraNo ratings yet

- STB40N60M2, STP40N60M2, STW40N60M2Document21 pagesSTB40N60M2, STP40N60M2, STW40N60M2Алексей АндрияшNo ratings yet

- Transistor 2021 Pag 3Document6 pagesTransistor 2021 Pag 3StuxnetNo ratings yet

- TL2843B Q1 etcTIDocument18 pagesTL2843B Q1 etcTIrahma jayaNo ratings yet

- ISL88731 ADocument23 pagesISL88731 ALưuVănViếtNo ratings yet

- STW19NM60NDocument14 pagesSTW19NM60NOscar TistaNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Body Diode Reverse Recovery Effects On SiC MOSFET Half-Bridge ConvertersDocument7 pagesBody Diode Reverse Recovery Effects On SiC MOSFET Half-Bridge ConvertersWilliam ManzolliNo ratings yet

- An-6076 - Design and Application Guide of Bootstrap Circuit ForDocument13 pagesAn-6076 - Design and Application Guide of Bootstrap Circuit ForwxapazmiNo ratings yet

- AbstractDocument4 pagesAbstractMohamed IbrahemNo ratings yet

- JY21LDocument5 pagesJY21Lajay sainiNo ratings yet

- A Design of A Wireless Power Receiving Unit With High Efficiency 6.78 MHZ Active Rectifier Using Shared Dlls For Magnetic Resonant A4Wp ApplicationsDocument28 pagesA Design of A Wireless Power Receiving Unit With High Efficiency 6.78 MHZ Active Rectifier Using Shared Dlls For Magnetic Resonant A4Wp Applicationsfelix_007_villedaNo ratings yet

- Igbt & Sic Gate Driver Fundamentals: Enabling The World To Do More With Less PowerDocument35 pagesIgbt & Sic Gate Driver Fundamentals: Enabling The World To Do More With Less Powersuper_facaNo ratings yet

- ISL62883 RenesasDocument37 pagesISL62883 Renesasanh_sao_dem_92No ratings yet

- Mini-LEGO CPU Voltage RegulatorDocument18 pagesMini-LEGO CPU Voltage RegulatorzzhbpainNo ratings yet

- Infineon-AN 2022 02 Pulses and Transmission Line theory-ApplicationNotes-v01 00-ENDocument45 pagesInfineon-AN 2022 02 Pulses and Transmission Line theory-ApplicationNotes-v01 00-ENCesar JakobyNo ratings yet

- STCMB 1Document59 pagesSTCMB 1Abhishek SinghNo ratings yet

- ZXGD3006E6: 40V 10A Gate Driver in Sot26 Description FeaturesDocument9 pagesZXGD3006E6: 40V 10A Gate Driver in Sot26 Description FeaturesManoel BonfimNo ratings yet

- Dual Full-Bridge MOSFET Driver With Microstepping TranslatorDocument18 pagesDual Full-Bridge MOSFET Driver With Microstepping TranslatorОлег ПрохоренкоNo ratings yet

- T - Type 1Document11 pagesT - Type 1Jhonatan Leandro Clavijo TrochesNo ratings yet

- Project1 Final Paper..solar PDFDocument47 pagesProject1 Final Paper..solar PDFsatish reddyNo ratings yet

- Design of A Driver IC IR2110 For MOSFETDocument21 pagesDesign of A Driver IC IR2110 For MOSFETAyoub RajawiNo ratings yet

- DRV8301Document40 pagesDRV8301Lu HoaNo ratings yet

- Motors - Stepper, BLDC, DCRDocument46 pagesMotors - Stepper, BLDC, DCRSaurabh Shukla100% (1)

- Infineon-AN 2306 PL88 2307 181713 Battery Powered BLDC Motor Drive Design Using The 6EDL71x1-ApplicationNotes-v01 00-ENDocument64 pagesInfineon-AN 2306 PL88 2307 181713 Battery Powered BLDC Motor Drive Design Using The 6EDL71x1-ApplicationNotes-v01 00-ENJulio Cesar Tapia ReyesNo ratings yet

- Tidue 54 BDocument71 pagesTidue 54 BCương PhạmNo ratings yet

- Dual Fast Turn-Off Intelligent Controller: Description FeaturesDocument13 pagesDual Fast Turn-Off Intelligent Controller: Description FeaturesDavid Alberto Lotero AlvarezNo ratings yet

- Description Features: Current Mode PWM ControllerDocument9 pagesDescription Features: Current Mode PWM ControllerAlex GerasimenkoNo ratings yet

- Power Supply Works With Fet Drivers, Drmos and Power Blocks For Flexible Placement Near MicroprocessorsDocument6 pagesPower Supply Works With Fet Drivers, Drmos and Power Blocks For Flexible Placement Near MicroprocessorsCSC-18F-018 Masood ChohanNo ratings yet

- ISL95836 Datasheet - Dual 3+2 PWM Controller - Intersil RenesasDocument33 pagesISL95836 Datasheet - Dual 3+2 PWM Controller - Intersil RenesasRodrigo BentoNo ratings yet

- Infineon-P-channel MOSFETs For Switching Applications selection-AN-v01 00-ENDocument10 pagesInfineon-P-channel MOSFETs For Switching Applications selection-AN-v01 00-ENFarmer 陳宏銘No ratings yet

- Caddyt Arc 150i Caddyt Tig 150i Origot Tig 150i: Service ManualDocument66 pagesCaddyt Arc 150i Caddyt Tig 150i Origot Tig 150i: Service Manualr_cristiNo ratings yet

- Development of A Step-Up Converter For A PV System: (Elec5510 - Practical Laboratory Session 1)Document23 pagesDevelopment of A Step-Up Converter For A PV System: (Elec5510 - Practical Laboratory Session 1)oopeoluwa_1No ratings yet

- Every Switch Needs A Driver: Gate Driver Application MatrixDocument10 pagesEvery Switch Needs A Driver: Gate Driver Application MatrixGGNo ratings yet

- PCIM Europe 2024 Preliminary Conference ProgramDocument48 pagesPCIM Europe 2024 Preliminary Conference Programankita.kaleNo ratings yet

- Fast Turn-Off Intelligent Rectifier With No Need For Auxiliary Winding Description FeaturesDocument14 pagesFast Turn-Off Intelligent Rectifier With No Need For Auxiliary Winding Description FeaturesKwun Hok ChongNo ratings yet