Professional Documents

Culture Documents

Operating Systems Fundamentals: Roadmap

Operating Systems Fundamentals: Roadmap

Uploaded by

Bigu Marius AlinOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Operating Systems Fundamentals: Roadmap

Operating Systems Fundamentals: Roadmap

Uploaded by

Bigu Marius AlinCopyright:

Available Formats

Karl O'Connell evSD1 - 2018

Operating

Systems

Fundamentals

Lecture: Computer System Overview

Karl O’Connell

Roadmap

– Basic Elements

– Processor Registers

– Instruction Execution

– Interrupts

– The Memory Hierarchy

– Cache Memory

– I/O Communication Techniques

Cork Institute of Technology 1

Karl O'Connell evSD1 - 2018

Operating System

• Exploits the hardware resources of one or

more processors

• Provides a set of services to system users

• Manages secondary memory and I/O

devices

A Computer’s

Basic Elements

• Processor

• Main Memory

• I/O Modules

• System Bus

Cork Institute of Technology 2

Karl O'Connell evSD1 - 2018

Processor

• Controls operation, performs data

processing

• Two internal registers

– Memory address resister (MAR)

– Memory buffer register (MBR)

• I/O address register

• I/O buffer register

Main Memory

• Volatile

– Data is typically lost when power is removed

• Referred to as real memory or primary

memory

• Consists of a set of locations defined by

sequentially numbers addresses

– Containing either data or instructions

Cork Institute of Technology 3

Karl O'Connell evSD1 - 2018

I/O Modules

• Moves data between the computer and the

external environment such as:

– Storage (e.g. hard drive)

– Communications equipment

– Terminals

• Specified by an I/O Address Register

– (I/OAR)

System Bus

• Communication among processors, main

memory, and I/O modules

Cork Institute of Technology 4

Karl O'Connell evSD1 - 2018

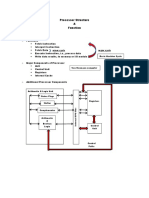

Top-Level View

Roadmap

– Basic Elements

– Processor Registers

– Instruction Execution

– Interrupts

– The Memory Hierarchy

– Cache Memory

– I/O Communication Techniques

Cork Institute of Technology 5

Karl O'Connell evSD1 - 2018

Processor Registers

• Faster and smaller than main memory

• User-visible registers

– Enable programmer to minimize main

memory references by optimizing register use

• Control and status registers

– Used by processor to control operating of the

processor

– Used by privileged OS routines to control the

execution of programs

User-Visible Registers

• May be referenced by machine language

– Available to all programs – application

programs and system programs

• Types of registers typically available are:

– data,

– address,

– condition code registers.

Cork Institute of Technology 6

Karl O'Connell evSD1 - 2018

Data and

Address Registers

• Data

– Often general purpose

– But some restrictions may apply

• Address

– Index Register

– Segment pointer

– Stack pointer

Control and

Status Registers

• Program counter (PC)

– Contains the address of an instruction to be

fetched

• Instruction register (IR)

– Contains the instruction most recently fetched

• Program status word (PSW)

– Contains status information

Cork Institute of Technology 7

Karl O'Connell evSD1 - 2018

Condition codes

• Usually part of the control register

– Also called flags

• Bits set by processor hardware as a result

of operations

– Read only, intended for feedback regarding

the results of instruction execution.

Roadmap

– Basic Elements

– Processor Registers

– Instruction Execution

– Interrupts

– The Memory Hierarchy

– Cache Memory

– I/O Communication Techniques

Cork Institute of Technology 8

Karl O'Connell evSD1 - 2018

Instruction Execution

• A program consists of a set of instructions

stored in memory

• Two steps

– Processor reads (fetches) instructions from

memory

– Processor executes each instruction

Basic Instruction Cycle

Cork Institute of Technology 9

Karl O'Connell evSD1 - 2018

Instruction Fetch

and Execute

• The processor fetches the instruction from

memory

• Program counter (PC) holds address of

the instruction to be fetched next

– PC is incremented after each fetch

Instruction Register

• Fetched instruction loaded into instruction

register

• Categories

– Processor-memory,

– processor-I/O,

– Data processing,

– Control

Cork Institute of Technology 10

Karl O'Connell evSD1 - 2018

Characteristics of a

Hypothetical Machine

Example of

Program Execution

Cork Institute of Technology 11

Karl O'Connell evSD1 - 2018

Roadmap

– Basic Elements

– Processor Registers

– Instruction Execution

– Interrupts

– The Memory Hierarchy

– Cache Memory

– I/O Communication Techniques

Interrupts

• Interrupt the normal sequencing of the

processor

• Provided to improve processor utilization

– Most I/O devices are slower than the

processor

– Processor must pause to wait for device

Cork Institute of Technology 12

Karl O'Connell evSD1 - 2018

Common Classes

of Interrupts

Flow of Control

without Interrupts

Cork Institute of Technology 13

Karl O'Connell evSD1 - 2018

Interrupts and the

Instruction Cycle

Transfer of Control

via Interrupts

Cork Institute of Technology 14

Karl O'Connell evSD1 - 2018

Instruction Cycle

with Interrupts

Short I/O Wait

Cork Institute of Technology 15

Karl O'Connell evSD1 - 2018

Long I/O wait

Simple

Interrupt Processing

Cork Institute of Technology 16

Karl O'Connell evSD1 - 2018

Changes in Memory and

Registers for an Interrupt

Multiple Interrupts

• Suppose an interrupt occurs while another

interrupt is being processed.

– E.g. printing data being received via

communications line.

• Two approaches:

– Disable interrupts during interrupt processing

– Use a priority scheme.

Cork Institute of Technology 17

Karl O'Connell evSD1 - 2018

Sequential

Interrupt Processing

Nested

Interrupt Processing

Cork Institute of Technology 18

Karl O'Connell evSD1 - 2018

Example of

Nested Interrupts

Multiprogramming

• Processor has more than one program to

execute

• The sequence the programs are executed

depend on their relative priority and

whether they are waiting for I/O

• After an interrupt handler completes,

control may not return to the program that

was executing at the time of the interrupt

Cork Institute of Technology 19

Karl O'Connell evSD1 - 2018

Roadmap

– Basic Elements

– Processor Registers

– Instruction Execution

– Interrupts

– The Memory Hierarchy

– Cache Memory

– I/O Communication Techniques

Memory Hierarchy

• Major constraints in memory

– Amount

– Speed

– Expense

• Faster access time, greater cost per bit

• Greater capacity, smaller cost per bit

• Greater capacity, slower access speed

Cork Institute of Technology 20

Karl O'Connell evSD1 - 2018

The Memory Hierarchy

• Going down the

hierarchy

– Decreasing cost per bit

– Increasing capacity

– Increasing access time

– Decreasing frequency of

access to the memory

by the processor

Secondary Memory

• Auxiliary memory

• External

• Nonvolatile

• Used to store program and data files

Cork Institute of Technology 21

Karl O'Connell evSD1 - 2018

Roadmap

– Basic Elements

– Processor Registers

– Instruction Execution

– Interrupts

– The Memory Hierarchy

– Cache Memory

– I/O Communication Techniques

Cache Memory

• Invisible to the OS

– Interacts with other memory management

hardware

• Processor must access memory at least

once per instruction cycle

– Processor speed faster than memory access

speed

• Exploit the principle of locality with a small

fast memory

Cork Institute of Technology 22

Karl O'Connell evSD1 - 2018

Principal of Locality

• More details later but in short …

• Data which is required soon is often close

to the current data

– If data is referenced, then it’s neighbour might

be needed soon.

Cache and Main Memory

Cork Institute of Technology 23

Karl O'Connell evSD1 - 2018

Cache Principles

• Contains copy of a portion of main

memory

• Processor first checks cache

– If not found, block of memory read into cache

• Because of locality of reference, likely

future memory references are in that block

Cache/Main-Memory

Structure

Cork Institute of Technology 24

Karl O'Connell evSD1 - 2018

Cache Read Operation

Cache Design Issues

• Main categories are:

– Cache size

– Block size

– Mapping function

– Replacement algorithm

– Write policy

Cork Institute of Technology 25

Karl O'Connell evSD1 - 2018

Size issues

• Cache size

– Small caches have significant impact on

performance

• Block size

– The unit of data exchanged between cache

and main memory

– Larger block size means more hits

– But too large reduces chance of reuse.

Mapping function

• Determines which cache location the block

will occupy

• Two constraints:

– When one block read in, another may need

replaced

– Complexity of mapping function increases

circuitry costs for searching.

Cork Institute of Technology 26

Karl O'Connell evSD1 - 2018

Replacement Algorithm

• Chooses which block to replace when a

new block is to be loaded into the cache.

• Ideally replacing a block that isn’t likely to

be needed again

– Impossible to guarantee

• Effective strategy is to replace a block that

has been used less than others

– Least Recently Used (LRU)

Write policy

• Dictates when the memory write operation

takes place

• Can occur every time the block is updated

• Can occur when the block is replaced

– Minimize write operations

– Leave main memory in an obsolete state

Cork Institute of Technology 27

Karl O'Connell evSD1 - 2018

Roadmap

– Basic Elements

– Processor Registers

– Instruction Execution

– Interrupts

– The Memory Hierarchy

– Cache Memory

– I/O Communication Techniques

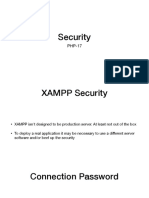

I/O Techniques

• When the processor encounters an

instruction relating to I/O,

– it executes that instruction by issuing a

command to the appropriate I/O module.

• Three techniques are possible for I/O

operations:

– Programmed I/O

– Interrupt-driven I/O

– Direct memory access (DMA)

Cork Institute of Technology 28

Karl O'Connell evSD1 - 2018

Programmed I/O

• The I/O module performs the requested

action

– then sets the appropriate bits in the I/O status

register

– but takes no further action to alert the

processor.

• As there are no interrupts, the processor

must determine when the instruction is

complete

Programmed I/O

Instruction Set

• Control

– Used to activate and instruct device

• Status

– Tests status conditions

• Transfer

– Read/write between process register and device

Cork Institute of Technology 29

Karl O'Connell evSD1 - 2018

Programmed

I/O Example

• Data read in a word at a

time

– Processor remains in status-

checking look while reading

Interrupt-Driven I/O

• Processor issues an I/O command to a

module

– and then goes on to do some other useful

work.

• The I/O module will then interrupt the

processor to request service when it is

ready to exchange data with the

processor.

Cork Institute of Technology 30

Karl O'Connell evSD1 - 2018

Interrupt-

Driven I/O

• Eliminates needless

waiting

– But everything passes

through processor.

Direct Memory Access

• Performed by a separate module on the

system

• When needing to read/write processor

issues a command to DMA module with:

– Whether a read or write is requested

– The address of the I/O device involved

– The starting location in memory to read/write

– The number of words to be read/written

Cork Institute of Technology 31

Karl O'Connell evSD1 - 2018

Direct Memory Access

• I/O operation delegated to

DMA module

• Processor only involved

when beginning and

ending transfer.

• Much more efficient.

Cork Institute of Technology 32

You might also like

- Chapter01 RevDocument9 pagesChapter01 RevYonal Supit DeruntauNo ratings yet

- Lec2 Hardware in Embedded System Compatibility ModeDocument32 pagesLec2 Hardware in Embedded System Compatibility ModeAnh NamNo ratings yet

- 2 Central Processing Unit PDFDocument68 pages2 Central Processing Unit PDFمعتز العجيليNo ratings yet

- Presentation of 8051Document178 pagesPresentation of 8051sivar22No ratings yet

- I/O: Connecting To Outside World: So Far, We've Learned How ToDocument8 pagesI/O: Connecting To Outside World: So Far, We've Learned How ToTrần LouisNo ratings yet

- Introduction To Microcontrollers: ECE473/573 Microprocessor System Design, Dr. Shiue 1Document14 pagesIntroduction To Microcontrollers: ECE473/573 Microprocessor System Design, Dr. Shiue 1zaheer_ahamed2000No ratings yet

- Unit 1 OSDocument61 pagesUnit 1 OSSAI ANDALAM (RA2111003011353)No ratings yet

- Unit - I: Basic Structure of A Computer System Computer SystemDocument25 pagesUnit - I: Basic Structure of A Computer System Computer Systempuli sivaNo ratings yet

- M3 General PurposeDocument45 pagesM3 General PurposeUsama SabirNo ratings yet

- Csea - 14200122072 - Samrat Mondal (Co)Document10 pagesCsea - 14200122072 - Samrat Mondal (Co)Samrat MondalNo ratings yet

- Computer Architecture and Organization ReviewerDocument14 pagesComputer Architecture and Organization ReviewerEmelex CortezNo ratings yet

- Lisa18 Slides MastersDocument127 pagesLisa18 Slides Mastersadrien.blanchetNo ratings yet

- High Performance Networking. Low Latency Devices. 'Network Fabric'Document40 pagesHigh Performance Networking. Low Latency Devices. 'Network Fabric'Jason WongNo ratings yet

- Lec 2Document33 pagesLec 2naveenNo ratings yet

- Instruction Format PDFDocument5 pagesInstruction Format PDFG.SAIDULUNo ratings yet

- 05 CSA RegistersDocument51 pages05 CSA RegistersHengCYNo ratings yet

- Lecture 2 - Typical Embedded SystemDocument5 pagesLecture 2 - Typical Embedded SystemrhodonelduatinNo ratings yet

- Lecture 02Document16 pagesLecture 02api-3801184No ratings yet

- UNIT 1 MicroprocessorDocument71 pagesUNIT 1 Microprocessorakshat.2125csit1203No ratings yet

- CH 1 - Introduction To Computer Architecture and Performance MeasurementDocument42 pagesCH 1 - Introduction To Computer Architecture and Performance MeasurementWajdi ElhamziNo ratings yet

- Chapter 4 Processor - 2014Document71 pagesChapter 4 Processor - 2014world channelNo ratings yet

- IntroductionDocument106 pagesIntroductionG P ROHTIHNo ratings yet

- Best Practices For Implementing Arm Cortex - A12 Processor and Mali - T6Xx Gpus For Mid-Range Mobile SocsDocument28 pagesBest Practices For Implementing Arm Cortex - A12 Processor and Mali - T6Xx Gpus For Mid-Range Mobile SocssharathNo ratings yet

- Input/Output: The Computer's Response Time Is No Match For OursDocument108 pagesInput/Output: The Computer's Response Time Is No Match For OursPrashantJoshiNo ratings yet

- CS 251 Introduction To Computer Organization & Assembly LanguageDocument16 pagesCS 251 Introduction To Computer Organization & Assembly LanguageidrissalmaNo ratings yet

- 01 - Mod 2 - Livro AutorresponsabilidadeDocument9 pages01 - Mod 2 - Livro AutorresponsabilidadeNillyNo ratings yet

- Processors and Programmable Logic: Khaled Grati Grati - Khaled@Supcom - TN 2020-2021Document18 pagesProcessors and Programmable Logic: Khaled Grati Grati - Khaled@Supcom - TN 2020-2021ibrahimNo ratings yet

- CH-03Document24 pagesCH-03Aayush KunwarNo ratings yet

- Lecture 17Document13 pagesLecture 17api-3801184No ratings yet

- Microprocessor Based System: My Lord! Advance Me in Knowledge and True UnderstandingDocument15 pagesMicroprocessor Based System: My Lord! Advance Me in Knowledge and True UnderstandingAsma' ZubirNo ratings yet

- Lecture 1 - Introduction To OS 2022 Till History of OSDocument74 pagesLecture 1 - Introduction To OS 2022 Till History of OSShagun Mengi 21bcs083No ratings yet

- CH 3Document45 pagesCH 3sakuNo ratings yet

- Proc Emb - Ch1Document37 pagesProc Emb - Ch1Jihene ZgolliNo ratings yet

- ECE 152 Where We Are in This Course Right Now: Introduction To Computer ArchitectureDocument7 pagesECE 152 Where We Are in This Course Right Now: Introduction To Computer ArchitectureMohammad NizamNo ratings yet

- ELECH473 Th03Document65 pagesELECH473 Th03hung kungNo ratings yet

- 1.1 The Characteristics of Contemporary Processors.280155520Document1 page1.1 The Characteristics of Contemporary Processors.280155520Mark RobsonNo ratings yet

- Embedded System Module 3 Part 2Document60 pagesEmbedded System Module 3 Part 2Harish G CNo ratings yet

- Su L17 Processor DatapathDocument33 pagesSu L17 Processor DatapathindramanokaranNo ratings yet

- Computer IO Buses and InterfacesDocument28 pagesComputer IO Buses and InterfacesRS Panneer SelvanNo ratings yet

- ProcessDocument12 pagesProcessuksogNo ratings yet

- Embedded Systems - RTOSDocument23 pagesEmbedded Systems - RTOSCheril MehtaNo ratings yet

- 01 Chap01 Introduction 4slotsDocument84 pages01 Chap01 Introduction 4slotsnguyenduyhai.athenaNo ratings yet

- Lec17 DisksDocument31 pagesLec17 Disksapi-3761983No ratings yet

- Chapt 02Document71 pagesChapt 02Mansoor QadirNo ratings yet

- ESY LEC01 ComputerArchitectureDocument54 pagesESY LEC01 ComputerArchitectureThomNo ratings yet

- FPGA and OpenCLDocument31 pagesFPGA and OpenCLalejandro2112No ratings yet

- Embedded Systems Design: A Unified Hardware/Software IntroductionDocument44 pagesEmbedded Systems Design: A Unified Hardware/Software IntroductionDr.S.A.SivakumarNo ratings yet

- Embedded Systems Design: A Unified Hardware/Software IntroductionDocument44 pagesEmbedded Systems Design: A Unified Hardware/Software IntroductionnazNo ratings yet

- Chapter 12 (Instruction Sets Characteristics and Functions)Document18 pagesChapter 12 (Instruction Sets Characteristics and Functions)ki.to4757No ratings yet

- CompArchOrg 01 - OverviewDocument23 pagesCompArchOrg 01 - OverviewVincent GaldoNo ratings yet

- 04 Computers Knowledge-OrganiserDocument5 pages04 Computers Knowledge-OrganiserNavdha SachdevaNo ratings yet

- Arrakis: The Operating System Is The Control Plane: Simon Peter, Jialin Li, Irene Zhang, Dan R. K. Ports, Et AlDocument30 pagesArrakis: The Operating System Is The Control Plane: Simon Peter, Jialin Li, Irene Zhang, Dan R. K. Ports, Et AlvigneshthegreatNo ratings yet

- 4CS015Week6CPUArchitecture 90180Document39 pages4CS015Week6CPUArchitecture 90180np03cs4a230235No ratings yet

- Getting To Know Embedded Systems HardwareDocument28 pagesGetting To Know Embedded Systems HardwareCata CaraNo ratings yet

- Computer Peripheral Units: Central Processing Unit (CPU)Document53 pagesComputer Peripheral Units: Central Processing Unit (CPU)wedo jiffyNo ratings yet

- Computer Organization and Architecture Major Advances in ComputersDocument14 pagesComputer Organization and Architecture Major Advances in ComputersFehmi DenguirNo ratings yet

- 3-Module 1-04-Aug-2021material II 04-Aug-2021 Unit 1 Presentation 2Document32 pages3-Module 1-04-Aug-2021material II 04-Aug-2021 Unit 1 Presentation 2jeevaaNo ratings yet

- Chapter 1 Intro To MicroproDocument22 pagesChapter 1 Intro To Microproellyshacb-wp21No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- How To Make ButterDocument2 pagesHow To Make ButterBigu Marius AlinNo ratings yet

- H+ Sport CustomersDocument42 pagesH+ Sport CustomersBigu Marius AlinNo ratings yet

- H+ Sport OrdersDocument13 pagesH+ Sport OrdersBigu Marius AlinNo ratings yet

- 10 BackupDocument18 pages10 BackupBigu Marius AlinNo ratings yet

- 10 Methodologies BasicConceptsDocument21 pages10 Methodologies BasicConceptsBigu Marius AlinNo ratings yet

- 11 Methodologies XP ScrumDocument17 pages11 Methodologies XP ScrumBigu Marius AlinNo ratings yet

- 12 Configuration+managementDocument33 pages12 Configuration+managementBigu Marius AlinNo ratings yet

- 9 File ManagementDocument16 pages9 File ManagementBigu Marius AlinNo ratings yet

- 9 LifecycleModelingDocument34 pages9 LifecycleModelingBigu Marius AlinNo ratings yet

- 6 - B - Personas OverviewDocument40 pages6 - B - Personas OverviewBigu Marius AlinNo ratings yet

- 4 Traditional REDocument29 pages4 Traditional REBigu Marius AlinNo ratings yet

- 7 System TestingDocument21 pages7 System TestingBigu Marius AlinNo ratings yet

- 8 Unit TestingDocument25 pages8 Unit TestingBigu Marius AlinNo ratings yet

- PHP 04Document59 pagesPHP 04Bigu Marius AlinNo ratings yet

- 3 ModelingWithUMLDocument25 pages3 ModelingWithUMLBigu Marius AlinNo ratings yet

- L10a - ExceptionsDocument25 pagesL10a - ExceptionsBigu Marius AlinNo ratings yet

- IT Solutions Architecture 1st Lab ReportDocument31 pagesIT Solutions Architecture 1st Lab ReportBigu Marius AlinNo ratings yet

- PHP 13Document57 pagesPHP 13Bigu Marius AlinNo ratings yet

- 2 ModelingwithUMLDocument28 pages2 ModelingwithUMLBigu Marius AlinNo ratings yet

- L10b - SoftwareQualityDocument35 pagesL10b - SoftwareQualityBigu Marius AlinNo ratings yet

- PHP 07Document20 pagesPHP 07Bigu Marius AlinNo ratings yet

- PHP 09Document62 pagesPHP 09Bigu Marius AlinNo ratings yet

- PHP 12Document24 pagesPHP 12Bigu Marius AlinNo ratings yet

- PHP 17Document34 pagesPHP 17Bigu Marius AlinNo ratings yet

- PHP 15Document34 pagesPHP 15Bigu Marius AlinNo ratings yet

- PHP 01Document30 pagesPHP 01Bigu Marius AlinNo ratings yet

- PHP 02Document47 pagesPHP 02Bigu Marius AlinNo ratings yet

- PHP 03Document50 pagesPHP 03Bigu Marius AlinNo ratings yet

- SOFT7006 Operating Systems: 5. ConcurrencyDocument79 pagesSOFT7006 Operating Systems: 5. ConcurrencyBigu Marius AlinNo ratings yet

- 05afile SystemsDocument40 pages05afile SystemsBigu Marius AlinNo ratings yet

- Huj GV7 U LDocument10 pagesHuj GV7 U LevermaniaNo ratings yet

- An Analysis On Slang Word Used in Jumanji 2 MovieDocument67 pagesAn Analysis On Slang Word Used in Jumanji 2 MovieDoniBenuNo ratings yet

- Data Mining Lab QuestionsDocument47 pagesData Mining Lab QuestionsSneha Pinky100% (1)

- Research Project Report Format MBA IV SemDocument3 pagesResearch Project Report Format MBA IV SemvinayNo ratings yet

- A Systematic Review of The Use of Virtual Reality in EducationDocument6 pagesA Systematic Review of The Use of Virtual Reality in Educationapi-688059491No ratings yet

- Veeam Backup Replication Best PracticesDocument322 pagesVeeam Backup Replication Best Practicesoscarlevitorres9719No ratings yet

- Sistem Informasi Tabungan Siswa (Sitasi) Berbasis Website Dengan Model PIECESDocument9 pagesSistem Informasi Tabungan Siswa (Sitasi) Berbasis Website Dengan Model PIECESJasika Jurnal Sistem Informasi AkuntansiNo ratings yet

- Ota000004 SDH Principle Issue 2.2Document49 pagesOta000004 SDH Principle Issue 2.2Nam VoNo ratings yet

- Excel Power Pivot TutorialDocument159 pagesExcel Power Pivot Tutorialarbsbpo100% (7)

- XII CS PB-I Sample Paper-VIII by KVS RO JaipurDocument9 pagesXII CS PB-I Sample Paper-VIII by KVS RO JaipurPoonam RavNo ratings yet

- Oracle Join Vs ANSI SQL Join SummaryDocument2 pagesOracle Join Vs ANSI SQL Join Summaryjcgutz3No ratings yet

- 8.0 - IBM - Security - Data - EncryptionDocument21 pages8.0 - IBM - Security - Data - EncryptionzOuheir MkhitarNo ratings yet

- Financial-Literacy EditedDocument58 pagesFinancial-Literacy EditedJoy Marie HuindaNo ratings yet

- BHCS39504 MViQ+ Brochure - R7Document12 pagesBHCS39504 MViQ+ Brochure - R7siienergia.uniNo ratings yet

- HPCC (High-Performance Computing Cluster)Document10 pagesHPCC (High-Performance Computing Cluster)Abhi GoyanNo ratings yet

- C# .Net Array PDFDocument8 pagesC# .Net Array PDFMonti SainiNo ratings yet

- Data Penting2Document30 pagesData Penting2wakatipdalNo ratings yet

- VinithaRavichandran ResumeDocument1 pageVinithaRavichandran ResumeBashiNo ratings yet

- Oracle LogMiner Viewer and Flashback TransactionDocument21 pagesOracle LogMiner Viewer and Flashback TransactionMohammad ZaheerNo ratings yet

- Substation Communications:: Technical InstituteDocument23 pagesSubstation Communications:: Technical InstitutenooralhudNo ratings yet

- Bettercloud Whitepaper Demystifying GDPR PDFDocument16 pagesBettercloud Whitepaper Demystifying GDPR PDFMonika DimovskaNo ratings yet

- Term 2 CS Practical File - SQLDocument12 pagesTerm 2 CS Practical File - SQLAnbuchelvan VKNo ratings yet

- Rigaku Journal 33-2-29-31Document3 pagesRigaku Journal 33-2-29-31Eduardo ArdilesNo ratings yet

- TreeView Control From The DatabaseDocument5 pagesTreeView Control From The DatabaseJayant ChouguleNo ratings yet

- 408Document32 pages408Ashwin RamankuttyNo ratings yet

- HDFS CommandsDocument6 pagesHDFS CommandsAscilton PereiraNo ratings yet

- Enable-Disable Archive Log Mode 10g-11gDocument6 pagesEnable-Disable Archive Log Mode 10g-11gJosé Carlos González SierraNo ratings yet

- 1 TSM Admin Best PracticesDocument43 pages1 TSM Admin Best PracticesnewbeoneNo ratings yet

- Unit 1: The Database Environment: Topic 1: Basic Concepts and Terminologies Data vs. Information - DataDocument27 pagesUnit 1: The Database Environment: Topic 1: Basic Concepts and Terminologies Data vs. Information - DataVance GonzalesNo ratings yet

- PR 1 Week 3 and Week 4Document6 pagesPR 1 Week 3 and Week 4Jaja CabaticNo ratings yet