Professional Documents

Culture Documents

Examination-Augijst, Examination Vlsi: Nol. All

Examination-Augijst, Examination Vlsi: Nol. All

Uploaded by

Nagendra ReddyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Examination-Augijst, Examination Vlsi: Nol. All

Examination-Augijst, Examination Vlsi: Nol. All

Uploaded by

Nagendra ReddyCopyright:

Available Formats

Reg.

No:

17750E,404

FOIJR YEAR B.TECH DEGREE EXAMINATION-AUGIJST, 2O2I

SEVENTH SEMESTER EXAMINATION

VLSI SIGNAL PROCESSING (VS)

(Scheme -2017)

OPtrN ELECTIVE

Time : 3 Hours Max. Marks : 60

Note : Answer Question Nol. and any One Question from each Unit.

All Questions Carry Equal Marks

1. Answer the following Questions (2X5:10)

a) Write equation for one dimensional discrete wavelet transform

b) Define Loop ,Path and Cycle

c) Write equation for the power consumption of pipelined filter

d) Write two basic steps in Unfolding algorithm

e) Define iteration vector , edge mapping, reduced dependence graph

TINIT - I

2. a) Design system level diagram of the LMS adaptive filter. (s)

b) Why VLSI Signal processors require Scaling in CMOS explain with (5)

lT-DRAM cell

OR

3. a) What are the noble identities for multirate systems (5)

(Note: Decimator and Expander are the references)

b) Represent DFG,SFG,DG and BD for 3tap FIR filter. (s)

LINIT - II

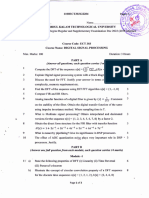

4. a) Find T.. for the DFG shown in Figure 4.1 (s)

(u (?)

(i r;\ ,'l\

\\--rLff,

J; '\*"/ ttl

dt

,1-

^ts"

rt r-\

- { l'<**

\r/

l)

\#

{11

f igure 4.1

b) Write an algorithm for constructing equivalent SRDFG from an MRDFG (s)

P.T.O

OR

5. Discuss any two algorithms for computing Iteration bound for the given ( l0 )

DFG.

LNIT - III

6. a) Design fine grain pipeline architecture for FIR filter with Tm:l8 units and ( 5)

Ta:2 units.

b) Derive power consumption for Pipelining and what is the importance of ' ( s)

FVo' in the power consumption.

OR

7. a) Design feed forward cutest for FIR filter with Tm:10 units and Ta:6 ( s)

units.

b) Design High Performance 3-tap FIR filter using parallel processing ( s)

TINIT - IV

8. a) Prove i) w,(p):w(p)+r(Vr)- r(Vo) (s)

ii) retiming does not alter the iteration bound of DFG

b) Prove "unfolding preserves the number of delays in a DFG' and any 2- (5)

folding transformation properti es.

(Hint: Assume your own example)

OR

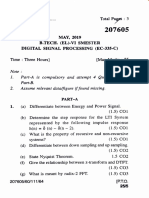

9. a) For the original DFG given in Figure 9.1 design 2-unfolded DFG with (s)

iteration bound and sample period.

Figure 9.1

b) Prove "adding the constant value j to the retiming value of each node does (s)

not change the mapping from G to G'."

LINIT -V

10. a) Design F, Design Rl for FIR systolic arrays. (5)

b) Design mapping methodology to accommodate delay elements in the space (s)

representation(Hint: [Jse single cell DG).

OR

11. a)' Design R2 and Dual R2, Design Rl for FIR systolic arrays. (s)

b) Briefly explain i) Matrix-Matrix Multiplication 1i) 2D Systolic anay design. (s)

You might also like

- Advanced Mathematical Methods With Maple: Derek RichardsDocument30 pagesAdvanced Mathematical Methods With Maple: Derek RichardsAurangZaib LaghariNo ratings yet

- (Ebook PDF) Handbook of Dam EngineeringDocument1 page(Ebook PDF) Handbook of Dam EngineeringDesalegn TamirNo ratings yet

- Fitment - Ugc 6th Pay CommissionDocument10 pagesFitment - Ugc 6th Pay CommissionJoseph Anbarasu100% (3)

- Ece6 DSP Dec09Document2 pagesEce6 DSP Dec09Nitish MahajanNo ratings yet

- DSP Digital Signal ProcessingDocument2 pagesDSP Digital Signal ProcessingHarikaNo ratings yet

- SS Previous PaperDocument7 pagesSS Previous PaperAshokNo ratings yet

- DSP PDFDocument2 pagesDSP PDFSibiviswa RajendranNo ratings yet

- DSP 5Document2 pagesDSP 5Suman RoyNo ratings yet

- Clat2-Set A QPDocument2 pagesClat2-Set A QPVikram ChaudharyNo ratings yet

- DSP2Document2 pagesDSP220001015503 MANAWWAR HUSSAINNo ratings yet

- Sem 6Document64 pagesSem 6Tushar SinghNo ratings yet

- WWW - Manaresults.Co - In: II B. Tech I Semester Regular Examinations, October/November - 2017 Signals & SystemsDocument8 pagesWWW - Manaresults.Co - In: II B. Tech I Semester Regular Examinations, October/November - 2017 Signals & SystemsBAKTHA SINGHNo ratings yet

- Digital Signal Processing Dec2021Document2 pagesDigital Signal Processing Dec2021adith t mNo ratings yet

- 002 Computer Science - November 2019 - SMCS11 Smse11Document6 pages002 Computer Science - November 2019 - SMCS11 Smse11SandipNo ratings yet

- CSE 560 - Practice Problem Set 4 SolutionDocument3 pagesCSE 560 - Practice Problem Set 4 SolutionHalim KorogluNo ratings yet

- CS302 - Analog and DigitalDocument5 pagesCS302 - Analog and DigitalGaitonde GaneshNo ratings yet

- Previous Questions1Document2 pagesPrevious Questions1Mounika GorikadiNo ratings yet

- 6th Sem Mid B.tech. CS, ItDocument29 pages6th Sem Mid B.tech. CS, Itreshu111202No ratings yet

- Principles Compiler Design May 2004Document2 pagesPrinciples Compiler Design May 2004api-3782519No ratings yet

- (A) (B) (C) (D) (E) (0 (G) (H) (I) O Tree? 2. (A) Examples' (B) Elemlnts' ToDocument2 pages(A) (B) (C) (D) (E) (0 (G) (H) (I) O Tree? 2. (A) Examples' (B) Elemlnts' Toapi-279049687No ratings yet

- DSP Previous PapersDocument8 pagesDSP Previous PapersecehodaietNo ratings yet

- DSP Nov 18Document2 pagesDSP Nov 18Saurabh BhiseNo ratings yet

- CST201 DATA STRUCTURES, December 2020Document2 pagesCST201 DATA STRUCTURES, December 2020Anas AnsarNo ratings yet

- Cp5151 Advanced Data Structures and AlgorithimsDocument3 pagesCp5151 Advanced Data Structures and AlgorithimsPragaDarshNo ratings yet

- Ect303 Digital Signal Processing, December 2022Document3 pagesEct303 Digital Signal Processing, December 2022Dinil DhananjayanNo ratings yet

- Ece Question PapaerDocument4 pagesEce Question PapaerAbhinavRahaNo ratings yet

- M A K A U T, W B: Aulana BUL Alam ZAD Niversity of Echnology EST EngalDocument4 pagesM A K A U T, W B: Aulana BUL Alam ZAD Niversity of Echnology EST EngalHimadri Sekhar DuttaNo ratings yet

- Sixth Semester B Tech (Enginee Ing) Degree Examination December 2 10Document2 pagesSixth Semester B Tech (Enginee Ing) Degree Examination December 2 10Abhishek EkNo ratings yet

- Cst201 Data Structures, December 2020Document2 pagesCst201 Data Structures, December 2020SHAHEEM TKNo ratings yet

- EC6009 Advanced Computer Architecture University Question Paper Nov Dec 2017Document3 pagesEC6009 Advanced Computer Architecture University Question Paper Nov Dec 2017Ramesh Kumar ANo ratings yet

- Microprocessors: Fifth Semester (M)Document7 pagesMicroprocessors: Fifth Semester (M)rinkydsNo ratings yet

- DSP Am08Document3 pagesDSP Am08Senthil KumarNo ratings yet

- RT22055052015Document8 pagesRT22055052015ksai.mbNo ratings yet

- (Ec8791)Document3 pages(Ec8791)Samraj ECENo ratings yet

- APR2013P21Document63 pagesAPR2013P21qsashutoshNo ratings yet

- DSP (5th) May2018Document2 pagesDSP (5th) May2018Nisha ManiNo ratings yet

- DSP 2015 PatternDocument2 pagesDSP 2015 PatternfilescodingNo ratings yet

- Embedded System DesignDocument23 pagesEmbedded System DesignlosssssssssNo ratings yet

- DSP (5th) May2019 PDFDocument2 pagesDSP (5th) May2019 PDFs tharunNo ratings yet

- Ii/Iv B. Tech. Degree Examinations, December - 2016 Second Semester Electronics & CommunicationsDocument10 pagesIi/Iv B. Tech. Degree Examinations, December - 2016 Second Semester Electronics & CommunicationsHARE KRISHNANo ratings yet

- Microprocessor and Interfacing - Question Paper May 2016 - Electronics & Telecomm (Semester 4) - Gujarat Technological University (GTU)Document4 pagesMicroprocessor and Interfacing - Question Paper May 2016 - Electronics & Telecomm (Semester 4) - Gujarat Technological University (GTU)YESHUDAS MUTTUNo ratings yet

- ComaDocument3 pagesComaMunshi Abdul AqiqNo ratings yet

- MST 2017 (O) PDFDocument2 pagesMST 2017 (O) PDFAdamyaKaushikNo ratings yet

- Thapar University, Patiala: Proc # RTN #A RTN #B RTN #C RTN #DDocument2 pagesThapar University, Patiala: Proc # RTN #A RTN #B RTN #C RTN #DAdamyaKaushikNo ratings yet

- LinearDocument2 pagesLinearYee Jing TanNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document3 pagesQuestion Paper Code:: (10×2 20 Marks)ManimegalaiNo ratings yet

- Research QuestionsDocument6 pagesResearch QuestionsiAmAlfaNo ratings yet

- 07a51101 Digital Signal ProcessingDocument8 pages07a51101 Digital Signal ProcessingSRINIVASA RAO GANTANo ratings yet

- Gate Sample PaperDocument7 pagesGate Sample Papershettyashwin19No ratings yet

- Questions 4 1Document95 pagesQuestions 4 1Anik PaulNo ratings yet

- Coa-June 2023Document2 pagesCoa-June 2023examlab57No ratings yet

- CS 801D PDFDocument4 pagesCS 801D PDFarnab paulNo ratings yet

- Cs 6302 Dbms 1718 Odd Iat2 With KeyDocument3 pagesCs 6302 Dbms 1718 Odd Iat2 With KeyhelloNo ratings yet

- DSP Nec-011 - 2Document4 pagesDSP Nec-011 - 2Chhaya GroverNo ratings yet

- Be Winter 2016Document2 pagesBe Winter 2016M.k. PrajapatNo ratings yet

- Hours L) 2) 3) : Paper (A0461)Document2 pagesHours L) 2) 3) : Paper (A0461)cool_spNo ratings yet

- DSP4Document3 pagesDSP420001015503 MANAWWAR HUSSAINNo ratings yet

- Ec1313 Dec07 Question PaperDocument3 pagesEc1313 Dec07 Question PapersrwaseemahamedNo ratings yet

- RT 21053112016Document4 pagesRT 21053112016RaunaqNo ratings yet

- 2017 Microprocessor and InterfaceDocument3 pages2017 Microprocessor and InterfaceprashantvlsiNo ratings yet

- IE1020 - Network Fundamentals 2019 JuneDocument5 pagesIE1020 - Network Fundamentals 2019 JunevihinsabNo ratings yet

- F (T) F (3-2t) F (T) .: Answer Any Two Questions, Each Carries 15 MarksDocument3 pagesF (T) F (3-2t) F (T) .: Answer Any Two Questions, Each Carries 15 MarksAnanNo ratings yet

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDFrom EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDNo ratings yet

- AWS Associate Solutions Architect Study - ACloud - GuruDocument70 pagesAWS Associate Solutions Architect Study - ACloud - Guruzinedine boubakerNo ratings yet

- Horizontal Steam Sterilizer V2Document12 pagesHorizontal Steam Sterilizer V2SujiNo ratings yet

- Lab Education English Mock Exam - Question Answer BookDocument14 pagesLab Education English Mock Exam - Question Answer BookMichelle ChungNo ratings yet

- Plusco325 Coatings External Pipe CoatingDocument1 pagePlusco325 Coatings External Pipe Coatinga.hasan670No ratings yet

- Effect of Asperity Location On Sliding Stability of Concrete DamsDocument12 pagesEffect of Asperity Location On Sliding Stability of Concrete DamsDipenNo ratings yet

- Afghanistan: Health Expenditure ProfileDocument2 pagesAfghanistan: Health Expenditure ProfileJoannaNo ratings yet

- Yak 52 Maitenance ManualDocument36 pagesYak 52 Maitenance ManualAvionicsfNo ratings yet

- PHD ThesisDocument270 pagesPHD Thesiskamba bryanNo ratings yet

- Asna NotesDocument95 pagesAsna NotesHumbang PurbaNo ratings yet

- Shift Report - November 25, 2023-2nd ShiftDocument4 pagesShift Report - November 25, 2023-2nd Shiftbobowapthree19No ratings yet

- BC 30s (2P)Document2 pagesBC 30s (2P)PT Bintang Baru MedikaNo ratings yet

- Experiment No: 01 TITLE OF EXPERIMENT: Implementation of Traffic Light Controller Using VHDL. A. DiagramDocument19 pagesExperiment No: 01 TITLE OF EXPERIMENT: Implementation of Traffic Light Controller Using VHDL. A. DiagramGauravNo ratings yet

- Architectural Documents For 3 Storey Residential HouseDocument26 pagesArchitectural Documents For 3 Storey Residential HouseArvin EmraNo ratings yet

- FRP Parameter Optimization Settings: Wilfried Baumgartner / Hans Georg Kloep, SAP July 6, 2016Document36 pagesFRP Parameter Optimization Settings: Wilfried Baumgartner / Hans Georg Kloep, SAP July 6, 2016atungmuNo ratings yet

- WhitePaper WePowerDocument46 pagesWhitePaper WePowerOnur OnukNo ratings yet

- The Potential of Banana (Musa: Acuminata) and Potato (Solanum Tuberosum) For Increasing The GrowthDocument19 pagesThe Potential of Banana (Musa: Acuminata) and Potato (Solanum Tuberosum) For Increasing The GrowthAlex GarmaNo ratings yet

- Design of Sequential Circuits - Example 1.3Document3 pagesDesign of Sequential Circuits - Example 1.3MD Saifuzzaman SohanNo ratings yet

- Sterilizer Broschure MST-V enDocument12 pagesSterilizer Broschure MST-V enVictor ȘchiopuNo ratings yet

- Almonte HistoryDocument3 pagesAlmonte HistoryAngelo ErispeNo ratings yet

- Merton On Structural FunctionalismDocument6 pagesMerton On Structural FunctionalismJahnaviSinghNo ratings yet

- De Jure MethodDocument2 pagesDe Jure MethodDr. Zulfiqar AliNo ratings yet

- Polymerization of Vegetable Oils and Their Uses in Printing InksDocument4 pagesPolymerization of Vegetable Oils and Their Uses in Printing InksJosé Antônio Nascimento NetoNo ratings yet

- Lab 4Document18 pagesLab 4Zhansaya KozhdanNo ratings yet

- Grade /: NO. 209 ofDocument3 pagesGrade /: NO. 209 ofrahad60882No ratings yet

- IEEE Standards Style ManualDocument70 pagesIEEE Standards Style ManualDiego Agudelo ContrerasNo ratings yet

- Current Status, Research Trends, and ChallengesDocument23 pagesCurrent Status, Research Trends, and Challengesqgi-tanyaNo ratings yet

- Cantilever SlabDocument3 pagesCantilever SlabMatumbi NaitoNo ratings yet