Professional Documents

Culture Documents

Pcie 5.0: The Next Generation of Peripheral Component Interconnect

Pcie 5.0: The Next Generation of Peripheral Component Interconnect

Uploaded by

Dheeraj SharmaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Pcie 5.0: The Next Generation of Peripheral Component Interconnect

Pcie 5.0: The Next Generation of Peripheral Component Interconnect

Uploaded by

Dheeraj SharmaCopyright:

Available Formats

PCIe 5.

0

The Next Generation of Peripheral Component Interconnect

Defining the Next Standard in Interconnect Technology

PCI Express 5.0 represents the latest in PCI standards using non-return to zero (NRZ) signaling;

doubling the PCIe 4.0 speed from 16 GT/s to 32 GT/s. The PCIe 5.0 standard is on a fast track

for development as the PCISIG (PCI Special Interest Group) — the standard body which controls

the PCI Express standard — has tasked the team to complete the PCIe 5.0 rules by the end of

2019.

Originally, the parallel PCI bus’s purpose was to extend the functionality of standard personal

computers and allow for the addition of networking cards, graphic cards, and other peripheral

interfaces. PCI Express represents a high-speed, differential, serial version of I/O technology that

shares significant roots with the old PCI bus. In all cases, the PCI and PCI Express standard’s

intent is for high-volume manufacturing with low material costs for PC Boards and connectors.

The PCI Express standard successfully meets this goal with speeds of 2.5 GT/s, 5 GT/s, and 8

GT/s. But PCI Express 4.0 at 16 GT/s, the latest speed enhancement to the standard, has proved

to be more difficult for adoption by the PC industry. Additionally, the motherboard and PC

channels typical of most computers will be significantly challenged to transfer the 32 GT/s of PCI

Express 5.0.

However, the demand for more speed has driven the standard body to define the next generation

of PCI Express. The goal of PCIe 5.0 is to increase the standard’s speed in as short a time as

possible. As such, PCIe 5.0 is intended as a straightforward speed bump to the PCIe 4.0

standard without any other significant new features.

For example, PCIe 5.0 does not support PAM4 signaling and only includes new capabilities

required to enable the PCIe standard to support 32 GT/s in as short a time as feasible.

Find us at www.keysight.com Page 1

Next Generation Challenges

The significant challenges to prepare a product to support PCI Express 5.0 relates to channel length. The

faster the signaling rate, the higher the carrier frequency of the signal transmitted over the PC board.

Two types of physical impairments limit how far an engineer can expect to propagate their PCIe signals:

1. The attenuation of the channel

2. Reflections that occur within the channel due to impedance discontinuities found in pins, connectors,

vias and other structures.

The PCIe 5.0 specification uses a channel with -36 dB attenuation at 16 GHz. The frequency 16 GHz

represents the Nyquist frequency of a 32 GT/s digital signal. For example, when a PCIe 5.0 signal starts

out, it may have a typical peak-to-peak voltage of 800 mV. However, after passing through the proposed

-36 dB channel, any resemblance to an open eye is missing. It is only through the application of

transmitter based equalization (de-emphasis) and receiver equalization (a combination of CTLE and DFE)

that a PCIe 5.0 signal can pass through the system channel and be interpreted accurately by the receiver.

The minimum expectation for eye height for a PCIe 5.0 signal is 10 mV (post-equalization). Even with a

near perfect, low jitter transmitter, the significant attenuation of the channel lowers the signal amplitude to

the point where any other type of signal impairment caused by reflections and crosstalk works to close

the recoverable eye.

How to Prepare for the Challenges

To help ensure success with products that support PCI Express 5.0, Keysight is actively engaged to

provide test solutions for validation of the physical layer properties of PCIe 5.0 transmitters and receivers.

Tools to help test PCIe 5.0 devices are available now, and used for the development of the PCIe 5.0

standard.

For example, to test a PCIe 5.0 transmitter, you should consider a real-time oscilloscope with a minimum

bandwidth of 50 GHz. If validating new silicon, you want to measure the transmitter output of the

integrated circuit as close to the output pins of the device as possible. De-embedding the loss attributable

to any breakout channel between the balls of the package to the connectors used to attach the test fixture

to your oscilloscope is required.

The transmit test parameters at 32 GT/s for PCIe 5.0 are the same parameters tested at the lower speeds

of 16 GT/s and 8 GT/s. A high-bandwidth oscilloscope (63 GHz or more) with high-signal integrity is an

ideal tool for these tests and PCIe development.

One of the most challenging aspects of PCIe 5.0 receiver testing is the stressed jitter measurement. A Bit

Error Rate Tester (BERT) can be used to test your receiver. In this test, a worst case PCIe 5.0 eye is

carefully constructed using calibrated impairments and physical ISI traces to achieve a target eye height

of 10 mV (post-equalization). With the target DUT in loopback, the goal is to present the stressed eye to

the receiver input and then to count errors as the signal loops back to the BERT’s error detector.

It is the calibration of the test signal which is the most challenging aspect of receiver testing. The standard

itself is not yet complete, so prototype software and test methods specific to PCIe 5.0 are evolving too.

Find us at www.keysight.com Page 2

The Keysight UXR

Series, M8040A and

M8020A J-BERTs

represent the preferred

choices for many of

today's technology

companies looking to

achieve PCIe 5.0

performance while also

delivering high-quality,

robust, and

interoperable design.

Conclusion

Scheduled for completion by the end of 2019, PCI Express 5.0 represents the latest in

PCIe standards doubling the data rate from the PCIe 4.0 speed of 16 GT/s to 32 GT/s

using non-return to zero (NRZ) signaling. The challenges inherent in PCIe 4.0, include

testing and implementation broadly across the PC industry, increases with PCIe 5.0 as

the speed doubles. However, test companies like Keysight are already developing the

test solutions to provide aid in overcoming these new design and test challenges.

Learn More

You can learn more about the recommended BERTs and oscilloscopes:

Keysight UXR Series oscilloscopes

D9050PCIC PCI Express 5.0 Transmitter Electrical Performance Validation and Compliance

D9050PCIC Data Sheet

Keysight M8040A Bit Error Rate Testers

Keysight M8020A J-BERT High-Performance BERT

M8070EDAB with M8070B - Error Distribution Analysis

Accurate PCI Express® Receiver Characterization

Learn more at: www.keysight.com

For more information on Keysight Technologies’ products, applications or services,

please contact your local Keysight office. The complete list is available at:

www.keysight.com/find/contactus

Find us at www.keysight.com Page 3

This information is subject to change without notice. © Keysight Technologies, 2019-2020, Published in USA, January 21, 2020, 5992-3141EN

You might also like

- 8993001467-003 Robbins 34RH C QRSDocument704 pages8993001467-003 Robbins 34RH C QRSlino.rendon.hdezNo ratings yet

- Autotrol 255-960 Dealer ManualDocument28 pagesAutotrol 255-960 Dealer ManualGreg ReynekeNo ratings yet

- P SERIES CIAC SERVICE MANUAL 9k-24k FVDocument97 pagesP SERIES CIAC SERVICE MANUAL 9k-24k FVAnthony Pineda ValenciaNo ratings yet

- PCIe Gen5 TX Tech Brief 090221Document12 pagesPCIe Gen5 TX Tech Brief 090221Sasikala KesavaNo ratings yet

- Hardware Design ConsiderationDocument6 pagesHardware Design ConsiderationWelington OliveiraNo ratings yet

- White Paper: Pci Express TechnologyDocument11 pagesWhite Paper: Pci Express Technologyallen3037100% (1)

- D9040PCIC enDocument28 pagesD9040PCIC enAli AlamehNo ratings yet

- Computer Telephony IntegrationDocument20 pagesComputer Telephony Integrationmirko_aguileraNo ratings yet

- Design and Verification For PCI Express Controller: Braham@yumail - Ac.kr and Kssung@yu - Ac.krDocument6 pagesDesign and Verification For PCI Express Controller: Braham@yumail - Ac.kr and Kssung@yu - Ac.krShilpa MachalliNo ratings yet

- PCI Express White PaperDocument8 pagesPCI Express White PaperUday KumarNo ratings yet

- Cfexpress 1 0 Press Release 2017417Document2 pagesCfexpress 1 0 Press Release 2017417walkrogNo ratings yet

- An Introduction To PCI Express™ Measurements - Tek PDFDocument36 pagesAn Introduction To PCI Express™ Measurements - Tek PDFYou TimNo ratings yet

- Seco Products GuideDocument68 pagesSeco Products GuidebabichemNo ratings yet

- The Next Frontier in Video Encoding: White PaperDocument7 pagesThe Next Frontier in Video Encoding: White PaperRishikesh BansodNo ratings yet

- HW FunctionalityDocument35 pagesHW FunctionalityBeto MurguiaNo ratings yet

- PSCAD Users Guide PDFDocument532 pagesPSCAD Users Guide PDFWilliams A.Subanth Assistant ProfessorNo ratings yet

- Advantech Full DatasheetDocument234 pagesAdvantech Full DatasheetE TNo ratings yet

- INFO TECH IEC61850 Software LibraryDocument29 pagesINFO TECH IEC61850 Software LibraryBalamurali KirankumarNo ratings yet

- DSV Vip CatalogDocument4 pagesDSV Vip CatalogSamNo ratings yet

- The Cisco Quantum Flow Auto Saved)Document12 pagesThe Cisco Quantum Flow Auto Saved)Kranthi KumarNo ratings yet

- RTD Embedded Technologies, Inc.: Rugged, Modular, Stackable SolutionsDocument24 pagesRTD Embedded Technologies, Inc.: Rugged, Modular, Stackable SolutionsPravin Balasaheb GunjalNo ratings yet

- Metaswitch Perimeta SBC Product BrochureDocument4 pagesMetaswitch Perimeta SBC Product BrochureXman HunterNo ratings yet

- Ni Crio BrochureDocument8 pagesNi Crio BrochureSuresh Kumar KongathiNo ratings yet

- Automotive Ethernet TBDocument2 pagesAutomotive Ethernet TBMuthanna AliNo ratings yet

- Ashwani Pande: 992629115 Mobile NoDocument8 pagesAshwani Pande: 992629115 Mobile NoKush ChaturvediNo ratings yet

- Mmi119 en Ixxat All You Need For Can 1 - 2016 Web PDFDocument20 pagesMmi119 en Ixxat All You Need For Can 1 - 2016 Web PDFBigdogguruNo ratings yet

- Atheros Ar9280Document2 pagesAtheros Ar9280Geyonk Yuli SetiawanNo ratings yet

- LF 755 KBDocument19 pagesLF 755 KBJose CuevasNo ratings yet

- Oxford Semiconductor PCIeDocument2 pagesOxford Semiconductor PCIeisoam123No ratings yet

- 2.1. Overview of PCI Express BusDocument19 pages2.1. Overview of PCI Express BusSomasekhar ChepuriNo ratings yet

- Modicon X80 I O PlatformDocument144 pagesModicon X80 I O Platformhmltdt9221No ratings yet

- Service Design For Sibridge TechnologiesDocument21 pagesService Design For Sibridge Technologiesbhavin05No ratings yet

- Embedded System On Pci: AbstractDocument12 pagesEmbedded System On Pci: AbstractbommojuvishuNo ratings yet

- PCIe Measurements 4HW 19375 1Document36 pagesPCIe Measurements 4HW 19375 1Satian AnantapanyakulNo ratings yet

- Nvme Ip Data Sheet En-XilinxDocument17 pagesNvme Ip Data Sheet En-XilinxMinlongerNo ratings yet

- PCI Express 2.0: Scalable Interconnect Technology, TNG: Here ResultsDocument2 pagesPCI Express 2.0: Scalable Interconnect Technology, TNG: Here Resultsavi0341No ratings yet

- CP 443-1Document28 pagesCP 443-1Jacob KalloorNo ratings yet

- Ericsson RedBack Smart Edge 800 DatasheetDocument6 pagesEricsson RedBack Smart Edge 800 DatasheetMannus PavlusNo ratings yet

- Qoriq P2040/P2041, P3 and P5 Series: High-Performance Multicore ProcessorsDocument9 pagesQoriq P2040/P2041, P3 and P5 Series: High-Performance Multicore ProcessorsPaulRicardEspanaNo ratings yet

- 2012 12 VIPA Broschuere HMI ENG Web 01Document6 pages2012 12 VIPA Broschuere HMI ENG Web 01Felix Bocanegra RuizNo ratings yet

- ACIDocument392 pagesACIOgnjen SimisicNo ratings yet

- Phy Ip For Pcie 3.0Document2 pagesPhy Ip For Pcie 3.0uparashar1No ratings yet

- LTRT-12320 Mediant E-SBC For Netia SIP Trunk With Microsoft Lync 2013 Configuration Note Ver. 6.8Document98 pagesLTRT-12320 Mediant E-SBC For Netia SIP Trunk With Microsoft Lync 2013 Configuration Note Ver. 6.8Paweł WyrekNo ratings yet

- Ethernet x520 Server Adapters BriefDocument4 pagesEthernet x520 Server Adapters BriefFiroj KhanNo ratings yet

- Hilscher ProductOverview eDocument6 pagesHilscher ProductOverview estudskirbyNo ratings yet

- PCI Express - ArchitectureDocument1 pagePCI Express - ArchitectureKrishna Saroja SankaNo ratings yet

- Controlador WirelessDocument22 pagesControlador WirelesspietroNo ratings yet

- Advances in Video Compression: Jens-Rainer OhmDocument5 pagesAdvances in Video Compression: Jens-Rainer OhmNguyễn Duy HiềnNo ratings yet

- App FF VANC InsertionDocument14 pagesApp FF VANC InsertionnishitNo ratings yet

- Cisco ASR 9000 Series Shared Port Adapter Support: Product OverviewDocument3 pagesCisco ASR 9000 Series Shared Port Adapter Support: Product OverviewScribdUser250No ratings yet

- Emulex Leaders in Fibre Channel Connectivity: Fibre Chanel Over EthernetDocument29 pagesEmulex Leaders in Fibre Channel Connectivity: Fibre Chanel Over Etherneteasyroc75No ratings yet

- NI Datasheet Ds 151Document20 pagesNI Datasheet Ds 151disturbedphaetonNo ratings yet

- Cisco Catalyst 9800-L Wireless ControllerDocument20 pagesCisco Catalyst 9800-L Wireless Controllerblackmamba etti jeanNo ratings yet

- A VHDL Scalable-Encryption-AlgorithmDocument79 pagesA VHDL Scalable-Encryption-AlgorithmghionoiucNo ratings yet

- TT Virtual Private NetworksDocument69 pagesTT Virtual Private NetworksMohammed ShukkurNo ratings yet

- Algorithm and Architecture Design of High Efficiency Video Coding (HEVC) StandardDocument8 pagesAlgorithm and Architecture Design of High Efficiency Video Coding (HEVC) Standardswati sakhareNo ratings yet

- Infoplc Net Curso Profibus 1Document18 pagesInfoplc Net Curso Profibus 1Jair malandrinNo ratings yet

- Micromite ManualDocument95 pagesMicromite Manualgrant muirNo ratings yet

- Harmonic EB Media Over IPDocument18 pagesHarmonic EB Media Over IPDavid KhechinashviliNo ratings yet

- VLSI Design for Video Coding: H.264/AVC Encoding from Standard Specification to ChipFrom EverandVLSI Design for Video Coding: H.264/AVC Encoding from Standard Specification to ChipNo ratings yet

- Versatile Routing and Services with BGP: Understanding and Implementing BGP in SR-OSFrom EverandVersatile Routing and Services with BGP: Understanding and Implementing BGP in SR-OSNo ratings yet

- (Extract Imp) Good MagazineDocument62 pages(Extract Imp) Good MagazineDheeraj SharmaNo ratings yet

- Integration of 31.6Mhz, 1Kw Solid State RF Power Amplifier in The Booster RF SystemDocument2 pagesIntegration of 31.6Mhz, 1Kw Solid State RF Power Amplifier in The Booster RF SystemDheeraj SharmaNo ratings yet

- BeveragesDocument3 pagesBeveragesDheeraj SharmaNo ratings yet

- Development of The Model of A Self Excited LoopDocument23 pagesDevelopment of The Model of A Self Excited LoopDheeraj SharmaNo ratings yet

- Cavity Testing FundamentalsDocument38 pagesCavity Testing FundamentalsDheeraj SharmaNo ratings yet

- Commissioning Experience With The PEP-II Low-Level RF SystemDocument3 pagesCommissioning Experience With The PEP-II Low-Level RF SystemDheeraj SharmaNo ratings yet

- GaN TransistorsDocument4 pagesGaN TransistorsDheeraj SharmaNo ratings yet

- 75d5a503 8Document75 pages75d5a503 8Dheeraj SharmaNo ratings yet

- 1SL371 1e Linearization of RF AmplifiersDocument21 pages1SL371 1e Linearization of RF AmplifiersDheeraj SharmaNo ratings yet

- 1KW-73835-0 Keithley 4200A-SCS 1f Current Noise Application Note 083021Document14 pages1KW-73835-0 Keithley 4200A-SCS 1f Current Noise Application Note 083021Dheeraj SharmaNo ratings yet

- Theory and Practice of Cavity RF Test Systems : Tom Powers, Thomas Jefferson National Accelerator FacilityDocument31 pagesTheory and Practice of Cavity RF Test Systems : Tom Powers, Thomas Jefferson National Accelerator FacilityDheeraj SharmaNo ratings yet

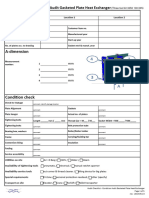

- Template - Condition Audit PHE Checklist Rev.3Document5 pagesTemplate - Condition Audit PHE Checklist Rev.3Karen GoolcharanNo ratings yet

- List of Approved Makes For ElectricalDocument7 pagesList of Approved Makes For ElectricalAvinash KumarNo ratings yet

- Abbreviations Plumbing Symbols: Fort Worth DistrictDocument21 pagesAbbreviations Plumbing Symbols: Fort Worth DistrictDenzel NgNo ratings yet

- Heat Load For 400kV GISDocument5 pagesHeat Load For 400kV GISSurajKurupNo ratings yet

- SPD-481000B Installation and WiringDocument2 pagesSPD-481000B Installation and WiringMNo ratings yet

- Motor Controller CenterDocument17 pagesMotor Controller CenterSimbu ArasanNo ratings yet

- S130 S150 GSM SMS 3G 4G Alarm Controller Ver 3.0Document19 pagesS130 S150 GSM SMS 3G 4G Alarm Controller Ver 3.0sofragiu petruNo ratings yet

- Demo 20078Document55 pagesDemo 20078alexander pinto100% (2)

- William Stallings Computer Organization and Architecture 9 EditionDocument46 pagesWilliam Stallings Computer Organization and Architecture 9 EditionmisbahNo ratings yet

- Alarm and Safety SystemsDocument44 pagesAlarm and Safety SystemsagvassNo ratings yet

- Econcept 50 ADocument36 pagesEconcept 50 ASpitzinstal SRLNo ratings yet

- Deep Sea Electronics PLC: DSE7450 Operator ManualDocument116 pagesDeep Sea Electronics PLC: DSE7450 Operator ManualMostafa ShannaNo ratings yet

- Moss AccsDocument74 pagesMoss Accsapi-3732333No ratings yet

- Toolbox Talk-Electrical SafetyDocument1 pageToolbox Talk-Electrical SafetyvictorNo ratings yet

- Finmon Mi64 Installer Manual Print Version 1.3Document52 pagesFinmon Mi64 Installer Manual Print Version 1.3sydney simonNo ratings yet

- CMOS VLSI Design 28Document1 pageCMOS VLSI Design 28Carlos SaavedraNo ratings yet

- Mass-Storage Structure: Bibliographical NotesDocument2 pagesMass-Storage Structure: Bibliographical NotesTugas UtomoNo ratings yet

- THHHDocument88 pagesTHHHZahid Babaić100% (1)

- Remington HC200CDocument12 pagesRemington HC200Ccostin5No ratings yet

- Hydratight BrochureDocument12 pagesHydratight BrochureI DDETPNo ratings yet

- Panasonic Ak18 ManualDocument32 pagesPanasonic Ak18 ManualJonathan TwynhamNo ratings yet

- 01 Micafil Bushings Overview English PDFDocument6 pages01 Micafil Bushings Overview English PDFanurag_jay12464100% (1)

- AFCompressors Brochure OPC OKDocument4 pagesAFCompressors Brochure OPC OKJD126No ratings yet

- Automatic Boot Open SystemDocument21 pagesAutomatic Boot Open SystemA A.DevanandhNo ratings yet

- VRF VS Chiller: Technical ManagerDocument38 pagesVRF VS Chiller: Technical ManagerJhon Lewis Pino100% (2)

- Piping Painting Colour CodeDocument1 pagePiping Painting Colour CodeBalaraman SNo ratings yet

- Waterman SS-250 Series Slide GatesDocument12 pagesWaterman SS-250 Series Slide GatesHarrianni ZakriNo ratings yet