Professional Documents

Culture Documents

Dasfgderh 57y45

Dasfgderh 57y45

Uploaded by

asdasdasfli.elkinOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Dasfgderh 57y45

Dasfgderh 57y45

Uploaded by

asdasdasfli.elkinCopyright:

Available Formats

S912 Datasheet Revision 0.

Bits(s) R/W Default Description

6 RW 0 ctrl_axi_rd_urgent:

0=DDR read request not urgent;

1=DDR read request urgent.

5:4 RW 0 ctrl_ahb_wr_burst_size:

0=AHB write request burst size 4x128-b;

1=AHB write request burst size 8x128-b;

2=AHB write request burst size 12x128-b;

3=AHB write request burst size 16x128-b.

3:2 RW 0 ctrl_ahb_rd_burst_size:

0=AHB read request burst size 4x128-b;

1=AHB read request burst size 8x128-b;

2=AHB read request burst size 12x128-b;

3=AHB read request burst size 16x128-b.

1 RW 0 ctrl_sw_reset:

0=No reset;

1=Reset RDMA logics except its own register interface.

0 RW 0 ctrl_free_clk_enable:

0=Enable clock gating;

1=No clock gating, enable free clock.

RDMA_STATUS

Bits(s) R/W Default Description

31:24 R 0 rdma_done_flag: interrupt status. 8-bit,

bit, one bit for each RDMA source.

[0] Manual src 0 RDMA done intr status.

[1] Auto src 1 RDMA done intr status.

[2] Auto src 2 RDMA done intr status.

[3] Auto src 3 RDMA done intr status.

[4] Auto src 4 RDMA done intr status.

tatus.

[5] Auto src 5 RDMA done intr status.

[6] Auto src 6 RDMA done intr status.

[7] Auto src 7 RDMA done intr status.

23 R 0 Reserved.

22 R 0 err_axi_wrfifo_undflow

21 R 0 err_axi_wrfifo_ovrflow

20 R 0 err_axi_rdfifo_ovrflow

19:18 R 0 axi_w_st:

AXI write data status:

0=Idle;

1=Wait Data;

2=Req;

3=Wait BRSP.

17:16 R 0 axi_aw_st:

AXI write address status:

0=Idle;

1=Req;

2=Wait RDY.

15:14 R 0 axi_ar_st:

AXI read address status:

0=Idle;

1=Wait FIFO;

2=Req;

3=Wait Done.

13:11 R 0 rdma_id_curr

10:8 R 0 rdma_id_pipe

347/554 AMLOGIC, Inc. Proprietary

S912 Datasheet Revision 0.1

7:0 R 0 req_latch:

Requests that are yet to be serviced. E.g.:

00000000=No request;

00000001=Req 0 waiting;

00001100=Req 2 and 3 waiting;

10000000=Req7 waiting.

RDMA_STATUS2

Bits(s) R/W Default Description

31:30 R 0 Reserved.

29:24 R 0 axi_wrfifo_cnt. FIFO count for buffering VCBus read data to sent to AXI.

23:22 R 0 Reserved.

21:16 R 0 axi_rdfifo_cnt. FIFO count for buffering data read from AXI.

15:14 R 0 Reserved.

13:8 R 32 axi_wrfifo_room. FIFO room for buffering VCBus read data to sent to AXI.

7:6 R 0 Reserved.

5:0 R 32 axi_rdfifo_room. FIFO room for buffering data read from AXI.

RDMA_STATUS3

Bits(s) R/W Default Description

31:24 R 0 Reserved.

23:8 R 0 axi_b_pending

7:0 R 0 axi_aw_pending

348/554 AMLOGIC, Inc. Proprietary

S912 Datasheet Revision 0.1

27.4 HDMI

S912 has Built-in HDMI 2.0 transmitter including both controller and PHY with CEC and HDCP 2,2, 4Kx2K@60 max resolution

output.

This section -level registers only. HDMITX module instantiates two IPs HDMI TX Controller and

HDCP2.2 Controller. These two IPs internal registers are specified by the correspond

Register Description

HDMITX Top-Level and HDMI TX Contoller IP Register Access

Accessing HDMITX Top-Level and TX Controller IP registers is by indirectly accessing two memory addresses, one of the

addresses is mapped to register address, the other one is mapped to read/write data. There is also an extra address for access

control. See Table below.

Table IV.29.4 HDMITX Top-Level

Level and TX Controller register access ports

Absolute Address Mnemonic Bit(s) Default Description

Address

0xda83a000 HDMITX_ADDR_PORT [31:0] 0 Map to register address.

0xda83a004 HDMITX_DATA_PORT [31:0] 0 Map to register read/write data.

0xda83a008 HDMITX_CTRL_PORT [31:0] 0x3ff Register access control. See Table1.1.

Table IV.29.5 HDMITX Control Port for register access

Bit(s) R/W Default Description

31:16 R 0 Reserved.

15 RW 0 err_en:

0=No limit on PREADY wait time;

1=Enable APB access PREADY watchdog timer.

14 W 0 stack_err_clr.

1=Clear stack_err.

Always read back 0.

13 R 0 stack_err.

1=Stack over/underflow.

12 RW 0 stack_enable.

Control whether to stack the indirect reg access sequence, in case register access is interrupted by an interrupt

that also indirectly access HDMITX.

0=Old behaviour that does not support interruption;

1=Enable stack function.

11:0 RW 0x3ff max_err:

If err_en=1, maximum number of APB clock cycle wait time for PREADY assertion, before it asserts APB access

error.

Table IV.29.6 HDMITX sub-module base address

Base Address Module Name Description

0x00 dev_offset_top Device address offset for AmLogic top-level wrapper that instantiates the IPs.

0x10 dev_offset_dwc Device address offset for HDMI TX Controller IP module.

To write to a Top-level register:

*((volatile uint32_t *) (HDMITX_ADDR_PORT+dev_offset_top)) = addr;

*((volatile uint32_t *) (HDMITX_DATA_PORT+dev_offset_top)) = data;

To write to a TX controller IP register:

349/554 AMLOGIC, Inc. Proprietary

S912 Datasheet Revision 0.1

*((volatile uint32_t *) (HDMITX_ADDR_PORT+dev_offset_dwc)) = addr;

*((volatile uint32_t *) (HDMITX_DATA_PORT+dev_offset_dwc)) = data;

To read from a Top-level register:

*((volatile uint32_t *) (HDMITX_ADDR_PORT+dev_offset_top)) = addr;

data = *((volatile uint32_t *) (HDMITX_DATA_PORT+dev_offset_top));

To read from a TX controller IP register:

*((volatile uint32_t *) (HDMITX_ADDR_PORT+dev_offset_dwc)) = addr;

data = *((volatile uint32_t *) (HDMITX_DATA_PORT+dev_offset_dwc));

HDCP2.2 IP Register Access

Table IV.29.7 HDCP2.2 IP register base address

Absolute Address Mnemonic Description

Address

0xd0044000 ELP_ESM_HPI_REG_BASE Address base to HDCP2.2 IP register access.

To write to an HDCP2.2 IP register:

*((volatile uint32_t *) (ELP_ESM_HPI_REG_BASE+addr)) = data;

To read from an HDCP2.2 IP register:

data = *((volatile uint32_t *) (ELP_ESM_HPI_REG_BASE+addr));

Table IV.29.8 HDMITX Top-Level

Top Level Registers

Addr Name RW Function

0x000 HDMITX_TOP_SW_RESET RW Software reset sub-modules.

0x001 HDMITX_TOP_CLK_CNTL RW Clock gating and inversion.

0x002 HDMITX_TOP_HPD_FILTER RW HPD input glitch filter.

0x003 HDMITX_TOP_INTR_MASKN RW Interrupt mask.

0x004 HDMITX_TOP_INTR_STAT RW Interrupt status.

0x005 HDMITX_TOP_INTR_STAT_CLR W Interrupt clear.

0x006 HDMITX_TOP_BIST_CNTL RW Build-In Self Test(BIST) control.

0x007 HDMITX_TOP_SHIFT_PTTN_012 RW Shift pattern for BIST.

0x008 HDMITX_TOP_SHIFT_PTTN_345 RW Shift pattern for BIST.

0x009 HDMITX_TOP_SHIFT_PTTN_67 RW Shift pattern for BIST.

0x00A HDMITX_TOP_TMDS_CLK_PTTN_01 RW TMDS clock pattern for generating /10 or /40 rate clock.

0x00B HDMITX_TOP_TMDS_CLK_PTTN_23 RW TMDS clock pattern for generating /10 or /40 rate clock.

0x00C HDMITX_TOP_TMDS_CLK_PTTN_CNTL RW TMDS clock pattern for generating /10 or /40 rate clock.

0x00D HDMITX_TOP_REVOCMEM_STAT RW Revocmem status

0x00E HDMITX_TOP_STAT0 RW Status.

0x010 HDMITX_TOP_SKP_CNTL_STAT RW SKP interface control for HDCP2.2.

0x011 HDMITX_TOP_NONCE_0 W Nonce[31:0] for HDCP2.2.

0x012 HDMITX_TOP_NONCE_1 W Nonce[63:32] for HDCP2.2.

0x013 HDMITX_TOP_NONCE_2 W Nonce[95:64] for HDCP2.2.

0x014 HDMITX_TOP_NONCE_3 W Nonce[127:96] for HDCP2.2.

0x015 HDMITX_TOP_PKF_0 W PKF[31:0] for HDCP2.2.

0x016 HDMITX_TOP_PKF_1 W PKF[63:32] for HDCP2.2.

0x017 HDMITX_TOP_PKF_2 W PKF[95:64] for HDCP2.2.

0x018 HDMITX_TOP_PKF_3 W PKF[127:96] for HDCP2.2.

0x019 HDMITX_TOP_DUK_0 W DUK [31:0] for HDCP2.2.

0x01A HDMITX_TOP_DUK_1 W DUK [63:32] for HDCP2.2.

0x01B HDMITX_TOP_DUK_2 W DUK [95:64] for HDCP2.2.

0x01C HDMITX_TOP_DUK_3 W DUK [127:96] for HDCP2.2.

0x01D HDMITX_TOP_INFILTER RW DDC and CEC input glitch filter control.

350/554 AMLOGIC, Inc. Proprietary

You might also like

- Porsche 912E Service InformationDocument47 pagesPorsche 912E Service InformationOscar Hamer100% (1)

- Probability of GodDocument10 pagesProbability of Godzahoor80No ratings yet

- PP3 C878e3Document612 pagesPP3 C878e3Ricardo LimaNo ratings yet

- Digital Systems - Mini AVR 5: Pere Pal' A - Alexis L OpezDocument15 pagesDigital Systems - Mini AVR 5: Pere Pal' A - Alexis L OpezPau Susin AlsinaNo ratings yet

- SD - REG9 - ICTL 0xc1108e24Document3 pagesSD - REG9 - ICTL 0xc1108e24asdasdasfli.elkinNo ratings yet

- Lecture 4-5 - ARM - Assembly - 3 (New)Document33 pagesLecture 4-5 - ARM - Assembly - 3 (New)abdelkarim.haider.7No ratings yet

- EE 224 Project 1 CPU IITBDocument5 pagesEE 224 Project 1 CPU IITBSenseiNo ratings yet

- S912 Datasheet Revision 0.1Document6 pagesS912 Datasheet Revision 0.1asdasdasfli.elkinNo ratings yet

- 8051 Unit ViDocument34 pages8051 Unit ViBhaskarReddyVangalaNo ratings yet

- Ip5306 Reg V1.4Document9 pagesIp5306 Reg V1.4Jonathan Llewellyn AndradaNo ratings yet

- XCH - Exchange - AVR AssemblerDocument1 pageXCH - Exchange - AVR AssemblerRegard'sDexterZacheusNo ratings yet

- Kylin SATA Arch DraftDocument34 pagesKylin SATA Arch DraftАндрашNo ratings yet

- Power Up Sequence: Sdram Device OperationDocument15 pagesPower Up Sequence: Sdram Device OperationvetchboyNo ratings yet

- Assembly Language ProgrammingDocument11 pagesAssembly Language ProgrammingAnonymous 4mPIMAL7zNo ratings yet

- PRA1Document15 pagesPRA1najlaecasalsgraciaNo ratings yet

- Led On of ConinterrupcionDocument2 pagesLed On of ConinterrupcionManuel sotoNo ratings yet

- Load and Store InstructionsDocument32 pagesLoad and Store Instructionsmkollam100% (1)

- PCSRCDocument2 pagesPCSRCLord LightningNo ratings yet

- 6 AdvancedAssemblyDocument26 pages6 AdvancedAssemblyKillers YTNo ratings yet

- WOZPAK Sweet-16 Article 1Document13 pagesWOZPAK Sweet-16 Article 1Moe B. Us100% (1)

- AVR Instruction SetDocument149 pagesAVR Instruction SetbharatvishnuNo ratings yet

- LAB4İSTENENDocument4 pagesLAB4İSTENENmehifo9503No ratings yet

- PI CSE30 Lecture 4 Part2Document26 pagesPI CSE30 Lecture 4 Part2fmsarwarNo ratings yet

- Design With Microprocessors: Year III Computer Science 1-st Semester Lecture 2: AVR Registers and InstructionsDocument26 pagesDesign With Microprocessors: Year III Computer Science 1-st Semester Lecture 2: AVR Registers and InstructionsSelmaGogaNo ratings yet

- ATtiny13, ATtiny2313, Instruction SetDocument19 pagesATtiny13, ATtiny2313, Instruction SetMihai PaunNo ratings yet

- 16C550 UartDocument18 pages16C550 UartChilly KewlNo ratings yet

- Each Bit Reset Each ChannelDocument4 pagesEach Bit Reset Each Channelasdasdasfli.elkinNo ratings yet

- 8051 ArchitectureDocument37 pages8051 ArchitectureALNo ratings yet

- EEE 204 - Lecture4Document27 pagesEEE 204 - Lecture4furkanarslan1285No ratings yet

- Lecture15 PDFDocument21 pagesLecture15 PDFTimothy EngNo ratings yet

- ATmega Set de InstruccionesDocument160 pagesATmega Set de Instruccionesdav.mova736No ratings yet

- Slide 05Document121 pagesSlide 05sαєєd αнмєd кαLωαrNo ratings yet

- ATmega Instruction SetDocument155 pagesATmega Instruction SetBình MaiNo ratings yet

- Lec 3Document8 pagesLec 3irtaxa60No ratings yet

- Micro 1Document13 pagesMicro 1Ahmed Razi UllahNo ratings yet

- Details About PIC InstructionsDocument41 pagesDetails About PIC InstructionsIdriss KhaldiNo ratings yet

- Openldi Interface Blocks For Qsys: Chris Esser Staff Product Fae November 16, 2015Document10 pagesOpenldi Interface Blocks For Qsys: Chris Esser Staff Product Fae November 16, 2015Santoshkumar MalabagiNo ratings yet

- 00.50.0023 B Yoyok WP LAMPIRANDocument21 pages00.50.0023 B Yoyok WP LAMPIRAN084Febe Zaman DatuNo ratings yet

- CODch 5 SlidesDocument118 pagesCODch 5 SlidesRajesh cNo ratings yet

- Arduino and Stepper MotorDocument5 pagesArduino and Stepper Motorchandramahesh736No ratings yet

- S3C2410 Developer Notice 030204Document7 pagesS3C2410 Developer Notice 030204ydongyolNo ratings yet

- EL203 Lec8Document42 pagesEL203 Lec8D StarNo ratings yet

- DDR SdramDocument28 pagesDDR SdramSrujana Reddy N.V.No ratings yet

- LC320Instructions 144663026Document16 pagesLC320Instructions 144663026Đức KhánhNo ratings yet

- Register Device Type Range Format Notes: Recipe DataDocument2 pagesRegister Device Type Range Format Notes: Recipe DataAlberto MolinaNo ratings yet

- Lecture6-Bit AddressabilityDocument27 pagesLecture6-Bit AddressabilityJawad shah SayedNo ratings yet

- Keyboard Input: Provides Multiplexed DisplayDocument6 pagesKeyboard Input: Provides Multiplexed Display5016 V.GayathriNo ratings yet

- 04 AVR ALU and SREG SetDocument12 pages04 AVR ALU and SREG SetDerbendeNo ratings yet

- FA21 - Lec04-2021-09-25 - RISC, Branching and LoopingDocument18 pagesFA21 - Lec04-2021-09-25 - RISC, Branching and LoopingMahreenNo ratings yet

- 8051 Memory Space, RAM-ROM OrganizationDocument28 pages8051 Memory Space, RAM-ROM OrganizationShikharNo ratings yet

- Example 13 ADD ADD r4: BranchDocument13 pagesExample 13 ADD ADD r4: BranchR INI BHANDARINo ratings yet

- ModbusConfig V1 01Document1 pageModbusConfig V1 01pedro pabloNo ratings yet

- Cap 11 - RISC-V - Parte IDocument22 pagesCap 11 - RISC-V - Parte IGuidoNo ratings yet

- COS10004 Lecture 8.2 - LED FLash (Part 2) - Busy Wait TimerDocument20 pagesCOS10004 Lecture 8.2 - LED FLash (Part 2) - Busy Wait TimerHồ Thành AnNo ratings yet

- Week 04Document68 pagesWeek 04aroosa naheedNo ratings yet

- Design Task 1 Final LabDocument15 pagesDesign Task 1 Final Labrazorblademk2No ratings yet

- Lecture8 8051 Instruction Set ReviewDocument35 pagesLecture8 8051 Instruction Set ReviewdineshlathiaNo ratings yet

- Lab 7 ADCDocument19 pagesLab 7 ADCakkauntdlyaigrichegotoescheNo ratings yet

- Addressing Modes (Part 1)Document2 pagesAddressing Modes (Part 1)Aadhya JyothiradityaaNo ratings yet

- Each Bit Reset Each ChannelDocument4 pagesEach Bit Reset Each Channelasdasdasfli.elkinNo ratings yet

- S912 Datasheet Revision 0.1Document6 pagesS912 Datasheet Revision 0.1asdasdasfli.elkinNo ratings yet

- 14.4. Register Description: 14.4.1. I2C - M - 0 - CONTROL - REG 0x2140Document3 pages14.4. Register Description: 14.4.1. I2C - M - 0 - CONTROL - REG 0x2140asdasdasfli.elkinNo ratings yet

- Isa - Timerg CBUS: 0x2666Document3 pagesIsa - Timerg CBUS: 0x2666asdasdasfli.elkinNo ratings yet

- 9.3.7. GPIO 4 7 Pin Select: 0x2622: S805 Datasheet Revision 0.8Document3 pages9.3.7. GPIO 4 7 Pin Select: 0x2622: S805 Datasheet Revision 0.8asdasdasfli.elkinNo ratings yet

- Func Ti OnsDocument3 pagesFunc Ti Onsasdasdasfli.elkinNo ratings yet

- 8.2.1. GPIO Bank X: S805 Datasheet Revision 0.8Document5 pages8.2.1. GPIO Bank X: S805 Datasheet Revision 0.8asdasdasfli.elkinNo ratings yet

- Altera MAX II Family IntroductionDocument6 pagesAltera MAX II Family Introductionasdasdasfli.elkinNo ratings yet

- Simplecv: "Exit " "CTRL+ D" "Clear" "Tutorial" "Example" "Forums" "Walkthrough"Document5 pagesSimplecv: "Exit " "CTRL+ D" "Clear" "Tutorial" "Example" "Forums" "Walkthrough"asdasdasfli.elkinNo ratings yet

- R8M DataSheet V02Document14 pagesR8M DataSheet V02asdasdasfli.elkinNo ratings yet

- Chapter 3 C Language and Arduino Type Ide For Pcduino: Toolchain of The Arduino LibraryDocument3 pagesChapter 3 C Language and Arduino Type Ide For Pcduino: Toolchain of The Arduino Libraryasdasdasfli.elkinNo ratings yet

- Bioemg Iii: Bioresearch Assoc. IncDocument3 pagesBioemg Iii: Bioresearch Assoc. Incasdasdasfli.elkinNo ratings yet

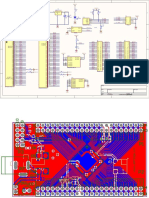

- EPM240MAINBOARD Schematic DiagramDocument2 pagesEPM240MAINBOARD Schematic Diagramasdasdasfli.elkinNo ratings yet

- MAX II Device Family DatasheetDocument86 pagesMAX II Device Family Datasheetasdasdasfli.elkinNo ratings yet

- Lesson Plan in Relation and FunctionsDocument5 pagesLesson Plan in Relation and FunctionsRexander TecalaNo ratings yet

- Analysis and Design of Projects in UaeDocument5 pagesAnalysis and Design of Projects in UaealbfaragNo ratings yet

- Electromagnetic Effects Part 1Document16 pagesElectromagnetic Effects Part 1SamuelGideonSimatupaNo ratings yet

- Number BasesDocument4 pagesNumber BasesHabib MohammedNo ratings yet

- The DL8000 Preset ControllerDocument8 pagesThe DL8000 Preset ControllerMarcio Vieira Santana100% (1)

- OAPT - Grade 11 Physics Contest - 2012 OAPT Grade 11 Physics ContestDocument7 pagesOAPT - Grade 11 Physics Contest - 2012 OAPT Grade 11 Physics ContestMircea PanteaNo ratings yet

- اخطاء انكسار 4Document4 pagesاخطاء انكسار 4Hassan AljaberiNo ratings yet

- 1.5 Inverse Functions & LogarithmsDocument11 pages1.5 Inverse Functions & Logarithms郭大維No ratings yet

- 10.1007/978 3 319 63324 4Document572 pages10.1007/978 3 319 63324 4Alexandre Champagne100% (1)

- 4.2 Costs, Scale of Production and Break-Even Analysis - LearnerDocument23 pages4.2 Costs, Scale of Production and Break-Even Analysis - LearnerDhivya Lakshmirajan100% (1)

- Inspection Checklist: Analyzers / Analyzer Shelters and Racks - Material Receiving STG Project 10-01759-001 EnppiDocument9 pagesInspection Checklist: Analyzers / Analyzer Shelters and Racks - Material Receiving STG Project 10-01759-001 EnppiTariqMalikNo ratings yet

- Iso 2896 - 2001 eDocument16 pagesIso 2896 - 2001 ehappyhandslearningcenter2023No ratings yet

- TMS RamSan620 DataSheetDocument2 pagesTMS RamSan620 DataSheetNaga Prasad PonnaNo ratings yet

- Mitigating Congestion in Wireless Sensor NetworksDocument14 pagesMitigating Congestion in Wireless Sensor NetworksIglesia RestauracionNo ratings yet

- Sem 3 Module 1Document3 pagesSem 3 Module 1fczeroNo ratings yet

- Adaptive Partitioning User's Guide: QNX Software Development Platform 6.6Document98 pagesAdaptive Partitioning User's Guide: QNX Software Development Platform 6.6Larken BradynNo ratings yet

- Module-5 3Document5 pagesModule-5 322-02923No ratings yet

- IIT JEE Main Advnaced Inorganic Chemistry 11th N&O Family PDFDocument58 pagesIIT JEE Main Advnaced Inorganic Chemistry 11th N&O Family PDFSesha Sai Kumar0% (1)

- ABC Guide To Temporary Pipework-Feb 2012 Rev5-SDocument84 pagesABC Guide To Temporary Pipework-Feb 2012 Rev5-SKwesi Edwards100% (2)

- Sir Mark ExamDocument5 pagesSir Mark ExamMark Gil GuillermoNo ratings yet

- Shannon Boettcher SeminarDocument45 pagesShannon Boettcher SeminarUCSBieeNo ratings yet

- Energies 14 00048Document41 pagesEnergies 14 00048Ayman EshraNo ratings yet

- Predictive Analysis For Big Mart Sales Using MachineDocument11 pagesPredictive Analysis For Big Mart Sales Using Machine563 K. VaishnaviNo ratings yet

- The Effects of Corporate Brand Attributes On Attitudinal and Behavioural Consumer LoyaltyDocument12 pagesThe Effects of Corporate Brand Attributes On Attitudinal and Behavioural Consumer LoyaltyjoannakamNo ratings yet

- Team Member Application Team Member Application Team Member Application Team Member ApplicationDocument35 pagesTeam Member Application Team Member Application Team Member Application Team Member ApplicationAnanth Nag PusalaNo ratings yet

- Copying Data From Microsoft Excel To ABAP Using OLEDocument10 pagesCopying Data From Microsoft Excel To ABAP Using OLERicky DasNo ratings yet

- Nta 855G Series PDFDocument4 pagesNta 855G Series PDFcalebwpbNo ratings yet