Professional Documents

Culture Documents

Module 1 Lpvlsi

Module 1 Lpvlsi

Uploaded by

anilm130484me0 ratings0% found this document useful (0 votes)

17 views48 pages1) As transistor density and operating frequencies increase due to Moore's Law, power dissipation of VLSI chips also increases, creating a need for low power chips.

2) Battery life is an important factor for portable electronics, translating to a need for lower power usage. High performance computing systems also drive low power needs due to their large power dissipation.

3) Power dissipation impacts packaging and cooling costs, as well as power supply and noise immunity design challenges. Environmental concerns around efficient energy usage also contribute to demands for low power chips and systems.

Original Description:

asdf

Original Title

module 1 lpvlsi

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Document1) As transistor density and operating frequencies increase due to Moore's Law, power dissipation of VLSI chips also increases, creating a need for low power chips.

2) Battery life is an important factor for portable electronics, translating to a need for lower power usage. High performance computing systems also drive low power needs due to their large power dissipation.

3) Power dissipation impacts packaging and cooling costs, as well as power supply and noise immunity design challenges. Environmental concerns around efficient energy usage also contribute to demands for low power chips and systems.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

17 views48 pagesModule 1 Lpvlsi

Module 1 Lpvlsi

Uploaded by

anilm130484me1) As transistor density and operating frequencies increase due to Moore's Law, power dissipation of VLSI chips also increases, creating a need for low power chips.

2) Battery life is an important factor for portable electronics, translating to a need for lower power usage. High performance computing systems also drive low power needs due to their large power dissipation.

3) Power dissipation impacts packaging and cooling costs, as well as power supply and noise immunity design challenges. Environmental concerns around efficient energy usage also contribute to demands for low power chips and systems.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 48

Need for Low power VLSI

1.Power dissipation of VLSI chips is traditionally a neglected subject. In

the past, the device density and operating frequency were low . As the

scale of integration improves, more transistors, faster and smaller than

their predecessors, are being packed into a chip. This leads to the steady

growth of the operating frequency and processing capacity per chip,

resulting in increased power dissipation.

2. There are various interpretations of the Moore s Law that predicts the

growth rate of integrated circuits. One estimate places the rate at 2X for

every eighteen months. A need for low power VLSI chips arises from

such evolution forces of integration circuits

3. Battery life is becoming a product differentiator in many portable

electronic markets. The craving for smaller, lighter and more durable

electronic products indirectly translates to low power requirements.

Continues …………………

4. High performance computing system characterized by large

power dissipation also drives the low power needs.

5. The power dissipation of high performance microprocessors

is now approaching several dozen Watts, comparable to that of

a hand-held soldering iron.

6. Power dissipation has a direct impact on the packaging cost

of the chip and the cooling cost of the system

7. A chip that operates at 3.3V consuming lOW means that the

average current is 3A. The transient current could be several

times larger than the average current. This creates problems in

the design of power supply rails and poses big challenges in the

analysis of digital noise immunity

8. Another major demand for low power chips and

systems comes from environmental concerns.

Computers are the fastest-growing electricity loads in the

commercial sector. Since electricity generation is a major

source of air pollution, inefficient energy usage in

computing equipment indirectly contributes to

environmental pollution.

The problem has prompted The US Environmental

Protection Agency and The US Department of Energy to

promote the Energy Star program

It’s the guidelines for the energy usage of computing

equipment.

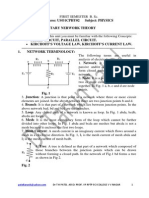

There are three sourses of power dissipation in CMOS Circuits

● Logic Transitions : The nodes in the CMOS circuits changes

back and forth between two logic level, leading to the

charging and discharging og the Parasitic capacitance. This

leads to power consumption

● Its Proportional to the supply Voltage , Node voltage swing

,and the average switched capacitance / cycle

● A layer of Insulator of Width “d” is sandwiched between metal Plate

and the semiconductor material.

● Assume the semiconductor of P type

● Voltage V is applied between Metal plate and substrate

● First consider V= 0,

● The energy difference between metal work function

and the semiconductor work function is Zero.

● wejgjgjgjgherheththhhhhhhh

Body Effect

Body effect refers to the change in the transistor threshold voltage (VT) resulting

from a voltage difference between the transistor source and body.

Short Channel Effect

• MOSFET Device is considered to be short when the

channel length is the same order of magnitude as the

depletion layer width of the source and drain junction .

• As the Channel length ( L) is reduced to increase both

operation and speed , and no. of components per chip,

the so called short channel effect arise.

Drain-induced barrier lowering (DIBL)

The electrons (carriers) in the channel face a potential

barrier that blocks their flows

The potential barrier, in small-geometry MOSFETs, is

controlled by a two-dimensional electric field vector (in

other words by both VGS and VDS)

If the drain voltage is increased the potential barrier in

the channel decreases, leading to

Drain-Induced Barrier Lowering (DIBL)

Drain-induced barrier lowering (DIBL) and Punchthrough

Under DIBL condiction electrons can flow between the

source and drain even if VGS < VT

The channel current that flows in this case is called

subthreshold current

Punchthrough

The DIBL phenomenon can be accompanied by the

so-called punchthrough, that occurs when the depletion

region surrounding the drain extends to the source

Punchthrough minimized with thinner oxide, larger

substrate doping (and longer channel!)

Punch through. Punch through in

a MOSFET is an extreme case of channel

length modulation where the depletion layers

around the drain and source regions merge

into a single depletion region. The field

underneath the gate then becomes strongly

dependent on the drain-source voltage, as is

the drain current.

Surface Scattering

• The velocity of the charge carriers is defined by the mobility of that

carrier times the electric field along the channel. When the carriers

travel along the channel, they are attracted to the surface by the

electric field created by the gate voltage.

• As a result, they keep crashing and bouncing against the surface,

during their travel, following a zig-zagging path. This effectively

reduces the surface mobility of the carriers, in comparison with their

bulk mobility.

• The change in carrier mobility impacts the current-voltage

relationship of the transistor.

Velocity-Saturation

• From the physics of semiconductors it is proved that the velocity of

charge carriers is linearly proportional to the electric field and the

proportionality constant is called as mobility of carrier.

• But when we increase the electric field beyond certain velocity called

as the thermal velocity or saturated velocity the velocity of the

charge carrier does not change with electric field as shown in Figure

below.

You might also like

- Ayyappa Prayer Book - MalayalamDocument38 pagesAyyappa Prayer Book - MalayalamSudarsana Kumar Vadasserikkara82% (17)

- 15A04802-Low Power VLSI Circuits & Systems - Two Marks Q&A-5 UnitsDocument31 pages15A04802-Low Power VLSI Circuits & Systems - Two Marks Q&A-5 UnitsPallavi Ch71% (7)

- Obsidian Rock+ Digitizer PDFDocument349 pagesObsidian Rock+ Digitizer PDFMoța FlorinNo ratings yet

- Low Power Design: Prof. A. K. SwainDocument28 pagesLow Power Design: Prof. A. K. SwainSrikanth PasumarthyNo ratings yet

- Minimization of Power Losses in Transmission Lines: Anyaka Boniface Onyemaechi, Olawoore Olaoluwa IsaacDocument4 pagesMinimization of Power Losses in Transmission Lines: Anyaka Boniface Onyemaechi, Olawoore Olaoluwa Isaacjose luisNo ratings yet

- Vlsi Design (Scaling)Document24 pagesVlsi Design (Scaling)ry7031978No ratings yet

- CMOS FundamentalsDocument96 pagesCMOS Fundamentalskvxrw7201No ratings yet

- CMOS Fundamentals Part2Document24 pagesCMOS Fundamentals Part2Bck SreedharNo ratings yet

- A Study On Multi Material Gate All Around SOI MOSFETDocument5 pagesA Study On Multi Material Gate All Around SOI MOSFETeditor_ijtelNo ratings yet

- Second Order EffectsDocument4 pagesSecond Order EffectsKancharana SarathchandraNo ratings yet

- Power MosfetsDocument17 pagesPower MosfetsKyaw SoeNo ratings yet

- LCPMOS TechniqueDocument72 pagesLCPMOS Techniqueadi_gopiNo ratings yet

- LPVLSI Unit 1 NotesDocument37 pagesLPVLSI Unit 1 NotesSai Sreeja100% (2)

- Leakage in Nanometer Scale CMOSDocument8 pagesLeakage in Nanometer Scale CMOSJimit GadaNo ratings yet

- An Evolutionary Transition of Conventional N MOS VLSI To CMOS Considering Scaling, Low Power and Higher MobilityDocument11 pagesAn Evolutionary Transition of Conventional N MOS VLSI To CMOS Considering Scaling, Low Power and Higher MobilityAJER JOURNALNo ratings yet

- Transformer Short Circuit Testing and Its Impact On Tap Changer FinalDocument6 pagesTransformer Short Circuit Testing and Its Impact On Tap Changer Finalsatheesh BabuNo ratings yet

- Term Paper of Ele-102: Topic:-Power and Distribution (Transformer'S Application)Document10 pagesTerm Paper of Ele-102: Topic:-Power and Distribution (Transformer'S Application)shailesh singhNo ratings yet

- Vacuum Circuit Breaker Capacitor Switching TechnologyDocument12 pagesVacuum Circuit Breaker Capacitor Switching TechnologyMohan K100% (2)

- Gopi Krishna Saramekala Assistant Professor: National Institute of Technology CalicutDocument56 pagesGopi Krishna Saramekala Assistant Professor: National Institute of Technology Calicutarjun raghavan.vNo ratings yet

- Limitations in ScalingDocument4 pagesLimitations in Scalingl_wondersNo ratings yet

- Transient Over VoltagesDocument38 pagesTransient Over Voltagesraghav4life8724No ratings yet

- Short Channel EffectsDocument6 pagesShort Channel EffectsRohanNo ratings yet

- Short Channel Effects and ScalingDocument23 pagesShort Channel Effects and ScalingskarthikpriyaNo ratings yet

- Electric Power TransmissionDocument4 pagesElectric Power Transmissionyibbabie tilahunNo ratings yet

- Punch ThroughDocument2 pagesPunch ThroughmodivivekNo ratings yet

- VLSI Design PPTDocument89 pagesVLSI Design PPTPavan S 4UB18EC024No ratings yet

- ThasisDocument77 pagesThasisSanjeev SinghNo ratings yet

- Malvika2022 Article AReviewOnANegativeCapacitanceFDocument15 pagesMalvika2022 Article AReviewOnANegativeCapacitanceFMD Salim EqubalNo ratings yet

- ElectromigrationDocument8 pagesElectromigrationRajniNo ratings yet

- Electric Power Transmission and DistributionDocument4 pagesElectric Power Transmission and DistributionAnupam Banerjee100% (1)

- Ultra Low Power DesignDocument8 pagesUltra Low Power DesignCHARANNo ratings yet

- 1 Low-Voltage Current-Mode Analog Cells Mohit Kumar Iit Bomb Ay 2002Document16 pages1 Low-Voltage Current-Mode Analog Cells Mohit Kumar Iit Bomb Ay 2002jaigodaraNo ratings yet

- Mod1 (2) - EC464 Low Power VLSI Design-Ktustudents - inDocument40 pagesMod1 (2) - EC464 Low Power VLSI Design-Ktustudents - insurya sundarNo ratings yet

- Mod1 (2) - EC464 Low Power VLSI Design-Ktustudents - inDocument40 pagesMod1 (2) - EC464 Low Power VLSI Design-Ktustudents - insurya sundarNo ratings yet

- A Lecture On Current LimiterDocument25 pagesA Lecture On Current LimiterLavanya VallbhareddyNo ratings yet

- Design of Transmission Line Using MatlabDocument12 pagesDesign of Transmission Line Using Matlabdensus88 densus89No ratings yet

- Electric Power TransmissionDocument42 pagesElectric Power TransmissionEarl Jay UayanNo ratings yet

- Lec14 DTMOSDocument88 pagesLec14 DTMOSSalim SanNo ratings yet

- Investigation of Dielectric Modulated DG-MOSFET With Different Configuration For Biosensor ApplicationsDocument25 pagesInvestigation of Dielectric Modulated DG-MOSFET With Different Configuration For Biosensor ApplicationsAnand KumarNo ratings yet

- Literature Review On Wireless Power TransmissionDocument7 pagesLiterature Review On Wireless Power TransmissionaflsqrbnqNo ratings yet

- Short Circuit Dissipation in CMOS Static Circuits and Its Impact On Buffer CircuitsDocument3 pagesShort Circuit Dissipation in CMOS Static Circuits and Its Impact On Buffer CircuitsNeelam AryaNo ratings yet

- LPVLSIDocument25 pagesLPVLSIAnil Kumar YernintiNo ratings yet

- Low Power VLSI Design: Abdulla K PDocument30 pagesLow Power VLSI Design: Abdulla K PVijay KumarNo ratings yet

- Microwave Tube Principles: Neets To Electronic Emission, Tubes, and Power SuppliesDocument5 pagesMicrowave Tube Principles: Neets To Electronic Emission, Tubes, and Power SupplieshelenarajNo ratings yet

- Mosfet PDFDocument13 pagesMosfet PDFTad-electronics TadelectronicsNo ratings yet

- Mesin Mesin ListrikDocument7 pagesMesin Mesin ListrikMerah Mirza YoshiokaNo ratings yet

- Nanometer MOSFETDocument12 pagesNanometer MOSFETSibi ManojNo ratings yet

- VLSIDocument130 pagesVLSIMrinal Sinha100% (2)

- VLSI NotesDocument130 pagesVLSI NotesOrcus DantalianNo ratings yet

- Scaling of MOSFETs and Short Channel EffectsDocument35 pagesScaling of MOSFETs and Short Channel EffectsAnonymous zn5X2z0% (1)

- EHV Sheath Earthing SystemDocument9 pagesEHV Sheath Earthing SystemZul FadzlyNo ratings yet

- Analytical Modeling of Double Gate MosfeDocument57 pagesAnalytical Modeling of Double Gate MosfeVijaya Kumar100% (1)

- Ipst PDFDocument6 pagesIpst PDFalexanderlimaNo ratings yet

- CMOS Power Dissipation VL9252Document6 pagesCMOS Power Dissipation VL9252Rohith RajNo ratings yet

- It Is Quite Another Electricity: Transmitting by One Wire and Without GroundingFrom EverandIt Is Quite Another Electricity: Transmitting by One Wire and Without GroundingNo ratings yet

- Relevant Characteristics of Power Lines Passing through Urban AreasFrom EverandRelevant Characteristics of Power Lines Passing through Urban AreasNo ratings yet

- Introduction to Electricity Supply and Regulation in IndiaFrom EverandIntroduction to Electricity Supply and Regulation in IndiaNo ratings yet

- Heat PipeDocument3 pagesHeat Pipeanilm130484meNo ratings yet

- Student Atendance Not Marked Periods ReportDocument4 pagesStudent Atendance Not Marked Periods Reportanilm130484meNo ratings yet

- HammerDocument12 pagesHammeranilm130484meNo ratings yet

- Graduation Day 2021 - Fee PaymentDocument10 pagesGraduation Day 2021 - Fee Paymentanilm130484meNo ratings yet

- Book 1Document2 pagesBook 1anilm130484meNo ratings yet

- AnvilDocument8 pagesAnvilanilm130484meNo ratings yet

- HPLCDocument4 pagesHPLCanilm130484meNo ratings yet

- Heat ExchangeDocument4 pagesHeat Exchangeanilm130484meNo ratings yet

- Black, White, Orange and Blue Minimalist PHD Dissertation PresentationDocument33 pagesBlack, White, Orange and Blue Minimalist PHD Dissertation Presentationanilm130484meNo ratings yet

- UltrasonicsDocument39 pagesUltrasonicsanilm130484meNo ratings yet

- LASERDocument30 pagesLASERanilm130484meNo ratings yet

- MET 203 MOF SERIES TEST 1 QP SchemeDocument2 pagesMET 203 MOF SERIES TEST 1 QP Schemeanilm130484meNo ratings yet

- Module 1Document87 pagesModule 1anilm130484meNo ratings yet

- Why Does The Conservation of Momentum Equation For Fluid Mechanics Use Gauge Instead of Absolute PressureDocument2 pagesWhy Does The Conservation of Momentum Equation For Fluid Mechanics Use Gauge Instead of Absolute Pressureanilm130484me0% (1)

- Retardation TestDocument1 pageRetardation Testanilm130484meNo ratings yet

- Module 5Document40 pagesModule 5anilm130484meNo ratings yet

- 28 - 4400 MCQ - IES - GATE - PSUs Mechanical EngineeringDocument21 pages28 - 4400 MCQ - IES - GATE - PSUs Mechanical Engineeringanilm130484meNo ratings yet

- Half LoadDocument2 pagesHalf Loadanilm130484meNo ratings yet

- Swami SharanamDocument4 pagesSwami Sharanamanilm130484meNo ratings yet

- Retardation Test ExDocument6 pagesRetardation Test Exanilm130484meNo ratings yet

- Condenser S and Cooling Towers: By, Prof. M.B. GohilDocument55 pagesCondenser S and Cooling Towers: By, Prof. M.B. Gohilanilm130484meNo ratings yet

- Paper 9, Module 26, ETextDocument11 pagesPaper 9, Module 26, ETextanilm130484meNo ratings yet

- Numerical Study On Hydrodynamic Behaviour of Bubbling Fluidized Bed in Biogas GasifierDocument12 pagesNumerical Study On Hydrodynamic Behaviour of Bubbling Fluidized Bed in Biogas Gasifieranilm130484meNo ratings yet

- DrillingDocument27 pagesDrillinganilm130484meNo ratings yet

- Schematically Shows The Open and Cross Belt Drive Quick Return Quick Return Mechanism of A PlanerDocument6 pagesSchematically Shows The Open and Cross Belt Drive Quick Return Quick Return Mechanism of A Planeranilm130484meNo ratings yet

- Analysis and Design of MosfetDocument355 pagesAnalysis and Design of MosfetnewgenerationNo ratings yet

- AO2020 Modbus MapDocument34 pagesAO2020 Modbus MapcesarintiNo ratings yet

- Plano Manitou PDFDocument192 pagesPlano Manitou PDFHadas Alberto Herrera MirandaNo ratings yet

- Us01cphy02 Unit 1 2014 THPDocument18 pagesUs01cphy02 Unit 1 2014 THPapi-264723824No ratings yet

- SC-350S/D, SC - 350S/D, SC - 600S/D: All-Axis Servo Driven Type Take-Out RobotDocument1 pageSC-350S/D, SC - 350S/D, SC - 600S/D: All-Axis Servo Driven Type Take-Out Robotbagas prakosoNo ratings yet

- Unit 2 DDocument31 pagesUnit 2 DShaleva SinghNo ratings yet

- Trouble Shooting GuideDocument18 pagesTrouble Shooting GuideDeyan VelikovNo ratings yet

- <!DOCTYPE HTML PUBLIC "-//W3C//DTD HTML 4.01 Transitional//EN" "http://www.w3.org/TR/html4/loose.dtd"> <HTML><HEAD><META HTTP-EQUIV="Content-Type" CONTENT="text/html; charset=iso-8859-1"> <TITLE>ERROR: The requested URL could not be retrieved</TITLE> <STYLE type="text/css"><!--BODY{background-color:#ffffff;font-family:verdana,sans-serif}PRE{font-family:sans-serif}--></STYLE> </HEAD><BODY> <H1>ERROR</H1> <H2>The requested URL could not be retrieved</H2> <HR noshade size="1px"> <P> While trying to process the request: <PRE> TEXT http://www.scribd.com/titlecleaner?title=Bridges_1993compressed.pdf HTTP/1.1 Host: www.scribd.com Proxy-Connection: keep-alive Cache-Control: max-age=0 Accept: */* Origin: http://www.scribd.com X-CSRF-Token: 32c7217e2e3c7d2ff8dfc8507de87c3a2f52331e User-Agent: Mozilla/5.0 (Windows NT 6.0) AppleWebKit/537.22 (KHTML, like Gecko) Chrome/25.0.1364.97 Safari/537.22 X-Requested-With: XMLHttpRequest Referer: http://www.scribd.com/upload-document AccDocument166 pages<!DOCTYPE HTML PUBLIC "-//W3C//DTD HTML 4.01 Transitional//EN" "http://www.w3.org/TR/html4/loose.dtd"> <HTML><HEAD><META HTTP-EQUIV="Content-Type" CONTENT="text/html; charset=iso-8859-1"> <TITLE>ERROR: The requested URL could not be retrieved</TITLE> <STYLE type="text/css"><!--BODY{background-color:#ffffff;font-family:verdana,sans-serif}PRE{font-family:sans-serif}--></STYLE> </HEAD><BODY> <H1>ERROR</H1> <H2>The requested URL could not be retrieved</H2> <HR noshade size="1px"> <P> While trying to process the request: <PRE> TEXT http://www.scribd.com/titlecleaner?title=Bridges_1993compressed.pdf HTTP/1.1 Host: www.scribd.com Proxy-Connection: keep-alive Cache-Control: max-age=0 Accept: */* Origin: http://www.scribd.com X-CSRF-Token: 32c7217e2e3c7d2ff8dfc8507de87c3a2f52331e User-Agent: Mozilla/5.0 (Windows NT 6.0) AppleWebKit/537.22 (KHTML, like Gecko) Chrome/25.0.1364.97 Safari/537.22 X-Requested-With: XMLHttpRequest Referer: http://www.scribd.com/upload-document Acceverest2007No ratings yet

- P-Q Controls, Inc.: Operations Manual Model 504 / 514 / 524 / 534Document5 pagesP-Q Controls, Inc.: Operations Manual Model 504 / 514 / 524 / 534eng_hamada_4uNo ratings yet

- ABB MV Switchgear - Single Busbar or Double Busbar - PDFDocument6 pagesABB MV Switchgear - Single Busbar or Double Busbar - PDFrod8silvaNo ratings yet

- SamsungDocument63 pagesSamsungHamza Abbasi AbbasiNo ratings yet

- Lecture 3 - Cable Sizing 2015Document22 pagesLecture 3 - Cable Sizing 2015Victor SaifiNo ratings yet

- Data Communications 2 ReviewerDocument6 pagesData Communications 2 ReviewerRechie VallenteNo ratings yet

- SCP6814 eDocument21 pagesSCP6814 eLê Minh Nguyên TriềuNo ratings yet

- Controlling Humidity of Nutrition Fog in Aerponic System Using Proportional - Integral MethodDocument10 pagesControlling Humidity of Nutrition Fog in Aerponic System Using Proportional - Integral MethodMax Salomon Cojab SaadNo ratings yet

- L3 - Wireless Communication PDFDocument76 pagesL3 - Wireless Communication PDFAbhishek KumarNo ratings yet

- RolandDG DXY880OCRDocument194 pagesRolandDG DXY880OCRCiborgSeptiembre0% (1)

- EEE 414 GRP 5 A2 Project ReportDocument46 pagesEEE 414 GRP 5 A2 Project Reporttiasa mondalNo ratings yet

- JBL 2412H Single Pack, 1 - Driver - Thomann UKDocument1 pageJBL 2412H Single Pack, 1 - Driver - Thomann UKAxel David ArteagaNo ratings yet

- t4300 Load SharerDocument4 pagest4300 Load SharerndukNo ratings yet

- DM 20Document12 pagesDM 20Hec AguNo ratings yet

- Alignment & AdjustmentDocument12 pagesAlignment & Adjustmentfalco2010No ratings yet

- Student'S Syllabus: Marine Electricity and Electrical MaintenanceDocument9 pagesStudent'S Syllabus: Marine Electricity and Electrical MaintenancemarpelNo ratings yet

- Young-Hwa: (Model No.: Yhass)Document8 pagesYoung-Hwa: (Model No.: Yhass)Diki NugrahaNo ratings yet

- Speed of Sound (Drinking Straw)Document10 pagesSpeed of Sound (Drinking Straw)JorgeNo ratings yet

- ALSTOM's Electrical Equipt - Chang Gong PresentationDocument20 pagesALSTOM's Electrical Equipt - Chang Gong PresentationJhen Gong ChengNo ratings yet

- Control StasDocument16 pagesControl StasSobe ThapaNo ratings yet

- Gujarat Technological University: InstructionsDocument2 pagesGujarat Technological University: InstructionsPritesh SaxenaNo ratings yet

- CSMA - CD Procedure Lecture NotesDocument3 pagesCSMA - CD Procedure Lecture Notestooba mukhtarNo ratings yet