Professional Documents

Culture Documents

Motor Drive Discrete Mosfet Bridge Circuit Design and Layout

Motor Drive Discrete Mosfet Bridge Circuit Design and Layout

Uploaded by

Juan DetemOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Motor Drive Discrete Mosfet Bridge Circuit Design and Layout

Motor Drive Discrete Mosfet Bridge Circuit Design and Layout

Uploaded by

Juan DetemCopyright:

Available Formats

AN296215 APPLICATION INFORMATION

MCO-0000999

P0084

MOTOR DRIVE DISCRETE MOSFET BRIDGE CIRCUIT

DESIGN AND LAYOUT

By Alistair Wood

Allegro MicroSystems

Introduction When QH is enabled the motor phase voltage will transi-

tion high, but during the transition, in addition to sourcing

This application note is intended to familiarize the reader the load current, QH must also source enough current to

with bridge circuit switching for motor drive applications. recover the low side body diode, and charge any parasitic

Recommendations for circuit design and layout to mitigate capacitance including the MOSFET intrinsic capacitances.

EMI and switching transients are provided.

This additional high-frequency loop current, IHFL, primar-

Bridge Circuit Switching Transients ily flows from the local ceramic decoupling capacitor CC,

Figure 1 shows the power section of a half-bridge discrete through the power transistors and gate driver circuitry to

MOSFET design. Typically during operation, QH and QL are ground. The aluminum electrolytic capacitor, CA, although

alternately enabled to regulate the current in the inductive larger in value, also has much higher parasitic inductance

motor winding. and resistance and primarily functions to replenish charge

on CC and provide supply decoupling for the lower fre-

ILFL quency load current loops. The high di/dt of the high

QH VBRG frequency loop current and resulting energy stored in the

CC CA parasitic inductance of the circuit components and PCB rout-

ing, can result in phase voltage overshoot which can exceed

GHx

the absolute maximum ratings of the gate drive circuitry if

Motor Phase

not mitigated.

Also, because power stage in Figure 1 has very little resis-

Sx ILOAD tance, the parasitic inductance and capacitance form a high

QL Q resonant circuit that can ring for many cycles if overshoot

is present.

GLx

IHFL For the example in Figure 1, where current is into the motor

phase, ringing will also be present when the phase volt-

LSS age goes low. On the falling transition, without the body

ILFL

CSxP diode recovery current, there is less risk of excessive voltage

CSxN RSHUNT PGND overshoot.

Although the example in Figure 1 illustrates the case when

the low-side body diode is forward biased, there is an analo-

Figure 1: Power section of half-bridge discrete MOSFET design gous case where the high-side body diode will forward bias

when current is flowing out of the motor phase.

The blue and green ILFL current paths illustrate the case when

the flow of current is unidirectional into the motor phase To limit the amount of overshoot and ringing, there are sev-

during the PWM cycle. For an initial state, assume that QL is eral preventative measures that can be taken:

on, synchronously rectifying the current recirculating around 1. Each half-bridge high-frequency power switching

the bottom of the half bridge. When transitioning from QL to loop, shown in red in Figure 1, should have a PCB

QH conducting, both drivers will typically be in the off state layout that minimizes the parasitic inductances around

during the dead time, and the body diode of QL will forward the loop and includes appropriate ceramic capacitors

bias for a short time to conduct the load current. to decouple the supply voltage.

AN296215 APPLICATION INFORMATION

MCO-0000999

P0084

2. To reduce EMI and high voltage overshoot, snubber placed to minimize the stray inductance and resistance

circuits should be used to dampen excessive motor around the high frequency current loop, marked with the red

phase ringing. dashed line.

3. The driver turn-on rate when recovering body diode CS RS

conduction should be limited to prevent excessive G

phase voltage overshoot. For gate drivers that have

PGND RSHUNT S QL D

internally programmable current gate drive, the gate

turn-on current can be set to control the switching

transients. Series gate resistors, which allow a limited - CC

CA MOTOR

degree of cross conduction, are an alternative effective

D S PHASE

method to control switching voltage transients. QH

+

4. Additional circuitry can be added to protect the gate G

RS

VBRG

driver if required. CS

These items will be covered in more detail in the subsequent Figure 3: PCB Layout

text. Controlling the bridge voltages in a high-power 48-volt

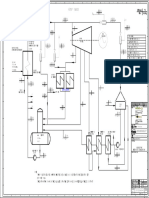

system can be challenging. To ensure a robust design, the Recommendations for the half bridge layout are:

absolute voltages of the gate drive circuity should not be 1. Arrange QL, QH , RSHUNT and CC in a tight loop, be-

exceeded. The terminal voltages present on the gate driver cause the parasitic loop inductance is a function of total

should be measured with a tip and barrel (spring clip) close loop distance.

to the gate driver. When measuring the terminal voltages, 2. Use wide PCB traces for the loop connections to

the time base of the oscilloscope should be short enough to minimize inductance and resistance and help dissipate

observe the peak voltages of the high-frequency transients. device heating.

The voltage transients should be verified over the full temper-

ature range, as they are often worst case at cold temperature. 3. Assuming a 4-layer PCB, PGND, and VBRG should

be connected to an internal PCB power ground and

Bridge Circuit Layout supply plane. These connections should be made with

numerous vias to carry the phase current and help with

QH VBRG thermal power dissipation.

CS

CC CA

4. The top-level metal pattern for the power loop should

GHx RS be duplicated on the bottom side of the PCB. These

top and bottom metal patterns should be connected

Motor Phase

with numerous vias to carry the phase current and help

with thermal power dissipation.

Sx

5. The snubber network connections should be made with

QL CS

short wide traces to reduce EMI and minimize parasitic

GLx RS inductance. Connections directly to the power and

ground planes should be avoided.

LSS 6. If more than one ceramic capacitor is used for CC, they

CSxP should be placed as close together as possible to avoid

CSxN RSHUNT PGND

forming a resonant LC circuit between the capacitors.

Typical values of CC are in the range of 2.2 to 4.7 µF.

The capacitance voltage and temperature coefficient

should be considered when selecting the value of CC.

Figure 2 : Bridge Circuit Layout

7. The half bridge layout can be replicated for other motor

In Figure 2, snubber networks have been added across the phases. To avoid potential interactions between half

power transistors to reduce EMI. Figure 3 shows an example bridges the PGND and VBRG connections should be

of component placement and top-level PCB metal pattern made to the internal power planes and not connected

for the half bridge in Figure 2. The components have been on the top and bottom PCB layers.

955 PERIMETER ROAD • MANCHESTER, NH 03103 • USA

+1-603-626-2300 • FAX: +1-603-641-5336 • ALLEGROMICRO.COM 2

AN296215 APPLICATION INFORMATION

MCO-0000999

P0084

Snubber Network Design

Assuming the snubber networks are not present in the circuit Equation 4: =

√

in Figure 2, the frequency of the motor phase voltage ringing

is given by:

Equation 5: =

1 × ×

Equation 1: =

2 √ × The power dissipation of the snubber resistors can be esti-

mated as:

where LP and CP are the equivalent sum series parasitic induc-

tance and capacitance of the power output stage. For the Equation 6:

snubber network to be effective in dampening ringing, CS = × ×( ×( + ) −( ) )

needs to be several times greater than CP. To reduce phase

voltage overshoot, the required value of CP can be consider- where fPWM is the motor phase PWM switching frequency,

ably higher depending on the speed of the output switching VOS is the value of any residual overshoot voltage, and the

and body diode reverse recovery characteristics. output is assumed to always be active. If there is no voltage

In practice, it is difficult to calculate the exact values of LP and overshoot this equation simplifies to:

CP from device specifications and examination of the PCB lay- Equation 7: = × ×

out. A practical way to determine the value of CP is to add a

known additional capacitance, CA, to the half-bridge output Once the calculated component values for CSN and RSN have

and observe the change in ringing frequency. been fitted to the PCB, some further tuning may be needed

Since most of the parasitic capacitance is due to the MOS- to improve performance. If the circuit is under-damped,

FET output capacitance, a reasonable value to select CA is increasing the resistance or capacitance will increase the

to use roughly four times the value of the MOSFET output dampening. If there is voltage overshoot present, and the

capacitance, COSS. The exact value is not critical, but it must design uses a gate drive turn-off that is considerably stronger

be large enough to observe an appreciable shift in frequency that the gate drive turn-on, increasing CSN while reducing

when added to the circuit. RSN can reduce the overshoot.

For the snubber capacitors, CS, it is best to use a low tem- Gate Drive Control Methods

perature and voltage coefficient ceramic capacitor to achieve

consistent snubbing performance across operating condi- Gate drivers are typically designed to drive a wide range of

tions. MOSFET devices that have dissimilar gate charge. Figure 4

shows an example of excessive overshoot and ringing that

If the PCB has been laid out to accommodate snubber com-

can occur when a high-current gate driver is used to drive a

ponents, RS can be replaced with a zero-ohm jumper and CA

low-capacitance MOSFET.

can be fitted in both CS locations.

By measuring the change in the ringing frequency from the

original circuit, fR, to the added capacitance case, fRA, the

approximate value of parasitic capacitance can be calculated

as:

Equation 2: = 2

−1

2

Once CP is known, the value of the parasitic inductance can

be approximated as:

1

Equation 3: =

× (2 )2

And first estimates for snubber network components can be

calculated as: Figure 4: Example of excessive overshoot and ringing

955 PERIMETER ROAD • MANCHESTER, NH 03103 • USA

+1-603-626-2300 • FAX: +1-603-641-5336 • ALLEGROMICRO.COM 3

AN296215 APPLICATION INFORMATION

MCO-0000999

P0084

In Figure 4, although the supply voltage is only 25 volts, the driver controls the high side MOSFET turn-off during the

output voltage at turn on reaches nearly 70 volts. For this negative output transition. The controlled gate discharge

case, the rapid turn-on of the high-side MOSFET results in a results in acceptable overshoot and minimal ringing that can

very high peak body diode recovery current of the low-side be further reduced with the addition of snubber networks.

MOSFET, which energizes the parasitic inductance, creating

the excessive overshoot and ringing. For the test condition in

Figure 4, no snubbing is present in the circuit.

Figure 7

In Figure 7, the gate driver is still the driving device, but the

Figure 5 current-limited gate drive is disabled, and 22-ohm series

gate resistors have been added to the high- and low-side

To better control MOSFET switching, many of the drivers

MOSFETs. Compared to Figure 4, the series gate resistor

manufactured by Allegro MicroSystems allow the user to

has increased the turn on time from 10 to 30 ns and the

program the gate drive current through SPI. Figure 5 shows

overshoot is well controlled. If series gate resistors are used,

same circuit as Figure 4, but in this case the gate driver has

to obtain similar results, the resistor value can be adjusted

been programmed to reduce the gate charging current

depending on the chosen MOSFET characteristics, keep-

during the initial high-side MOSFET turn-on and then boost

ing in mind the absolute maximum ratings of the gate driver

the drive current near the end of the switching to rapidly

and other circuit components. Snubber circuits are typically

enhance the MOSFET. With the slower initial turn-on, the

added to help reduce EMI due to output ringing.

peak diode recovery current is reduced, eliminating the

overshoot entirely. No snubbers or series gate resistors are

used for this case.

Figure 8

Figure 6 Figure 8 provides some additional insight on the effect of

using series gate resistors. The yellow and green traces are

In Figure 6, the programmable current gate drive of the gate the gate and source of the low side MOSFET, and the pink

955 PERIMETER ROAD • MANCHESTER, NH 03103 • USA

+1-603-626-2300 • FAX: +1-603-641-5336 • ALLEGROMICRO.COM 4

AN296215 APPLICATION INFORMATION

MCO-0000999

P0084

trace is the difference between these traces, the VGS of the During negative switching transients, because GHX is driven

low side MOSFET. When gate resistors are used, the MOS- with respect to SX, the SX negative clamp voltage will effec-

FET in the off-state, in this case the low-side MOSFET, will tively allow QH to remain conductive clamping the phase

partially turn on during switching transition, which helps to node at a negative voltage given by:

limit output overshoot at the expense of some cross conduc- Equation 8:

tion loss.

VCLNEG = – (VD2BV + VBDQ1 + VGSQH)

Gate Driver Protection Circuitry

Other shared clamp configurations are possible when R1

For some 48-volt designs with high switching speed require- is included. For information regarding gate drivers that are

ments, if after optimizing the PCB layout, gate drive, and compatible with resistance added in series with SX, refer to

snubber design, there are still excessive voltages on the specific device documentation or contact the applications

gate driver terminals, additional circuitry may be needed to support team.

protect the gate driver.

For the circuit in Figure 9, R1 has an impedance of 2 to

4 ohms and effectively decouples the motor phase from the

SX node of the gate driver so that the clamping circuit can

limit the voltage on the gate driver SX and CX terminals.

The breakdown voltage of D1 should be chosen to turn on Q1

to clamp the SX node voltage at less than the maximum rating

of the SX terminal. C1 and R2 act to keep Q1 off during normal

switching transients. Diode D2 can be chosen to allow SX to

be clamped at a negative voltage by conduction through the

body diode of Q1.

VBRG

Cx

CBOOT QH

GHx

Gate

Driver

Sx

R1

QL

SX Clamp D2

Circuit GLx

D1 Q1

C1

R2 LSS

CSxP

CSxN RSHUNT

Figure 9 : Gate driver protection circuitry

955 PERIMETER ROAD • MANCHESTER, NH 03103 • USA

+1-603-626-2300 • FAX: +1-603-641-5336 • ALLEGROMICRO.COM 5

AN296215 APPLICATION INFORMATION

MCO-0000999

P0084

Revision History

Number Date Description Responsibility

– November 19, 2020 Initial release A. Wood

Copyright 2020, Allegro MicroSystems.

The information contained in this document does not constitute any representation, warranty, assurance, guaranty, or induce-

ment by Allegro to the customer with respect to the subject matter of this document. The information being provided does

not guarantee that a process based on this information will be reliable, or that Allegro has explored all of the possible failure

modes. It is the customer’s responsibility to do sufficient qualification testing of the final product to insure that it is reliable and

meets all design requirements.

Copies of this document are considered uncontrolled documents.

955 PERIMETER ROAD • MANCHESTER, NH 03103 • USA

+1-603-626-2300 • FAX: +1-603-641-5336 • ALLEGROMICRO.COM

You might also like

- Design of A Synchronous Rectified Switching Regulator Chip For CPU Power SupplyDocument4 pagesDesign of A Synchronous Rectified Switching Regulator Chip For CPU Power SupplysrdjanNo ratings yet

- Wee4 EtDocument4 pagesWee4 EtlaboratorioNo ratings yet

- Isolated Bidirectional Full-Bridge DCDC Converter With A Flyback SnubberDocument8 pagesIsolated Bidirectional Full-Bridge DCDC Converter With A Flyback SnubberHsekum RamukNo ratings yet

- Based On UCC3895 Phase-Shift Full Bridge ZVZCS With Average Current Control Closed Loop Simulation and DesignDocument6 pagesBased On UCC3895 Phase-Shift Full Bridge ZVZCS With Average Current Control Closed Loop Simulation and DesigngarriyakNo ratings yet

- A Closed Loop Control of Buck Boost Ac Ac Converter With Reduced THDDocument9 pagesA Closed Loop Control of Buck Boost Ac Ac Converter With Reduced THDAndrés ToroNo ratings yet

- Low-Power Digital Systems Based On Adiabatic3 Witching PrinciplesDocument10 pagesLow-Power Digital Systems Based On Adiabatic3 Witching PrinciplesVishwas GosainNo ratings yet

- Fix3 33333333Document4 pagesFix3 33333333doanminhtien030903No ratings yet

- BER-37 Direct On Line Energization of Subsea Power Transformers1Document63 pagesBER-37 Direct On Line Energization of Subsea Power Transformers1Gopa KumarNo ratings yet

- Operation Principles of Bi-Directional Full-Bridge DCDC Converter With Unified Soft-Switching Scheme and Soft-Starting CapabilityDocument8 pagesOperation Principles of Bi-Directional Full-Bridge DCDC Converter With Unified Soft-Switching Scheme and Soft-Starting CapabilityJie99No ratings yet

- Grid Tie Inverter Schematic and Principals of OperationDocument6 pagesGrid Tie Inverter Schematic and Principals of Operation31482No ratings yet

- BGR Design TechniquesDocument4 pagesBGR Design Techniquessachin saxenaNo ratings yet

- A High-Efficiency QR Flyback DC-DC Converter WithDocument21 pagesA High-Efficiency QR Flyback DC-DC Converter WithRakesh SandarativjuNo ratings yet

- Energization of Subsea Power TransformerDocument9 pagesEnergization of Subsea Power Transformerchandraippa2No ratings yet

- Frequency Tracking Burst-Mode PDM-controlled Class-D Zero Voltage Soft-Switching Resonant Converter For Inductive Power Transfer ApplicationsDocument8 pagesFrequency Tracking Burst-Mode PDM-controlled Class-D Zero Voltage Soft-Switching Resonant Converter For Inductive Power Transfer ApplicationsLuis Alfonso Martinez FdezNo ratings yet

- Modeling The Effect of Dead-Time On The Soft-Switching Characteristic of Variable-Frequency Modulated Series-Resonant DAB ConverterDocument8 pagesModeling The Effect of Dead-Time On The Soft-Switching Characteristic of Variable-Frequency Modulated Series-Resonant DAB ConverterPatil MounicareddyNo ratings yet

- Predictive ZVS Control With Improved ZVS Time Margin and Limited Variable Frequency Range For A 99 Efficient 130-W In3 MHZ GaN Totem-Pole PFC RectifierDocument13 pagesPredictive ZVS Control With Improved ZVS Time Margin and Limited Variable Frequency Range For A 99 Efficient 130-W In3 MHZ GaN Totem-Pole PFC RectifierMuhammad Arsalan FarooqNo ratings yet

- Investigation On Capacitor Switching Transient Limiter With A Three Phase Variable ResistanceDocument6 pagesInvestigation On Capacitor Switching Transient Limiter With A Three Phase Variable ResistanceArohi RoyNo ratings yet

- AuxResionantCommuted PoleDocument8 pagesAuxResionantCommuted PoleAjit JainNo ratings yet

- Novel Zero-Current-Transition PWM Converters: Eric X. CDocument6 pagesNovel Zero-Current-Transition PWM Converters: Eric X. Ccarlos_eqnNo ratings yet

- Application Note AN-6076: Design and Application Guide of Bootstrap Circuit For High-Voltage Gate-Drive ICDocument13 pagesApplication Note AN-6076: Design and Application Guide of Bootstrap Circuit For High-Voltage Gate-Drive ICFeroz KhanNo ratings yet

- And Automotive 3-Phase BLDC Controller and MOSFET Driver: Description Features and BenefitsDocument21 pagesAnd Automotive 3-Phase BLDC Controller and MOSFET Driver: Description Features and BenefitsCanerNo ratings yet

- Paper 5 PDFDocument6 pagesPaper 5 PDFrhusheinNo ratings yet

- A Method To Reduce DC-link Overvoltage of PMSG Based WECS During LVRTDocument6 pagesA Method To Reduce DC-link Overvoltage of PMSG Based WECS During LVRTSagiraju DileepNo ratings yet

- SwitchmodePowerSupplies PDFDocument4 pagesSwitchmodePowerSupplies PDFDavidNo ratings yet

- A Schematic Adiabatic Design of Cmos Circuit For Measurement of Low Power DissipationDocument7 pagesA Schematic Adiabatic Design of Cmos Circuit For Measurement of Low Power DissipationSanjeev SinghNo ratings yet

- High-Power Density Design of A Soft-Switching High-Power Bidirectional DC-DC ConverterDocument9 pagesHigh-Power Density Design of A Soft-Switching High-Power Bidirectional DC-DC Convertermurthy237No ratings yet

- LatchupDocument3 pagesLatchuppraveenkumargodaNo ratings yet

- Design and Implementation of A High-Efficiency OnBoard Battery Charger For Electric Vehicles WithDocument6 pagesDesign and Implementation of A High-Efficiency OnBoard Battery Charger For Electric Vehicles Withrock starNo ratings yet

- A New, Soft-Switched, High-Power-Factor Boost Converter With IgbtsDocument8 pagesA New, Soft-Switched, High-Power-Factor Boost Converter With IgbtsNandish AcharlNo ratings yet

- AC-AC (DC Link) - B.H.KWon PDFDocument10 pagesAC-AC (DC Link) - B.H.KWon PDFBui DaiNo ratings yet

- Soft SW AC-AC PDFDocument4 pagesSoft SW AC-AC PDFBui DaiNo ratings yet

- An-703 Application Note: Driving High Power LedsDocument8 pagesAn-703 Application Note: Driving High Power LedsSebastiao RochaNo ratings yet

- Adiabatic SwitchingDocument10 pagesAdiabatic Switchingdhirajmore88No ratings yet

- Active Front EndDocument5 pagesActive Front EndDaleel LillaNo ratings yet

- The Lang 20W Class-A Mosfet AmplifierDocument7 pagesThe Lang 20W Class-A Mosfet AmplifiermoisesNo ratings yet

- An Integrated High-Power-Factor Converter With ZVS TransitionDocument10 pagesAn Integrated High-Power-Factor Converter With ZVS TransitionBook4AllNo ratings yet

- Triac Applications - Great TheoryDocument48 pagesTriac Applications - Great TheoryJeff MaxwellNo ratings yet

- 6919 UsingHighResolution BH 20210226 WebDocument9 pages6919 UsingHighResolution BH 20210226 WebJoão Márcio JorgeNo ratings yet

- Carrier Based Sinusodial PWM Scheme For The Nine Switch ConverterDocument6 pagesCarrier Based Sinusodial PWM Scheme For The Nine Switch ConverterShankar MukalNo ratings yet

- Bidirectional DC DC Converter With Full Bridge Push Pull Circuit For Automobile Electric Power SystemsDocument5 pagesBidirectional DC DC Converter With Full Bridge Push Pull Circuit For Automobile Electric Power SystemsrowrerNo ratings yet

- Slua 053Document13 pagesSlua 053carlosibaNo ratings yet

- 1-MHz Self-Driven ZVS Full-Bridge Converter For 48-V Power Pod and DC-DC BrickDocument10 pages1-MHz Self-Driven ZVS Full-Bridge Converter For 48-V Power Pod and DC-DC Brick李漢祥No ratings yet

- Power Oscillation Damping: POLYTECHNIC UNIVERSITYDocument3 pagesPower Oscillation Damping: POLYTECHNIC UNIVERSITYRajashekarNo ratings yet

- Sisngle Phase RectifierDocument5 pagesSisngle Phase RectifiermücahitNo ratings yet

- Mahesh Swamy Tsuneo J. Kume Noriyuki TakadaDocument7 pagesMahesh Swamy Tsuneo J. Kume Noriyuki TakadabcostiucNo ratings yet

- Capacitor Switching Comparison: The Supremacy of Diode TechnologyDocument8 pagesCapacitor Switching Comparison: The Supremacy of Diode TechnologyKelly chatNo ratings yet

- Isolated Mosfet Gate Driver PaperDocument6 pagesIsolated Mosfet Gate Driver PapergenwittsNo ratings yet

- Ijiset - V5 - I05 - 08 (My Paper 2018)Document4 pagesIjiset - V5 - I05 - 08 (My Paper 2018)krishna mohan pandeyNo ratings yet

- Resonant OcnverterDocument7 pagesResonant Ocnvertersatyam swarup dubeyNo ratings yet

- Synchronous Inverse SEPIC Topology Provides High Efficiency For Noninverting Buck/Boost Voltage ConvertersDocument5 pagesSynchronous Inverse SEPIC Topology Provides High Efficiency For Noninverting Buck/Boost Voltage ConvertersLeonardo OrtizNo ratings yet

- ISSCC2022 Session 18 DC-DC ConvertersDocument26 pagesISSCC2022 Session 18 DC-DC ConvertershstrybestNo ratings yet

- 1995 Iscas 2Document4 pages1995 Iscas 2frostyfoleyNo ratings yet

- ATPDraw EbookDocument111 pagesATPDraw EbookMarcio De Andrade VogtNo ratings yet

- A Thyristor Regulator Circuit For SCR Deflection-zlZDocument5 pagesA Thyristor Regulator Circuit For SCR Deflection-zlZjulio perezNo ratings yet

- A Novel Single Stage DC-AC Buck Boost Inverter For Solar Power ExtractionDocument6 pagesA Novel Single Stage DC-AC Buck Boost Inverter For Solar Power ExtractionsatheshkumarNo ratings yet

- TENCON2016Document6 pagesTENCON2016Nagaraj NeradhalaNo ratings yet

- Modulation and Control of Single-Stage Bidirectional Isolated Direct-Matrix-based AC-DC ConvertersDocument6 pagesModulation and Control of Single-Stage Bidirectional Isolated Direct-Matrix-based AC-DC ConvertersShubhasree MondalNo ratings yet

- Design of Plasma Generator Driven by High-FrequencDocument10 pagesDesign of Plasma Generator Driven by High-Frequencsigit kurniawanNo ratings yet

- The Resonant Link Converter-A New Concept in Static Power ConversionDocument9 pagesThe Resonant Link Converter-A New Concept in Static Power ConversionDar JahangeerNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Dendrómetro AnalóxicoDocument8 pagesDendrómetro AnalóxicoJuan DetemNo ratings yet

- Didactic DC/DC Buck Converter: With Discrete PID ControllerDocument14 pagesDidactic DC/DC Buck Converter: With Discrete PID ControllerJuan DetemNo ratings yet

- As5040 DS000374 5-00Document62 pagesAs5040 DS000374 5-00Long ThaiNo ratings yet

- Inductor Saturation VishayDocument1 pageInductor Saturation VishayJuan DetemNo ratings yet

- Tic116 Series Silicon Controlled RectifiersDocument4 pagesTic116 Series Silicon Controlled RectifiersJuan DetemNo ratings yet

- Transformerless Power Supply DesignDocument9 pagesTransformerless Power Supply DesignJuan DetemNo ratings yet

- Galaad EngDocument440 pagesGalaad EngJuan DetemNo ratings yet

- D-155 - 3 Cylinder Diesel Engine (01/75 - 12/85) 00 - Complete Machine 15-04 - Turbocharger, ADocument3 pagesD-155 - 3 Cylinder Diesel Engine (01/75 - 12/85) 00 - Complete Machine 15-04 - Turbocharger, AMANUALESNo ratings yet

- 2nd MCQ AUTOMATION IN MANUFACTURINGDocument10 pages2nd MCQ AUTOMATION IN MANUFACTURINGGaurav RajputNo ratings yet

- Installation Guide 45681-293Document2 pagesInstallation Guide 45681-293Miguelangel GomezNo ratings yet

- Em 2Document89 pagesEm 2Wallace JnrNo ratings yet

- CLM Bref 0510Document495 pagesCLM Bref 0510Hamada Shoukry MohammedNo ratings yet

- General Notes: Fourth Floor PlanDocument1 pageGeneral Notes: Fourth Floor PlanJuan IstilNo ratings yet

- UNIT8 Libro de InglesDocument8 pagesUNIT8 Libro de InglesDominic SantiagoNo ratings yet

- Unit5 Dgset UpsDocument9 pagesUnit5 Dgset UpsPatel NeelNo ratings yet

- CompoundingDocument5 pagesCompoundingMajester RigsNo ratings yet

- Project Completion Report On Torrefaction of BambooDocument28 pagesProject Completion Report On Torrefaction of BambooevanyllaNo ratings yet

- Sandrea Mexico Paper July 2019 FINAL 1Document20 pagesSandrea Mexico Paper July 2019 FINAL 1civalerick549No ratings yet

- Manual Lavavajilla Electrolux NHT60Document14 pagesManual Lavavajilla Electrolux NHT60Victor Hugo Quiñonez QuintanaNo ratings yet

- FMDS0281Document56 pagesFMDS0281HữuĐầuĐấtNo ratings yet

- Analysis of Pressure Transverse Between Pump Stations of Fula Pipeline Under Different Operation ScenariosDocument6 pagesAnalysis of Pressure Transverse Between Pump Stations of Fula Pipeline Under Different Operation ScenariosWAHA COMPUTERNo ratings yet

- Unipower HPL110 Technical InformationDocument2 pagesUnipower HPL110 Technical InformationpauloNo ratings yet

- Marelli P8 300608Document21 pagesMarelli P8 300608Nicolas MonroyNo ratings yet

- Tata Punch Petrol Fusebox Location and InformationDocument4 pagesTata Punch Petrol Fusebox Location and InformationsuryabasarNo ratings yet

- Ship Oily Bilge Water SystemDocument8 pagesShip Oily Bilge Water SystemEyüphan UlusoyNo ratings yet

- TOEFL ReadingDocument11 pagesTOEFL ReadingM.subhandi SubhandiNo ratings yet

- Introduction Heat ExchangerDocument11 pagesIntroduction Heat ExchangerLorna AhlaamiNo ratings yet

- 1 Water Treatment Plant - 240 KLDDocument7 pages1 Water Treatment Plant - 240 KLDSajeshKumarNo ratings yet

- ASHRAE Standards & Guidelines For Building Energy AuditsDocument33 pagesASHRAE Standards & Guidelines For Building Energy AuditsОсама А.ШоукиNo ratings yet

- HBD of 60% OP1 Bypass ConditionDocument1 pageHBD of 60% OP1 Bypass ConditionMohd Ridzuan AhmadNo ratings yet

- Komatsu Wheel Loaders Wa150pz 5 Shop ManualDocument20 pagesKomatsu Wheel Loaders Wa150pz 5 Shop Manualjoan100% (55)

- UPS Kaise 6-10kva RT - Hoja de DatosDocument2 pagesUPS Kaise 6-10kva RT - Hoja de DatosGermanYPNo ratings yet

- Frigider BekoDocument380 pagesFrigider BekopanoiuNo ratings yet

- IRENA-ETSAP Tech Brief P10 Production - of - Liquid BiofuelsDocument28 pagesIRENA-ETSAP Tech Brief P10 Production - of - Liquid BiofuelsAhmed YousryNo ratings yet

- Lab 1 Introduction To Power System ProtectionDocument11 pagesLab 1 Introduction To Power System Protectionsaud aliNo ratings yet

- Detailed StatementDocument19 pagesDetailed StatementDinesh GnanamoorthyNo ratings yet

- Saudi Aramco: Well LocationsDocument7 pagesSaudi Aramco: Well LocationsMahrouz MadoNo ratings yet