Professional Documents

Culture Documents

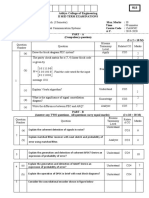

Vlsi Cat 2

Vlsi Cat 2

Uploaded by

Pradeep ravichander0 ratings0% found this document useful (0 votes)

41 views2 pagesThis document is a test paper for the course Digital VLSI System Design. It contains questions assessing different course outcomes and knowledge levels. Part A contains 4 multiple choice questions assessing topics like priority encoders, Moore and Mealy models, and Verilog keywords. Part B requires designing a shift register and explaining D and JK flip-flops. It also asks about Verilog modules and ports. Part C gives options to answer questions on a decade counter, Verilog simulation and synthesis, or levels of design description.

Original Description:

Original Title

VLSI CAT 2

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document is a test paper for the course Digital VLSI System Design. It contains questions assessing different course outcomes and knowledge levels. Part A contains 4 multiple choice questions assessing topics like priority encoders, Moore and Mealy models, and Verilog keywords. Part B requires designing a shift register and explaining D and JK flip-flops. It also asks about Verilog modules and ports. Part C gives options to answer questions on a decade counter, Verilog simulation and synthesis, or levels of design description.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

0 ratings0% found this document useful (0 votes)

41 views2 pagesVlsi Cat 2

Vlsi Cat 2

Uploaded by

Pradeep ravichanderThis document is a test paper for the course Digital VLSI System Design. It contains questions assessing different course outcomes and knowledge levels. Part A contains 4 multiple choice questions assessing topics like priority encoders, Moore and Mealy models, and Verilog keywords. Part B requires designing a shift register and explaining D and JK flip-flops. It also asks about Verilog modules and ports. Part C gives options to answer questions on a decade counter, Verilog simulation and synthesis, or levels of design description.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

You are on page 1of 2

B.

Tech (ECE) (III-Year/ VI-Semester)

Continuous Assessment Test-2, March-2022

DIGITAL VLSI SYSTEM DESIGN– U19ECT62

Day and Date: Section:B

Time: 09.00 AM to 10.40AM Max. Marks- 50

Instructions:

IMP: Verify that you have received question paper with correct course, code, branch etc.

i) All questions are compulsory.

ii) Figure to the right indicate full marks.

iii) Assume suitable data wherever necessary.

Course Outcomes:

CO2: Discuss about the different combinational and sequential logic blocks

CO3: Describe the terms and keywords in Verilog HDL.

Knowledge Level:K1–Remember,K2–Understand,K3–Apply,K4–Analyze,K5–Evaluate&K6-Create

Mark CO’

B.L

s s

PART A (10 Marks)

Answer all the Questions

Q.1 2 K2 CO

Write a truth table of priority encoder?

2

Q.2 2 K3 CO

Differentiate Moore and Mealy model with neat block diagram

2

Q.3 In the coding given below, fill the keyword needed in line no.2 2 K2 CO

3

Line No. Verilog code

1 module gate (input a, input b, output sum, output

carry);

2 ____ (sum,a,b);

3 assign carry = a&b;

4 endmodule

Q.4 What are the key functions of Programming Language Interface 2 K2 CO

(PLI). 3

Q.5 2 K3 CO

What is the use of the keyword “PARAMETER “ in Verilog HDL?

3

PART B (20 Marks)

Answer all the Questions

Design a shift register where “1011” can be loaded at 0th clock 5 K3 CO

cycle and outputs are taken as shown below 2

Clock Q

Q.6 1 1

2 1

3 0

4 1

With a neat logic diagram and truth table explain 5 K3 CO

Q.7 i) D Flip flop 2

ii) JK Flip flop

5 K2 CO

Q.8 Write in detail about module and its port types

3

Q.9 Explain the following language constraints with example in 5 K3 CO

Verilog HDL 3

i) Keywords

ii) Identifiers

iii) White Space Characters

PART C (20 Marks)

Answer any two Questions

Q.1 Design a decade counter in which all the flip-flops will have 10 K3 CO

0 common clock signal. 2

Q.1 Explain in detail about simulation and synthesis with the help of 10 K3 CO

1 Vivado 2014.4 3

Q.1 10 K3 CO

What are the Levels of design description in Verilog?

2 3

You might also like

- Brill Formulation Manual v004Document253 pagesBrill Formulation Manual v004stoisesti71% (7)

- Filter Separator SizingDocument3 pagesFilter Separator SizingChem.EnggNo ratings yet

- Subaru 4-Stroke V-Twin Engines Service ManualDocument85 pagesSubaru 4-Stroke V-Twin Engines Service ManualALFREDO TEXACANo ratings yet

- 7.2.3.5 Lab - Using Wireshark To Examine A UDP DNS Capture - ILMDocument6 pages7.2.3.5 Lab - Using Wireshark To Examine A UDP DNS Capture - ILMRuy Pequeno CidNo ratings yet

- CIA - II - Cs8501 - Theory of Computation - CIA I - Set ADocument1 pageCIA - II - Cs8501 - Theory of Computation - CIA I - Set Asaran SanjayNo ratings yet

- CS3351 - ModelDocument2 pagesCS3351 - Modelrkkumar07No ratings yet

- Dhanalakshmi Srinivasan: College of EngineeringDocument3 pagesDhanalakshmi Srinivasan: College of Engineeringhamsalakshmi cNo ratings yet

- B.Tech. (ECE) (III-Year / VI-Semester) : InstructionsDocument1 pageB.Tech. (ECE) (III-Year / VI-Semester) : InstructionsPradeep ravichanderNo ratings yet

- 1st YEAR 22ADT202 Computer Architecture SET 1Document2 pages1st YEAR 22ADT202 Computer Architecture SET 1Vanishree KondhandanNo ratings yet

- 1st YEAR 22ADT202 Computer Architecture SET 2Document2 pages1st YEAR 22ADT202 Computer Architecture SET 2Vanishree KondhandanNo ratings yet

- 20itpc302 - Software EngineeringDocument3 pages20itpc302 - Software EngineeringHARIBABU N SEC 2020No ratings yet

- Iae 2QP CadmDocument1 pageIae 2QP CadmPrabin MahatoNo ratings yet

- Unit 1 & Ii QbankDocument4 pagesUnit 1 & Ii QbankNetaji GandiNo ratings yet

- 2021 CaoDocument2 pages2021 CaoSudeep ShuklaNo ratings yet

- Os MergedDocument8 pagesOs Mergedatulo1308No ratings yet

- BCS302 Set 2Document2 pagesBCS302 Set 2megumifushiguru999No ratings yet

- Etp23mctd105 PSMDocument2 pagesEtp23mctd105 PSMtmahakaviyarasiNo ratings yet

- V18ect29 SDTVDocument2 pagesV18ect29 SDTVPavansaikumar SamudrapuNo ratings yet

- 3 and 4 TH Unit Cloud Computing III YrDocument2 pages3 and 4 TH Unit Cloud Computing III Yrsuriyakala vinothNo ratings yet

- CN QP Pattern IIDocument2 pagesCN QP Pattern IISivakumar MuthuNo ratings yet

- 1st Sem - ESEDocument8 pages1st Sem - ESEaditya ManhasNo ratings yet

- Dhanalakshmi Srinivasan: College of EngineeringDocument3 pagesDhanalakshmi Srinivasan: College of Engineeringhamsalakshmi cNo ratings yet

- I) All Questions Are Compulsory. Ii) Figure To The Right Indicate Full Marks. Iii) Assume Suitable Data Wherever NecessaryDocument1 pageI) All Questions Are Compulsory. Ii) Figure To The Right Indicate Full Marks. Iii) Assume Suitable Data Wherever Necessarythamizharasi arulNo ratings yet

- Mid Sem 1Document5 pagesMid Sem 1uttkarsh singhNo ratings yet

- I - IA - VHDL - 18EC56 (18 Batch)Document1 pageI - IA - VHDL - 18EC56 (18 Batch)NithiyaNo ratings yet

- IT - KOE 039 - ST2 Question Paper 2022-23Document2 pagesIT - KOE 039 - ST2 Question Paper 2022-23dhdw kwhdhwNo ratings yet

- Ect203 Scheme 2021Document9 pagesEct203 Scheme 2021ShakiraNo ratings yet

- Unit 1 - Assignment - Updated - AKTUDocument2 pagesUnit 1 - Assignment - Updated - AKTULovish SheikhNo ratings yet

- 17me62 - Cim - I Ia - QPDocument1 page17me62 - Cim - I Ia - QPPrashanth JNo ratings yet

- B.E/B.Tech Degree Examinations, Nov/Dec 2021 - Feb 2022: Reg. NoDocument3 pagesB.E/B.Tech Degree Examinations, Nov/Dec 2021 - Feb 2022: Reg. NoNanduIQNo ratings yet

- Department of Computer Science & Engineering First Internal Assessment Test, October 2020 - 21Document1 pageDepartment of Computer Science & Engineering First Internal Assessment Test, October 2020 - 21Sri SriNo ratings yet

- Iii Cse Ay 2022-2023 Odd Sem Model - I Set - 1Document2 pagesIii Cse Ay 2022-2023 Odd Sem Model - I Set - 1saran SanjayNo ratings yet

- Cia 1Document2 pagesCia 1Asst Prof ECENo ratings yet

- Coa 2021Document2 pagesCoa 2021jiumimyt0No ratings yet

- (KAS 401) Technical CommunicationDocument2 pages(KAS 401) Technical CommunicationAditi MahendraNo ratings yet

- Aditya College of EngineeringDocument2 pagesAditya College of EngineeringN.RAMAKUMARNo ratings yet

- New Horizon College of Engineering, Bangalore: 19CSE33 USNDocument12 pagesNew Horizon College of Engineering, Bangalore: 19CSE33 USNAhmad RazaNo ratings yet

- DSP EsDocument1 pageDSP EsFh Player 7No ratings yet

- BCS302 Set 1Document2 pagesBCS302 Set 1Mina KimNo ratings yet

- DD&CO Model Set1 Paper 2022 SchemeDocument2 pagesDD&CO Model Set1 Paper 2022 Schemeanveshrao024No ratings yet

- Dss Test QP1 - SET ADocument1 pageDss Test QP1 - SET AGopalakrishna Murthy C RNo ratings yet

- 19EC516 - QR - HDL Programming APRIL 2024Document15 pages19EC516 - QR - HDL Programming APRIL 2024Nanda KishoreNo ratings yet

- Emerging Technology For Engineering KMC202Document1 pageEmerging Technology For Engineering KMC202YashNo ratings yet

- Model Exam IVyrDocument3 pagesModel Exam IVyrsuriyakala vinothNo ratings yet

- See AddDocument2 pagesSee Add1ms21ec132No ratings yet

- P18ec53 U2Document2 pagesP18ec53 U2nandiniNo ratings yet

- Model CS3551 DC Set 2Document2 pagesModel CS3551 DC Set 2NambiRajaNo ratings yet

- Cao Iat 1 QP 2019 Set1Document2 pagesCao Iat 1 QP 2019 Set1formyphdNo ratings yet

- Digital Electronics Koe 039Document2 pagesDigital Electronics Koe 039Abhishek 8299No ratings yet

- MP - Int - 2Document2 pagesMP - Int - 2MATHAN RAJ MNo ratings yet

- 20aiel507 Set2Document2 pages20aiel507 Set2Keerthana KNo ratings yet

- Computer Graphics Qut PaperDocument2 pagesComputer Graphics Qut PaperjyotirmaypatelNo ratings yet

- Signal 2Document2 pagesSignal 2imvuuser1No ratings yet

- Digital ElectronicsDocument7 pagesDigital ElectronicsAlakaaa PromodNo ratings yet

- SDTVQ1Document2 pagesSDTVQ1Pavansaikumar SamudrapuNo ratings yet

- Model Exam Cloud Computing III YrDocument3 pagesModel Exam Cloud Computing III Yrsuriyakala vinothNo ratings yet

- SEM II PythonDocument2 pagesSEM II Pythonvishal Srinivasan (CPT. A)No ratings yet

- S.Y. B.Tech. (Computer Science & Engineering) : End Semester Examination, December-2021Document1 pageS.Y. B.Tech. (Computer Science & Engineering) : End Semester Examination, December-2021A.K. GamingNo ratings yet

- Cns QPDocument2 pagesCns QPsridharchandrasekarNo ratings yet

- Btech 1 Sem Programming For Problem Solving Kcs 101 2018 19 PDFDocument3 pagesBtech 1 Sem Programming For Problem Solving Kcs 101 2018 19 PDFAlok SinghNo ratings yet

- Time: 3 Hours Total Marks: 100Document3 pagesTime: 3 Hours Total Marks: 100Alok SinghNo ratings yet

- Computer Organization and Architecture KCS 302 1Document2 pagesComputer Organization and Architecture KCS 302 1Aman LakhwariaNo ratings yet

- Token Ring Technology ReportFrom EverandToken Ring Technology ReportNo ratings yet

- Professional Ethics AbstractDocument10 pagesProfessional Ethics AbstractPradeep ravichanderNo ratings yet

- B.Tech. (ECE) (III-Year / VI-Semester) : InstructionsDocument1 pageB.Tech. (ECE) (III-Year / VI-Semester) : InstructionsPradeep ravichanderNo ratings yet

- Software Description 1.1.1 ARDUINO IDEDocument4 pagesSoftware Description 1.1.1 ARDUINO IDEPradeep ravichanderNo ratings yet

- MergeResult 2022 05 14 03 35 12Document365 pagesMergeResult 2022 05 14 03 35 12Pradeep ravichanderNo ratings yet

- Relay and Voltage RegulatorDocument15 pagesRelay and Voltage RegulatorPradeep ravichanderNo ratings yet

- MODEL ANSWER KEY VLSI-converted-compressedDocument28 pagesMODEL ANSWER KEY VLSI-converted-compressedPradeep ravichanderNo ratings yet

- 2 Mark (ED Questions)Document26 pages2 Mark (ED Questions)Pradeep ravichanderNo ratings yet

- Relation Between Density & Compressive Strength of Foamed ConcreteDocument22 pagesRelation Between Density & Compressive Strength of Foamed Concretekinley dorjeeNo ratings yet

- C18 ACERT 448bkW PDFDocument5 pagesC18 ACERT 448bkW PDFAndre KellerNo ratings yet

- CO2024 Tutorial Hypothesis TestingDocument4 pagesCO2024 Tutorial Hypothesis TestingPinaNo ratings yet

- Fajar Afrindo, Merryana AdrianiDocument11 pagesFajar Afrindo, Merryana Adrianiwaode azfariNo ratings yet

- Chapter 1.6, Problem 9EDocument11 pagesChapter 1.6, Problem 9EAscar OzatbekNo ratings yet

- Paver 7.0 AboutDocument12 pagesPaver 7.0 AboutairpavsetNo ratings yet

- Iec 61000Document5 pagesIec 61000james wangNo ratings yet

- Towers of HanoiDocument16 pagesTowers of HanoiBharadwaj KasturiNo ratings yet

- 55DRS 63l-Mek64Document16 pages55DRS 63l-Mek64Aleksey OvchinnikovNo ratings yet

- Heat and Mass Transfer Heat Transfer For PDFDocument7 pagesHeat and Mass Transfer Heat Transfer For PDFEinar TverangerNo ratings yet

- Arbox Reliability Collaborative Phase 3 Gearbox 3 Test PlanDocument76 pagesArbox Reliability Collaborative Phase 3 Gearbox 3 Test PlannawadaoNo ratings yet

- Automatic Sukuma Wiki Cutting MachineDocument10 pagesAutomatic Sukuma Wiki Cutting MachineAmos Mwangi100% (1)

- Desalination: A.L. Ahmad, N.M. Yusuf, B.S. OoiDocument6 pagesDesalination: A.L. Ahmad, N.M. Yusuf, B.S. OoirukwavuNo ratings yet

- LaMotte 3673-01 DC1200-CO Copper Colorimeter Kit InstructionsDocument4 pagesLaMotte 3673-01 DC1200-CO Copper Colorimeter Kit InstructionsPromagEnviro.comNo ratings yet

- Static Program Analysis: Anders Møller and Michael I. SchwartzbachDocument6 pagesStatic Program Analysis: Anders Møller and Michael I. SchwartzbachDoob StrifeNo ratings yet

- Jfe 380Document4 pagesJfe 380Samuel HarjantoNo ratings yet

- Schneider Electric - Harmony-Control - RM35UA13MWDocument8 pagesSchneider Electric - Harmony-Control - RM35UA13MWammelinoNo ratings yet

- Data Sheet 6ES7516-3FN01-0AB0: General InformationDocument9 pagesData Sheet 6ES7516-3FN01-0AB0: General InformationMarko VadasNo ratings yet

- 6 Hydrogeochemical Facies Investigation of Surface and GroundwaterDocument13 pages6 Hydrogeochemical Facies Investigation of Surface and GroundwaterMervatNo ratings yet

- Basis Set: Harno D Pranowo Pusat Kimia Komputasi Indonesia-Austria Fmipa UgmDocument16 pagesBasis Set: Harno D Pranowo Pusat Kimia Komputasi Indonesia-Austria Fmipa UgmNdhoz Los GandhozNo ratings yet

- Jmeter TutorialDocument298 pagesJmeter TutorialPraveen KumarNo ratings yet

- Evolution FinalDocument30 pagesEvolution FinalHari HaranNo ratings yet

- 329 1011 1 PBDocument12 pages329 1011 1 PBTasya ArwieNo ratings yet

- Jurnal GerdDocument6 pagesJurnal GerddilaNo ratings yet

- Ricoh Aficio MPC2500 Trouble Error CodesDocument23 pagesRicoh Aficio MPC2500 Trouble Error CodesnafeesNo ratings yet

- HP ProLiant DL560 Gen8 - Data SheetDocument4 pagesHP ProLiant DL560 Gen8 - Data SheetJohari Yovera DelgadoNo ratings yet