Professional Documents

Culture Documents

TS922, TS922A: Rail-To-Rail, High Output Current Dual Operational Amplifier

TS922, TS922A: Rail-To-Rail, High Output Current Dual Operational Amplifier

Uploaded by

curzOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

TS922, TS922A: Rail-To-Rail, High Output Current Dual Operational Amplifier

TS922, TS922A: Rail-To-Rail, High Output Current Dual Operational Amplifier

Uploaded by

curzCopyright:

Available Formats

TS922, TS922A

Rail-to-rail, high output current dual operational amplifier

Datasheet - production data

Features

• Rail-to-rail input and output

• Low noise: 9 nV/√Hz

• Low distortion

J • High output current: 80 mA

Flip-chip with backcoating (able to drive 32 Ω loads)

• High-speed: 4 MHz, 1 V/μs

• Operating from 2.7 to 12 V

• Low input offset voltage: 900 μV max.

(TS922A)

MiniSO8 • ESD internal protection: 2 kV

(plastic micropackage) • Latch-up immunity

• Macromodel included in this specification

• Dual version available in Flip-chip package

Applications

D

SO8 • Headphone and servo amplifiers

(plastic micropackage) • Sound cards, multimedia systems

• Line drivers, actuator drivers

• Mobile phones and portable equipment

• Instrumentation with low noise as key factor

• Piezoelectric speaker drivers

P Description

TSSOP8

(thin shrink small outline package) TS922 and TS922A devices are rail-to-rail dual

BiCMOS operational amplifiers optimized and

fully specified for 3 V and 5 V operation. These

devices have high output currents which allow

low-load impedances to be driven.

Very low noise, low distortion, low offset, and

N a high output current capability make these

DIP8 devices an excellent choice for high quality, low

(plastic package) voltage, or battery operated audio systems.

The devices are stable for capacitive loads up to

500 pF.

June 2013 DocID5150 Rev 11 1/24

This is information on a product in full production. www.st.com

Contents TS922, TS922A

Contents

1 Pin diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2 Absolute maximum ratings and operating conditions . . . . . . . . . . . . . 4

3 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

4 TS922, TS922A macromodel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.1 Important note concerning this macromodel . . . . . . . . . . . . . . . . . . . . . . 12

4.2 Electrical characteristics from macromodelization . . . . . . . . . . . . . . . . . . 12

4.3 Macromodel code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5 Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5.1 8-bump Flip-chip package information . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5.2 MiniSO8 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.3 SO8 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

5.4 TSSOP8 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5.5 DIP8 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

6 Ordering information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

7 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2/24 DocID5150 Rev 11

TS922, TS922A Pin diagrams

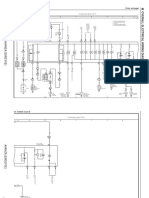

1 Pin diagrams

Figure 1. Pinout for Flip-chip package (top view)

OUT2

OUT2 -IN2 +IN2

-

+

VVCC+ V CC-

GND

CC+

-

OUT1

OUT1 -IN1 +IN1

Figure 2. Pin connections for MiniSO8, SO8, TSSOP8, and DIP8 (top view)

DocID5150 Rev 11 3/24

24

Absolute maximum ratings and operating conditions TS922, TS922A

2 Absolute maximum ratings and operating conditions

Table 1. Absolute maximum ratings (AMR)

Symbol Parameter Value Unit

VCC Supply voltage(1) 14

Vid (2)

Differential input voltage ±1 V

(3)

Vin Input voltage VCC- -0.3 to VCC++0.3

Tstg Storage temperature -65 to +150 °C

(4)

Thermal resistance junction to ambient

Flip-chip 90

Rthja

SO8 125

TSSOP8 120 °C/W

Thermal resistance junction to case(4)

Rthjc SO8 40

TSSOP8 37

Tj Maximum junction temperature 150 °C

HBM: human body model(5) 2000

ESD MM: machine model(6) 120 V

CDM: charged device model(7) 1500

Output short-circuit duration See note(8)

Latch-up immunity 200 mA

Soldering temperature (10 s), leaded version 250

°C

Soldering temperature (10 s), unleaded version 260

1. All voltage values, except differential voltage are with respect to network ground terminal.

2. The differential voltage is the non-inverting input terminal with respect to the inverting input terminal. If

Vid > ±1 V, the maximum input current must not exceed ±1 mA. In this case (Vid > ±1 V), an input series

resistor must be added to limit the input current.

3. Do not exceed 14 V.

4. Short-circuits can cause excessive heating. Destructive dissipation can result from simultaneous short-

circuits on all amplifiers. These values are typical.

5. Human body model: 100 pF discharged through a 1.5 kΩ resistor between two pins of the device, done for

all couples of pin combinations with other pins floating.

6. Machine model: a 200 pF capacitor is charged to the specified voltage, then discharged directly between

two pins of the device with no external series resistor (internal resistor < 5 Ω). This is done for all couples of

pin combinations with other pins floating.

7. Charged device model: all pins and plus package are charged together to the specified voltage and then

discharged directly to ground.

8. There is no short-circuit protection inside the device: short-circuits from the output to VCC can cause

excessive heating. The maximum output current is approximately 80 mA, independent of the magnitude of

VCC. Destructive dissipation can result from simultaneous short-circuits on all amplifiers.

4/24 DocID5150 Rev 11

TS922, TS922A Absolute maximum ratings and operating conditions

Table 2. Operating conditions

Symbol Parameter Value Unit

VCC Supply voltage 2.7 to 12

V

Vicm Common mode input voltage range VCC- -0.2 to VCC+ +0.2

Toper Operating free air temperature range -40 to +125 °C

DocID5150 Rev 11 5/24

24

Electrical characteristics TS922, TS922A

3 Electrical characteristics

Table 3. Electrical characteristics measured at VCC = +3 V, VCC- = 0 V, Vicm = VCC/2,

Tamb = 25 °C, and RL connected to VCC/2 (unless otherwise specified)

Symbol Parameter Test conditions Min. Typ. Max. Unit

TS922 3

TS922A 0.9

TS922IJ (Flip-chip) 1.5

Vio Input offset voltage Tmin ≤ Tamb ≤ Tmax mV

TS922 5

TS922A 1.8

TS922IJ (Flip-chip) 2.5

ΔVio/ΔT Input offset voltage drift 2 μV/°C

Vout = VCC/2 1 30

Iio Input offset current

Tmin ≤ Tamb ≤ Tmax 30

nA

Vout = VCC/2 15 100

Iib Input bias current

Tmin ≤ Tamb ≤ Tmax 100

RL= 10 kΩ 2.90

Tmin ≤ Tamb ≤ Tmax 2.90

VOH High level output voltage RL = 600 Ω 2.87 V

Tmin ≤ Tamb ≤ Tmax 2.87

RL = 32 Ω 2.63

RL= 10 kΩ 50

Tmin ≤ Tamb ≤ Tmax 50

VOL Low level output voltage RL = 600 Ω 100 mV

Tmin ≤ Tamb ≤ Tmax 100

RL = 32 Ω 180

RL= 10 kΩ, Vout = 2 Vp-p 200

Tmin ≤ Tamb ≤ Tmax 70

Avd Large signal voltage gain RL = 600 Ω, Vout = 2 Vp-p 35 V/mV

Tmin ≤ Tamb ≤ Tmax 15

RL = 32 Ω, Vout = 2 Vp-p 16

No load, Vout = VCC/2 2 3

ICC Total supply current mA

Tmin ≤ Tamb ≤ Tmax 3.2

GBP Gain bandwidth product RL = 600 Ω 4 MHz

Vicm = 0 to 3 V 60 80

CMR Common mode rejection ratio

Tmin ≤ Tamb ≤ Tmax 56

dB

VCC = 2.7 to 3.3 V 60 85

SVR Supply voltage rejection ratio

Tmin ≤ Tamb ≤ Tmax 60

Io Output short-circuit current 50 80 mA

SR Slew rate 0.7 1.3 V/μs

6/24 DocID5150 Rev 11

TS922, TS922A Electrical characteristics

Table 3. Electrical characteristics measured at VCC = +3 V, VCC- = 0 V, Vicm = VCC/2,

Tamb = 25 °C, and RL connected to VCC/2 (unless otherwise specified) (continued)

Symbol Parameter Test conditions Min. Typ. Max. Unit

φm Phase margin at unit gain 68 Degrees

RL = 600 Ω, CL = 100 pF

Gm Gain margin 12 dB

Equivalent input noise nV

en f = 1 kHz 9 ------------

voltage Hz

Vout = 2 Vp-p, f = 1 kHz, Av = 1,

THD Total harmonic distortion 0.005 %

RL = 600 Ω

Cs Channel separation 120 dB

DocID5150 Rev 11 7/24

24

Electrical characteristics TS922, TS922A

Table 4. Electrical characteristics measured at VCC = 5 V, VCC- = 0 V, Vicm = VCC/2,

Tamb = 25 °C, and RL connected to VCC/2 (unless otherwise specified)

Symbol Parameter Conditions Min. Typ. Max. Unit

TS922 3

TS922A 0.9

TS922IJ (Flip-chip) 1.5

Vio Input offset voltage Tmin ≤ Tamb ≤ Tmax mV

TS922 5

TS922A 1.8

TS922IJ (Flip-chip) 2.5

ΔVio/ΔT Input offset voltage drift 2 μV/°C

Vout = VCC/2 1 30

Iio Input offset current

Tmin ≤ Tamb ≤ Tmax 30

nA

Vout = VCC/2 15 100

Iib Input bias current

Tmin ≤ Tamb ≤ Tmax 100

RL= 10 kΩ 4.9

Tmin ≤ Tamb ≤ Tmax 4.9

VOH High level output voltage RL = 600 Ω 4.85 V

Tmin ≤ Tamb ≤ Tmax 4.85

RL = 32 Ω 4.4

RL= 10 kΩ 50

Tmin ≤ Tamb ≤ Tmax 50

VOL Low level output voltage RL = 600 Ω 120 mV

Tmin ≤ Tamb ≤ Tmax 120

RL = 32 Ω 300

RL= 10 kΩ, Vout = 2 Vp-p 200

Tmin ≤ Tamb ≤ Tmax 70

Avd Large signal voltage gain RL = 600 Ω, Vout = 2 Vp-p 35 V/mV

Tmin ≤ Tamb ≤ Tmax 20

RL = 32 Ω, Vout = 2 Vp-p 16

No load, Vout = VCC/2 2 3

Icc Total supply current mA

Tmin ≤ Tamb ≤ Tmax 3.2

GBP Gain bandwidth product RL = 600 Ω 4 MHz

Common mode rejection Vicm = 0 to 5 V 60 80

CMR

ratio Tmin ≤ Tamb ≤ Tmax 56

dB

VCC = 4.5 to 5.5 V 60 85

SVR Supply voltage rejection ratio

Tmin ≤ Tamb ≤ Tmax 60

Io Output short-circuit current 50 80 mA

SR Slew rate 0.7 1.3 V/μs

φm Phase margin at unit gain 68 Degrees

RL = 600 Ω, CL =100 pF

Gm Gain margin 12 dB

Equivalent input noise nV

en f = 1 kHz 9 ------------

voltage Hz

8/24 DocID5150 Rev 11

TS922, TS922A Electrical characteristics

Table 4. Electrical characteristics measured at VCC = 5 V, VCC- = 0 V, Vicm = VCC/2,

Tamb = 25 °C, and RL connected to VCC/2 (unless otherwise specified) (continued)

Symbol Parameter Conditions Min. Typ. Max. Unit

Vout = 2 Vp-p, f = 1 kHz, Av = 1,

THD Total harmonic distortion 0.005 %

RL = 600 Ω

Cs Channel separation 120 dB

DocID5150 Rev 11 9/24

24

Electrical characteristics TS922, TS922A

Figure 3. Output short-circuit current vs. Figure 4. Total supply current vs.

output voltage supply voltage

Figure 5. Voltage gain and phase vs. Figure 6. Equivalent input noise voltage vs.

frequency frequency

60 180

Phase 30

Equivalent input noise (nV/sqrt(Hz)

40 120 25

VCC = ±1.5 V

Gain Cl = 100 pF RL = 100 Ω

Phase (deg.)

20

Gain (dB)

20 60 15

10

0 0 5

0

0.01 0.1 1 10 100

-20 -60 Frequency (kHz)

1E+02 1E+03 1E+04 1E+05 1E+06 1E+07 1E+08

Frequency (Hz)

Figure 7. THD + noise vs. frequency Figure 8. THD + noise vs. frequency

(RL = 2 kΩ, Vo = 10 Vpp, VCC = ± 6 V) (RL = 32 Ω, Vo = 4 Vpp, VCC = ± 2.5 V)

0.02 0.04

0.032

THD + noise (%)

THD + noise (%)

0.015

0.024

0.01 RL= 2 kΩ, Vo = 10 Vpp RL = 32 Ω, Vo = 4 Vpp

VCC = ±6 V, Av = 1 VCC = ±2.5 V, Av = 1

0.016

0.005

0.008

0 0

0.01 0.1 1 10 100 0.01 0.1 1 10 100

Frequency (kHz) Frequency (kHz)

10/24 DocID5150 Rev 11

TS922, TS922A Electrical characteristics

Figure 9. THD + noise vs. frequency Figure 10. THD + noise vs. output voltage

(RL = 32 Ω, Vo = 2 Vpp, VCC = ± 1.5 V) (RL = 600 Ω, f = 1 kHz, VCC = 0/3 V)

10,000

0.7

0.6

1,000

THD + noise (%)

0.5

THD + noise (%)

RL = 32 Ω, Vo = 2 Vpp

0.4 VCC = ±1.5 V, Av = 10 RL = 600 Ω, f = 1 kHz

0,100 VCC = 0/3 V, Av = -1

0.3

0.2

0,010

0.1

0

0,001

0.01 0.1 1 10 100 0 0,2 0,4 0,6 0,8 1 1,2

Frequency (kHz) Vout (Vrms)

Figure 11. THD + noise vs. output voltage Figure 12. THD + noise vs. output voltage

(RL = 32 Ω, f = 1 kHz, VCC = ± 1.5 V) (RL = 2 kΩ, f = 1 kHz, VCC = ± 1.5 V)

10

10

RL = 32 Ω, f = 1 kHz

THD + noise (%)

THD + noise (%)

1 VCC = ±1.5 V, Av = -1

0.1

RL = 2 kΩ, f = 1 kHz

VCC = ±1.5 V, Av = -1

0.1

0.01

0.01

0 0.2 0.4 0.6 0. 0.001

Vout (Vrms) 0 0.2 0.4 0.6 0.8 1 1.2

Vout (Vrms)

Figure 13. Open loop gain and phase vs. frequency

50 180

40

120

Phase (deg.)

Gain (dB)

30

CL = 500 pF

20

60

10

0 0

1E+2 1E+3 1E+4 1E+5 1E+6 1E+7 1E+8

Frequency (Hz)

DocID5150 Rev 11 11/24

24

TS922, TS922A macromodel TS922, TS922A

4 TS922, TS922A macromodel

4.1 Important note concerning this macromodel

• All models are a trade-off between accuracy and complexity (i.e. simulation time).

• Macromodels are not a substitute to breadboarding; rather, they confirm the validity of

a design approach and help to select surrounding component values.

• A macromodel emulates the nominal performance of a typical device within specified

operating conditions (for example, temperature and supply voltage). Thus the

macromodel is often not as exhaustive as the datasheet, its purpose is to illustrate the

main parameters of the product.

Data derived from macromodels used outside of the specified conditions (for example, VCC,

temperature) or worse, outside of the device operating conditions (for example, VCC, Vicm),

are not reliable in any way.

Section 4.2 provides the electrical characteristics resulting from the use of the TS922,

TS922A macromodel.

4.2 Electrical characteristics from macromodelization

Table 5. Electrical characteristics resulting from macromodel simulation

at VCC = 3 V, VCC- = 0 V, RL, CL connected to VCC/2, Tamb = 25 °C

(unless otherwise specified)

Symbol Conditions Value Unit

Vio 0 mV

Avd RL = 10 kΩ 200 V/mV

ICC No load, per operator 1.2 mA

Vicm -0.2 to 3.2

V

VOH 2.95

RL = 10 kΩ

VOL 25 mV

Isink VO = 3 V

80 mA

Isource VO = 0 V

GBP RL = 600 kΩ 4 MHz

SR RL = 10 kΩ, CL = 100 pF 1.3 V/μs

φm RL = 600 kΩ 68 Degrees

12/24 DocID5150 Rev 11

TS922, TS922A TS922, TS922A macromodel

4.3 Macromodel code

** Standard Linear Ics Macromodels, 1996.

** CONNECTIONS:

* 1 INVERTING INPUT

* 2 NON-INVERTING INPUT

* 3 OUTPUT

* 4 POSITIVE POWER SUPPLY

* 5 NEGATIVE POWER SUPPLY

*

.SUBCKT TS92X 1 2 3 4 5

*

.MODEL MDTH D IS=1E-8 KF=2.664234E-16 CJO=10F

*

* INPUT STAGE

CIP 2 5 1.000000E-12

CIN 1 5 1.000000E-12

EIP 10 5 2 5 1

EIN 16 5 1 5 1

RIP 10 11 8.125000E+00

RIN 15 16 8.125000E+00

RIS 11 15 2.238465E+02

DIP 11 12 MDTH 400E-12

DIN 15 14 MDTH 400E-12

VOFP 12 13 DC 153.5u

VOFN 13 14 DC 0

IPOL 13 5 3.200000E-05

CPS 11 15 1e-9

DINN 17 13 MDTH 400E-12

VIN 17 5 -0.100000e+00

DINR 15 18 MDTH 400E-12

VIP 4 18 0.400000E+00

FCP 4 5 VOFP 1.865000E+02

FCN 5 4 VOFN 1.865000E+02

FIBP 2 5 VOFP 6.250000E-03

FIBN 5 1 VOFN 6.250000E-03

* GM1 STAGE ***************

FGM1P 119 5 VOFP 1.1

FGM1N 119 5 VOFN 1.1

RAP 119 4 2.6E+06

RAN 119 5 2.6E+06

* GM2 STAGE ***************

G2P 19 5 119 5 1.92E-02

G2N 19 5 119 4 1.92E-02

R2P 19 4 1E+07

DocID5150 Rev 11 13/24

24

TS922, TS922A macromodel TS922, TS922A

R2N 19 5 1E+07

**************************

VINT1 500 0 5

GCONVP 500 501 119 4 19.38

VP 501 0 0

GCONVN 500 502 119 5 19.38

VN 502 0 0

********* orientation isink isource *******

VINT2 503 0 5

FCOPY 503 504 VOUT 1

DCOPYP 504 505 MDTH 400E-9

VCOPYP 505 0 0

DCOPYN 506 504 MDTH 400E-9

VCOPYN 0 506 0

***************************

F2PP 19 5 poly(2) VCOPYP VP 0 0 0 0 0.5

F2PN 19 5 poly(2) VCOPYP VN 0 0 0 0 0.5

F2NP 19 5 poly(2) VCOPYN VP 0 0 0 0 1.75

F2NN 19 5 poly(2) VCOPYN VN 0 0 0 0 1.75

* COMPENSATION ************

CC 19 119 25p

* OUTPUT ***********

DOPM 19 22 MDTH 400E-12

DONM 21 19 MDTH 400E-12

HOPM 22 28 VOUT 6.250000E+02

VIPM 28 4 5.000000E+01

HONM 21 27 VOUT 6.250000E+02

VINM 5 27 5.000000E+01

VOUT 3 23 0

ROUT 23 19 6

COUT 3 5 1.300000E-10

DOP 19 25 MDTH 400E-12

VOP 4 25 1.052

DON 24 19 MDTH 400E-12

VON 24 5 1.052

.ENDS;TS92X

14/24 DocID5150 Rev 11

TS922, TS922A Package information

5 Package information

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK® packages, depending on their level of environmental compliance. ECOPACK®

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK® is an ST trademark.

DocID5150 Rev 11 15/24

24

Package information TS922, TS922A

5.1 8-bump Flip-chip package information

Figure 14. 8-bump Flip-chip package dimensions (top view)

1. Die size: 1600 μm x 1600 μm ±30 μm

Die height: 350 µm ±20 µm

Die height (including bumps): 650 µm

Bump diameter: 315 µm ±50 µm

Bump height: 250 µm ±40 µm

Pitch: 500 µm ±10 µm

Backcoating

Figure 15. 8-bump Flip-chip footprint recommendation

16/24 DocID5150 Rev 11

TS922, TS922A Package information

Figure 16. 8-bump Flip-chip marking (top view)

(4) (1)

(2)

(3)

GAMS0306131526CB

1. ST logo

2. Part number

3. Date code: Y = year, WW = week

4. This dot indicates the bump corner 1A

Figure 17. 8-bump Flip-chip tape and reel specification (top view)

1 1

A A

User direction of feed

1. Device orientation: the devices are oriented in the carrier pocket with bump number A1 adjacent to the

sprocket holes.

DocID5150 Rev 11 17/24

24

Package information TS922, TS922A

5.2 MiniSO8 package information

Figure 18. MiniSO8 package mechanical drawing

Table 6. MiniSO8 package mechanical data

Dimensions

Symbol Millimeters Inches

Min. Typ. Max. Min. Typ. Max.

A 1.1 0.043

A1 0 0.15 0 0.006

A2 0.75 0.85 0.95 0.030 0.033 0.037

b 0.22 0.40 0.009 0.016

c 0.08 0.23 0.003 0.009

D 2.80 3.00 3.20 0.11 0.118 0.126

E 4.65 4.90 5.15 0.183 0.193 0.203

E1 2.80 3.00 3.10 0.11 0.118 0.122

e 0.65 0.026

L 0.40 0.60 0.80 0.016 0.024 0.031

L1 0.95 0.037

L2 0.25 0.010

k 0° 8° 0° 8°

ccc 0.10 0.004

18/24 DocID5150 Rev 11

TS922, TS922A Package information

5.3 SO8 package information

Figure 19. SO8 package mechanical drawing

Table 7. SO8 package mechanical data

Dimensions

Symbol Millimeters Inches

Min. Typ. Max. Min. Typ. Max.

A 1.75 0.069

A1 0.10 0.25 0.004 0.010

A2 1.25 0.049

b 0.28 0.48 0.011 0.019

c 0.17 0.23 0.007 0.010

D 4.80 4.90 5.00 0.189 0.193 0.197

E 5.80 6.00 6.20 0.228 0.236 0.244

E1 3.80 3.90 4.00 0.150 0.154 0.157

e 1.27 0.050

h 0.25 0.50 0.010 0.020

L 0.40 1.27 0.016 0.050

L1 1.04 0.040

k 0 8° 1° 8°

ccc 0.10 0.004

DocID5150 Rev 11 19/24

24

Package information TS922, TS922A

5.4 TSSOP8 package information

Figure 20. TSSOP8 package mechanical drawing

Table 8. TSSOP8 package mechanical data

Dimensions

Symbol Millimeters Inches

Min. Typ. Max. Min. Typ. Max.

A 1.20 0.047

A1 0.05 0.15 0.002 0.006

A2 0.80 1.00 1.05 0.031 0.039 0.041

b 0.19 0.30 0.007 0.012

c 0.09 0.20 0.004 0.008

D 2.90 3.00 3.10 0.114 0.118 0.122

E 6.20 6.40 6.60 0.244 0.252 0.260

E1 4.30 4.40 4.50 0.169 0.173 0.177

e 0.65 0.0256

k 0° 8° 0° 8°

L 0.45 0.60 0.75 0.018 0.024 0.030

L1 1 0.039

aaa 0.10 0.004

20/24 DocID5150 Rev 11

TS922, TS922A Package information

5.5 DIP8 package information

Figure 21. DIP8 package mechanical drawing

Table 9. DIP8 package mechanical data

Dimensions

Symbol Millimeters Inches

Min. Typ. Max. Min. Typ. Max.

A 5.33 0.210

A1 0.38 0.015

A2 2.92 3.30 4.95 0.115 0.130 0.195

b 0.36 0.46 0.56 0.014 0.018 0.022

b2 1.14 1.52 1.78 0.045 0.060 0.070

c 0.20 0.25 0.36 0.008 0.010 0.014

D 9.02 9.27 10.16 0.355 0.365 0.400

E 7.62 7.87 8.26 0.300 0.310 0.325

E1 6.10 6.35 7.11 0.240 0.250 0.280

e 2.54 0.100

eA 7.62 0.300

eB 10.92 0.430

L 2.92 3.30 3.81 0.115 0.130 0.150

DocID5150 Rev 11 21/24

24

Ordering information TS922, TS922A

6 Ordering information

Table 10. Order codes

Temperature

Order codes Package Packaging Marking

range

TS922ID

922I

TS922IDT

SO-8 Tube or

TS922AID

tape and reel 922AI

TS922AIDT

TS922IYDT(1) SO-8 922IY

TS922AIYDT (1) (automotive grade) 922AIY

TS922IPT 922I

TSSOP8

TS922AIPT Tape and reel 922AI

TS922IST -40 °C to +125 °C K158

MiniSO8

TS922AIST K159

TS922IN DIP8 Tube TS922IN

TS922IYPT(2) TSSOP8 922IY

TS922AIYPT(2) (automotive grade) 922AY

(2)

TS922IYST MiniSO8 Tape and reel K10A

TS922AIYST(2) (automotive grade) K10B

TS922IJT/EIJT Flip-chip with backcoating 922

1. Qualified and characterized according to AEC Q100 and Q003 or equivalent, advanced screening

according to AEC Q001 and Q 002 or equivalent.

2. Qualification and characterization according to AEC Q100 and Q003 or equivalent, advanced screening

according to AEC Q001 and Q 002 or equivalent are ongoing.

22/24 DocID5150 Rev 11

TS922, TS922A Revision history

7 Revision history

Table 11. Document revision history

Date Revision Changes

01-Feb-2001 1 First release.

01-Jul-2004 2 Flip-chip package inserted in the document.

Modifications in AMR Table 1 on page 4 (explanation of Vid and Vi

02-May-2005 3

limits, ESD MM and CDM values added, Rthja added).

01-Aug-2005 4 PPAP references inserted in the datasheet, see Table 6 on page 22.

TS922EIJT part number inserted in the datasheet, see

01-Mar-2006 5

Table 6 on page 22.

Modifications in AMR Table 1 on page 4 (Rthjc added), parameter

26-Jan-2007 6 limits on full temperature range added in Table 3 on page 6 and

Table 4 on page 8.

Added notes on ESD in AMR table.

12-Nov-2007 7 Re-formatted package information.

Added notes for automotive grade in order codes table.

Document reformatted.

02-Feb-2010 8 Added root part number TS922A on cover page.

Removed TS922AIYD order code from Table 10.

Added MiniSO8 package.

Modified test conditions for CMR in Table 3 and Table 4.

Replaced VDD by VCC- in title of Table 3, Table 4, and Table 5.

15-Jan-2013 9 Updated titles of Figure 7 to Figure 12 (added conditions to

differentiate them).

Removed TS922IYD device from Table 10.

Minor corrections throughout document.

Features: updated package information for Flip-chip

Figure 2: Updated title

Table 1: updated footnotes 5, 6, and 7

04-Jun-2013 10 Table 3 and Table 4: replaced DVio with ΔVio/ΔT

Figure 14: added backcoating to package information

Figure 16: updated footnote 3

Table 10: updated package information for Flip-chip

27-Jun-2013 11 Figure 14: updated to include new height for backcoating

DocID5150 Rev 11 23/24

24

TS922, TS922A

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT AUTHORIZED FOR USE IN WEAPONS. NOR ARE ST PRODUCTS DESIGNED OR AUTHORIZED FOR USE

IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH

PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR

ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED

FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER’S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN

WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR “AUTOMOTIVE,

AUTOMOTIVE SAFETY OR MEDICAL” INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS.

PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE

CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

24/24 DocID5150 Rev 11

You might also like

- Parte Manual Focus Rs 2016 5Document96 pagesParte Manual Focus Rs 2016 5Garikoitz FranciscoeneNo ratings yet

- TS924, TS924A: Rail-To-Rail Output Current Quad Operational AmplifierDocument18 pagesTS924, TS924A: Rail-To-Rail Output Current Quad Operational AmplifierewertonNo ratings yet

- 3 W Filter-Free Class D Audio Power Amplifier: Related ProductsDocument41 pages3 W Filter-Free Class D Audio Power Amplifier: Related ProductsМирослава НиколенкоNo ratings yet

- Wireless Components: 7 X 5 Video Matrix Switch TDA 6920 Version 1.0Document28 pagesWireless Components: 7 X 5 Video Matrix Switch TDA 6920 Version 1.0MPIMLACNo ratings yet

- Ucc 27321Document36 pagesUcc 27321Khalil AwawdaNo ratings yet

- Pca 9306Document32 pagesPca 9306Adhiezzz GamingNo ratings yet

- Pca 9306Document38 pagesPca 9306qozzaqNo ratings yet

- UCC2751x Single-Channel, High-Speed, Low-Side Gate Driver (Based On CMOS Input Threshold With 4-A Peak Source and 4-A Peak Sink)Document33 pagesUCC2751x Single-Channel, High-Speed, Low-Side Gate Driver (Based On CMOS Input Threshold With 4-A Peak Source and 4-A Peak Sink)George ThomasNo ratings yet

- Max3232 PDFDocument27 pagesMax3232 PDFpiyushpandeyNo ratings yet

- MAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver/Receiver With 15-kV ESD ProtectionDocument31 pagesMAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver/Receiver With 15-kV ESD Protectionsuperpuma86No ratings yet

- MAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver/Receiver With 15-kV ESD ProtectionDocument29 pagesMAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver/Receiver With 15-kV ESD ProtectionBechir BrahmiNo ratings yet

- MAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver and Receiver With 15-kV ESD ProtectionDocument30 pagesMAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver and Receiver With 15-kV ESD Protectionpenetrator123No ratings yet

- MAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver and Receiver With 15-kV ESD ProtectionDocument30 pagesMAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver and Receiver With 15-kV ESD Protectionessen999No ratings yet

- MAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver and Receiver With 15-kV ESD ProtectionDocument35 pagesMAX3232 3-V To 5.5-V Multichannel RS-232 Line Driver and Receiver With 15-kV ESD ProtectionIván CastilloNo ratings yet

- TPA2005D1 1.4-W MONO Filter-Free Class-D Audio Power AmplifierDocument42 pagesTPA2005D1 1.4-W MONO Filter-Free Class-D Audio Power AmplifierVarun RajaranganNo ratings yet

- Pca 9306Document36 pagesPca 9306احسن طاہرNo ratings yet

- Tda 7492 PeDocument23 pagesTda 7492 PeMew MobNo ratings yet

- TDA7851F: 4 X 48 W MOSFET Quad Bridge Power AmplifierDocument18 pagesTDA7851F: 4 X 48 W MOSFET Quad Bridge Power AmplifierChua BoonLianNo ratings yet

- TDA7851F: 4 X 48 W MOSFET Quad Bridge Power AmplifierDocument18 pagesTDA7851F: 4 X 48 W MOSFET Quad Bridge Power AmplifierMarcioNo ratings yet

- TDA7376B: 2 X 35 W Power Amplifier For Car RadioDocument15 pagesTDA7376B: 2 X 35 W Power Amplifier For Car RadioAnirudh AggarwalNo ratings yet

- OipyufcgsDocument39 pagesOipyufcgsednardo CunhaNo ratings yet

- Lmx58-N Low-Power, Dual-Operational Amplifiers: 1 Features 3 DescriptionDocument38 pagesLmx58-N Low-Power, Dual-Operational Amplifiers: 1 Features 3 DescriptionNalsonNo ratings yet

- Lmx58-N Low-Power, Dual-Operational Amplifiers: 1 Features 3 DescriptionDocument38 pagesLmx58-N Low-Power, Dual-Operational Amplifiers: 1 Features 3 DescriptionEliezer OcantoNo ratings yet

- Si720x Switch/Latch Hall Effect Magnetic Position Sensor Data SheetDocument32 pagesSi720x Switch/Latch Hall Effect Magnetic Position Sensor Data Sheetvlade naumovskiNo ratings yet

- Tps 723Document31 pagesTps 723hungdvNo ratings yet

- 3-V To 5.5-V Multichannel RS-232 Line Driver and Receiver With 15-kV ESD ProtectionDocument28 pages3-V To 5.5-V Multichannel RS-232 Line Driver and Receiver With 15-kV ESD ProtectioncafosokNo ratings yet

- LMV 321Document48 pagesLMV 321Tanmay MalhotraNo ratings yet

- TPS54328 4.5-V To 18-V Input, 3-A Synchronous Step-Down Converter With Eco-Mode™Document31 pagesTPS54328 4.5-V To 18-V Input, 3-A Synchronous Step-Down Converter With Eco-Mode™Gus Khoir SrNo ratings yet

- STPA003: 4 X 52 W Quad Bridge Power Amplifier With High Side Driver and Low Voltage OperationDocument25 pagesSTPA003: 4 X 52 W Quad Bridge Power Amplifier With High Side Driver and Low Voltage OperationBrian morenoNo ratings yet

- Ucc27324 q1Document26 pagesUcc27324 q1info.wenamericaNo ratings yet

- ADMP401Document12 pagesADMP401Ayman Thafer Abdul-nafaNo ratings yet

- LM78L 100-Ma Fixed Output Linear Regulator: 1 Features 3 DescriptionDocument35 pagesLM78L 100-Ma Fixed Output Linear Regulator: 1 Features 3 DescriptionPashaNo ratings yet

- LM78L 100-Ma Fixed Output Linear Regulator: 1 Features 3 DescriptionDocument34 pagesLM78L 100-Ma Fixed Output Linear Regulator: 1 Features 3 DescriptionLeandroNo ratings yet

- THVD 1400Document33 pagesTHVD 1400victorvpaiva07No ratings yet

- H-Bridge l9960tDocument95 pagesH-Bridge l9960tAdlan MessaoudNo ratings yet

- TPS6217x 28-V, 0.5-A Step-Down Converter With Sleep Mode: 1 Features 3 DescriptionDocument38 pagesTPS6217x 28-V, 0.5-A Step-Down Converter With Sleep Mode: 1 Features 3 DescriptionBarbieru PavelNo ratings yet

- Amoled Driver STMDocument23 pagesAmoled Driver STManalog changeNo ratings yet

- Obsolete Product(s) - Obsolete Product(s) : 4 X 47W MOSFET Quad Bridge Power AmplifierDocument12 pagesObsolete Product(s) - Obsolete Product(s) : 4 X 47W MOSFET Quad Bridge Power AmplifiermicaelfnNo ratings yet

- Adm485 PDFDocument16 pagesAdm485 PDFrezaNo ratings yet

- Max 3243Document29 pagesMax 3243alephzeroNo ratings yet

- lm158 N PDFDocument39 pageslm158 N PDFYahel Zopel ZucenNo ratings yet

- Datasheet lm2904Document40 pagesDatasheet lm2904zpetznaz139No ratings yet

- lm158 NDocument38 pageslm158 NLokesh SkumarNo ratings yet

- 358 DatasheetDocument38 pages358 DatasheetJual PsuNo ratings yet

- Lmx58-N Low-Power, Dual-Operational Amplifiers: 1 Features 3 DescriptionDocument40 pagesLmx58-N Low-Power, Dual-Operational Amplifiers: 1 Features 3 DescriptionAnkit SrivastavaNo ratings yet

- TPS54327 3-A Output Single Synchronous Step-Down Switcher With Integrated FETDocument28 pagesTPS54327 3-A Output Single Synchronous Step-Down Switcher With Integrated FETGuillermo González CastilloNo ratings yet

- MAX202 5-V Dual RS-232 Line Driver and Receiver With 15-kV ESD ProtectionDocument28 pagesMAX202 5-V Dual RS-232 Line Driver and Receiver With 15-kV ESD ProtectionSashika KumaraNo ratings yet

- Max 202Document29 pagesMax 202JerryPussykilla11No ratings yet

- Lmx58-N Low-Power, Dual-Operational Amplifiers: 1 Features 3 DescriptionDocument25 pagesLmx58-N Low-Power, Dual-Operational Amplifiers: 1 Features 3 DescriptionWilliam RamírezNo ratings yet

- Anexo ACaracteristicas Tecnicas de Los EquiposDocument18 pagesAnexo ACaracteristicas Tecnicas de Los EquiposAlvaroZolaNo ratings yet

- DAC2904Document17 pagesDAC2904api-3825669100% (4)

- Max 3243Document30 pagesMax 3243Dario Gabriel Coz RojasNo ratings yet

- LP 5900Document29 pagesLP 5900dvdmorderousNo ratings yet

- SN 74 LVC 1 T 45Document38 pagesSN 74 LVC 1 T 45miguel CryptoNo ratings yet

- Ib Il Rs Uni (-2Mbd) - Pac: Inline Communication Terminal For Serial Data TransmissionDocument25 pagesIb Il Rs Uni (-2Mbd) - Pac: Inline Communication Terminal For Serial Data TransmissionGuilherme CeveseNo ratings yet

- MX Series Pulser Options: Instruction ManualDocument16 pagesMX Series Pulser Options: Instruction ManualRómulo Zevallos GutiérrezNo ratings yet

- HMC Auh312Document17 pagesHMC Auh312payam79bNo ratings yet

- THVD1500 500 Kbps RS-485 Transceivers With 8-kV IEC ESD ProtectionDocument29 pagesTHVD1500 500 Kbps RS-485 Transceivers With 8-kV IEC ESD ProtectionsyahabdulrizalNo ratings yet

- Mgate Mb3170/Mb3270 Quick Installation Guide: Edition 7.1, February 2016Document6 pagesMgate Mb3170/Mb3270 Quick Installation Guide: Edition 7.1, February 2016heikelNo ratings yet

- Lm3241 6-Mhz, 750-Ma Miniature, Adjustable, Step-Down DC-DC Converter For RF Power AmplifiersDocument28 pagesLm3241 6-Mhz, 750-Ma Miniature, Adjustable, Step-Down DC-DC Converter For RF Power AmplifiersMahmoud EL-SayedNo ratings yet

- Radio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142From EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142No ratings yet

- Presto enDocument100 pagesPresto encurzNo ratings yet

- (At Command) Usr Tcp232 E2 at Command Set - v1.0.0Document22 pages(At Command) Usr Tcp232 E2 at Command Set - v1.0.0curzNo ratings yet

- 50650.installation Guide 2061303Document39 pages50650.installation Guide 2061303curzNo ratings yet

- Horizon Compact Plus Loss of Management After 208 Days - TN-000041-01-En-02Document5 pagesHorizon Compact Plus Loss of Management After 208 Days - TN-000041-01-En-02curzNo ratings yet

- Manual Do ProdutoDocument26 pagesManual Do ProdutocurzNo ratings yet

- Resumen SW NewDocument20 pagesResumen SW NewcurzNo ratings yet

- Cambium PTP 650 Series User Guide: System Release 650-01-00Document196 pagesCambium PTP 650 Series User Guide: System Release 650-01-00curzNo ratings yet

- VI-200 / VI-J00 Family: Design Guide & Applications ManualDocument97 pagesVI-200 / VI-J00 Family: Design Guide & Applications ManualcurzNo ratings yet

- LTC 4252Document37 pagesLTC 4252curzNo ratings yet

- Manual Do ProdutoDocument26 pagesManual Do ProdutocurzNo ratings yet

- Sofix Power Cable AssembliesDocument2 pagesSofix Power Cable AssembliescurzNo ratings yet

- Manual Do ProdutoDocument26 pagesManual Do ProdutocurzNo ratings yet

- Important Notice: Kind RegardsDocument15 pagesImportant Notice: Kind RegardscurzNo ratings yet

- Customer Release Notes 07 01 83 7 1 Phase I - RGMDocument18 pagesCustomer Release Notes 07 01 83 7 1 Phase I - RGMcurzNo ratings yet

- Customer Release Notes 07 01 83 7 1 Phase I - RGMDocument17 pagesCustomer Release Notes 07 01 83 7 1 Phase I - RGMcurzNo ratings yet

- UPC2762TB: Bipolar Analog Integrated CircuitDocument6 pagesUPC2762TB: Bipolar Analog Integrated CircuitcurzNo ratings yet

- Credenziali ARIADocument1 pageCredenziali ARIAcurzNo ratings yet

- HA178L00 Series: 3-Terminal Fixed Voltage RegulatorsDocument22 pagesHA178L00 Series: 3-Terminal Fixed Voltage RegulatorscurzNo ratings yet

- 2.5-6.0/5.0-12.0 GHZ Gaas Mmic Active Doubler: Features Chip Device Layout X1002-BdDocument5 pages2.5-6.0/5.0-12.0 GHZ Gaas Mmic Active Doubler: Features Chip Device Layout X1002-BdcurzNo ratings yet

- Key Features: Bias: VD 5 V & 7 V, Idq 1.05 ADocument18 pagesKey Features: Bias: VD 5 V & 7 V, Idq 1.05 AcurzNo ratings yet

- Rtcclient Tool Quick Guide: Date Jan. 25, 2011Document3 pagesRtcclient Tool Quick Guide: Date Jan. 25, 2011curzNo ratings yet

- Europe Power Cord Specs PDFDocument9 pagesEurope Power Cord Specs PDFcurzNo ratings yet

- Board PcChips M756LMRT-M756LRT-M756TDocument43 pagesBoard PcChips M756LMRT-M756LRT-M756Tmelecobd0% (1)

- Galaxy S20+ 5G (G986U1) Application ListDocument8 pagesGalaxy S20+ 5G (G986U1) Application ListxvitehxNo ratings yet

- Nokia Operations in BangladeshDocument38 pagesNokia Operations in Bangladeshmmnaim90No ratings yet

- Arduino Based Digital Temperature Sensor With 7-Segment Displays-1 DOCUMENTATIONDocument21 pagesArduino Based Digital Temperature Sensor With 7-Segment Displays-1 DOCUMENTATIONchandramahesh736No ratings yet

- Cory R Garrett Resume For WeeblyDocument1 pageCory R Garrett Resume For Weeblyapi-283375341No ratings yet

- Ip Sample Paper 7Document8 pagesIp Sample Paper 7NEEMA GANDHINo ratings yet

- Manual Mic Geffel MT-71-S - 9kIAtDocument2 pagesManual Mic Geffel MT-71-S - 9kIAtTati RossiNo ratings yet

- Automotive Study RO-SBDocument69 pagesAutomotive Study RO-SBioanchiNo ratings yet

- Voltex ElectricalDocument80 pagesVoltex Electricalmustang460100% (1)

- RX 360 GMP Audit Manual Data Governance and Data IntegrityDocument24 pagesRX 360 GMP Audit Manual Data Governance and Data Integrityjess100% (2)

- Alteon ITM TrainingDocument39 pagesAlteon ITM Training李謝揚No ratings yet

- Diff Wire & Wireless Comm SlideDocument12 pagesDiff Wire & Wireless Comm SlideKila HamzahNo ratings yet

- PRICE MATCH ModuleDocument6 pagesPRICE MATCH Module3dicNo ratings yet

- SOP Building & MaintenanceDocument6 pagesSOP Building & MaintenanceTitien HermansyahNo ratings yet

- 74HC86Document9 pages74HC86jnax101No ratings yet

- P6 EPPM Server RequirementsDocument21 pagesP6 EPPM Server RequirementsCarlosCerdaRuizNo ratings yet

- Commercialization PDFDocument102 pagesCommercialization PDFasolisNo ratings yet

- BRD TemplateDocument7 pagesBRD TemplatethorstenNo ratings yet

- Beats PILL User ManualDocument40 pagesBeats PILL User ManualJohn M. RoyNo ratings yet

- B2 UNIT 9 Life Skills Video WorksheetDocument1 pageB2 UNIT 9 Life Skills Video WorksheetmairaNo ratings yet

- Flag-F (Logistics Note-G20-ETWG-1-Indonesia)Document5 pagesFlag-F (Logistics Note-G20-ETWG-1-Indonesia)SHAILENDRA SINGHNo ratings yet

- ANT-APE4518R34v06 Datasheet BasicDocument1 pageANT-APE4518R34v06 Datasheet BasicvyshyNo ratings yet

- EN - ISO - 10423 (2004) - (E) CodifiedDocument7 pagesEN - ISO - 10423 (2004) - (E) CodifiedjczezarNo ratings yet

- The 8051 Microcontroller & Embedded Systems: Muhammad Ali Mazidi, Janice Mazidi & Rolin MckinlayDocument50 pagesThe 8051 Microcontroller & Embedded Systems: Muhammad Ali Mazidi, Janice Mazidi & Rolin MckinlayAkshwin KisoreNo ratings yet

- Machine Design 2021 Guidelines and MechanicsDocument2 pagesMachine Design 2021 Guidelines and Mechanicsreneil llegueNo ratings yet

- Child Labor Laws PDFDocument1 pageChild Labor Laws PDFapi-270507494No ratings yet

- Avh-X7700bt Update Instruction Ver853 PDFDocument3 pagesAvh-X7700bt Update Instruction Ver853 PDFLaloPianoNo ratings yet

- Wiring-diagram-Avanza Combination Meter Manual OnlyDocument2 pagesWiring-diagram-Avanza Combination Meter Manual OnlyMurham Munir100% (4)

- Selwico CS4000 User ManualDocument46 pagesSelwico CS4000 User Manualcostica100% (4)