Professional Documents

Culture Documents

Ua 2240 CN

Ua 2240 CN

Uploaded by

qlx4Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ua 2240 CN

Ua 2240 CN

Uploaded by

qlx4Copyright:

Available Formats

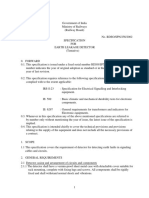

uA2240C PROGRAMMABLE TIMER/COUNTER

SLFS045 JUNE 1978 REVISED MAY 1988

D D D D D

Accurate Timing From Microseconds to Days Programmable Delays From 1 Time Constant to 255 Time Constants Outputs Compatible With TTL and CMOS Wide Supply-Voltage Range External Sync and Modulation Capability

N PACKAGE (TOP VIEW)

OUTPUTS

description

The uA2240C consists of a time-base oscillator, an 8-bit counter, a control flip-flop, and a voltage regulator. The frequency of the time-base oscillator is set by the time constant of an external resistor and capacitor at R/C and can be synchronized or modulated by signals applied to the modulation input. The output of the time-base section is applied directly to the input of the counter section and also appears at (TIME BASE). TIME BASE may be used to monitor the frequency of the oscillator, to provide an output pulse to other circuitry, or (with the time-base section disabled) to drive the counter input from an external source. The counter input is activated on a negative-going transition. The reset input stops the time-base oscillator and sets each binary output, Q0Q7, and the time-base output to a TTL high level. After resetting, the trigger input starts the oscillator and all Q outputs go low. Once triggered, the uA2240C will ignore any signals at the trigger input until it is reset. The uA2240C timer/counter may be operated in the free-running mode or with output-signal feedback to the reset input for automatic reset. Two or more binary outputs may be connected together to generate complex pulse patterns, or each output may be used separately to provide eight output frequencies. Using two circuits in cascade can provide precise time delays of up to three years. The uA2240C is characterized for operation from 0C to 70C.

AVAILABLE OPTIONS SYMBOLIZATION DEVICE uA2240C PACKAGE SUFFIX N OPERATING TEMPERATURE RANGE 0C to 70C VT max AT 25C 2V

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

1 2 3 4 5 6 7 8

16 15 14 13 12 11 10 9

VCC REGULATOR TIME BASE R/C MODULATION TRIGGER RESET GND

OUTPUTS

INPUTS

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1988, Texas Instruments Incorporated

POST OFFICE BOX 655303 DALLAS, TEXAS 75265 POST OFFICE BOX 1443 HOUSTON, TEXAS 772511443

uA2240C PROGRAMMABLE TIMER/COUNTER

SLFS045 JUNE 1978 REVISED MAY 1988

functional block diagram

VCC 16 REG OUT 15

TRIGGER

11

S & R

Voltage Regulator

RESET

10

Time Base Oscillator 7 k 12 12 k R/C 13 T T T S S S

MODULATION

GND

9 14 Time Base Q0 1 Q1 2 Q7 8

= open-collector outputs

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage, VCC (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 V Output voltage: Q0 Q7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 V Output current: Q0 Q7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 mA Regulator output current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 mA Continuous total dissipation at (or below) 25C free-air temperature . . . . . . . . . . . . . . . . . . . . . . . . . . 650 mW Operating free-air temperature range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0C to 70C Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260C

NOTE 1: Voltage values are with respect to the network ground terminal.

recommended operating conditions

MIN Supply voltage, VCC (see Note 2) Timing resistor Timing capacitor Counter input frequency (Pin 14) Pull-up resistor, time-based output Trigger and reset input pulse voltage Trigger and reset input pulse duration External clock input pulse voltage External clock input pulse duration NOTE 2: For operation with VCC 4.5 V, short regulator output to VCC. 2 2 3 1 4 0.001 0.01 1.5 20 3 NOM MAX 14 10 1000 UNIT V M F MHz k V s V s

POST OFFICE BOX 655303 DALLAS, TEXAS 75265 POST OFFICE BOX 1443 HOUSTON, TEXAS 772511443

uA2240C PROGRAMMABLE TIMER/COUNTER

SLFS045 JUNE 1978 REVISED MAY 1988

electrical characteristics at 25C free-air temperature

PARAMETER Regulator output voltage Modulation input open circuit voltage Trigger threshold voltage High-level trigger current Reset threshold voltage High-level reset current Counter input (time base) threshold voltage Low-level output current, Q0 Q7 High-level output current, Q0 Q7 Supply current TEST CIRCUIT 1 2 1 1 1 1 1 2 2 2 1 1 3 VCC = 5 V, VCC = 15 V, VCC = 5 V, VCC = 15 V, VCC = 5 V, VCC = 5 V, VCC = 5 V, VCC = 5 V, VCC = 5 V, VCC = 5 V, VOL < 0.4 V VOH = 15 V, VCC = 5 V, VCC = 15 V, V+ = 4 V TEST CONDITIONS TRIGGER and RESET open or grounded TRIGGER and RESET open or grounded TRIGGER and RESET open or grounded TRIGGER and RESET open or grounded RESET at 0 V TRIGGER at 2 V, TRIGGER at 0 V TRIGGER at 0 V TRIGGER and RESET open or grounded TRIGGER at 2 V, RESET at 2 V, TRIGGER at 0 V, TRIGGER at 0 V, RESET at 0 V, TRIGGER at 0 V RESET at 5 V RESET at 5 V 1 2 RESET at 0 V MIN 3.9 5.8 2.8 TYP 4.4 6.3 3.5 10.5 1.4 10 1.4 10 1.4 4 0.01 4 13 1.5 15 7 18 mA 2 2 6.8 4.2 MAX UNIT V V V A V A V mA A

operating characteristics at 25C free-air temperature (unless otherwise noted)

PARAMETER Initial error of time base Temperature coefficient of timebase period Supply voltage sensitivity of timebase period Time-base output frequency Propagation delay time Output rise time 2 TEST CIRCUIT 1 1 1 1 VCC = 5 V, TEST CONDITIONS TRIGGER at 5 V, RESET at 0 V VCC = 5 V VCC = 15 V MIN TYP 0.5 200 80 0.08 R = MIN, C = MIN From TRIGGER input From RESET input CL = 10 pF Q0 Q7 130 1 0.8 180 0.3 MAX 5 UNIT % ppm/C %/ V kHz s

TA = 0C to 70C VCC 8 V VCC = 5 V, See Note 3 RL = 3 k k,

ns Output fall time 180 For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions. This is the time-base period error due only to the uA2240C and expressed as a percentage of nominal (1.00 RC). NOTE 3: Propagation delay time is measured from the 50% point on the leading edge of an input pulse to the 50% point on the leading edge of the resulting change of state at Q0.

POST OFFICE BOX 655303 DALLAS, TEXAS 75265 POST OFFICE BOX 1443 HOUSTON, TEXAS 772511443

uA2240C PROGRAMMABLE TIMER/COUNTER

SLFS045 JUNE 1978 REVISED MAY 1988

PARAMETER MEASUREMENT INFORMATION

VCC R = 10 k (Unless Otherwise Specified) 0.01 F Connected for Operating Characteristics Tests Only

R/C C = 0.1 F (Unless Otherwise Specified) TRIG RESET TIME BASE Q0 20 k Q1 uA2240C

MOD

VCC

REGULATOR Q4 Q5 Q6 Q7

Q2

Q3

Each Q0 Thru Q7 Output Load = 10 k

Figure 1. General Test Circuit

VCC

1 k (Disables Oscillator) 3V 0V Input Signal for Operating Characteristics Tests Only R/C TRIG RESET Time Base Q0 Q1 uA2240C Q2 Q3 Q4 Q5 Q6 Q7 MOD VCC REGULATOR (Open)

Each QO Thru Q7 Output Load = RL

Figure 2. Counter Test Circuit

(Open) V+ = 4 V

R/C TRIG RESET TIME BASE Q0 Q1

MOD

VCC REGULATOR

uA2240C Q2 Q3 Q4

Q5

Q6

Q7

Each QO Thru Q7 Output Load = 10 k These connections may be open or ungrounded for this test.

Figure 3. Reduced-Power Test Circuit (Time Base Disabled)

POST OFFICE BOX 655303 DALLAS, TEXAS 75265 POST OFFICE BOX 1443 HOUSTON, TEXAS 772511443

uA2240C PROGRAMMABLE TIMER/COUNTER

SLFS045 JUNE 1978 REVISED MAY 1988

TYPICAL CHARACTERISTICS

NORMALIZED TIME-BASE PERIOD vs MODULATION INPUT VOLTAGE

2.5

2 Normalize Timing

1.5

RC 0.5 0 1 2 3 4 5 6 Modulation Voltage V

Figure 4

APPLICATION INFORMATION

Figure 5 shows voltage waveforms for typical operation of the uA2240C. If both RESET and TRIGGER are low during power up, the timer/ counter will be in a reset state with all binary (Q) outputs high and the oscillator stopped. In this state, a high level on the trigger input starts the time-base oscillator. The initial negative-going pulse from the oscillator sets the Q outputs to low logic levels at the beginning of the first time-base period. The uA2240C will ignore any further signals at the TRIGGER until after a reset signal is applied to RESET. With TRIGGER low, a high level at the reset input will set Q outputs high and stop the time-base oscillator. If the reset signal occurs while TRIGGER is high, the reset is ignored. If RESET remains high when TRIGGER goes low, the uA2240C will reset.

TRIGGER RESET TBO Q0 Q1 Q7

Figure 5. Timing Diagram of Output Waveform

POST OFFICE BOX 655303 DALLAS, TEXAS 75265 POST OFFICE BOX 1443 HOUSTON, TEXAS 772511443

uA2240C PROGRAMMABLE TIMER/COUNTER

SLFS045 JUNE 1978 REVISED MAY 1988

APPLICATION INFORMATION

In monostable applications of the uA2240C, one or more of the binary outputs will be connected to RESET as shown in Figure 6. The binary outputs are open-collector stages that can be connected together to a common pullup resistor to provide a wired-OR function. The combined output will be low as long as any one of the outputs is low. This type of arrangement can be used for time delays that are integer multiples of the time-base period. For example, if Q5 (25 = 32) only is connected to the reset input, every trigger pulse will generate a 32-period active-low output. Similarly, if Q0, Q4, and Q5 are connected to RESET, each trigger pulse creates a 49-period delay. In astable operation, the uA2240C will free-run from the time it is triggered until it receives an external reset signal. The period of the time-base oscillator is equal to the RC time constant of an external resistor and capacitor connected as shown in Figure 6 when the modulation input is open (approximately 3.5 V internal, (see Figure 4). Under conditions of high supply voltage (VCC > 7 V) and low value of timing capacitor (C < 0.1 F), the pulse duration of the time-base oscillator may be too short to properly trigger the counters. This situation can be corrected by adding a 300-pF capacitor between the time-base output and ground. The time-base output (TBO) is an open-collector output that requires a 20-k pullup resistor in VREG for proper operation. The time-base pin may also be used as an input to the counters for an external timebase or as an active-low inhibit to interrupt counting without resetting. The modulation input varies the ratio of the time-base period to the RC time constant as a function of the DC bias voltage (see Figure 4). It can also be used to synchronize the timer/counter to an external clock or sync signal. The regulator output is used internally to drive the binary counters and the control logic. This terminal can be used to supply voltage to additional uA2240C devices to minimize power dissipation when several timer circuits are cascaded. For circuit operation with an external clock, the regulator output can be used as the VCC input terminal to power down the internal time base and reduce power dissipation. When supply voltages less than 4.5 V are used with the internal time base, VREG should be shorted to VCC.

VCC

16 R 13 RC C 0.1 F 12 11 TRIGGER 10 RESET 4.7 k GND 9 S1 MODULATOR TIME BASE uA2240 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 VCC REGULATOR

15 20 k 14 1 2 3 4 5 6 7 8 Output 10 k RL

Figure 6. Basic Connections for Timing Applications

POST OFFICE BOX 655303 DALLAS, TEXAS 75265 POST OFFICE BOX 1443 HOUSTON, TEXAS 772511443

IMPORTANT NOTICE Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TIs standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements. CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (CRITICAL APPLICATIONS). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMERS RISK. In order to minimize risks associated with the customers applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TIs publication of information regarding any third partys products or services does not constitute TIs approval, warranty or endorsement thereof.

Copyright 1998, Texas Instruments Incorporated

You might also like

- Short Circuit 3Document3 pagesShort Circuit 3Gaspar Howell Minga0% (2)

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Manufacturing Process of Speaker EnclosureDocument8 pagesManufacturing Process of Speaker EnclosureShoaib AhmadNo ratings yet

- Telemecanique Altivar28 Manual PDFDocument74 pagesTelemecanique Altivar28 Manual PDFqlx4No ratings yet

- 12 Volt Relay Wiring DiagramDocument1 page12 Volt Relay Wiring Diagramgoshhub100% (1)

- SN 74 HCT 245Document22 pagesSN 74 HCT 245agiyafersyaNo ratings yet

- SN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsDocument7 pagesSN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsMadhukar PuliNo ratings yet

- D D D D: SN54ACT573, SN74ACT573 Octal D-Type Transparent Latches With 3-State OutputsDocument16 pagesD D D D: SN54ACT573, SN74ACT573 Octal D-Type Transparent Latches With 3-State OutputsĐạt Hoàng TrầnNo ratings yet

- D D D D D D D D D: SN75C188 Quadruple Low-Power Line DriversDocument10 pagesD D D D D D D D D: SN75C188 Quadruple Low-Power Line DriversMarimuthu RajNo ratings yet

- Datasheet SN74HC04 - Hex InversorDocument16 pagesDatasheet SN74HC04 - Hex InversorPablo CarvalhoNo ratings yet

- Max 232Document14 pagesMax 232abcx397No ratings yet

- SN 74 HCT 244Document22 pagesSN 74 HCT 244Filipe BrendlerNo ratings yet

- Dual Retriggerable Monostable Multivibrator: Order CodesDocument12 pagesDual Retriggerable Monostable Multivibrator: Order Codeswrite2skNo ratings yet

- 78 hct14Document16 pages78 hct14Bruno AlvesNo ratings yet

- SN754410 Quadruple Half-H Driver: 1,2EN 1A 1Y V 4A 4Y Heat Sink and Ground 3Y 3A 3,4EN Heat Sink and GroundDocument10 pagesSN754410 Quadruple Half-H Driver: 1,2EN 1A 1Y V 4A 4Y Heat Sink and Ground 3Y 3A 3,4EN Heat Sink and GroundFrankin Esteban Carmona AguilarNo ratings yet

- D D D D D D D D D: Description/ordering InformationDocument18 pagesD D D D D D D D D: Description/ordering InformationMauricio BarriosNo ratings yet

- D D D D D D D D D: Description/ordering InformationDocument17 pagesD D D D D D D D D: Description/ordering InformationStephanny Muñoz CotrinaNo ratings yet

- D D D D D D D D D: Description/ordering InformationDocument18 pagesD D D D D D D D D: Description/ordering InformationJayson SarionNo ratings yet

- Uc3842 Monitor Power Supply Regulator IcDocument7 pagesUc3842 Monitor Power Supply Regulator IcJoseph Sidhom SnadaNo ratings yet

- D D D D D D D D D D D: Description/ordering InformationDocument15 pagesD D D D D D D D D D D: Description/ordering InformationDomsNo ratings yet

- Datasheet Search Site - WWW - AlldatasheetDocument23 pagesDatasheet Search Site - WWW - AlldatasheetPanagiotis PanagosNo ratings yet

- Description Features: CMOS Low-Power Monostable/Astable MultivibratorDocument15 pagesDescription Features: CMOS Low-Power Monostable/Astable Multivibratorதினேஷ் குமார்No ratings yet

- Mc1455-d Timer IcDocument11 pagesMc1455-d Timer IcDecker JamesNo ratings yet

- 75C189Document20 pages75C189guy426No ratings yet

- LM555 Single Timer: Features DescriptionDocument13 pagesLM555 Single Timer: Features Descriptionduy2706No ratings yet

- MC1455Document13 pagesMC1455eduardolsNo ratings yet

- Lm555 555c TimerDocument12 pagesLm555 555c TimerAlexis Orellana VediaNo ratings yet

- D D D D D D D D D: Description/ordering InformationDocument16 pagesD D D D D D D D D: Description/ordering InformationCarlos de SouzaNo ratings yet

- CD4047Document15 pagesCD4047mohankumarktvrNo ratings yet

- Current Mode PWM Controller: Features DescriptionDocument9 pagesCurrent Mode PWM Controller: Features DescriptionJozo ĆurčićNo ratings yet

- 74LS14Document16 pages74LS14Daniela S Arroba CNo ratings yet

- SN74LS273N PDFDocument7 pagesSN74LS273N PDFOsman KoçakNo ratings yet

- AM26C32CDocument17 pagesAM26C32Cvanhuong87No ratings yet

- 74 HC 191Document10 pages74 HC 191Ravi RathodNo ratings yet

- Ci MonoestableDocument13 pagesCi MonoestableGary DiazNo ratings yet

- Datasheet.... Schmitt TriggerDocument22 pagesDatasheet.... Schmitt TriggerIc CruiseNo ratings yet

- Sn7414 Schmitt TriggerDocument13 pagesSn7414 Schmitt TriggerFaazil FairoozNo ratings yet

- Single Timer: Features DescriptionDocument13 pagesSingle Timer: Features DescriptionRicardo Pasquati PontarolliNo ratings yet

- D D D D D D: AM26LS31C Quadruple Differential Line DriverDocument10 pagesD D D D D D: AM26LS31C Quadruple Differential Line Drivercucu77No ratings yet

- L293 Quadruple Half-H Driver: Description Logic SymbolDocument5 pagesL293 Quadruple Half-H Driver: Description Logic SymbolSiddhant YadavNo ratings yet

- D D D D D D: SN74LVC244A Octal Buffer/Driver With 3-State OutputsDocument6 pagesD D D D D D: SN74LVC244A Octal Buffer/Driver With 3-State OutputsAhmad JamilNo ratings yet

- IC-ON-LINE - CN In74hc164a 4331941Document6 pagesIC-ON-LINE - CN In74hc164a 4331941enriquevagoNo ratings yet

- CD4541 PDFDocument7 pagesCD4541 PDFtutesamNo ratings yet

- 74HC14Document15 pages74HC14Adilson LucaNo ratings yet

- D D D D D D D: TL7757 Supply-Voltage Supervisor and Precision Voltage DetectorDocument20 pagesD D D D D D D: TL7757 Supply-Voltage Supervisor and Precision Voltage DetectorToni BioscaNo ratings yet

- Hcf4541bey ApplicationDocument10 pagesHcf4541bey ApplicationAlecsandru NitaNo ratings yet

- Data Sheet: IC Timers 555 and 556Document8 pagesData Sheet: IC Timers 555 and 556Adenilson MatiasNo ratings yet

- D D D D D D D: Description/ordering InformationDocument17 pagesD D D D D D D: Description/ordering InformationYugi Abdul LathifNo ratings yet

- Adc 0804 DatasheetDocument7 pagesAdc 0804 DatasheetPamela AricoNo ratings yet

- LM555 Timer: General Description FeaturesDocument12 pagesLM555 Timer: General Description FeaturesMark J A. OkyoNo ratings yet

- 74 HC 4538Document11 pages74 HC 4538vagitusNo ratings yet

- Ne5534 PDFDocument7 pagesNe5534 PDFJhelson CondeNo ratings yet

- 8-Bit Serial-Input/Serial or Parallel-Output Shift Register With Latched 3-State OutputsDocument11 pages8-Bit Serial-Input/Serial or Parallel-Output Shift Register With Latched 3-State OutputsLưu TinhNo ratings yet

- Octal Bus Transceiver With 3-State Outputs: FeaturesDocument24 pagesOctal Bus Transceiver With 3-State Outputs: FeaturesLungoci AdrianNo ratings yet

- 3414ADocument12 pages3414AfaneiNo ratings yet

- 555 Oscilador Datasheet PDFDocument6 pages555 Oscilador Datasheet PDFArlés GómezNo ratings yet

- NE/SA/SE555/SE555C: TimerDocument12 pagesNE/SA/SE555/SE555C: TimerPhoenix AngelNo ratings yet

- UC3524Document6 pagesUC3524Rudy Manuel Huamani FernandezNo ratings yet

- Max232 Icl232 PDFDocument5 pagesMax232 Icl232 PDFIván MeyerNo ratings yet

- Datasheet Fairchild UC3843Document7 pagesDatasheet Fairchild UC3843Tina JohnsonNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Simpson 269-2 User Manual-1966Document19 pagesSimpson 269-2 User Manual-1966qlx467% (3)

- Power Kata Log 2006Document140 pagesPower Kata Log 2006tarpinoNo ratings yet

- Digital Aud 25 A 1200WDocument9 pagesDigital Aud 25 A 1200Wqlx4No ratings yet

- HF Transceiver PDFDocument13 pagesHF Transceiver PDFlg900df5063No ratings yet

- MK RTDocument339 pagesMK RTqlx4100% (1)

- Circuito 5 D1 A D6 Silicio 1000V P.I.V.: R1 R2 R3 Q1 Q2 Q3 Q4 Q5-8 C1 R4 - 7Document2 pagesCircuito 5 D1 A D6 Silicio 1000V P.I.V.: R1 R2 R3 Q1 Q2 Q3 Q4 Q5-8 C1 R4 - 7qlx4No ratings yet

- Sinfin de CarniceriaDocument25 pagesSinfin de Carniceriaqlx4No ratings yet

- F30u60 Ultra Fast DiodeDocument4 pagesF30u60 Ultra Fast Diodeqlx4No ratings yet

- Infineon IGBT ModulesDocument16 pagesInfineon IGBT Modulesqlx4No ratings yet

- Scan FABDocument2 pagesScan FABqlx4No ratings yet

- Andrew ATM200 A20Document3 pagesAndrew ATM200 A20Vin Pruebas0% (1)

- Tugas 11 Bahasa InggrisDocument2 pagesTugas 11 Bahasa InggrisGesa Ananda Putra BTNFCNo ratings yet

- Electromagnetic Effects Part 1Document16 pagesElectromagnetic Effects Part 1SamuelGideonSimatupaNo ratings yet

- ECEL ProjectDocument6 pagesECEL ProjectPeter AndrewNo ratings yet

- L002 DatasheetDocument1 pageL002 DatasheetPușcă MartinNo ratings yet

- Carlo Gavazzi Small CatDocument226 pagesCarlo Gavazzi Small CatkcraussNo ratings yet

- Ps-I Pse Te Elt New Cgpa (Set1)Document51 pagesPs-I Pse Te Elt New Cgpa (Set1)TUFAN GAMINGNo ratings yet

- Residual Current Circuit Breakers: Afi Type Ac - NfitypeaDocument38 pagesResidual Current Circuit Breakers: Afi Type Ac - NfitypeaGrydon ChimeraNo ratings yet

- Solar Charge Controller Basics - Northern Arizona Wind & SunDocument3 pagesSolar Charge Controller Basics - Northern Arizona Wind & SunGepel OntanillasNo ratings yet

- MT6570 Android ScatterDocument7 pagesMT6570 Android ScatterВасилий ИвановNo ratings yet

- Mca Manual Feb12Document15 pagesMca Manual Feb12luistorcatt72No ratings yet

- Advantages of Angle Modulation Compared With Amplitude ModulationDocument3 pagesAdvantages of Angle Modulation Compared With Amplitude ModulationBilly Joe C. Samonte33% (3)

- Rain Gauge Smart Sensor (S-Rgx-M002) Manual: SpecificationsDocument3 pagesRain Gauge Smart Sensor (S-Rgx-M002) Manual: SpecificationsYoudivin inmypoolNo ratings yet

- Price List: Ref. Description P.V.PDocument78 pagesPrice List: Ref. Description P.V.PKamal BennaniNo ratings yet

- Mcqs On BcsDocument1,172 pagesMcqs On Bcskomal bandleNo ratings yet

- RdsoDocument7 pagesRdsoMrinmy ChakrabortyNo ratings yet

- X15a User ManualDocument8 pagesX15a User ManualMoises MojicaNo ratings yet

- Uponor Smatrix Space/Space PLUS: Uk Installation and Operation ManualDocument40 pagesUponor Smatrix Space/Space PLUS: Uk Installation and Operation Manualjamppajoo2No ratings yet

- ScienceSLM G7 Q3 M6 ElectricityDocument29 pagesScienceSLM G7 Q3 M6 ElectricityXemelle SuelloNo ratings yet

- Horiba: Continuous Monitor For SO Model HORIBA APSA-370Document2 pagesHoriba: Continuous Monitor For SO Model HORIBA APSA-370ikarimzaiNo ratings yet

- Brochure - Poskom PXP-100CA (Inglés)Document4 pagesBrochure - Poskom PXP-100CA (Inglés)David LarreaNo ratings yet

- Compal LA-4491P - LA-4495PDocument52 pagesCompal LA-4491P - LA-4495Pfirman firdausNo ratings yet

- Midland FRS GMRS Portable Comparison SheetDocument1 pageMidland FRS GMRS Portable Comparison SheetMarcos Alberto Francisco de CarvalhoNo ratings yet

- NGD15N41CL, NGB15N41CL, NGP15N41CL Ignition IGBT 15 Amps, 410 VoltsDocument11 pagesNGD15N41CL, NGB15N41CL, NGP15N41CL Ignition IGBT 15 Amps, 410 Voltsmarino246No ratings yet

- UTC 2N3055 Silicon NPN TransistorDocument2 pagesUTC 2N3055 Silicon NPN TransistorPCP MaprisNo ratings yet

- q3p vzh-1Document15 pagesq3p vzh-1Boris ČelebićNo ratings yet

- Chapters IIIDocument29 pagesChapters IIIRon Michael CruzNo ratings yet