Professional Documents

Culture Documents

Stef12E: Electronic Fuse For 12 V Line

Stef12E: Electronic Fuse For 12 V Line

Uploaded by

Anand SalunkeOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Stef12E: Electronic Fuse For 12 V Line

Stef12E: Electronic Fuse For 12 V Line

Uploaded by

Anand SalunkeCopyright:

Available Formats

STEF12E

Datasheet

Electronic fuse for 12 V line

Features

• Continuous current typ. 3.6 A

• N-channel on-resistance typ. 45 mΩ

• Enable/fault functions

DFN10 (3x3 mm)

• Output clamp voltage typ. 15 V

• Undervoltage lockout

• Short-circuit limit

• Overload current limit

• Controlled output voltage ramp

• Thermal latch typ. 165 °C

• Uses tiny capacitors

• Operating junction temp. -40 °C to 125 °C

• Available in DFN10 (3x3 mm) package

Applications

• Hard disk drives

• Solid state drives (SSD)

• Hard disk and SSD arrays

• Set-top boxes

• DVD and Blu-ray disc drivers

Maturity status link

STEF12E Description

The STEF12E is an integrated electronic fuse optimized for monitoring output current

Device summary and input voltage. Connected in series to a 12 V rail, it is capable of protecting the

Order code STEF12EPUR electronic circuitry on its output from overcurrent and overvoltage. The device has a

controlled delay and turn-on time. When an overload condition occurs, the STEF12E

Package DFN10 (3x3 mm) limits the output current to a predefined safe value. If the anomalous overload

Packing Tape and reel condition persists it goes into an open state, disconnecting the load from the power

supply. If a continuous short-circuit is present on the board, when power is re-applied

the E-fuse initially limits the output current to a safe value and then again goes into

an open state. The device is equipped with a thermal protection circuit. The

intervention of the thermal protection is signalled to the board monitoring circuits

through a signal on the Fault pin. Unlike the mechanical fuses, which must be

physically replaced after a single event, the Efuse does not degrade in its

performance after short-circuit/thermal protection interventions and it is reset either

by recycling the supply voltage or using the Enable pin. The companion chip for the 5

V power rails is also available with part number STEF05.

DS12800 - Rev 1 - October 2018 www.st.com

For further information contact your local STMicroelectronics sales office.

STEF12E

Device block diagram

1 Device block diagram

Figure 1. Block diagram

DS12800 - Rev 1 page 2/20

STEF12E

Pin configuration

2 Pin configuration

Figure 2. Pin configuration (top view)

GND Source

dv/dt Source

En/fault VCC Source

I-Limit Source

N/C Source

AMG300320171101MT

Table 1. Pin description

Pin n° Symbol Note

1 GND Ground pin.

The internal dv/dt circuit controls the slew rate of the output voltage on turn-on. The internal

2 dv/dt capacitor allows a ramp-up time of around 1 ms. An external capacitor can be added to this pin to

increase the ramp time. If an additional capacitor is not required, this pin should be left open.

The Enable/Fault pin is a tri-state, bi-directional interface. During normal operation the pin must be

left floating, or it can be used to disable the output of the device by pulling it to ground using an

open drain or open collector device.

3 En/fault

If a thermal fault occurs, the voltage on this pin goes into an intermediate state to signal a monitor

circuit that the device is in thermal shutdown. It can be connected to another device of this family

to cause a simultaneous shutdown during thermal events.

A resistor between this pin and the Source pin sets the overload and short-circuit current limit

4 I-Limit

levels.

5 N/C Not connected.

6 to 10 VOUT/Source Connected to the source of the internal power MOSFET and to the output terminal of the fuse.

11 VCC Exposed pad. Positive input voltage must be connected to VCC.

DS12800 - Rev 1 page 3/20

STEF12E

Maximum ratings

3 Maximum ratings

Table 2. Absolute maximum ratings

Symbol Parameter Value Unit

Positive power supply voltage (steady-state) -0.3 to 18

VCC V

Positive power supply voltage (max. 100 ms) -0.3 to 25

VOUT/source (max. 100 ms) -0.3 to Vcc+0.3 V

I-Limit (max. 100 ms) -0.3 to 25 V

En/fault -0.3 to 7 V

dv/dt -0.3 to 7 V

Top Operating junction temperature range -40 to 125 °C

TSTG Storage temperature range -65 to 150 °C

TLEAD Lead temperature (soldering) 10 s 260 °C

1. The thermal limit is set above the maximum thermal ratings. It is not recommended to operate the device at

temperatures greater than the maximum ratings for extended periods of time.

Note: Absolute maximum ratings are those values beyond which damage to the device may occur. Functional

operation under these conditions is not implied.

Table 3. Thermal data

Symbol Parameter Value Unit

RthJA Thermal resistance junction-ambient 52.7 °C/W

RthJC Thermal resistance junction-case 17.4 °C/W

1. The value refers to the package mounted on a 4 layer JEDEC standard test board with 4 thermal vias

connecting the thermal land to the first buried plane.

Table 4. ESD performance

Symbol Parameter Test condition Value Unit

HBM 2 kV

ESD ESD protection MM 200 V

CDM 500 V

DS12800 - Rev 1 page 4/20

STEF12E

Electrical characteristics

4 Electrical characteristics

VCC = 12 V, VEN = 3.3 V, CI = 10 µF, CO = 47 µF, TJ = 25 °C (unless otherwise specified).

Table 5. Electrical characteristics for STEF12E

Symbol Parameter Test conditions Min. Typ. Max. Unit

Under/overvoltage protection

VClamp Output clamping voltage VCC = 18 V 13.8 15 16.2 V

VUVLO Undervoltage lockout Turn-on, voltage rising 7.7 8.5 9.3 V

VHyst UVLO hysteresis 0.80 V

Power MOSFET

Enabling of chip to ID = 100 mA with a 1 A

tdly Delay time 350 µs

resistive load

35 45 55

RDSon On-resistance (1) mΩ

- 40 °C < TJ < 125 °C (2) 70

VOFF Off-state output voltage VCC = 18 V, VGS = 0, RL = infinite 40 100 mV

0.5 in2 pad, TA = 25 °C (2) 3.6

ID Continuous current A

Minimum copper, TA = 80 °C 1.7

Current limit

IShort Short-circuit current limit RLimit = 22 Ω 3.3 4.4 5.5 A

ILim Overload current limit RLimit = 22 Ω 4.4 A

dv/dt circuit

dv/dt Output voltage ramp time Enable to VOUT = 11.7 V, No Cdv/dt 0.5 0.9 2.6 ms

Enable/fault

VIL Low level input voltage Output disabled 0.35 0.58 0.81 V

VI(INT) Intermediate level input voltage Thermal fault, output disabled 0.82 1.4 1.95 V

VIH High level input voltage Output enabled 1.96 2.64 3.3 V

VI(MAX) High state maximum voltage 3.4 4.3 5.4 V

IIL Low level input current (sink) VEnable = 0 V -10 -30 µA

High level leakage current for

II VEnable = 3.3 V 1 µA

external switch

Total numbers of chips that can be connected to

Maximum fan-out for fault signal 3 Units

this pin for simultaneous shutdown

Total device

Device operational 1.5 2

IBias Bias current mA

Thermal shutdown 1

Vmin Minimum operating voltage 7.6 V

Thermal latch

TSD Shutdown temperature (1) 165 °C

1. Pulse test: pulse width = 300 µs, duty cycle = 2%.

2. Guaranteed by design, but not tested in production.

DS12800 - Rev 1 page 5/20

STEF12E

Typical application

5 Typical application

Figure 3. Application circuit

Figure 4. Typical HDD application circuit

DS12800 - Rev 1 page 6/20

STEF12E

Operating modes

6 Operating modes

6.1 Turn-on

When the input voltage is applied, the enable/fault pin goes up to the high state, enabling the internal control

circuitry.

After an initial delay time of typically 350 µs, the output voltage is supplied with a slope defined by the internal

dv/dt circuitry. If no additional capacitor is connected to dv/dt pin, the total time, from the enable signal going high

to the output voltage reaching the nominal value, is around 1 ms (refer to Figure 5. Delay time and VOUT ramp-up

time).

6.2 Normal operating conditions

The STEF12E E-Fuse behaves like a mechanical fuse, buffering the circuitry on its output with the same voltage

shown on its input, with a small voltage fall due to the N-channel MOSFET RDS(on).

6.3 Output voltage clamp

This internal protection circuit clamps the output voltage to a maximum safe value, typically 15 V, if the input

voltage exceeds this threshold.

6.4 Current limiting

When an overload event occurs, the current limiting circuit reduces the conductivity of the power MOSFET, in

order to clamp the output current at the value selected externally by the limiting resistor RLimit (see

Figure 3. Application circuit).

6.5 Thermal shutdown

If the device temperature exceeds the thermal latch threshold, typically 165 °C, the thermal shutdown circuitry

turns the power MOSFET off, thus disconnecting the load. The EN/fault pin of the device is automatically set to an

intermediate voltage, in order to signal the overtemperature event. In this condition the E-Fuse can be reset either

by cycling the supply voltage or by pulling down the EN pin below the VIL threshold and then releasing it.

6.6 R-Lim calculation

As shown in Figure 3. Application circuit, the device uses an internal N-channel SenseFET with a fixed ratio, to

monitor the output current and limit it at the level set by the user.

To achieve the requested current limitation, the R-Lim value can be estimated by using the following theoretical

formula, together with the graph in Figure 13. Current limit vs. RLimit .

95

RLim = (1)

ISℎort

6.7 Cdv/dt calculation

Connecting a capacitor between the Cdv/dt pin and GND allows the modification of the output voltage ramp-up

time.

Given the desired time interval ∆t, during which the output voltage goes from zero to its maximum value, the

capacitance to be added to the Cdv/dt pin can be calculated using the following theoretical formula:

Cdv = 3.92 × 10−8 ∆ t − 35.3 × 10−12 (2)

dt

Where Cdv/dt is expressed in farads and the time in seconds.

The addition of an external Cdv/dt also influences the initial delay time, defined as the time between the enable

signal going high and the start of the VOUT slope (Figure 5. Delay time and VOUT ramp-up time).

The contribution of the external capacitor to this time interval can be estimated by using the following theoretical

formula:

delay time s = 35 × 10−5 + 71 × 105 × Cdv/dt F (3)

DS12800 - Rev 1 page 7/20

STEF12E

En/fault pin

Figure 5. Delay time and VOUT ramp-up time

12

En/fault

10 delay ramp -up

time time VOUT

8

V

6

0

Time

AMG300320171104MT

6.8 En/fault pin

The En/fault pin has the dual function to control the output of the device and, at the same time, provide the

application with information about the device status.

When it is used as a standard enable pin, it should be connected to an external open-drain or open-collector

device. In this case, when it is pulled to low logic level, it turns the output of the E-Fuse off.

If this pin is left floating, since it has an internal pull-up circuitry, the output of the E-Fuse is kept on, in normal

operating conditions.

In case of thermal fault, the pin is pulled to an intermediate state (Figure 6. En/fault pin status). This signal can be

provided to a monitor circuit, informing it that a thermal shutdown has occurred, or it can be directly connected to

the Enable/fault pin of the other STEFxx devices on the same application in order to achieve a simultaneous

enable/disable feature.

When a thermal fault occurs, the device can be reset either by cycling the supply voltage or by pulling down the

Enable pin below the VIL threshold and then releasing it.

Figure 6. En/fault pin status

DS12800 - Rev 1 page 8/20

STEF12E

Typical performance characteristics

7 Typical performance characteristics

The following plots are referred to the typical application circuit and, unless otherwise noted, at TA = 25 °C.

Figure 7. Clamping voltage vs. temperature Figure 8. UVLO voltage vs. temperature

16.5 9.5

VCC = from 0 to 12 V, R LIMIT = 15 Ω

VCC = 18 V 9.3

16

9.1

8.9

15.5

Output Voltage (V)

UVLO Voltage (V)

8.7

15 8.5

8.3

14.5

8.1

7.9

14

7.7

13.5 7.5

-40 -25 0 25 55 85 125 150 -40 -25 0 25 55 85 125 150

Temperature °C Temperature °C

AMG300320171106MT AMG300320171107MT

Figure 9. UVLO hysteresis vs. temperature Figure 10. Off-state voltage vs. temperature

1.4 250

VCC from 12 to 0 V, RLIMIT = 15 Ω VCC = 18 V, VGS = 0 , R L = infinite

1.2

200

1

UVLO Hysteresys (V)

Output Voltage (mV)

150

0.8

100

0.6

50

0.4

0.2 0

-40 -25 0 25 55 85 125 150 -40 -25 0 25 55 85 125 150

Temperature°C Temperature °C

AMG300320171108MT AMG300320171109MT

Figure 11. Bias current (device operational) Figure 12. ON-resistance vs. temperature

VCC = 12 V, R LIMIT = 15 Ω

2.5

2

Current ( mA)

1.5

0.5

0

-40 -25 0 25 55 85 125 150

Temperature °C

AMG300320171110MT

DS12800 - Rev 1 page 9/20

STEF12E

Typical performance characteristics

Figure 13. Current limit vs. RLimit Figure 14. Thermal latch delay vs. power

9.00

800

VCC = 12 V, T= 25 °C

8.00

7.00

T=25 °C

ILIM

6.00 80 T=55 °C

Limit & Short Current (A)

Thermal Action Time (ms)

ISHORT

T=85 °C

5.00

4.00

3.00 8

2.00

1.00

0.00 0.8

0 10 20 30 40 50 60 70 80 0 10 20 30 40 50 60

External Sensing Resistor (Ω) Power (W)

AMG300320171112MT AMG300320171113MT

Figure 15. VOUT ramp-up vs. enable Figure 16. VOUT clamping

Figure 17. Line transient Figure 18. Startup into output short-circuit

DS12800 - Rev 1 page 10/20

STEF12E

Typical performance characteristics

Figure 19. Thermal latch from 2 A load to short-circuit Figure 20. Startup into output short-circuit (fast rise)

DS12800 - Rev 1 page 11/20

STEF12E

Package information

8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK®

packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions

and product status are available at: www.st.com. ECOPACK® is an ST trademark.

DS12800 - Rev 1 page 12/20

STEF12E

DFN10 (3x3 mm) package information

8.1 DFN10 (3x3 mm) package information

Figure 21. DFN10 (3x3 mm) package outline

7426335_L

DS12800 - Rev 1 page 13/20

STEF12E

DFN10 (3x3 mm) package information

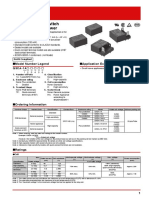

Table 6. DFN10 (3x3 mm) mechanical data

mm

Dim.

Min. Typ. Max.

A 0.80 0.90 1.00

A1 0.02 00.5

A2 0.70

A3 0.20

b 0.18 0.23 0.30

D 2.85 3.00 3.15

D2 2.23 2.38 2.50

E 2.85 3.00 3.15

E2 1.49 1.64 1.75

E3 0.230

E4 0.365

e 0.50

L 0.30 0.40 0.50

ddd 0.08

Figure 22. DFN10 (3x3 mm) recommended footprint

7426335_L

DS12800 - Rev 1 page 14/20

STEF12E

DFN10 (3 x 3 mm) package information

8.2 DFN10 (3 x 3 mm) package information

Figure 23. DFN10 (3x3 mm) tape and reel outline

Table 7. DFN10 (3x3 mm) tape and reel mechanical data

mm

Dim.

Min. Typ. Max.

A 330

C 12.8 13.2

D 20.2

N 60

T 18.4

Ao 3.3

Bo 3.3

Ko 1.1

Po 4

P 8

DS12800 - Rev 1 page 15/20

STEF12E

Revision history

Table 8. Document revision history

Date Revision Changes

30-Oct-2018 1 Initial release.

DS12800 - Rev 1 page 16/20

STEF12E

Contents

Contents

1 Device block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

3 Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

4 Electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

5 Typical application. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

6 Operating modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

6.1 Turn-on . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

6.2 Normal operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

6.3 Output voltage clamp . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

6.4 Current limiting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

6.5 Thermal shutdown. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

6.6 R-Lim calculation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

6.7 Cdv/dt calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

6.8 En/fault pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

7 Typical performance characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

8 Package information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

8.1 DFN10L (3x3 mm) package information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

8.2 DFN10 (3 x 3 mm) package information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

List of tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

List of figures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

DS12800 - Rev 1 page 17/20

STEF12E

List of tables

List of tables

Table 1. Pin description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Table 2. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 3. Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 4. ESD performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 5. Electrical characteristics for STEF12E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Table 6. DFN10 (3x3 mm) mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 7. DFN10 (3x3 mm) tape and reel mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 8. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

DS12800 - Rev 1 page 18/20

STEF12E

List of figures

List of figures

Figure 1. Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Figure 2. Pin configuration (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Figure 3. Application circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 4. Typical HDD application circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 5. Delay time and VOUT ramp-up time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 6. En/fault pin status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 7. Clamping voltage vs. temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 8. UVLO voltage vs. temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 9. UVLO hysteresis vs. temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 10. Off-state voltage vs. temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 11. Bias current (device operational). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 12. ON-resistance vs. temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 13. Current limit vs. RLimit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 14. Thermal latch delay vs. power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 15. VOUT ramp-up vs. enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 16. VOUT clamping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 17. Line transient . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 18. Startup into output short-circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 19. Thermal latch from 2 A load to short-circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 20. Startup into output short-circuit (fast rise) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 21. DFN10 (3x3 mm) package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 22. DFN10 (3x3 mm) recommended footprint. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 23. DFN10 (3x3 mm) tape and reel outline. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

DS12800 - Rev 1 page 19/20

STEF12E

IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST

products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST

products are sold pursuant to ST’s terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of

Purchasers’ products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics – All rights reserved

DS12800 - Rev 1 page 20/20

You might also like

- IP3005A - C181685 enDocument14 pagesIP3005A - C181685 enFernandoNo ratings yet

- EEMAC Codes & StandardsDocument2 pagesEEMAC Codes & StandardsAdam Behiels0% (1)

- tmp15 InstallationDocument2 pagestmp15 InstallationMohammad Nabil AbdullahNo ratings yet

- Loss of Mains Relay Type LMR-122D: Installation and Start Up InstructionsDocument4 pagesLoss of Mains Relay Type LMR-122D: Installation and Start Up InstructionsLUATNo ratings yet

- Proportional Amplifier Type EV22K5: Product DocumentationDocument21 pagesProportional Amplifier Type EV22K5: Product DocumentationAsa ReidNo ratings yet

- Ast965-U12 IgbtDocument6 pagesAst965-U12 IgbtBhethhoNo ratings yet

- Eng SS Ltpe-Qi-3178-01 0310 PDFDocument6 pagesEng SS Ltpe-Qi-3178-01 0310 PDFJosé LuisNo ratings yet

- Tde 1707Document17 pagesTde 1707Fábio MuckenfuhsNo ratings yet

- ICM518 App Guide LIAF247 1Document2 pagesICM518 App Guide LIAF247 1devaughnNo ratings yet

- Chipown: Low Standby-Power Quasi-Resonant Primary-Side ConverterDocument10 pagesChipown: Low Standby-Power Quasi-Resonant Primary-Side ConverterJoaquin Andres AlarconNo ratings yet

- Stdrive 101Document33 pagesStdrive 101AleksMaslyc-zykNo ratings yet

- SI-8120JD: Step-Down To 12.0 V, 1.5 A, DC/DC ConverterDocument10 pagesSI-8120JD: Step-Down To 12.0 V, 1.5 A, DC/DC ConverterStuxnetNo ratings yet

- Stdrive101: Triple Half-Bridge Gate DriverDocument32 pagesStdrive101: Triple Half-Bridge Gate DriverAlper ÜZÜMNo ratings yet

- RMF-112D, Installation Instructions 4189340238 UKDocument5 pagesRMF-112D, Installation Instructions 4189340238 UKFrancisco J. Rodriguez PermuyNo ratings yet

- For Operating Voltage of 3.3V and Below Ultra Low Capacitance: 0.45pF TypicalDocument9 pagesFor Operating Voltage of 3.3V and Below Ultra Low Capacitance: 0.45pF TypicalFábio MenezesNo ratings yet

- Icepower 1000 AspdataDocument27 pagesIcepower 1000 AspdataLuis Eduardo TorcattNo ratings yet

- DatasheetDocument12 pagesDatasheetHoii ClarkNo ratings yet

- For Operating Voltage of 3.3V and Below Ultra Low Capacitance: 0.45pF TypicalDocument9 pagesFor Operating Voltage of 3.3V and Below Ultra Low Capacitance: 0.45pF TypicalChithiran C SspNo ratings yet

- For Operating Voltage of 5V and Below Ultra Low Capacitance: 0.5pF TypicalDocument10 pagesFor Operating Voltage of 5V and Below Ultra Low Capacitance: 0.5pF TypicalTri Nguyen Real EstateNo ratings yet

- KA1L0880B/KA1M0880B: Fairchild Power Switch (FPS)Document10 pagesKA1L0880B/KA1M0880B: Fairchild Power Switch (FPS)vetchboyNo ratings yet

- Tda 8358Document20 pagesTda 8358Alexander CastroNo ratings yet

- FSGM300N Fairchild SemiconductorDocument16 pagesFSGM300N Fairchild SemiconductorValdelio JuniorNo ratings yet

- Preventa Safety Detection XCSE7313Document2 pagesPreventa Safety Detection XCSE7313Alex SkanderNo ratings yet

- Datasheet - 2022-01-05T074219.435Document12 pagesDatasheet - 2022-01-05T074219.435Erasmo Franco SNo ratings yet

- Data Sheet: ACPL-331JDocument23 pagesData Sheet: ACPL-331JPiman MiriNo ratings yet

- FSL106HR Green Mode Fairchild Power Switch (FPS™) : Features DescriptionDocument14 pagesFSL106HR Green Mode Fairchild Power Switch (FPS™) : Features DescriptionDarknezzNo ratings yet

- Features General Description: Source and Sink, 2A, Fast Transient Response Linear RegulatorDocument18 pagesFeatures General Description: Source and Sink, 2A, Fast Transient Response Linear RegulatorEnriqueNo ratings yet

- FSL106HRDocument13 pagesFSL106HRGerson SoaresNo ratings yet

- DRV 8701Document43 pagesDRV 8701P SNo ratings yet

- Datasheet PDFDocument23 pagesDatasheet PDFshamim ahmedNo ratings yet

- Applicationnote: The Protection of USB 2.0 ApplicationsDocument11 pagesApplicationnote: The Protection of USB 2.0 ApplicationsMoritery miraNo ratings yet

- S7PENDocument32 pagesS7PENAnonymous zY8xIMoNo ratings yet

- AP8012 ChipownDocument8 pagesAP8012 ChipownRavi ChavhanNo ratings yet

- FS7M0680, FS7M0880: Fairchild Power Switch (FPS)Document18 pagesFS7M0680, FS7M0880: Fairchild Power Switch (FPS)Candelaria CortesNo ratings yet

- Datasheet TDA 8358JDocument20 pagesDatasheet TDA 8358JJose BenavidesNo ratings yet

- Datasheet TDA8358J PDFDocument20 pagesDatasheet TDA8358J PDFJose BenavidesNo ratings yet

- TPD2015FNDocument17 pagesTPD2015FNLamayah FordNo ratings yet

- AT91SAM7SE Microcontroller Series Schematic Check ListDocument18 pagesAT91SAM7SE Microcontroller Series Schematic Check Listmar_barudjNo ratings yet

- Fdpf7n50u Fdpf7n50u GDocument8 pagesFdpf7n50u Fdpf7n50u Gdhunter ZenfoneNo ratings yet

- E981-10 Elmos DsDocument19 pagesE981-10 Elmos DsgreemaxNo ratings yet

- Current Mode PWM Controller Az3842/3/4/5Document13 pagesCurrent Mode PWM Controller Az3842/3/4/5Emmanuel ZambranoNo ratings yet

- Amc 1311Document36 pagesAmc 1311shivguptaNo ratings yet

- Slvucm 1Document15 pagesSlvucm 1matheuzalexsanderNo ratings yet

- Festo Smt-8m-A-Pns - PsoDocument2 pagesFesto Smt-8m-A-Pns - PsoPedro Luiz PráNo ratings yet

- FDL100N50F D-2312204Document11 pagesFDL100N50F D-2312204x-wire OfficialsNo ratings yet

- KA1M0880D: Fairchild Power Switch (FPS)Document10 pagesKA1M0880D: Fairchild Power Switch (FPS)ja jaNo ratings yet

- SLG7NT402V: An Ultra-Small 3 MM, 8.5 M, 4 A, Internally-Protected Integrated Power SwitchDocument15 pagesSLG7NT402V: An Ultra-Small 3 MM, 8.5 M, 4 A, Internally-Protected Integrated Power Switchremo meinNo ratings yet

- 13 Circuit Descriptions: 13-1 Overall Block Structure Power TreeDocument8 pages13 Circuit Descriptions: 13-1 Overall Block Structure Power Tree81968No ratings yet

- Infineon TLE4252D DS v01 - 40 ENDocument13 pagesInfineon TLE4252D DS v01 - 40 ENMohamed AmineNo ratings yet

- G5ca 1a RelayDocument4 pagesG5ca 1a Relaysdancer75No ratings yet

- Low Capacitance TVS For LVDS Interfaces: Protection Products - Railclamp Description FeaturesDocument7 pagesLow Capacitance TVS For LVDS Interfaces: Protection Products - Railclamp Description FeaturesFakhri AliNo ratings yet

- gm07652r PDFDocument21 pagesgm07652r PDFjose luisNo ratings yet

- AL8812Document11 pagesAL8812julio cesar calveteNo ratings yet

- DS3695 Multipoint RS485 RS422 Transceivers RepeatersDocument17 pagesDS3695 Multipoint RS485 RS422 Transceivers RepeatersJuan Gil Roca100% (1)

- 13 Circuit Descriptions: 13-1 Overall Block Structure Power TreeDocument8 pages13 Circuit Descriptions: 13-1 Overall Block Structure Power TreeJoseni FigueiredoNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- S1 Titan: Innovation With IntegrityDocument4 pagesS1 Titan: Innovation With IntegrityAnand SalunkeNo ratings yet

- RT Acceptance Standard Section IXDocument3 pagesRT Acceptance Standard Section IXAnand SalunkeNo ratings yet

- Mandatory Appendix 4Document8 pagesMandatory Appendix 4Anand SalunkeNo ratings yet

- RT Hole and Wire IQI TableDocument7 pagesRT Hole and Wire IQI TableAnand SalunkeNo ratings yet

- Product Sheet IR 2011: Intended UseDocument1 pageProduct Sheet IR 2011: Intended UseMarcelo Silva100% (2)

- Product Data: 24ABB3 Comfortt13 Air Conditioner With Puronr Refrigerant 1 - 1/2 To 5 Nominal TonsDocument20 pagesProduct Data: 24ABB3 Comfortt13 Air Conditioner With Puronr Refrigerant 1 - 1/2 To 5 Nominal TonsK NavinNo ratings yet

- Cge Drill PipesDocument3 pagesCge Drill Pipesallen wongNo ratings yet

- Fluke 111 Datasheet ID6527Document2 pagesFluke 111 Datasheet ID6527CarlNo ratings yet

- JSS20-48 Single Time Control Digital Display Time Relay: Page 1 / 2Document2 pagesJSS20-48 Single Time Control Digital Display Time Relay: Page 1 / 2FranciscoNo ratings yet

- KS Se3Document35 pagesKS Se3Erik Noer MazhlinaNo ratings yet

- MotherboardDocument4 pagesMotherboardDave SedigoNo ratings yet

- ASM Katalogus 2021 EN CL-616Document1 pageASM Katalogus 2021 EN CL-616Kdr PaxtonNo ratings yet

- How Digital Multimeter Works - VSADocument6 pagesHow Digital Multimeter Works - VSAManish Kumar DubeyNo ratings yet

- GSC003 Rev 03Document31 pagesGSC003 Rev 03Dragos CîmpeanuNo ratings yet

- PC Byte PricelistDocument97 pagesPC Byte PricelistTatsNo ratings yet

- ElektrikaDocument483 pagesElektrikaLotfi Ben SlimNo ratings yet

- Mechatronics - de ZG516Document18 pagesMechatronics - de ZG516Umesh BhadaleNo ratings yet

- MEP NormsDocument4 pagesMEP NormsDilip Kumar75% (4)

- Specifications For Spark-Gap SwitchesDocument11 pagesSpecifications For Spark-Gap SwitchesDavid WalkerNo ratings yet

- DIY Club Project 1 Part 2 of 4 v03Document21 pagesDIY Club Project 1 Part 2 of 4 v03M HNo ratings yet

- Mercosur - India: ANNEX II - India's Offer List To MERCOSURDocument15 pagesMercosur - India: ANNEX II - India's Offer List To MERCOSURapi-3736392No ratings yet

- Escort 5580Document2 pagesEscort 5580liviupuNo ratings yet

- LV PDFDocument44 pagesLV PDFGyanesh BhujadeNo ratings yet

- Cavity Magnetron: Vacuum Tube MicrowavesDocument3 pagesCavity Magnetron: Vacuum Tube MicrowavesPaavni SharmaNo ratings yet

- ГТР manual - 4265757 - C273.7-101 - TPL-1972 - 2013-06-04Document42 pagesГТР manual - 4265757 - C273.7-101 - TPL-1972 - 2013-06-04Sirius PrimeNo ratings yet

- 2013 KTM Power Parts CatalogDocument74 pages2013 KTM Power Parts CatalogGeorge IrelandNo ratings yet

- AC MOX330 12HFN8 R MSEPBU 12HRFN8 R - 1661973296 Eb 2925dcd7Document6 pagesAC MOX330 12HFN8 R MSEPBU 12HRFN8 R - 1661973296 Eb 2925dcd7Szasz ZsomborNo ratings yet

- Stock Report FormateDocument9 pagesStock Report Formatekibria0misNo ratings yet

- KM-2810 DP-110: Parts ListDocument47 pagesKM-2810 DP-110: Parts ListDuplicar Soluções GráficasNo ratings yet

- Brother GTXDocument4 pagesBrother GTXSamantha RalamboniainaNo ratings yet

- Saleem DMP Printer 4Document16 pagesSaleem DMP Printer 4Prince Saleem50% (2)

- cdd161033-LG MS119MLDocument36 pagescdd161033-LG MS119MLfranklin antonio RodriguezNo ratings yet

- Controllable Pitch PropelleDocument12 pagesControllable Pitch PropelleJoshua SanchezNo ratings yet