Professional Documents

Culture Documents

Trenchmos Transistor Buk7624-55 Standard Level Fet: General Description Quick Reference Data

Trenchmos Transistor Buk7624-55 Standard Level Fet: General Description Quick Reference Data

Uploaded by

Nicki LarsonOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Trenchmos Transistor Buk7624-55 Standard Level Fet: General Description Quick Reference Data

Trenchmos Transistor Buk7624-55 Standard Level Fet: General Description Quick Reference Data

Uploaded by

Nicki LarsonCopyright:

Available Formats

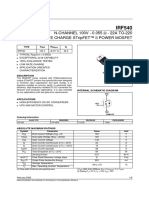

Philips Semiconductors Product specification

TrenchMOS transistor BUK7624-55

Standard level FET

GENERAL DESCRIPTION QUICK REFERENCE DATA

N-channel enhancement mode SYMBOL PARAMETER MAX. UNIT

standard level field-effect power

transistor in a plastic envelope VDS Drain-source voltage 55 V

suitable for surface mounting. Using ID Drain current (DC) 45 A

’trench’ technology the device Ptot Total power dissipation 103 W

features very low on-state resistance Tj Junction temperature 175 ˚C

and has integral zener diodes giving RDS(ON) Drain-source on-state 24 mΩ

ESD protection up to 2kV. It is resistance VGS = 10 V

intended for use in automotive and

general purpose switching

applications.

PINNING - SOT404 PIN CONFIGURATION SYMBOL

PIN DESCRIPTION

d

mb

1 gate

2 drain

g

3 source

2

mb drain 1 3 s

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

VDS Drain-source voltage - - 55 V

VDGR Drain-gate voltage RGS = 20 kΩ - 55 V

±VGS Gate-source voltage - - 16 V

ID Drain current (DC) Tmb = 25 ˚C - 45 A

ID Drain current (DC) Tmb = 100 ˚C - 31 A

IDM Drain current (pulse peak value) Tmb = 25 ˚C - 180 A

Ptot Total power dissipation Tmb = 25 ˚C - 103 W

Tstg, Tj Storage & operating temperature - - 55 175 ˚C

ESD LIMITING VALUE

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

VC Electrostatic discharge capacitor Human body model - 2 kV

voltage, all pins (100 pF, 1.5 kΩ)

THERMAL RESISTANCES

SYMBOL PARAMETER CONDITIONS TYP. MAX. UNIT

Rth j-mb Thermal resistance junction to - - 1.45 K/W

mounting base

Rth j-a Thermal resistance junction to Minimum footprint, FR4 50 - K/W

ambient board

April 1998 1 Rev 1.000

Philips Semiconductors Product specification

TrenchMOS transistor BUK7624-55

Standard level FET

STATIC CHARACTERISTICS

Tj= 25˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V(BR)DSS Drain-source breakdown VGS = 0 V; ID = 0.25 mA; 55 - - V

voltage Tj = -55˚C 50 - - V

VGS(TO) Gate threshold voltage VDS = VGS; ID = 1 mA 2.0 3.0 4.0 V

Tj = 175˚C 1.0 - - V

Tj = -55˚C - - 4.4

IDSS Zero gate voltage drain current VDS = 55 V; VGS = 0 V; - 0.05 10 µA

Tj = 175˚C - - 500 µA

IGSS Gate source leakage current VGS = ±10 V; VDS = 0 V - 0.02 1 µA

Tj = 175˚C - - 20 µA

±V(BR)GSS Gate source breakdown voltage IG = ±1 mA; 16 - - V

RDS(ON) Drain-source on-state VGS = 10 V; ID = 25 A - 19 24 mΩ

resistance Tj = 175˚C - - 50 mΩ

DYNAMIC CHARACTERISTICS

Tmb = 25˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

gfs Forward transconductance VDS = 25 V; ID = 25 A 4 11 - S

Ciss Input capacitance VGS = 0 V; VDS = 25 V; f = 1 MHz - 1100 1500 pF

Coss Output capacitance - 280 340 pF

Crss Feedback capacitance - 130 180 pF

td on Turn-on delay time VDD = 30 V; ID = 25 A; - 12 18 ns

tr Turn-on rise time VGS = 10 V; RG = 10 Ω - 19 35 ns

td off Turn-off delay time Resistive load - 25 35 ns

tf Turn-off fall time - 18 25 ns

Ld Internal drain inductance Measured from upper edge of drain - 2.5 - nH

tab to centre of die

Ls Internal source inductance Measured from source lead - 7.5 - nH

soldering point to source bond pad

REVERSE DIODE LIMITING VALUES AND CHARACTERISTICS

Tj = 25˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

IDR Continuous reverse drain - - 45 A

current

IDRM Pulsed reverse drain current - - 160 A

VSD Diode forward voltage IF = 25 A; VGS = 0 V - 0.95 1.2 V

IF = 40 A; VGS = 0 V - 1.0 -

trr Reverse recovery time IF = 40 A; -dIF/dt = 100 A/µs; - 40 - ns

Qrr Reverse recovery charge VGS = -10 V; VR = 30 V - 0.07 - µC

April 1998 2 Rev 1.000

Philips Semiconductors Product specification

TrenchMOS transistor BUK7624-55

Standard level FET

AVALANCHE LIMITING VALUE

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

WDSS Drain-source non-repetitive ID = 40 A; VDD ≤ 25 V; - - 80 mJ

unclamped inductive turn-off VGS = 10 V; RGS = 50 Ω; Tmb = 25 ˚C

energy

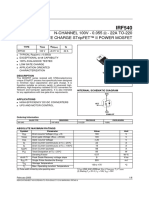

PD% Normalised Power Derating ID / A 7524-55

120 1000

110

100

90

RDS(ON) = VDS / ID

80 100

70 tp = 10 us

60

50 100 us

40 10

DC 1 ms

30

20 10 ms

10

100 ms

0 1

0 20 40 60 80 100 120 140 160 180 1 10 100 1000

Tmb / C VDS / V

Fig.1. Normalised power dissipation. Fig.3. Safe operating area. Tmb = 25 ˚C

PD% = 100⋅PD/PD 25 ˚C = f(Tmb) ID & IDM = f(VDS); IDM single pulse; parameter tp

ID% Normalised Current Derating Transient thermal impedance, Zth (K/W)

120 10

110

100

90 1

0.5

80

0.2

70

0.1

60 0.1 0.05

50 0.02

PD tp tp

40 D=

T

30 0.01 0

20 T t

10

0 0.001

0 20 40 60 80 100 120 140 160 180 10us 1ms 0.1s 10s

Tmb / C pulse width, tp (s)

Fig.2. Normalised continuous drain current. Fig.4. Transient thermal impedance.

ID% = 100⋅ID/ID 25 ˚C = f(Tmb); conditions: VGS ≥ 5 V Zth j-mb = f(t); parameter D = tp/T

April 1998 3 Rev 1.000

Philips Semiconductors Product specification

TrenchMOS transistor BUK7624-55

Standard level FET

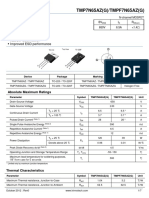

100 25

16 10 9

ID/A VGS/V =

12 gfs/S

8.5

80 20

8.0

7.5

60 15

7.0

40 6.5 10

6.0

20 5

5.5

5.0

4.5

0 0

0 2 4 VSD/V 6 8 10 0 20 40 ID/A 60 80 100

Fig.5. Typical output characteristics, Tj = 25 ˚C. Fig.8. Typical transconductance, Tj = 25 ˚C.

ID = f(VDS); parameter VGS gfs = f(ID); conditions: VDS = 25 V

RDS(ON)/mOhm BUK959-60 Rds(on) normlised to 25degC

40 a

2.5

VGS/V = 6

6.5

35

7 2

30

8 1.5

9

25

10

1

20

15 0.5

0 10 20 30 40 50 60 70 80 -100 -50 0 50 100 150 200

ID/A Tmb / degC

Fig.6. Typical on-state resistance, Tj = 25 ˚C. Fig.9. Normalised drain-source on-state resistance.

RDS(ON) = f(ID); parameter VGS a = RDS(ON)/RDS(ON)25 ˚C = f(Tj); ID = 25 A; VGS = 5 V

100 VGS(TO) / V BUK759-60

5

ID/A

max.

80

4

typ.

60

3

min.

40 2

20 1

Tj/C = 175 25

0 0

0 2 4 6 8 10 12 -100 -50 0 50 100 150 200

VGS/V Tj / C

Fig.7. Typical transfer characteristics. Fig.10. Gate threshold voltage.

ID = f(VGS) ; conditions: VDS = 25 V; parameter Tj VGS(TO) = f(Tj); conditions: ID = 1 mA; VDS = VGS

April 1998 4 Rev 1.000

Philips Semiconductors Product specification

TrenchMOS transistor BUK7624-55

Standard level FET

Sub-Threshold Conduction 100

1E-01

IF/A

80

1E-02

2% typ 98% 60

1E-03

40

1E-04 Tj/C = 175 25

20

1E-05

1E-06 0

0 0.5 1 1.5

0 1 2 3 4 5 VSDS/V

Fig.11. Sub-threshold drain current. Fig.14. Typical reverse diode current.

ID = f(VGS); conditions: Tj = 25 ˚C; VDS = VGS IF = f(VSDS); conditions: VGS = 0 V; parameter Tj

3 WDSS%

120

110

2.5

100

90

Thousands pF

2 80

70

1.5 60

50

1 40

30

20

5

10

0

0 20 40 60 80 100 120 140 160 180

0.01 0.1 1 VDS/V 10 100 Tmb / C

Fig.12. Typical capacitances, Ciss, Coss, Crss. Fig.15. Normalised avalanche energy rating.

C = f(VDS); conditions: VGS = 0 V; f = 1 MHz WDSS% = f(Tmb); conditions: ID = 75 A

12

VGS/V VDD

10

VDS = 14V

+

L

VDS = 44V

8

VDS

6 VGS

-

-ID/100

4 0 T.U.T.

R 01

2 RGS

shunt

0

0 5 10 15 20 25 30 35

QG/nC

Fig.16. Avalanche energy test circuit.

Fig.13. Typical turn-on gate-charge characteristics.

VGS = f(QG); conditions: ID = 50 A; parameter VDS WDSS = 0.5 ⋅ LID2 ⋅ BVDSS /(BVDSS − VDD )

April 1998 5 Rev 1.000

Philips Semiconductors Product specification

TrenchMOS transistor BUK7624-55

Standard level FET

VDD

+

RD

VDS

VGS

-

RG

0 T.U.T.

Fig.17. Switching test circuit.

April 1998 6 Rev 1.000

Philips Semiconductors Product specification

TrenchMOS transistor BUK7624-55

Standard level FET

MECHANICAL DATA

Dimensions in mm 10.3 max 4.5 max

1.4 max

Net Mass: 1.4 g

11 max

15.4

2.5

0.85 max 0.5

(x2)

2.54 (x2)

Fig.18. SOT404 : centre pin connected to mounting base.

MOUNTING INSTRUCTIONS

Dimensions in mm 11.5

9.0

17.5

2.0

3.8

5.08

Fig.19. SOT404 : soldering pattern for surface mounting.

Notes

1. Observe the general handling precautions for electrostatic-discharge sensitive devices (ESDs) to prevent

damage to MOS gate oxide.

2. Epoxy meets UL94 V0 at 1/8".

April 1998 7 Rev 1.000

Philips Semiconductors Product specification

TrenchMOS transistor BUK7624-55

Standard level FET

DEFINITIONS

Data sheet status

Objective specification This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification This data sheet contains final product specifications.

Limiting values

Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and

operation of the device at these or at any other conditions above those given in the Characteristics sections of

this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

Philips Electronics N.V. 1998

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the

copyright owner.

The information presented in this document does not form part of any quotation or contract, it is believed to be

accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any

consequence of its use. Publication thereof does not convey nor imply any license under patent or other

industrial or intellectual property rights.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these

products can be reasonably expected to result in personal injury. Philips customers using or selling these products

for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting

from such improper use or sale.

April 1998 8 Rev 1.000

You might also like

- N-Channel Enhancement Mode Irfz44Ns Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz44Ns Trenchmos Transistor: General Description Quick Reference DataDaniel Orlando Carballo FernándezNo ratings yet

- N-Channel Enhancement Mode Irfz44N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz44N Trenchmos Transistor: General Description Quick Reference DataingucvNo ratings yet

- N-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataNixon MaldonadoNo ratings yet

- IRFZ24NDocument8 pagesIRFZ24NarcatusNo ratings yet

- Buk9635-100a 1Document7 pagesBuk9635-100a 1Raul OsoNo ratings yet

- BUK 9575 - Interruptor de PotênciaDocument8 pagesBUK 9575 - Interruptor de PotênciaTiago LeonhardtNo ratings yet

- Buk7514 55a - Buk7614 55aDocument9 pagesBuk7514 55a - Buk7614 55aHabacuc LopezNo ratings yet

- Buk7508 Buk7608-55a 1Document9 pagesBuk7508 Buk7608-55a 1Habacuc LopezNo ratings yet

- Trenchmos Transistor Buk9535-55A Logic Level Fet Buk9635-55ADocument9 pagesTrenchmos Transistor Buk9535-55A Logic Level Fet Buk9635-55AMotor CsillagNo ratings yet

- Buk555 60a PDFDocument7 pagesBuk555 60a PDFGiraldoCarpioRamosNo ratings yet

- PDF Philips 26610Document11 pagesPDF Philips 26610ecsa tallerNo ratings yet

- IRF540Document9 pagesIRF540paul mathewNo ratings yet

- N-Channel Trenchmos Transistor Irf530N: Features Symbol Quick Reference DataDocument7 pagesN-Channel Trenchmos Transistor Irf530N: Features Symbol Quick Reference DataLenin Cadillo GutierrezNo ratings yet

- Buk455 200a PDFDocument8 pagesBuk455 200a PDFCarl Conter OnderNo ratings yet

- Datasheet 6Document9 pagesDatasheet 6Ivanor Ipanaque CordovaNo ratings yet

- N-Channel Trenchmos Transistor Phx9Nq20T, Phf9Nq20T: Features Symbol Quick Reference DataDocument10 pagesN-Channel Trenchmos Transistor Phx9Nq20T, Phf9Nq20T: Features Symbol Quick Reference DatareparacionesdmaNo ratings yet

- N-Channel Trenchmos Transistor Psmn040-200W: Features Symbol Quick Reference DataDocument7 pagesN-Channel Trenchmos Transistor Psmn040-200W: Features Symbol Quick Reference DataRobert sibueaNo ratings yet

- Powermos Transistor Buk475-200A/B Isolated Version of Buk455-200A/BDocument7 pagesPowermos Transistor Buk475-200A/B Isolated Version of Buk455-200A/Bmaykel valdezNo ratings yet

- Powermos Transistor Irf730 Avalanche Energy Rated: Features Symbol Quick Reference DataDocument7 pagesPowermos Transistor Irf730 Avalanche Energy Rated: Features Symbol Quick Reference DataCarlos Morales AvilaNo ratings yet

- Powermos Transistors Irfp460 Avalanche Energy Rated: Features Symbol Quick Reference DataDocument7 pagesPowermos Transistors Irfp460 Avalanche Energy Rated: Features Symbol Quick Reference DataRio CandrapurwitaNo ratings yet

- Stp5Nc50 - Stp5Nc50Fp Stb5Nc50 - Stb5Nc50-1: N-Channel 500V - 1.3 - 5.5A To-220/Fp/D Pak/I Pak Powermesh Ii MosfetDocument12 pagesStp5Nc50 - Stp5Nc50Fp Stb5Nc50 - Stb5Nc50-1: N-Channel 500V - 1.3 - 5.5A To-220/Fp/D Pak/I Pak Powermesh Ii MosfetJavier55No ratings yet

- Stp80Pf55: P-Channel 55V - 0.016 - 80A To-220 Stripfet Ii Power MosfetDocument7 pagesStp80Pf55: P-Channel 55V - 0.016 - 80A To-220 Stripfet Ii Power MosfetRadoslav RadoslavovNo ratings yet

- Powermos Transistors Php6N60E, Phb6N60E Avalanche Energy RatedDocument9 pagesPowermos Transistors Php6N60E, Phb6N60E Avalanche Energy RatedEmmanuel ZambranoNo ratings yet

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectNo ratings yet

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectNo ratings yet

- Irf 540Document8 pagesIrf 540Tom TweedleNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharNo ratings yet

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFRubenNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharNo ratings yet

- 16N50Document6 pages16N50Fábio Vitor MartinsNo ratings yet

- STP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetDocument8 pagesSTP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetCarlos A AvilaNo ratings yet

- STP80NF75L STB80NF75L STB80NF75L-1: N-CHANNEL 75V - 0.008 - 80A TO-220/D Pak/I PAK Stripfet™ Ii Power MosfetDocument11 pagesSTP80NF75L STB80NF75L STB80NF75L-1: N-CHANNEL 75V - 0.008 - 80A TO-220/D Pak/I PAK Stripfet™ Ii Power MosfetRyn YahuFNo ratings yet

- 2NS04ZDocument6 pages2NS04ZNazım DallasNo ratings yet

- 9T16GH MOSFET CANAL N SMDDocument4 pages9T16GH MOSFET CANAL N SMDVictorManuelBernalBlancoNo ratings yet

- KIA KIA KIA: 1.descriptionDocument5 pagesKIA KIA KIA: 1.descriptionzakreaNo ratings yet

- BUK92150-55A: 1. DescriptionDocument13 pagesBUK92150-55A: 1. DescriptionrenzoNo ratings yet

- Bf245a bf245b bf245c - 2Document11 pagesBf245a bf245b bf245c - 2Antony VilcayauriNo ratings yet

- Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument5 pagesNiko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorJulio Rafael GamboaNo ratings yet

- Bf245a B CDocument11 pagesBf245a B CtemplpaNo ratings yet

- p5506hvg NikoDocument5 pagesp5506hvg Nikoاحسن طاہرNo ratings yet

- DatasheetDocument12 pagesDatasheetErwin Rolando EscobarNo ratings yet

- Data Sheet: N-Channel Enhancement Mode MOS TransistorDocument8 pagesData Sheet: N-Channel Enhancement Mode MOS TransistorArgenis VeraNo ratings yet

- 7A 650V N-Channel Enhancement Mode Power MOSFET: 7N65/F7N65/I7N65/E7N65/B7N65/D7N65Document11 pages7A 650V N-Channel Enhancement Mode Power MOSFET: 7N65/F7N65/I7N65/E7N65/B7N65/D7N65Sergio Daniel CaminoNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument6 pagesAdvanced Power Electronics Corp.: DescriptionEbrahemAlatfeNo ratings yet

- Datasheet 2Document4 pagesDatasheet 2Eligio VillalobosNo ratings yet

- Mosfet (70t03gh)Document4 pagesMosfet (70t03gh)Allan Souza SantanaNo ratings yet

- MOSFETDocument7 pagesMOSFETjoswil21No ratings yet

- 70L02GHDocument8 pages70L02GHJtzabalaNo ratings yet

- Important Notice: Kind RegardsDocument8 pagesImportant Notice: Kind Regardscarlosjamal95No ratings yet

- Advanced Power Electronics Corp.: AP70T03GH/JDocument4 pagesAdvanced Power Electronics Corp.: AP70T03GH/JVolodiyaNo ratings yet

- Advanced Power Electronics Corp.: AP70T03GH/JDocument4 pagesAdvanced Power Electronics Corp.: AP70T03GH/JkikinNo ratings yet

- 70T03GH AdvancedPowerElectronics PDFDocument4 pages70T03GH AdvancedPowerElectronics PDFAdriano Neoaver TavaresNo ratings yet

- STK0765BF: Switching Regulator Applications FeaturesDocument8 pagesSTK0765BF: Switching Regulator Applications FeaturesHumberto AguilarNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Syllabus - FLWKDocument3 pagesSyllabus - FLWKabhrajitsahaNo ratings yet

- ABC For Electronic BallastDocument22 pagesABC For Electronic BallastneorabbitNo ratings yet

- Cat 320D2Document22 pagesCat 320D2ricsnikNo ratings yet

- Modelling, Simulation and Performance Analysis of A Variable Frequency Drive in Speed Control of Induction MotorDocument7 pagesModelling, Simulation and Performance Analysis of A Variable Frequency Drive in Speed Control of Induction MotorAjfer IntekhabNo ratings yet

- Lab. Activity #1Document8 pagesLab. Activity #1Dahlia FernandezNo ratings yet

- IEEMA Basics of Dual Ratio Transformers PDFDocument3 pagesIEEMA Basics of Dual Ratio Transformers PDFKelly chatNo ratings yet

- ECE 1201 BJT TransistorsDocument77 pagesECE 1201 BJT TransistorsA.K.M.TOUHIDUR RAHMAN100% (1)

- 3SU11502BM603NA0 Datasheet enDocument3 pages3SU11502BM603NA0 Datasheet enkelvinNo ratings yet

- Ds LEIAN DCDU 12B SpecificationDocument9 pagesDs LEIAN DCDU 12B SpecificationDr.Ahmed GhareebNo ratings yet

- Series - Parallel Circuit NotesDocument4 pagesSeries - Parallel Circuit NotesAnonymous v5QjDW2eHxNo ratings yet

- CascadingDocument1 pageCascadingDenzo RyugaNo ratings yet

- N-Channel 30-V (D-S) MOSFET: Features Product SummaryDocument9 pagesN-Channel 30-V (D-S) MOSFET: Features Product SummaryMaikel Borges IglesiasNo ratings yet

- EC3353 QB 01 2MARKS - by LearnEngineering - inDocument18 pagesEC3353 QB 01 2MARKS - by LearnEngineering - insanthoshini7555No ratings yet

- Installation of PVC Insulated Heavy Duty CablesDocument1 pageInstallation of PVC Insulated Heavy Duty CablesYaserNo ratings yet

- Class Notes For DIodesDocument2 pagesClass Notes For DIodesCedric MontianoNo ratings yet

- Pad-Mount & Substation Transformers: Catalog InformationDocument59 pagesPad-Mount & Substation Transformers: Catalog InformationHassan SaeedNo ratings yet

- Otn, Otr, Otf TransformersDocument6 pagesOtn, Otr, Otf TransformersDott PalmitoNo ratings yet

- Bitx Version 3 Linear Amplifier AssemblyDocument14 pagesBitx Version 3 Linear Amplifier Assemblyapi-26282181100% (1)

- DC Shunt Motor Exp7 PDFDocument10 pagesDC Shunt Motor Exp7 PDFGopinath B L NaiduNo ratings yet

- Imesa Minifluor Copertina - en WebDocument52 pagesImesa Minifluor Copertina - en WebAlaa ZoraNo ratings yet

- Start Here: Assembly InstructionsDocument2 pagesStart Here: Assembly InstructionsAfzal ImamNo ratings yet

- Determining The Circuit Breaker Size For Three-Phase InvertersDocument3 pagesDetermining The Circuit Breaker Size For Three-Phase InvertersBill BreakerNo ratings yet

- Type of Earthing SystemDocument6 pagesType of Earthing SystemMokr AchourNo ratings yet

- c945 Data SheetDocument2 pagesc945 Data SheetAdnan AliNo ratings yet

- Det50063 PW1 Static Converter 1 QuadrantDocument7 pagesDet50063 PW1 Static Converter 1 QuadrantFara FaraNo ratings yet

- R8017G MBCHDocument52 pagesR8017G MBCHmjbriceno@gmail.com100% (1)

- Clipper CircuitsDocument9 pagesClipper CircuitsMitali SinghNo ratings yet

- For Synchronous GeneratorDocument34 pagesFor Synchronous GeneratorNIKESH PATELNo ratings yet

- H782 Series Hermetically Sealed Electromechanical Relay Selection GuideDocument4 pagesH782 Series Hermetically Sealed Electromechanical Relay Selection GuideArafath HashimNo ratings yet

- SS42R Series: Active High/Active Low Complementary Output Hall-Effect LatchDocument4 pagesSS42R Series: Active High/Active Low Complementary Output Hall-Effect Latchfernandoireta994No ratings yet