Professional Documents

Culture Documents

CPE241 Digital Logic Design

CPE241 Digital Logic Design

Uploaded by

Souban JavedCopyright:

Available Formats

You might also like

- How To Write Your Engineering Experience Record - Professional Engineers ExaDocument3 pagesHow To Write Your Engineering Experience Record - Professional Engineers ExaTherese Araymond67% (3)

- COMSATS University Islamabad: Course Description FileDocument8 pagesCOMSATS University Islamabad: Course Description FileSouban JavedNo ratings yet

- SATIP D 001 01 (Revision 4)Document3 pagesSATIP D 001 01 (Revision 4)Anonymous 4e7GNjzGW100% (1)

- CPE415 Digital Image ProcessingDocument9 pagesCPE415 Digital Image ProcessingSouban JavedNo ratings yet

- CPE324 Digital Signal ProcessingDocument9 pagesCPE324 Digital Signal ProcessingSouban JavedNo ratings yet

- CPE314 Data Communication and Computer NetworksDocument9 pagesCPE314 Data Communication and Computer NetworksSouban JavedNo ratings yet

- CSC141 Introduction To Computer ProgrammingDocument8 pagesCSC141 Introduction To Computer ProgrammingSouban JavedNo ratings yet

- EEE231 Electronics IDocument9 pagesEEE231 Electronics IMotivational SpeakersNo ratings yet

- CPE446 Real Time Embedded SystemsDocument10 pagesCPE446 Real Time Embedded SystemsSouban JavedNo ratings yet

- CDF-CSC322 Operating SystemsDocument9 pagesCDF-CSC322 Operating SystemsHassam HafeezNo ratings yet

- CPE251 Probability Methods in EngineeringDocument7 pagesCPE251 Probability Methods in EngineeringSouban JavedNo ratings yet

- CDF CPE222 Electric Circuits Analysis IIDocument8 pagesCDF CPE222 Electric Circuits Analysis IIASAD AHMADNo ratings yet

- CPE440 Computer ArchitectureDocument7 pagesCPE440 Computer ArchitectureSouban JavedNo ratings yet

- Digital System Design: Course Code PrerequisitesDocument6 pagesDigital System Design: Course Code PrerequisitesAamir AltafNo ratings yet

- CPE121 Electric Circuits Analysis IDocument9 pagesCPE121 Electric Circuits Analysis IMuhammad UmarNo ratings yet

- CPE345 Embedded Systems WorkshopDocument7 pagesCPE345 Embedded Systems WorkshopSouban JavedNo ratings yet

- CSC103 Outline 1st 2021-2022Document4 pagesCSC103 Outline 1st 2021-2022A QanasNo ratings yet

- EEE440 Computer ArchitectureDocument7 pagesEEE440 Computer ArchitecturekirpkNo ratings yet

- MENG 313 C.Specification - ByLaw 2007Document6 pagesMENG 313 C.Specification - ByLaw 2007Eman AhmedNo ratings yet

- DR - KB - OFC OutlineDocument6 pagesDR - KB - OFC OutlineEngr SayedNo ratings yet

- EEE362 Microwave EngineeringDocument9 pagesEEE362 Microwave EngineeringMuhammad UmarNo ratings yet

- CDF DLD TheoryDocument4 pagesCDF DLD TheoryMuhammad Fayyaz Khan AP Electronics ABTNo ratings yet

- EEE4134 CO Spring2021Document4 pagesEEE4134 CO Spring2021Abdullah Al SakibNo ratings yet

- CS-4th SemcourseinfoDocument57 pagesCS-4th SemcourseinfoTausifAliNo ratings yet

- ELE 3212 - SS LabDocument49 pagesELE 3212 - SS LabsheetalprachandraNo ratings yet

- B.sc-computer-Science 2017 2018 SyllabusDocument70 pagesB.sc-computer-Science 2017 2018 SyllabusDHIVYA SNo ratings yet

- Elec Lab OutlineDocument3 pagesElec Lab OutlineMushfiq Us SalehinNo ratings yet

- BMCG 2513 - Teaching Plan Sem - 2 2016 2017 - BasriDocument11 pagesBMCG 2513 - Teaching Plan Sem - 2 2016 2017 - BasriW Mohd Zailimi AbdullahNo ratings yet

- Department of Electronic Engineering Bachelors in Electronic EngineeringDocument3 pagesDepartment of Electronic Engineering Bachelors in Electronic EngineeringHani HasanNo ratings yet

- Course Outline - FEADocument2 pagesCourse Outline - FEAFahad IqbalNo ratings yet

- Control Engineering - Units of Study... - Swinburne University of Technology - Melbourne, AustraliaDocument4 pagesControl Engineering - Units of Study... - Swinburne University of Technology - Melbourne, AustraliaFaisal MohmandNo ratings yet

- Cmpe224 CS Fall2010-2011Document3 pagesCmpe224 CS Fall2010-2011MICHAEL K. E. DonkorNo ratings yet

- Introduction To Structural Dynamics and Earthquake EngineeringDocument2 pagesIntroduction To Structural Dynamics and Earthquake EngineeringfefahimNo ratings yet

- Teaching Plan Software EngineeringDocument11 pagesTeaching Plan Software EngineeringHabeeb E SadeedNo ratings yet

- Course Information Sem 12134Document9 pagesCourse Information Sem 12134YooganNo ratings yet

- School of Engineering and Computer Science Department of Electrical & Electronic EngineeringDocument10 pagesSchool of Engineering and Computer Science Department of Electrical & Electronic EngineeringMD. Akif RahmanNo ratings yet

- Eee404 - Eee302 - Lab Sheet GubDocument68 pagesEee404 - Eee302 - Lab Sheet Gubএস এইচ সাকিবNo ratings yet

- Special Topics in ElectronicsDocument6 pagesSpecial Topics in Electronicsramkumar rajaNo ratings yet

- Dwarkadas J. Sanghvi College of EngineeringDocument22 pagesDwarkadas J. Sanghvi College of EngineeringMjNo ratings yet

- EEE 2000 Course SyllabusDocument3 pagesEEE 2000 Course SyllabusAl AminNo ratings yet

- SyllipusDocument4 pagesSyllipusAmeen AlzeidiNo ratings yet

- Chapter 1 - IntroductionDocument28 pagesChapter 1 - Introductioningxing23No ratings yet

- 00 Syllabus For Honors Course Please Dont ShareDocument16 pages00 Syllabus For Honors Course Please Dont ShareAdityaNo ratings yet

- University of Bahrain: MATHS 101 Course SyllabusDocument8 pagesUniversity of Bahrain: MATHS 101 Course SyllabusKomail AlmajjedNo ratings yet

- Course Assesmnet SheetDocument3 pagesCourse Assesmnet SheetMohsin QaziNo ratings yet

- Be Comp Engg Sem-Viii r2019Document56 pagesBe Comp Engg Sem-Viii r2019Sahil KNo ratings yet

- Üsküdar University Faculty of Engineering and Natural Sciences Department of Software EngineeringDocument71 pagesÜsküdar University Faculty of Engineering and Natural Sciences Department of Software EngineeringSomeoneNo ratings yet

- RS579 - Computer Engineering Curriculum 2073 PDFDocument80 pagesRS579 - Computer Engineering Curriculum 2073 PDFreema yadav75% (8)

- CLP - Course Learning Plan SAB 24603 Applied Digital Electronics January 2019Document6 pagesCLP - Course Learning Plan SAB 24603 Applied Digital Electronics January 2019MOHAMAD FADZLI BIN HANIFF 14668No ratings yet

- Elec 578 - Integrated Circuit DesignDocument4 pagesElec 578 - Integrated Circuit DesignVishnu 3333No ratings yet

- Introduction To Data Science Lab ManualDocument76 pagesIntroduction To Data Science Lab Manualpavan kalyanNo ratings yet

- Mechatronics Digital Material RMK Unit I PDFDocument57 pagesMechatronics Digital Material RMK Unit I PDFRajmchzNo ratings yet

- SL - DMA 2122 - Asas Elektrik Dan ElektronikDocument7 pagesSL - DMA 2122 - Asas Elektrik Dan ElektronikfarizanNo ratings yet

- East West University: Department of Computer Science and Engineering Course Outline Spring 2019 SemesterDocument6 pagesEast West University: Department of Computer Science and Engineering Course Outline Spring 2019 Semesterthe rexaNo ratings yet

- Mca-R20-Course Structure-Syllabus (16122021)Document78 pagesMca-R20-Course Structure-Syllabus (16122021)SIXTIE NYNNo ratings yet

- Syllabus Maths111 - 2023-2024 - Sem. II - UpdatedDocument7 pagesSyllabus Maths111 - 2023-2024 - Sem. II - Updatedkingzeus8976No ratings yet

- Bca Scheme and SyllabusDocument76 pagesBca Scheme and SyllabusAbcd GoogleNo ratings yet

- 4EC4-21 ADC Lab AS-16aDocument93 pages4EC4-21 ADC Lab AS-16aSu KoshNo ratings yet

- 1 & 2 Sem Scheme of StudiesDocument2 pages1 & 2 Sem Scheme of StudiesDayanand Gowda KrNo ratings yet

- Course Assesmnet SheetDocument3 pagesCourse Assesmnet SheetMaheen ArshadNo ratings yet

- Introduction to Dynamic Programming: International Series in Modern Applied Mathematics and Computer Science, Volume 1From EverandIntroduction to Dynamic Programming: International Series in Modern Applied Mathematics and Computer Science, Volume 1No ratings yet

- CSC211 Data Structures and AlgorithmsDocument7 pagesCSC211 Data Structures and AlgorithmsSouban JavedNo ratings yet

- Mutee Abdullah FA20-BCE-068 BCE-3B: Implementation of Circular Doubly Linked Lists in C LanguageDocument7 pagesMutee Abdullah FA20-BCE-068 BCE-3B: Implementation of Circular Doubly Linked Lists in C LanguageSouban JavedNo ratings yet

- Electric Machines EEE371 Lab Report # 6: Osama AfzalDocument11 pagesElectric Machines EEE371 Lab Report # 6: Osama AfzalSouban JavedNo ratings yet

- Figure 1: Queue Abstract Data TypeDocument3 pagesFigure 1: Queue Abstract Data TypeSouban JavedNo ratings yet

- CSC141 Introduction To Computer ProgrammingDocument8 pagesCSC141 Introduction To Computer ProgrammingSouban JavedNo ratings yet

- DSA Lab5 Complte PDFDocument4 pagesDSA Lab5 Complte PDFSouban JavedNo ratings yet

- CPE490 Final Year ProjectDocument5 pagesCPE490 Final Year ProjectSouban JavedNo ratings yet

- Curriculum OverviewDocument6 pagesCurriculum OverviewSouban JavedNo ratings yet

- CSC112 Algorithms and Data StructuresDocument8 pagesCSC112 Algorithms and Data StructuresSouban JavedNo ratings yet

- CPE446 Real Time Embedded SystemsDocument10 pagesCPE446 Real Time Embedded SystemsSouban JavedNo ratings yet

- CPE415 Digital Image ProcessingDocument9 pagesCPE415 Digital Image ProcessingSouban JavedNo ratings yet

- CPE314 Data Communication and Computer NetworksDocument9 pagesCPE314 Data Communication and Computer NetworksSouban JavedNo ratings yet

- CPE251 Probability Methods in EngineeringDocument7 pagesCPE251 Probability Methods in EngineeringSouban JavedNo ratings yet

- Terminal: Introduction To Computer Programming CSC-14Document7 pagesTerminal: Introduction To Computer Programming CSC-14Souban JavedNo ratings yet

- MGT462 Project Planning and ManagementDocument9 pagesMGT462 Project Planning and ManagementSouban JavedNo ratings yet

- CPE440 Computer ArchitectureDocument7 pagesCPE440 Computer ArchitectureSouban JavedNo ratings yet

- CPE324 Digital Signal ProcessingDocument9 pagesCPE324 Digital Signal ProcessingSouban JavedNo ratings yet

- CPE345 Embedded Systems WorkshopDocument7 pagesCPE345 Embedded Systems WorkshopSouban JavedNo ratings yet

- Electronics 2 Lab Report #10 Submitted To: DR Khurram Ali Submitted By: Wahaj Rahim Fa18-Bee-160CDocument11 pagesElectronics 2 Lab Report #10 Submitted To: DR Khurram Ali Submitted By: Wahaj Rahim Fa18-Bee-160CSouban JavedNo ratings yet

- Screencapture Chegg Homework Help Questions and Answers Show Work Part B Hint Engineering Electromagnetics Third Edition Nathan Ida q38395171 2022 07 04 23 - 51 - 25Document2 pagesScreencapture Chegg Homework Help Questions and Answers Show Work Part B Hint Engineering Electromagnetics Third Edition Nathan Ida q38395171 2022 07 04 23 - 51 - 25Souban JavedNo ratings yet

- Christian Thibaudeau Men Transformation Plan Updated PDFDocument117 pagesChristian Thibaudeau Men Transformation Plan Updated PDFSouban Javed100% (5)

- Lab Report: 09Document10 pagesLab Report: 09Souban JavedNo ratings yet

- SP20 - Terminal - Dr. Adnan IftikharDocument2 pagesSP20 - Terminal - Dr. Adnan IftikharSouban JavedNo ratings yet

- Lab#4 For and Nested For Loops: A) Yes Yes No No Yes Yes No No No No No No No No No No Yes Yes Yes No No No No NoDocument7 pagesLab#4 For and Nested For Loops: A) Yes Yes No No Yes Yes No No No No No No No No No No Yes Yes Yes No No No No NoSouban JavedNo ratings yet

- Lab 1 To 10 DLDDocument43 pagesLab 1 To 10 DLDSouban JavedNo ratings yet

- Sessional 2Document3 pagesSessional 2Souban JavedNo ratings yet

- (30 Marks) : Lab Sessional 2: Course: ICP (CSC141) Class: BEE 2C - SP 2021Document3 pages(30 Marks) : Lab Sessional 2: Course: ICP (CSC141) Class: BEE 2C - SP 2021Souban JavedNo ratings yet

- Lab 06: Wheatstone Bridge, Delta To Wye and Wye To Delta TransformationDocument7 pagesLab 06: Wheatstone Bridge, Delta To Wye and Wye To Delta TransformationSouban JavedNo ratings yet

- Lab 6 - 10 DLDDocument16 pagesLab 6 - 10 DLDSouban JavedNo ratings yet

- Fa20-Bee-137 Icp Lab6Document8 pagesFa20-Bee-137 Icp Lab6Souban JavedNo ratings yet

- Ansi B16 - 5Document157 pagesAnsi B16 - 5Felipe SandovalNo ratings yet

- 10 Highest Paying PHD DegreesDocument8 pages10 Highest Paying PHD DegreesSteven OsharenaNo ratings yet

- Introduction To Structural EngineeringDocument45 pagesIntroduction To Structural EngineeringAizha JhayNo ratings yet

- Design Patterns SW Quality - English VersionDocument18 pagesDesign Patterns SW Quality - English VersionAdemir Constantino100% (1)

- Society InteriorsDocument208 pagesSociety InteriorsliabocNo ratings yet

- Asme Section II A-2 Sa-455 Sa-455mDocument4 pagesAsme Section II A-2 Sa-455 Sa-455mAnonymous GhPzn1xNo ratings yet

- Vision MissionDocument2 pagesVision MissionmanmohansinghloteyNo ratings yet

- Hoek-Brown Parameters For Predicting The Depth of Brittle Failure Around Tunnels DestacadoDocument16 pagesHoek-Brown Parameters For Predicting The Depth of Brittle Failure Around Tunnels DestacadoPamela Paz Donoso MatusNo ratings yet

- Advantages of PrestressedDocument3 pagesAdvantages of PrestressedLarete PaoloNo ratings yet

- Wireless Communication Unit I Anna UniversityDocument36 pagesWireless Communication Unit I Anna UniversityMr.A.Sriram Asst. ProfNo ratings yet

- Mechanical IntegrityDocument9 pagesMechanical Integritysenor pinkNo ratings yet

- OBE Syllabus - ME 424 - Fluid MachineryDocument3 pagesOBE Syllabus - ME 424 - Fluid MachineryJerico LlovidoNo ratings yet

- Lead Chart 1Document9 pagesLead Chart 1Hoque joynulNo ratings yet

- John Carlos M. Critica Me, RMP, Msiem: ExperienceDocument2 pagesJohn Carlos M. Critica Me, RMP, Msiem: ExperienceCarlos_CriticaNo ratings yet

- 04 SoftwareEngineeringNotCSDocument7 pages04 SoftwareEngineeringNotCSPankaj SoniNo ratings yet

- University of Engineering and Technology Peshawar: B.SC Engineering Degree Programme Academic Session 2019-20Document5 pagesUniversity of Engineering and Technology Peshawar: B.SC Engineering Degree Programme Academic Session 2019-20SarDar AzhiiNo ratings yet

- Post-Tensioning Software Post Tensioning Software ADAPT-Builder / Floor ProDocument18 pagesPost-Tensioning Software Post Tensioning Software ADAPT-Builder / Floor ProAnderson MuñetonNo ratings yet

- Oprema Ravne Pneumatic Tools PresentationDocument3 pagesOprema Ravne Pneumatic Tools PresentationYeimy Estupiñan Fredy VegaNo ratings yet

- 2022 GKS-UIC Application Guidelines (English)Document20 pages2022 GKS-UIC Application Guidelines (English)aprielNo ratings yet

- CB Vs ContactorDocument2 pagesCB Vs ContactorAmit Kumar SinghNo ratings yet

- Concrete Technology: by Dr. R. P. RethaliyaDocument4 pagesConcrete Technology: by Dr. R. P. RethaliyaAkhilesh Kumar67% (3)

- Eligibility Criteria: Bachelor of Computer Applications (BCA) Is A Four-YearDocument3 pagesEligibility Criteria: Bachelor of Computer Applications (BCA) Is A Four-YearTanmoy MitraNo ratings yet

- CH1 TeSys Motor Starters - Open VersionDocument216 pagesCH1 TeSys Motor Starters - Open VersionevansparrowNo ratings yet

- AFT Arrow 9 Quickstart MetricDocument126 pagesAFT Arrow 9 Quickstart MetricUdaya kumar SubramaniNo ratings yet

- Developments in Equipment and Standards For Testing Porosity in CoatingsDocument11 pagesDevelopments in Equipment and Standards For Testing Porosity in Coatingsmfazl33No ratings yet

- Wa0052Document3 pagesWa0052Frank HardingNo ratings yet

- C A 2018 ET HP DesigninfoDocument9 pagesC A 2018 ET HP DesigninfoJonathan DouglasNo ratings yet

CPE241 Digital Logic Design

CPE241 Digital Logic Design

Uploaded by

Souban JavedOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CPE241 Digital Logic Design

CPE241 Digital Logic Design

Uploaded by

Souban JavedCopyright:

Available Formats

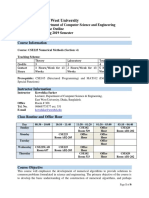

CPE241

Digital Logic Design Spring 2022

COMSATS University Islamabad

COURSE DESCRIPTION FILE

CPE241 Digital Logic Design

DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

COMSATS University Islamabad Page 1

CPE241 Digital Logic Design Spring 2022

COMSATS University Islamabad

COURSE DESCRIPTION FILE

CPE241 Digital Logic Design

DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

Prepared By: Checked By: Approved By:

‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐ ‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐ ‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐‐

COMSATS University Islamabad Page 2

CPE241 Digital Logic Design Spring 2022

Digital Logic Design

Course code:

CPE241 (3+1)

Prerequisites:

None

Co requisites:

None

Course Catalog Description:

Introduction to Digital Computer and Systems, Number Systems, Binary Arithmetic, Boolean Algebra,

Algebraic Manipulation, Canonical and Standard Form & Conversions, Logical Operations and Gates,

Simplification of Functions, Karnaugh Map Methods, Two Level Implementations, Don’t Care Conditions,

Prime Implicants, Combinational Logic Design, Arithmetic Operations and Circuits, Analysis Procedures,

Multilevel NAND/NOR Circuits, Decoders, Encoders, Multiplexers, Demultiplexers, Memory Types, Read

Only Memory, Random Access Memory, Programmable Logic Array (PLA), Sequential Logic, Flip‐Flops,

Clocked Sequential Circuits, State Machine Concept, Design of Sequential Circuits using State Machines,

Counters and their design, Synchronous Counters, Asynchronous Counters, Shift Registers.

Textbooks:

1. M. Morris Mano and Michael D. Ciletti, Digital Design: With an Introduction to Verilog HDL, Fifth

Edition, Prentice Hall, 2012.

2. Stephen Brown and Zvonko Vranesic, Fundamentals of Digital Logic with Verilog Design, Third

Edition, McGraw‐Hill, 2013.

Reference Books:

1. Floyd and Jain, Digital Fundamentals, Tenth Edition, Prentice Hall, 2009.

2. Samir Palnitkar, Verilog HDL, Second Edition, Prentice Hall, 2003.

3. Digital Design with RTL Design, VHDL, and Verilog by Frank Vahid, Second Edition, John Wiley, 2011.

Course Learning Objectives:

This course aims to familiarize the students with the basic concepts in digital logic design. Two basic

categories are emphasized: combinational and sequential logic circuits. The teaching material helps the

students to solve many practical hardware problems and to be able to understand the principles of

digital hardware design.

Course Learning Outcomes:

After successfully completing the course, the students will be able to:

1. Understand number systems, codes and Boolean algebra for the analysis and design of digital logic

circuits. (C2‐PLO1)

COMSATS University Islamabad Page 3

CPE241 Digital Logic Design Spring 2022

2. Demonstrate an understanding of how a digital function behaves, its various representations such as

canonical and standard forms and gate level minimization techniques. (C3‐PLO1)

3. Analyze combinational and sequential logic circuits using traditional techniques, such as K‐maps and

state tables. (C4‐PLO2)

4. Design and implement combinational and synchronous sequential circuits. (C5‐PLO3)

5. Design and conduct experiments and analyze and interpret the experimental data to derive

valid conclusions. (C6‐PLO4)

6. Present and analyze data with effective report writing skills. (A2‐PLO10)

Course Schedule:

3 credit hours/week

One laboratory session/week (3 hours/session)

Topics Covered:

1. Fundamental digital concepts, Boolean algebra (1 week)

2. Number Systems and codes, synthesis using logic gates (1week)

3. Fundamentals of Verilog, NMOS/CMOS implementation technologies (1 week)

4. Optimized Implementation of logic functions using K‐Maps (1 week)

5. Combinational building blocks (1.5 weeks)

6. Arithmetic with Verilog (1 week)

7. Verilog for combinational logic (1 week)

8. Sequential circuits and flip‐Flops (1 week)

9. Analysis of sequential circuits (1 week)

10. Sequential circuit design and state machines (1.5 weeks)

11. Synthesis using D‐flip flops, J/K and T flip‐flops (1 week)

12. Registers and Counters (2 weeks)

13. Introduction to RAM, ROM, PLAs, PALs and FPGAs (1 week)

14. Assessment Plan:

Theory Quizzes (4) 15%

Homework assignments 10%

Mid‐term exam (in class, 60‐80 minutes) 25%

Terminal exam (3 hours) 50%

Total (theory) 100%

Lab work Lab reports (12) 25%

Lab Mid‐term exam 25%

Lab project and terminal exam 50%

Total (lab) 100%

Final marks Theory marks * 0.75 + Lab marks * 0.25

COMSATS University Islamabad Page 4

CPE241 Digital Logic Design Spring 2022

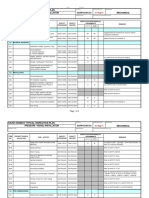

Learning Outcomes Assessment Plan (Tentative):

Sr. # Course Learning Outcomes Assessment

1. Quiz 1

2. Quiz 2

3. Quiz 3

4. Quiz 4

5. Assignment 1

6. Assignment 2

7. Assignment 3

8. Assignment 4

9. Mid‐term Exam

10. Terminal Exam

Table 1: Assessment Plan for Course Learning Outcomes

Laboratory Experiences:

There is a Laboratory component in all 3+1 credit courses taught at the department. Lab work consists

of a minimum of 12 experiments and related assignments, which constitute 25% of the overall course‐

grade. The laboratory experiments include implementation of combinational and sequential circuits

taught in class using software tools such as Modelsim and Xilinx ISE as well as 7400 series ICs.

Laboratory Resources:

The relevant laboratory is equipped with workbenches and computers to facilitate the experiments

outlined in the lab handbook(s) that are periodically updated. A current list of the 12 lab experiments

performed in this course is provided as Annexure‐II. The list of software and equipment available is also

posted in all labs and is managed by staff dedicated for this purpose.

Computer Resources:

For the purposes of this course, the digital design and simulation software such as Modelsim and Xilinx

ISE are installed in the laboratory that is used for implementation of digital circuits.

COMSATS University Islamabad Page 5

CPE241 Digital Logic Design Spring 2022

Mapping Course Learning Outcomes (CLOs) to Program Learning Outcomes (PLOs):

PLO 1 Engineering Knowledge: An ability to apply knowledge of mathematics, science,

engineering fundamentals and an engineering specialization to the solution of complex

engineering problems.

PLO 2 Problem Analysis: An ability to identify, formulate, research literature, and analyze

complex engineering problems reaching substantiated conclusions using first principles

of mathematics, natural sciences and engineering sciences.

PLO 3 Design/Development of Solutions: An ability to design solutions for complex

engineering problems and design systems, components or processes that meet

specified needs with appropriate consideration for public health and safety, cultural,

societal, and environmental considerations.

PLO 4 Investigation: An ability to investigate complex engineering problems in a methodical

way including literature survey, design and conduct of experiments, analysis and

interpretation of experimental data, and synthesis of information to derive valid

conclusions.

PLO 5 Modern Tool Usage: An ability to create, select and apply appropriate techniques,

resources, and modern engineering and IT tools, including prediction and modeling, to

complex engineering activities, with an understanding of the limitations.

PLO 6 The Engineer and Society: An ability to apply reasoning informed by contextual

knowledge to assess societal, health, safety, legal and cultural issues and the

consequent responsibilities relevant to professional engineering practice and solution

to complex engineering problems.

PLO 7 Environment and Sustainability: An ability to understand the impact of professional

engineering solutions in societal and environmental contexts and demonstrate

knowledge of and need for sustainable development.

PLO 8 Ethics: Apply ethical principles and commit to professional ethics and responsibilities

and norms of engineering practice.

PLO 9 Individual and Team Work: An ability to work effectively, as an individual or in a team,

on multifaceted and /or multidisciplinary settings.

PLO 10 Communication: An ability to communicate effectively, orally as well as in writing, on

complex engineering activities with the engineering community and with society at

large, such as being able to comprehend and write effective reports and design

documentation, make effective presentations, and give and receive clear instructions.

PLO 11 Project Management: An ability to demonstrate management skills and apply

engineering principles to one’s own work, as a member and/or leader in a team, to

manage projects in a multidisciplinary environment.

PLO 12 Lifelong Learning: An ability to recognize importance of, and pursue lifelong learning in

the broader context of innovation and technological developments.

COMSATS University Islamabad Page 6

CPE241 Digital Logic Design Spring 2022

PLOs

PLO10

PLO11

PL012

PLO 9

PLO1

PLO2

PLO3

PLO4

PLO5

PLO6

PLO7

PLO8

CLOs

CLO1 C2

CLO2 C3

CLO3 C4

CLO4 C5

CLO5 C6

CLO6 A2

Table 2: Mapping CLOs to PLOs

PLO Coverage Explanation:

PLO 1: Engineering Knowledge

The homework, exams, and laboratory experiments require direct application of mathematics, scientific,

and engineering knowledge to successfully complete the course. This includes the function minimization

using Boolean algebra, K‐Maps and state tables. (High relevance to course)

PLO 2: Problem Analysis

The final design project is given as a set of specifications that the students' design must meet. Therefore,

they must identify the key limiting issues, formulate a solution strategy, research and test their

approach, and finally prototype and test the design to prove that it works. (High relevance to course)

PLO 3: Design/Development of Solutions

Through design and implementation of combinational and synchronous sequential circuits the students

enhance their design and development ability. (High relevance to course)

PLO4 – Investigation:

The ability to design and conduct experiments, analyse/interpret results and deduce informed

conclusions is developed in the students through multiple open‐ended labs.

PLO 10: Communication

The course project to be done in teams imparts various written and oral communication skills in project

reports and project presentations. It also develops the ability to function in teams as well as honing on

time management skills. As an experiment a cross‐departmental team can be established to work on a

larger project that requires HW and SW skills. (Low relevance to course)

PLO 5 ‐ 9, 11 and 12 are not covered and checked in the course directly. However certain aspects are

covered directly or indirectly. For example project management skill is developed during planning of

different stages of the design projects. (Low relevance to course)

COMSATS University Islamabad Page 7

CPE241 Digital Logic Design Spring 2022

ANNEXURE‐I

Tentative Lecture Breakdown (30 Lectures):

No. of

Topics

Lectures

Introduction to Digital Systems, binary numbers, and Number base conversions, Binary

arithmetic operations, Complements of numbers, and subtraction with compliments, 3

Binary Logic, Theorems and Postulates of Boolean Algebra, Operator Precedence

Digital Logic Gates, Logic Levels, Boolean functions, (NAND‐NOR Implementation),

Algebraic Manipulation, Function Complement, Canonical and Standard Forms, Signed 3

Binary Numbers

K‐Maps, Prime Implicants, Essential Prime Implicants, Product of Sum Simplification and

2

Don’t care Conditions

Combinational Logic: Analysis Procedure and Design Procedure, Binary Adder/Subtractor,

BCD Adder, Binary Multiplier, Magnitude Comparator and Decoders, Encoders, Parity 7

Encoders, Mux, Boolean Function Implementation using MUX

Sequential Circuits, SR Latch (NAND/NOR), D Latch, Types and characteristics of Flip Flops

(D, J‐K, T), Analysis of clocked Sequential circuits (State Equations, State Table, State 4

Diagram)

Mealy and Moore models of Finite State Machines, State reductions and State

Assignments, Design Procedure of Sequential Circuits, Synthesis using D‐F/F (Sequence

5

Detector Non‐Overlapping), Excitation Tables, Pattern/Sequence Detector (Overlapping),

Synthesis using J/K, T F/F

Registers, Register with Parallel Load, Shift Registers, Universal Shift Register 2

Binary Ripple Counter, Synchronous Counter (Binary Counter), Up/Down Binary Counter 2

Introduction to Memory, RAM, ROM, PLDs, PALs and FPGAs 2

COMSATS University Islamabad Page 8

CPE241 Digital Logic Design Spring 2022

ANNEXURE‐II

List of Experiments:

Lab No. Details

1 Introduction to Basic Logic Gate ICs on Digital Logic Trainer and Proteus Simulation

2 Boolean Function Implementation using Universal Gates

3 Introduction to Verilog and Simulation using XILINX ISE

4 Design and Implementation of Boolean Functions By Standard Forms Using ICs/Verilog

5 Logic Minimization of Complex Functions using Automated Tools

6 XILINX ISE Design Flow with FPGA

7 Design and Implementation of an 𝑛 𝑏𝑖𝑡 Adder/Subtractor on FPGA

8 Design and Implementation of an 𝑛 𝑏𝑖𝑡 Multiplier on FPGA

9 Design and Implementation of Binary to BCD to 7‐Segment Decoder on FPGA

10 Design and Implementation of a Sequence Detector using Mealy/Moore Machine

11 Implementation of a BCD Counter with Control Inputs on FPGA (Open Ended Lab)

12 Implementation of a Special Shift Register on FPGA (Open Ended Lab)

13‐14 Lab Project / Viva

Version Applicable From

Version 1 Fall 2016

Version 2 Spring 2017

Version 3 Fall 2017

Version 4 Fall 2018

Version 5 Fall 2019

Version 6 Fall 2021

COMSATS University Islamabad Page 9

You might also like

- How To Write Your Engineering Experience Record - Professional Engineers ExaDocument3 pagesHow To Write Your Engineering Experience Record - Professional Engineers ExaTherese Araymond67% (3)

- COMSATS University Islamabad: Course Description FileDocument8 pagesCOMSATS University Islamabad: Course Description FileSouban JavedNo ratings yet

- SATIP D 001 01 (Revision 4)Document3 pagesSATIP D 001 01 (Revision 4)Anonymous 4e7GNjzGW100% (1)

- CPE415 Digital Image ProcessingDocument9 pagesCPE415 Digital Image ProcessingSouban JavedNo ratings yet

- CPE324 Digital Signal ProcessingDocument9 pagesCPE324 Digital Signal ProcessingSouban JavedNo ratings yet

- CPE314 Data Communication and Computer NetworksDocument9 pagesCPE314 Data Communication and Computer NetworksSouban JavedNo ratings yet

- CSC141 Introduction To Computer ProgrammingDocument8 pagesCSC141 Introduction To Computer ProgrammingSouban JavedNo ratings yet

- EEE231 Electronics IDocument9 pagesEEE231 Electronics IMotivational SpeakersNo ratings yet

- CPE446 Real Time Embedded SystemsDocument10 pagesCPE446 Real Time Embedded SystemsSouban JavedNo ratings yet

- CDF-CSC322 Operating SystemsDocument9 pagesCDF-CSC322 Operating SystemsHassam HafeezNo ratings yet

- CPE251 Probability Methods in EngineeringDocument7 pagesCPE251 Probability Methods in EngineeringSouban JavedNo ratings yet

- CDF CPE222 Electric Circuits Analysis IIDocument8 pagesCDF CPE222 Electric Circuits Analysis IIASAD AHMADNo ratings yet

- CPE440 Computer ArchitectureDocument7 pagesCPE440 Computer ArchitectureSouban JavedNo ratings yet

- Digital System Design: Course Code PrerequisitesDocument6 pagesDigital System Design: Course Code PrerequisitesAamir AltafNo ratings yet

- CPE121 Electric Circuits Analysis IDocument9 pagesCPE121 Electric Circuits Analysis IMuhammad UmarNo ratings yet

- CPE345 Embedded Systems WorkshopDocument7 pagesCPE345 Embedded Systems WorkshopSouban JavedNo ratings yet

- CSC103 Outline 1st 2021-2022Document4 pagesCSC103 Outline 1st 2021-2022A QanasNo ratings yet

- EEE440 Computer ArchitectureDocument7 pagesEEE440 Computer ArchitecturekirpkNo ratings yet

- MENG 313 C.Specification - ByLaw 2007Document6 pagesMENG 313 C.Specification - ByLaw 2007Eman AhmedNo ratings yet

- DR - KB - OFC OutlineDocument6 pagesDR - KB - OFC OutlineEngr SayedNo ratings yet

- EEE362 Microwave EngineeringDocument9 pagesEEE362 Microwave EngineeringMuhammad UmarNo ratings yet

- CDF DLD TheoryDocument4 pagesCDF DLD TheoryMuhammad Fayyaz Khan AP Electronics ABTNo ratings yet

- EEE4134 CO Spring2021Document4 pagesEEE4134 CO Spring2021Abdullah Al SakibNo ratings yet

- CS-4th SemcourseinfoDocument57 pagesCS-4th SemcourseinfoTausifAliNo ratings yet

- ELE 3212 - SS LabDocument49 pagesELE 3212 - SS LabsheetalprachandraNo ratings yet

- B.sc-computer-Science 2017 2018 SyllabusDocument70 pagesB.sc-computer-Science 2017 2018 SyllabusDHIVYA SNo ratings yet

- Elec Lab OutlineDocument3 pagesElec Lab OutlineMushfiq Us SalehinNo ratings yet

- BMCG 2513 - Teaching Plan Sem - 2 2016 2017 - BasriDocument11 pagesBMCG 2513 - Teaching Plan Sem - 2 2016 2017 - BasriW Mohd Zailimi AbdullahNo ratings yet

- Department of Electronic Engineering Bachelors in Electronic EngineeringDocument3 pagesDepartment of Electronic Engineering Bachelors in Electronic EngineeringHani HasanNo ratings yet

- Course Outline - FEADocument2 pagesCourse Outline - FEAFahad IqbalNo ratings yet

- Control Engineering - Units of Study... - Swinburne University of Technology - Melbourne, AustraliaDocument4 pagesControl Engineering - Units of Study... - Swinburne University of Technology - Melbourne, AustraliaFaisal MohmandNo ratings yet

- Cmpe224 CS Fall2010-2011Document3 pagesCmpe224 CS Fall2010-2011MICHAEL K. E. DonkorNo ratings yet

- Introduction To Structural Dynamics and Earthquake EngineeringDocument2 pagesIntroduction To Structural Dynamics and Earthquake EngineeringfefahimNo ratings yet

- Teaching Plan Software EngineeringDocument11 pagesTeaching Plan Software EngineeringHabeeb E SadeedNo ratings yet

- Course Information Sem 12134Document9 pagesCourse Information Sem 12134YooganNo ratings yet

- School of Engineering and Computer Science Department of Electrical & Electronic EngineeringDocument10 pagesSchool of Engineering and Computer Science Department of Electrical & Electronic EngineeringMD. Akif RahmanNo ratings yet

- Eee404 - Eee302 - Lab Sheet GubDocument68 pagesEee404 - Eee302 - Lab Sheet Gubএস এইচ সাকিবNo ratings yet

- Special Topics in ElectronicsDocument6 pagesSpecial Topics in Electronicsramkumar rajaNo ratings yet

- Dwarkadas J. Sanghvi College of EngineeringDocument22 pagesDwarkadas J. Sanghvi College of EngineeringMjNo ratings yet

- EEE 2000 Course SyllabusDocument3 pagesEEE 2000 Course SyllabusAl AminNo ratings yet

- SyllipusDocument4 pagesSyllipusAmeen AlzeidiNo ratings yet

- Chapter 1 - IntroductionDocument28 pagesChapter 1 - Introductioningxing23No ratings yet

- 00 Syllabus For Honors Course Please Dont ShareDocument16 pages00 Syllabus For Honors Course Please Dont ShareAdityaNo ratings yet

- University of Bahrain: MATHS 101 Course SyllabusDocument8 pagesUniversity of Bahrain: MATHS 101 Course SyllabusKomail AlmajjedNo ratings yet

- Course Assesmnet SheetDocument3 pagesCourse Assesmnet SheetMohsin QaziNo ratings yet

- Be Comp Engg Sem-Viii r2019Document56 pagesBe Comp Engg Sem-Viii r2019Sahil KNo ratings yet

- Üsküdar University Faculty of Engineering and Natural Sciences Department of Software EngineeringDocument71 pagesÜsküdar University Faculty of Engineering and Natural Sciences Department of Software EngineeringSomeoneNo ratings yet

- RS579 - Computer Engineering Curriculum 2073 PDFDocument80 pagesRS579 - Computer Engineering Curriculum 2073 PDFreema yadav75% (8)

- CLP - Course Learning Plan SAB 24603 Applied Digital Electronics January 2019Document6 pagesCLP - Course Learning Plan SAB 24603 Applied Digital Electronics January 2019MOHAMAD FADZLI BIN HANIFF 14668No ratings yet

- Elec 578 - Integrated Circuit DesignDocument4 pagesElec 578 - Integrated Circuit DesignVishnu 3333No ratings yet

- Introduction To Data Science Lab ManualDocument76 pagesIntroduction To Data Science Lab Manualpavan kalyanNo ratings yet

- Mechatronics Digital Material RMK Unit I PDFDocument57 pagesMechatronics Digital Material RMK Unit I PDFRajmchzNo ratings yet

- SL - DMA 2122 - Asas Elektrik Dan ElektronikDocument7 pagesSL - DMA 2122 - Asas Elektrik Dan ElektronikfarizanNo ratings yet

- East West University: Department of Computer Science and Engineering Course Outline Spring 2019 SemesterDocument6 pagesEast West University: Department of Computer Science and Engineering Course Outline Spring 2019 Semesterthe rexaNo ratings yet

- Mca-R20-Course Structure-Syllabus (16122021)Document78 pagesMca-R20-Course Structure-Syllabus (16122021)SIXTIE NYNNo ratings yet

- Syllabus Maths111 - 2023-2024 - Sem. II - UpdatedDocument7 pagesSyllabus Maths111 - 2023-2024 - Sem. II - Updatedkingzeus8976No ratings yet

- Bca Scheme and SyllabusDocument76 pagesBca Scheme and SyllabusAbcd GoogleNo ratings yet

- 4EC4-21 ADC Lab AS-16aDocument93 pages4EC4-21 ADC Lab AS-16aSu KoshNo ratings yet

- 1 & 2 Sem Scheme of StudiesDocument2 pages1 & 2 Sem Scheme of StudiesDayanand Gowda KrNo ratings yet

- Course Assesmnet SheetDocument3 pagesCourse Assesmnet SheetMaheen ArshadNo ratings yet

- Introduction to Dynamic Programming: International Series in Modern Applied Mathematics and Computer Science, Volume 1From EverandIntroduction to Dynamic Programming: International Series in Modern Applied Mathematics and Computer Science, Volume 1No ratings yet

- CSC211 Data Structures and AlgorithmsDocument7 pagesCSC211 Data Structures and AlgorithmsSouban JavedNo ratings yet

- Mutee Abdullah FA20-BCE-068 BCE-3B: Implementation of Circular Doubly Linked Lists in C LanguageDocument7 pagesMutee Abdullah FA20-BCE-068 BCE-3B: Implementation of Circular Doubly Linked Lists in C LanguageSouban JavedNo ratings yet

- Electric Machines EEE371 Lab Report # 6: Osama AfzalDocument11 pagesElectric Machines EEE371 Lab Report # 6: Osama AfzalSouban JavedNo ratings yet

- Figure 1: Queue Abstract Data TypeDocument3 pagesFigure 1: Queue Abstract Data TypeSouban JavedNo ratings yet

- CSC141 Introduction To Computer ProgrammingDocument8 pagesCSC141 Introduction To Computer ProgrammingSouban JavedNo ratings yet

- DSA Lab5 Complte PDFDocument4 pagesDSA Lab5 Complte PDFSouban JavedNo ratings yet

- CPE490 Final Year ProjectDocument5 pagesCPE490 Final Year ProjectSouban JavedNo ratings yet

- Curriculum OverviewDocument6 pagesCurriculum OverviewSouban JavedNo ratings yet

- CSC112 Algorithms and Data StructuresDocument8 pagesCSC112 Algorithms and Data StructuresSouban JavedNo ratings yet

- CPE446 Real Time Embedded SystemsDocument10 pagesCPE446 Real Time Embedded SystemsSouban JavedNo ratings yet

- CPE415 Digital Image ProcessingDocument9 pagesCPE415 Digital Image ProcessingSouban JavedNo ratings yet

- CPE314 Data Communication and Computer NetworksDocument9 pagesCPE314 Data Communication and Computer NetworksSouban JavedNo ratings yet

- CPE251 Probability Methods in EngineeringDocument7 pagesCPE251 Probability Methods in EngineeringSouban JavedNo ratings yet

- Terminal: Introduction To Computer Programming CSC-14Document7 pagesTerminal: Introduction To Computer Programming CSC-14Souban JavedNo ratings yet

- MGT462 Project Planning and ManagementDocument9 pagesMGT462 Project Planning and ManagementSouban JavedNo ratings yet

- CPE440 Computer ArchitectureDocument7 pagesCPE440 Computer ArchitectureSouban JavedNo ratings yet

- CPE324 Digital Signal ProcessingDocument9 pagesCPE324 Digital Signal ProcessingSouban JavedNo ratings yet

- CPE345 Embedded Systems WorkshopDocument7 pagesCPE345 Embedded Systems WorkshopSouban JavedNo ratings yet

- Electronics 2 Lab Report #10 Submitted To: DR Khurram Ali Submitted By: Wahaj Rahim Fa18-Bee-160CDocument11 pagesElectronics 2 Lab Report #10 Submitted To: DR Khurram Ali Submitted By: Wahaj Rahim Fa18-Bee-160CSouban JavedNo ratings yet

- Screencapture Chegg Homework Help Questions and Answers Show Work Part B Hint Engineering Electromagnetics Third Edition Nathan Ida q38395171 2022 07 04 23 - 51 - 25Document2 pagesScreencapture Chegg Homework Help Questions and Answers Show Work Part B Hint Engineering Electromagnetics Third Edition Nathan Ida q38395171 2022 07 04 23 - 51 - 25Souban JavedNo ratings yet

- Christian Thibaudeau Men Transformation Plan Updated PDFDocument117 pagesChristian Thibaudeau Men Transformation Plan Updated PDFSouban Javed100% (5)

- Lab Report: 09Document10 pagesLab Report: 09Souban JavedNo ratings yet

- SP20 - Terminal - Dr. Adnan IftikharDocument2 pagesSP20 - Terminal - Dr. Adnan IftikharSouban JavedNo ratings yet

- Lab#4 For and Nested For Loops: A) Yes Yes No No Yes Yes No No No No No No No No No No Yes Yes Yes No No No No NoDocument7 pagesLab#4 For and Nested For Loops: A) Yes Yes No No Yes Yes No No No No No No No No No No Yes Yes Yes No No No No NoSouban JavedNo ratings yet

- Lab 1 To 10 DLDDocument43 pagesLab 1 To 10 DLDSouban JavedNo ratings yet

- Sessional 2Document3 pagesSessional 2Souban JavedNo ratings yet

- (30 Marks) : Lab Sessional 2: Course: ICP (CSC141) Class: BEE 2C - SP 2021Document3 pages(30 Marks) : Lab Sessional 2: Course: ICP (CSC141) Class: BEE 2C - SP 2021Souban JavedNo ratings yet

- Lab 06: Wheatstone Bridge, Delta To Wye and Wye To Delta TransformationDocument7 pagesLab 06: Wheatstone Bridge, Delta To Wye and Wye To Delta TransformationSouban JavedNo ratings yet

- Lab 6 - 10 DLDDocument16 pagesLab 6 - 10 DLDSouban JavedNo ratings yet

- Fa20-Bee-137 Icp Lab6Document8 pagesFa20-Bee-137 Icp Lab6Souban JavedNo ratings yet

- Ansi B16 - 5Document157 pagesAnsi B16 - 5Felipe SandovalNo ratings yet

- 10 Highest Paying PHD DegreesDocument8 pages10 Highest Paying PHD DegreesSteven OsharenaNo ratings yet

- Introduction To Structural EngineeringDocument45 pagesIntroduction To Structural EngineeringAizha JhayNo ratings yet

- Design Patterns SW Quality - English VersionDocument18 pagesDesign Patterns SW Quality - English VersionAdemir Constantino100% (1)

- Society InteriorsDocument208 pagesSociety InteriorsliabocNo ratings yet

- Asme Section II A-2 Sa-455 Sa-455mDocument4 pagesAsme Section II A-2 Sa-455 Sa-455mAnonymous GhPzn1xNo ratings yet

- Vision MissionDocument2 pagesVision MissionmanmohansinghloteyNo ratings yet

- Hoek-Brown Parameters For Predicting The Depth of Brittle Failure Around Tunnels DestacadoDocument16 pagesHoek-Brown Parameters For Predicting The Depth of Brittle Failure Around Tunnels DestacadoPamela Paz Donoso MatusNo ratings yet

- Advantages of PrestressedDocument3 pagesAdvantages of PrestressedLarete PaoloNo ratings yet

- Wireless Communication Unit I Anna UniversityDocument36 pagesWireless Communication Unit I Anna UniversityMr.A.Sriram Asst. ProfNo ratings yet

- Mechanical IntegrityDocument9 pagesMechanical Integritysenor pinkNo ratings yet

- OBE Syllabus - ME 424 - Fluid MachineryDocument3 pagesOBE Syllabus - ME 424 - Fluid MachineryJerico LlovidoNo ratings yet

- Lead Chart 1Document9 pagesLead Chart 1Hoque joynulNo ratings yet

- John Carlos M. Critica Me, RMP, Msiem: ExperienceDocument2 pagesJohn Carlos M. Critica Me, RMP, Msiem: ExperienceCarlos_CriticaNo ratings yet

- 04 SoftwareEngineeringNotCSDocument7 pages04 SoftwareEngineeringNotCSPankaj SoniNo ratings yet

- University of Engineering and Technology Peshawar: B.SC Engineering Degree Programme Academic Session 2019-20Document5 pagesUniversity of Engineering and Technology Peshawar: B.SC Engineering Degree Programme Academic Session 2019-20SarDar AzhiiNo ratings yet

- Post-Tensioning Software Post Tensioning Software ADAPT-Builder / Floor ProDocument18 pagesPost-Tensioning Software Post Tensioning Software ADAPT-Builder / Floor ProAnderson MuñetonNo ratings yet

- Oprema Ravne Pneumatic Tools PresentationDocument3 pagesOprema Ravne Pneumatic Tools PresentationYeimy Estupiñan Fredy VegaNo ratings yet

- 2022 GKS-UIC Application Guidelines (English)Document20 pages2022 GKS-UIC Application Guidelines (English)aprielNo ratings yet

- CB Vs ContactorDocument2 pagesCB Vs ContactorAmit Kumar SinghNo ratings yet

- Concrete Technology: by Dr. R. P. RethaliyaDocument4 pagesConcrete Technology: by Dr. R. P. RethaliyaAkhilesh Kumar67% (3)

- Eligibility Criteria: Bachelor of Computer Applications (BCA) Is A Four-YearDocument3 pagesEligibility Criteria: Bachelor of Computer Applications (BCA) Is A Four-YearTanmoy MitraNo ratings yet

- CH1 TeSys Motor Starters - Open VersionDocument216 pagesCH1 TeSys Motor Starters - Open VersionevansparrowNo ratings yet

- AFT Arrow 9 Quickstart MetricDocument126 pagesAFT Arrow 9 Quickstart MetricUdaya kumar SubramaniNo ratings yet

- Developments in Equipment and Standards For Testing Porosity in CoatingsDocument11 pagesDevelopments in Equipment and Standards For Testing Porosity in Coatingsmfazl33No ratings yet

- Wa0052Document3 pagesWa0052Frank HardingNo ratings yet

- C A 2018 ET HP DesigninfoDocument9 pagesC A 2018 ET HP DesigninfoJonathan DouglasNo ratings yet