Professional Documents

Culture Documents

Fdms3660S: Powertrench Power Stage

Fdms3660S: Powertrench Power Stage

Uploaded by

Max Assistência TécnicaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Fdms3660S: Powertrench Power Stage

Fdms3660S: Powertrench Power Stage

Uploaded by

Max Assistência TécnicaCopyright:

Available Formats

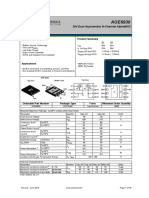

FDMS3660S PowerTrench® Power Stage

January 2012

FDMS3660S

PowerTrench® Power Stage

Asymmetric Dual N-Channel MOSFET

Features General Description

Q1: N-Channel This device includes two specialized N-Channel MOSFETs in a

Max rDS(on) = 8 mΩ at VGS = 10 V, ID = 13 A dual PQFN package. The switch node has been internally

Max rDS(on) = 11 mΩ at VGS = 4.5 V, ID = 11 A connected to enable easy placement and routing of synchronous

buck converters. The control MOSFET (Q1) and synchronous

Q2: N-Channel

SyncFET (Q2) have been designed to provide optimal power

Max rDS(on) = 1.8 mΩ at VGS = 10 V, ID = 30 A

efficiency.

Max rDS(on) = 2.2 mΩ at VGS = 4.5 V, ID = 27 A

Applications

Low inductance packaging shortens rise/fall times, resulting in

lower switching losses Computing

MOSFET integration enables optimum layout for lower circuit Communications

inductance and reduced switch node ringing

General Purpose Point of Load

RoHS Compliant

Notebook VCORE

G1

D1

D1

D1 Q2

D1 S2 5 4 D1

PHASE S2 6 PHASE 3 D1

(S1/D2)

S2 7 2 D1

G2

S2 G2

S2

S2 8 Q1

1 G1

Top Power 56 Bottom

MOSFET Maximum Ratings TA = 25 °C unless otherwise noted

Symbol Parameter Q1 Q2 Units

VDS Drain to Source Voltage 30 30 V

VGS Gate to Source Voltage (Note 3) ±20 ±12 V

Drain Current -Continuous (Package limited) TC = 25 °C 30 60

-Continuous (Silicon limited) TC = 25 °C 60 145

ID A

-Continuous TA = 25 °C 131a 301b

-Pulsed 40 120

EAS Single Pulse Avalanche Energy 334 865 mJ

1a

Power Dissipation for Single Operation TA = 25 °C 2.2 2.51b

PD W

Power Dissipation for Single Operation TA = 25 °C 11c 11d

TJ, TSTG Operating and Storage Junction Temperature Range -55 to +150 °C

Thermal Characteristics

RθJA Thermal Resistance, Junction to Ambient 571a 501b

RθJA Thermal Resistance, Junction to Ambient 1251c 1201d °C/W

RθJC Thermal Resistance, Junction to Case 2.9 2.2

Package Marking and Ordering Information

Device Marking Device Package Reel Size Tape Width Quantity

22CF

FDMS3660S Power 56 13 ” 12 mm 3000 units

07OD

©2011 Fairchild Semiconductor Corporation 1 www.fairchildsemi.com

FDMS3660S Rev.C1

FDMS3660S PowerTrench® Power Stage

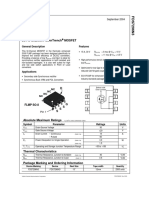

Electrical Characteristics TJ = 25 °C unless otherwise noted

Symbol Parameter Test Conditions Type Min Typ Max Units

Off Characteristics

ID = 250 μA, VGS = 0 V Q1 30

BVDSS Drain to Source Breakdown Voltage V

ID = 1 mA, VGS = 0 V Q2 30

ΔBVDSS Breakdown Voltage Temperature ID = 250 μA, referenced to 25 °C Q1 16

mV/°C

ΔTJ Coefficient ID = 10 mA, referenced to 25 °C Q2 24

Q1 1 μA

IDSS Zero Gate Voltage Drain Current VDS = 24 V, VGS = 0 V

Q2 500 μA

VGS = 20 V, VDS= 0 V Q1 100 nA

IGSS Gate to Source Leakage Current

VGS = 12 V, VDS= 0 V Q2 100 nA

On Characteristics

VGS = VDS, ID = 250 μA Q1 1.1 1.9 2.7

VGS(th) Gate to Source Threshold Voltage V

VGS = VDS, ID = 1 mA Q2 1.1 1.5 2.2

ΔVGS(th) Gate to Source Threshold Voltage ID = 250 μA, referenced to 25 °C Q1 -6

mV/°C

ΔTJ Temperature Coefficient ID = 10 mA, referenced to 25 °C Q2 -3

VGS = 10 V, ID = 13 A 4 8

VGS = 4.5 V, ID = 11 A Q1 6 11

VGS = 10 V, ID = 13 A , TJ = 125 °C 5.7 8.7

rDS(on) Drain to Source On Resistance mΩ

VGS = 10 V, ID = 30 A 1.3 1.8

VGS = 4.5 V, ID = 27 A Q2 1.5 2.2

VGS = 10 V, ID = 30 A , TJ = 125 °C 1.86 2.6

VDS = 5 V, ID = 13 A Q1 62

gFS Forward Transconductance S

VDS = 5 V, ID = 30 A Q2 231

Dynamic Characteristics

Q1: Q1 1325 1765

Ciss Input Capacitance pF

VDS = 15 V, VGS = 0 V, f = 1 MHZ Q2 4130 5493

Q1 466 620

Coss Output Capacitance pF

Q2: Q2 915 1220

VDS = 15 V, VGS = 0 V, f = 1 MHZ Q1 46 70

Crss Reverse Transfer Capacitance pF

Q2 124 185

Q1 0.2 0.6 2

Rg Gate Resistance Ω

Q2 0.2 0.8 3

Switching Characteristics

Q1 7.7 15

td(on) Turn-On Delay Time ns

Q2 11 20

Q1:

Q1 2.2 10

tr Rise Time VDD = 15 V, ID = 13 A, RGEN = 6 Ω ns

Q2 5 10

Q2: Q1 19 34

td(off) Turn-Off Delay Time ns

Q2 40 64

VDD = 15 V, ID = 30 A, RGEN = 6 Ω

Q1 1.8 10

tf Fall Time ns

Q2 3.9 10

Q1 21 29

Qg Total Gate Charge VGS = 0 V to 10 V Q1: nC

Q2 62 87

VDD = 15 V,

Q1 9.5 13

Qg Total Gate Charge VGS = 0 V to 4.5 V ID = 13 A nC

Q2 29 41

Q1 3.9

Qgs Gate to Source Gate Charge Q2: nC

Q2 9

VDD = 15 V,

ID = 30 A Q1 2.6

Qgd Gate to Drain “Miller” Charge nC

Q2 7

©2011 Fairchild Semiconductor Corporation 2 www.fairchildsemi.com

FDMS3660S Rev.C1

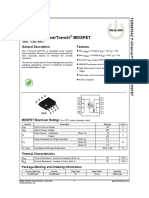

FDMS3660S PowerTrench® Power Stage

Electrical Characteristics TJ = 25 °C unless otherwise noted

Symbol Parameter Test Conditions Type Min Typ Max Units

Drain-Source Diode Characteristics

VGS = 0 V, IS = 13 A (Note 2) Q1 0.8 1.2

V = 0 V, IS = 2 A (Note 2) Q1 0.7 1.2

VSD Source to Drain Diode Forward Voltage GS V

VGS = 0 V, IS = 30 A (Note 2) Q2 0.8 1.2

VGS = 0 V, IS = 2 A (Note 2) Q2 0.6 1.2

Q1: Q1 26 42

trr Reverse Recovery Time ns

IF = 13 A, di/dt = 100 A/μs Q2 29 46

Q2: Q1 10 20

Qrr Reverse Recovery Charge IF = 30 A, di/dt = 300 A/μs nC

Q2 32 50

Notes:

1: RθJA is determined with the device mounted on a 1 in2 pad 2 oz copper pad on a 1.5 x 1.5 in. board of FR-4 material. RθJC is guaranteed by design while RθCA is determined

by the user's board design.

b. 50 °C/W when mounted on

a. 57 °C/W when mounted on a 1 in2 pad of 2 oz copper

a 1 in2 pad of 2 oz copper

c. 125 °C/W when mounted on a d. 120 °C/W when mounted on a

minimum pad of 2 oz copper minimum pad of 2 oz copper

2: Pulse Test: Pulse Width < 300 μs, Duty cycle < 2.0%.

3: As an N-ch device, the negative Vgs rating is for low duty cycle pulse ocurrence only. No continuous rating is implied with the negative Vgs rating.

4: EAS of 33 mJ is based on starting TJ = 25 oC; N-ch: L = 1.9 mH, IAS = 6 A, VDD = 27 V, VGS = 10 V. 100% test at L= 0.1 mH, IAS = 16 A.

5: EAS of 86 mJ is based on starting TJ = 25 oC; N-ch: L = 0.6 mH, IAS = 17 A, VDD = 27 V, VGS = 10 V. 100% test at L= 0.1 mH, IAS = 31 A.

©2011 Fairchild Semiconductor Corporation 3 www.fairchildsemi.com

FDMS3660S Rev.C1

FDMS3660S PowerTrench® Power Stage

Typical Characteristics (Q1 N-Channel) TJ = 25 °C unless otherwise noted

40 4

VGS = 10 V

DRAIN TO SOURCE ON-RESISTANCE

PULSE DURATION = 80 μs

DUTY CYCLE = 0.5% MAX

ID, DRAIN CURRENT (A)

30 3

VGS = 6 V VGS = 3.5 V

NORMALIZED

VGS = 4.5 V

20 VGS = 4 V

2

VGS = 4 V

VGS = 3.5 V

10 1

PULSE DURATION = 80 μs VGS = 4.5 V VGS = 6 V VGS = 10 V

DUTY CYCLE = 0.5% MAX

0 0

0.0 0.2 0.4 0.6 0.8 1.0 0 10 20 30 40

VDS, DRAIN TO SOURCE VOLTAGE (V) ID, DRAIN CURRENT (A)

Figure 1. On Region Characteristics Figure 2. Normalized On-Resistance

vs Drain Current and Gate Voltage

1.6 20

ID = 13 A

DRAIN TO SOURCE ON-RESISTANCE

PULSE DURATION = 80 μs

SOURCE ON-RESISTANCE (mΩ)

VGS = 10 V DUTY CYCLE = 0.5% MAX

1.4 16

rDS(on), DRAIN TO ID = 13 A

NORMALIZED

1.2 12

TJ = 125 oC

1.0 8

0.8 4

TJ = 25 oC

0.6 0

-75 -50 -25 0 25 50 75 100 125 150 2 4 6 8 10

TJ, JUNCTION TEMPERATURE (oC) VGS, GATE TO SOURCE VOLTAGE (V)

Figure 3. Normalized On Resistance Figure 4. On-Resistance vs Gate to

vs Junction Temperature Source Voltage

40 40

VGS = 0 V

IS, REVERSE DRAIN CURRENT (A)

PULSE DURATION = 80 μs

DUTY CYCLE = 0.5% MAX 10

ID, DRAIN CURRENT (A)

30

VDS = 5 V TJ = 150 oC

1

TJ = 150 oC

20

0.1 TJ = 25 oC

TJ = 25 oC

10 TJ = -55 oC

TJ = -55 oC

0.01

0 0.001

1.5 2.0 2.5 3.0 3.5 4.0 0.0 0.2 0.4 0.6 0.8 1.0 1.2

VGS, GATE TO SOURCE VOLTAGE (V) VSD, BODY DIODE FORWARD VOLTAGE (V)

Figure 5. Transfer Characteristics Figure 6. Source to Drain Diode

Forward Voltage vs Source Current

©2011 Fairchild Semiconductor Corporation 4 www.fairchildsemi.com

FDMS3660S Rev.C1

FDMS3660S PowerTrench® Power Stage

Typical Characteristics (Q1 N-Channel) TJ = 25 °C unless otherwise noted

10 2000

VGS, GATE TO SOURCE VOLTAGE (V)

ID = 13 A

VDD = 10 V 1000 Ciss

8

CAPACITANCE (pF)

VDD = 15 V Coss

6

VDD = 20 V

100

4

2 Crss

f = 1 MHz

VGS = 0 V

0 10

0 5 10 15 20 25 0.1 1 10 30

Qg, GATE CHARGE (nC) VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 7. Gate Charge Characteristics Figure 8. Capacitance vs Drain

to Source Voltage

100 80

o

RθJC = 2.9 C/W

IAS, AVALANCHE CURRENT (A)

ID, DRAIN CURRENT (A) 60 VGS = 10 V

TJ = 25 oC

10 40 VGS = 4.5 V

TJ = 100 oC

20

Limited by Package

TJ = 125 oC

1 0

0.001 0.01 0.1 1 10 100 25 50 75 100 125 150

tAV, TIME IN AVALANCHE (ms) TC, CASE TEMPERATURE ( C)

o

Figure 9. Unclamped Inductive Figure 10. Maximum Continuous Drain

Switching Capability Current vs Case Temperature

100 1000

P(PK), PEAK TRANSIENT POWER (W)

SINGLE PULSE

100 μs

o

RθJA = 125 C/W

ID, DRAIN CURRENT (A)

10 100

1 ms

1 THIS AREA IS

10

LIMITED BY rDS(on) 10 ms

100 ms

SINGLE PULSE

TJ = MAX RATED 1s

0.1 1

RθJA = 125 oC/W 10 s

DC

TA = 25 oC

0.01 0.1 -4

0.01 0.1 1 10 100200 10 10

-3

10

-2

10

-1

1 10 100 1000

VDS, DRAIN to SOURCE VOLTAGE (V) t, PULSE WIDTH (sec)

Figure 11. Forward Bias Safe Figure 12. Single Pulse Maximum

Operating Area Power Dissipation

©2011 Fairchild Semiconductor Corporation 5 www.fairchildsemi.com

FDMS3660S Rev.C1

FDMS3660S PowerTrench® Power Stage

Typical Characteristics (Q1 N-Channel) TJ = 25 °C unless otherwise noted

2

DUTY CYCLE-DESCENDING ORDER

1

NORMALIZED THERMAL

D = 0.5

IMPEDANCE, ZθJA

0.2

0.1 PDM

0.1

0.05

0.02

0.01 t1

t2

0.01 SINGLE PULSE

o NOTES:

RθJA = 125 C/W DUTY FACTOR: D = t1/t2

(Note 1c) PEAK TJ = PDM x ZθJA x RθJA + TA

0.001 -4 -3 -2 -1

10 10 10 10 1 10 100 1000

t, RECTANGULAR PULSE DURATION (sec)

Figure 13. Junction-to-Ambient Transient Thermal Response Curve

©2011 Fairchild Semiconductor Corporation 6 www.fairchildsemi.com

FDMS3660S Rev.C1

FDMS3660S PowerTrench® Power Stage

Typical Characteristics (Q2 N-Channel) TJ = 25 oC unlenss otherwise noted

120 4

VGS = 10 V PULSE DURATION = 80 μs

DRAIN TO SOURCE ON-RESISTANCE

DUTY CYCLE = 0.5% MAX

100

VGS = 4.5 V

ID, DRAIN CURRENT (A)

3

VGS = 3.5 V VGS = 2.5 V

80

NORMALIZED

VGS = 3 V

60 2 VGS = 3 V

40

PULSE DURATION = 80 μs 1

20 DUTY CYCLE = 0.5% MAX VGS = 3.5 V VGS = 4.5 V VGS = 10 V

VGS = 2.5 V

0 0

0.0 0.2 0.4 0.6 0.8 1.0 0 20 40 60 80 100 120

VDS, DRAIN TO SOURCE VOLTAGE (V) ID, DRAIN CURRENT (A)

Figure 14. On-Region Characteristics Figure 15. Normalized on-Resistance vs Drain

Current and Gate Voltage

1.6 8

ID = 30 A

DRAIN TO SOURCE ON-RESISTANCE

PULSE DURATION = 80 μs

SOURCE ON-RESISTANCE (mΩ)

VGS = 10 V

DUTY CYCLE = 0.5% MAX

1.4

rDS(on), DRAIN TO 6

ID = 30 A

NORMALIZED

1.2

4

1.0

TJ = 125 oC

2

0.8

TJ = 25 oC

0.6 0

-75 -50 -25 0 25 50 75 100 125 150 2 4 6 8 10

TJ, JUNCTION TEMPERATURE (oC) VGS, GATE TO SOURCE VOLTAGE (V)

Figure 16. Normalized On-Resistance Figure 17. On-Resistance vs Gate to

vs Junction Temperature Source Voltage

120 100

PULSE DURATION = 80 μs

IS, REVERSE DRAIN CURRENT (A)

VGS = 0 V

DUTY CYCLE = 0.5% MAX

100

10

VDS = 5 V TJ = 125 oC

ID, DRAIN CURRENT (A)

80

TJ = 125 oC 1

60

TJ = 25 oC

0.1 TJ = 25 oC

40

TJ = -55 oC

0.01 TJ = -55 oC

20

0 0.001

1.0 1.5 2.0 2.5 3.0 0.0 0.2 0.4 0.6 0.8 1.0

VGS, GATE TO SOURCE VOLTAGE (V) VSD, BODY DIODE FORWARD VOLTAGE (V)

Figure 18. Transfer Characteristics Figure 19. Source to Drain Diode

Forward Voltage vs Source Current

©2011 Fairchild Semiconductor Corporation 7 www.fairchildsemi.com

FDMS3660S Rev.C1

FDMS3660S PowerTrench® Power Stage

Typical Characteristics (Q2 N-Channel) TJ = 25 oC unless otherwise noted

10 10000

VGS, GATE TO SOURCE VOLTAGE (V)

ID = 30 A

8 Ciss

CAPACITANCE (pF)

VDD = 10 V

1000

6

Coss

VDD = 15 V

4

VDD = 20 V 100

Crss

2

f = 1 MHz

VGS = 0 V

0 10

0 10 20 30 40 50 60 70 0.1 1 10 30

Qg, GATE CHARGE (nC) VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 20. Gate Charge Characteristics Figure 21. Capacitance vs Drain

to Source Voltage

100

160

o

RθJC = 2.2 C/W

IAS, AVALANCHE CURRENT (A)

VGS = 10 V

ID, DRAIN CURRENT (A) 120

TJ = 25 oC

VGS = 4.5 V

10 TJ = 100 oC 80

TJ = 125 oC 40

Limited by Package

1

0.001 0.01 0.1 1 10 100 1000 0

25 50 75 100 125 150

tAV, TIME IN AVALANCHE (ms) o

TC, CASE TEMPERATURE ( C)

Figure 22. Unclamped Inductive Figure 23. Maximun Continuous Drain

Switching Capability Current vs Case Temperature

200

2000

100 SINGLE PULSE

P(PK), PEAK TRANSIENT POWER (W)

1000

o

100 μs RθJA = 120 C/W

ID, DRAIN CURRENT (A)

10

100

1 ms

10 ms

1 THIS AREA IS

LIMITED BY rDS(on) 100 ms

SINGLE PULSE 1s 10

0.1 TJ = MAX RATED

10s

RθJA = 120 oC/W

DC

TA = 25 oC 1

0.01

0.01 0.1 1 10 100200 0.5 -4 -3 -2 -1

10 10 10 10 1 10 100 1000

VDS, DRAIN to SOURCE VOLTAGE (V)

t, PULSE WIDTH (sec)

Figure 24. Forward Bias Safe Figure 25. Single Pulse Maximum

Operating Area Power Dissipation

©2011 Fairchild Semiconductor Corporation 8 www.fairchildsemi.com

FDMS3660S Rev.C1

FDMS3660S PowerTrench® Power Stage

Typical Characteristics (Q2 N-Channel) TJ = 25 oC unless otherwise noted

2

DUTY CYCLE-DESCENDING ORDER

1

D = 0.5

NORMALIZED THERMAL

0.2

0.1

IMPEDANCE, ZθJA

0.1

0.05 PDM

0.02

0.01 0.01

t1

t2

SINGLE PULSE

o NOTES:

0.001 RθJA = 120 C/W DUTY FACTOR: D = t1/t2

(Note 1d) PEAK TJ = PDM x ZθJA x RθJA + TA

0.0001 -4 -3 -2 -1

10 10 10 10 1 10 100 1000

t, RECTANGULAR PULSE DURATION (sec)

Figure 26. Junction-to-Ambient Transient Thermal Response Curve

©2011 Fairchild Semiconductor Corporation 9 www.fairchildsemi.com

FDMS3660S Rev.C1

FDMS3660S PowerTrench® Power Stage

Typical Characteristics (continued)

SyncFET Schottky body diode

Characteristics

Fairchild’s SyncFET process embeds a Schottky diode in parallel Schottky barrier diodes exhibit significant leakage at high tem-

with PowerTrench MOSFET. This diode exhibits similar perature and high reverse voltage. This will increase the power

characteristics to a discrete external Schottky diode in parallel in the device.

with a MOSFET. Figure 27 shows the reverse recovery

characteristic of the FDMS3660S.

-2

35 10

IDSS, REVERSE LEAKAGE CURRENT (A)

TJ = 125 oC

30

-3

25 10

didt = 300 A/μs

CURRENT (A)

20 TJ = 100 oC

-4

15 10

10

-5

5 10

0 TJ = 25 oC

-6

-5 10

0 100 200 300 400 0 5 10 15 20 25

TIME (ns) VDS, REVERSE VOLTAGE (V)

Figure 27. FDMS3660S SyncFET body Figure 28. SyncFET body diode reverse

diode reverse recovery characteristic leakage versus drain-source voltage

©2011 Fairchild Semiconductor Corporation 10 www.fairchildsemi.com

FDMS3660S Rev.C1

FDMS3660S PowerTrench® Power Stage

Application Information

1. Switch Node Ringing Suppression

Fairchild’s Power Stage products incorporate a proprietary design* that minimizes the peak overshoot, ringing voltage on the switch

node (PHASE) without the need of any external snubbing components in a buck converter. As shown in the figure 29, the Power Stage

solution rings significantly less than competitor solutions under the same set of test conditions.

Power Stage Device Competitors solution

Figure 29. Power Stage phase node rising edge, High Side Turn on

*Patent Pending

©2011 Fairchild Semiconductor Corporation 11 www.fairchildsemi.com

FDMS3660S Rev.C1

FDMS3660S PowerTrench® Power Stage

Figure 30. Shows the Power Stage in a buck converter topology

2. Recommended PCB Layout Guidelines

As a PCB designer, it is necessary to address critical issues in layout to minimize losses and optimize the performance of the power

train. Power Stage is a high power density solution and all high current flow paths, such as VIN (D1), PHASE (S1/D2) and GND (S2),

should be short and wide for better and stable current flow, heat radiation and system performance. A recommended layout proce-

dure is discussed below to maximize the electrical and thermal performance of the part.

Figure 31. Recommended PCB Layout

©2011 Fairchild Semiconductor Corporation 12 www.fairchildsemi.com

FDMS3660S Rev.C1

FDMS3660S PowerTrench® Power Stage

Following is a guideline, not a requirement which the PCB designer should consider:

1. Input ceramic bypass capacitors C1 and C2 must be placed close to the D1 and S2 pins of Power Stage to help reduce parasitic

inductance and high frequency conduction loss induced by switching operation. C1 and C2 show the bypass capacitors placed close

to the part between D1 and S2. Input capacitors should be connected in parallel close to the part. Multiple input caps can be connected

depending upon the application.

2. The PHASE copper trace serves two purposes; In addition to being the current path from the Power Stage package to the output

inductor (L), it also serves as heat sink for the lower FET in the Power Stage package. The trace should be short and wide enough to

present a low resistance path for the high current flow between the Power Stage and the inductor. This is done to minimize conduction

losses and limit temperature rise. Please note that the PHASE node is a high voltage and high frequency switching node with high

noise potential. Care should be taken to minimize coupling to adjacent traces. The reference layout in figure 31 shows a good balance

between the thermal and electrical performance of Power Stage.

3. Output inductor location should be as close as possible to the Power Stage device for lower power loss due to copper trace

resistance. A shorter and wider PHASE trace to the inductor reduces the conduction loss. Preferably the Power Stage should be

directly in line (as shown in figure 31) with the inductor for space savings and compactness.

4. The PowerTrench® Technology MOSFETs used in the Power Stage are effective at minimizing phase node ringing. It allows the

part to operate well within the breakdown voltage limits. This eliminates the need to have an external snubber circuit in most cases. If

the designer chooses to use an RC snubber, it should be placed close to the part between the PHASE pad and S2 pins to dampen

the high-frequency ringing.

5. The driver IC should be placed close to the Power Stage part with the shortest possible paths for the High Side gate and Low Side

gates through a wide trace connection. This eliminates the effect of parasitic inductance and resistance between the driver and the

MOSFET and turns the devices on and off as efficiently as possible. At higher-frequency operation this impedance can limit the gate

current trying to charge the MOSFET input capacitance. This will result in slower rise and fall times and additional switching losses.

Power Stage has both the gate pins on the same side of the package which allows for back mounting of the driver IC to the board. This

provides a very compact path for the drive signals and improves efficiency of the part.

6. S2 pins should be connected to the GND plane with multiple vias for a low impedance grounding. Poor grounding can create a noise

transient offset voltage level between S2 and driver ground. This could lead to faulty operation of the gate driver and MOSFET.

7. Use multiple vias on each copper area to interconnect top, inner and bottom layers to help smooth current flow and heat conduction.

Vias should be relatively large, around 8 mils to 10 mils, and of reasonable inductance. Critical high frequency components such as

ceramic bypass caps should be located close to the part and on the same side of the PCB. If not feasible, they should be connected

from the backside via a network of low inductance vias.

©2011 Fairchild Semiconductor Corporation 13 www.fairchildsemi.com

FDMS3660S Rev.C1

FDMS3660S PowerTrench® Power Stage

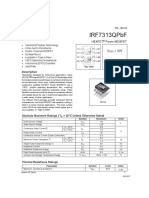

Dimensional Outline and Pad Layout

5.10

4.00

5.10 C

L

4.90

2.00

0.10 C A

0.00

2X PKG B 1.27 TYP

CL

8 5 0.65 TYP

0.63

8 7 6 5

2.52

PKG CL 6.10 1.60

5.90

2.15

0.00 CL

PIN #1 4.16 1.21

IDENT MAY KEEP

1 4 0.10 C 2.13 2.31 OUT

APPEAR AS

OPTIONAL TOP VIEW 2X 1 2 3 4 3.15 AREA

0.63

SEE 0.59

1.18

DETAIL A

3.18

RECOMMENDED LAND PATTERN

SIDE VIEW

0.10 C A B

0.58 3.00 0.70

0.38 2.80 0.50 0.05 C

0.35 1.32

1 2 3 4

6X 1.12

0.71

0.61

NOTES: UNLESS OTHERWISE SPECIFIED

2.25

3.90 2.05

3.70 A) DOES NOT FULLY CONFORM TO

JEDEC REGISTRATION, MO-240,

1.02 ISSUE B DATED 10/2009.

0.58 8 7 6 5 0.82 B) ALL DIMENSIONS ARE IN

0.38 MILLIMETERS.

1.27

0.44 C) DIMENSIONS DO NOT INCLUDE

3.81 BURRS OR MOLD FLASH. MOLD

0.24

BOTTOM VIEW FLASH OR BURRS DOES NOT

EXCEED 0.10MM.

0.51 D) DIMENSIONING AND TOLERANCING

0.31 PER ASME Y14.5M-1994.

0.10 C

E) IT IS RECOMMENDED TO HAVE NO

TRACES OR VIAS WITHIN THE KEEP

OUT AREA.

0.08 C F) DRAWING FILE NAME: PQN08EREV4.

0.30 0.05 C

1.10 0.20 0.00 SEATING

0.90

PLANE

DETAIL A

(SCALE: 2X)

©2011 Fairchild Semiconductor Corporation 14 www.fairchildsemi.com

FDMS3660S Rev.C1

FDMS3660S PowerTrench® Power Stage

TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not

intended to be an exhaustive list of all such trademarks.

2Cool™ F-PFS™ PowerTrench® The Power Franchise®

AccuPower™ FRFET® PowerXS™ ®

AX-CAP™* Global Power ResourceSM Programmable Active Droop™

BitSiC® Green Bridge™ QFET® tm

TinyBoost™

Build it Now™ Green FPS™ QS™

TinyBuck™

CorePLUS™ Green FPS™ e-Series™ Quiet Series™

TinyCalc™

CorePOWER™ Gmax™ RapidConfigure™

TinyLogic®

CROSSVOLT™ GTO™ ™ TINYOPTO™

CTL™ IntelliMAX™

TinyPower™

Current Transfer Logic™ ISOPLANAR™ Saving our world, 1mW/W/kW at a time™

TinyPWM™

DEUXPEED® Marking Small Speakers Sound Louder SignalWise™

TinyWire™

Dual Cool™ and Better™ SmartMax™

TranSiC®

EcoSPARK® MegaBuck™ SMART START™

TriFault Detect™

EfficentMax™ MICROCOUPLER™ Solutions for Your Success™

TRUECURRENT®*

ESBC™ MicroFET™ SPM®

μSerDes™

® MicroPak™ STEALTH™

MicroPak2™ SuperFET®

Fairchild® MillerDrive™ SuperSOT™-3

MotionMax™ SuperSOT™-6 UHC®

Fairchild Semiconductor®

Motion-SPM™ SuperSOT™-8 Ultra FRFET™

FACT Quiet Series™

mWSaver™ SupreMOS® UniFET™

FACT®

OptoHiT™ SyncFET™ VCX™

FAST®

OPTOLOGIC® Sync-Lock™ VisualMax™

FastvCore™

OPTOPLANAR® ®* VoltagePlus™

FETBench™

XS™

FlashWriter® * ®

tm

FPS™

*Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE

RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY

PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY

THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE

EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used here in:

1. Life support devices or systems are devices or systems which, (a) are 2. A critical component in any component of a life support, device, or

intended for surgical implant into the body or (b) support or sustain life, system whose failure to perform can be reasonably expected to cause

and (c) whose failure to perform when properly used in accordance with the failure of the life support device or system, or to affect its safety or

instructions for use provided in the labeling, can be reasonably effectiveness.

expected to result in a significant injury of the user.

ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation’s Anti-Counterfeiting Policy. Fairchild’s Anti-Counterfeiting Policy is also stated on our external website,

www.Fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufactures of semiconductor products are experiencing counterfeiting of their

parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed

application, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the

proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild

Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild

Distributors are genuine parts, have full traceability, meet Fairchild’s quality standards for handing and storage and provide access to Fairchild’s full range of

up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address and

warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is

committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Datasheet contains the design specifications for product development. Specifications

Advance Information Formative / In Design

may change in any manner without notice.

Datasheet contains preliminary data; supplementary data will be published at a later

Preliminary First Production date. Fairchild Semiconductor reserves the right to make changes at any time without

notice to improve design.

Datasheet contains final specifications. Fairchild Semiconductor reserves the right to

No Identification Needed Full Production make changes at any time without notice to improve the design.

Datasheet contains specifications on a product that is discontinued by Fairchild

Obsolete Not In Production

Semiconductor. The datasheet is for reference information only.

Rev. I61

©2011 Fairchild Semiconductor Corporation 15 www.fairchildsemi.com

FDMS3660S Rev.C1

You might also like

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Asymmetric Dual N-Channel MOSFET FDMS3606SDocument16 pagesAsymmetric Dual N-Channel MOSFET FDMS3606SopenstorebussinesNo ratings yet

- FDMS3600S FairchildSemiconductorDocument16 pagesFDMS3600S FairchildSemiconductorvinuNo ratings yet

- FDS8958B ONSemiconductorDocument11 pagesFDS8958B ONSemiconductorMaycon FerreiraNo ratings yet

- General Description Product Summary: 30V Dual Asymmetric N-Channel MOSFETDocument10 pagesGeneral Description Product Summary: 30V Dual Asymmetric N-Channel MOSFETseborgNo ratings yet

- Dual P-Channel Powertrench Mosfet: November 2008Document6 pagesDual P-Channel Powertrench Mosfet: November 2008Gedealdo TorresNo ratings yet

- Ic Dual Channel - FDS6982-79262Document10 pagesIc Dual Channel - FDS6982-79262BryanJermyHendrikNo ratings yet

- General Description Product Summary: 30V Dual Asymmetric N-Channel MOSFETDocument10 pagesGeneral Description Product Summary: 30V Dual Asymmetric N-Channel MOSFETErnesto PuenteNo ratings yet

- Fdw9926A: Dual N-Channel 2.5V Specified Powertrench MosfetDocument5 pagesFdw9926A: Dual N-Channel 2.5V Specified Powertrench MosfetbilarodrigoNo ratings yet

- Fdms7698: N-Channel Powertrench MosfetDocument7 pagesFdms7698: N-Channel Powertrench MosfetAdrian Kim BabelaNo ratings yet

- Fdms7682: N-Channel Powertrench MosfetDocument8 pagesFdms7682: N-Channel Powertrench MosfetGustavo RodriguezNo ratings yet

- Fds6982S: Dual Notebook Power Supply N-Channel Powertrench SyncfetDocument9 pagesFds6982S: Dual Notebook Power Supply N-Channel Powertrench SyncfetManuel LeaNo ratings yet

- General Description Product Summary: 30V Dual Asymmetric N-Channel MOSFETDocument10 pagesGeneral Description Product Summary: 30V Dual Asymmetric N-Channel MOSFETkornolNo ratings yet

- FDS8958Document8 pagesFDS8958Fabio NevesNo ratings yet

- FDMS0310AS FairchildSemiconductorDocument8 pagesFDMS0310AS FairchildSemiconductorThisal DamsikaNo ratings yet

- 2424 FDMS86300Document7 pages2424 FDMS86300Ivkan MarsovskiNo ratings yet

- Fds 4559Document8 pagesFds 4559Roni SocompiNo ratings yet

- Asymmetric Dual N-Channel Trench MOSFET 30V: General Description FeaturesDocument9 pagesAsymmetric Dual N-Channel Trench MOSFET 30V: General Description Featureschristian romoNo ratings yet

- Fds 9933 ADocument5 pagesFds 9933 Aasasdassdfdf asdfasdsdfsfsdNo ratings yet

- AM9945NDocument9 pagesAM9945NCarlos AlbertoNo ratings yet

- c9945 TermokingDocument7 pagesc9945 TermokingNelson CabelloNo ratings yet

- Fds 9953 ADocument6 pagesFds 9953 AМирослава НиколенкоNo ratings yet

- FDMC 8884Document7 pagesFDMC 8884Kholit LitNo ratings yet

- FDS6990ASDocument8 pagesFDS6990ASal.aliefzainiiNo ratings yet

- General Description Product Summary: 30V Dual Asymmetric N-Channel AlphamosDocument10 pagesGeneral Description Product Summary: 30V Dual Asymmetric N-Channel AlphamosSomendra SinghNo ratings yet

- General Description Product Summary: 30V Complementary MOSFETDocument9 pagesGeneral Description Product Summary: 30V Complementary MOSFETSebastian CorreaNo ratings yet

- MDU5593S: Dual Asymmetric N-Channel Trench MOSFET 30VDocument9 pagesMDU5593S: Dual Asymmetric N-Channel Trench MOSFET 30VYuri PryimychNo ratings yet

- NDS9955 Dual N-Channel Enhancement Mode Field Effect TransistorDocument9 pagesNDS9955 Dual N-Channel Enhancement Mode Field Effect TransistorMahdi RayNo ratings yet

- Fds6986S: Dual Notebook Power Supply N-Channel Powertrench SyncfetDocument10 pagesFds6986S: Dual Notebook Power Supply N-Channel Powertrench Syncfetdayne81sNo ratings yet

- Fds 4435 ADocument5 pagesFds 4435 AThoni Tsaqif BRNo ratings yet

- AO4932 MosfetDocument9 pagesAO4932 MosfetMuhammad MajidNo ratings yet

- Si4925Dy Dual P-Channel, Logic Level, Powertrench Mosfet: January 2001Document6 pagesSi4925Dy Dual P-Channel, Logic Level, Powertrench Mosfet: January 2001Julio Hernandez MateoNo ratings yet

- Fairchild - Semiconductor FDMC8884 DatasheetDocument7 pagesFairchild - Semiconductor FDMC8884 DatasheetmirandowebsNo ratings yet

- Dual N-Channel 60 V (D-S) 175 °C MOSFET: P5506HVGDocument9 pagesDual N-Channel 60 V (D-S) 175 °C MOSFET: P5506HVGYoannel Ceballo EstradaNo ratings yet

- Fds6690A Single N-Channel, Logic Level, Powertrench MosfetDocument8 pagesFds6690A Single N-Channel, Logic Level, Powertrench MosfetEsmir MarinNo ratings yet

- FDS6630A DatasheetDocument5 pagesFDS6630A DatasheetAytac GulNo ratings yet

- Fds6975 Dual P-Channel, Logic Level, Powertrench MosfetDocument8 pagesFds6975 Dual P-Channel, Logic Level, Powertrench MosfetAbdul KurniadiNo ratings yet

- FDS6975Document5 pagesFDS6975sweet boy play boyNo ratings yet

- Fds6690As: 30V N-Channel Powertrench SyncfetDocument8 pagesFds6690As: 30V N-Channel Powertrench SyncfetManuel LeaNo ratings yet

- Dual 30V P-Channel Powertrench Mosfet: General Description FeaturesDocument5 pagesDual 30V P-Channel Powertrench Mosfet: General Description FeaturesLuis AntunesNo ratings yet

- FDS6298 FairchildSemiconductorDocument6 pagesFDS6298 FairchildSemiconductortigajaya1568No ratings yet

- Onsemiconductor Nds8410a Datasheets 3577Document5 pagesOnsemiconductor Nds8410a Datasheets 3577Google EyeNo ratings yet

- SQJ992EP: Vishay SiliconixDocument11 pagesSQJ992EP: Vishay SiliconixcqlNo ratings yet

- Si 7212 DNDocument12 pagesSi 7212 DNVenegas GamaNo ratings yet

- FDC6312PDocument5 pagesFDC6312PsbrhomeNo ratings yet

- FDS7296N3 - 30V N-Channel PowerTrench MOSFETDocument7 pagesFDS7296N3 - 30V N-Channel PowerTrench MOSFETLangllyNo ratings yet

- FDS6930 PDFDocument5 pagesFDS6930 PDFTut MorisNo ratings yet

- General Description Product Summary: 30V Dual P-Channel MOSFETDocument7 pagesGeneral Description Product Summary: 30V Dual P-Channel MOSFETDaniel CarreraNo ratings yet

- SPF0004 Data Sheet: V = 275 V, R = 0.26 Ω Dual N-channel Power MOSFETDocument11 pagesSPF0004 Data Sheet: V = 275 V, R = 0.26 Ω Dual N-channel Power MOSFETytnateNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument5 pagesAdvanced Power Electronics Corp.: DescriptionСергій ЖабкоNo ratings yet

- Fdq7238S: Dual Notebook Power Supply N Channel Powertrench in So-14 PackageDocument10 pagesFdq7238S: Dual Notebook Power Supply N Channel Powertrench in So-14 PackageEdy Valeriano ChicllaNo ratings yet

- Fds6679Az P-Channel Powertrench Mosfet: - 30V, - 13A, 9M General Description FeaturesDocument6 pagesFds6679Az P-Channel Powertrench Mosfet: - 30V, - 13A, 9M General Description FeaturesEdgxr DxnielNo ratings yet

- Irf7313Qpbf: Hexfet Power Mosfet V 30V R 0.029Document7 pagesIrf7313Qpbf: Hexfet Power Mosfet V 30V R 0.029daslanNo ratings yet

- N-Channel Powertrench Mosfet: 30V, 7A, 23M General Description FeaturesDocument6 pagesN-Channel Powertrench Mosfet: 30V, 7A, 23M General Description FeaturesLuis CarlosNo ratings yet

- Fdp52N20 / Fdpf52N20T: UnifetDocument10 pagesFdp52N20 / Fdpf52N20T: UnifetJoão de barroNo ratings yet

- FDMC 7692 SDocument8 pagesFDMC 7692 SAndrey RossiNo ratings yet

- SQJ960EP: Vishay SiliconixDocument11 pagesSQJ960EP: Vishay SiliconixgilamadaNo ratings yet

- WSF3013Document10 pagesWSF3013Abu SaeedNo ratings yet

- fdp33n25 fdpf33n25tDocument10 pagesfdp33n25 fdpf33n25tNovri AndiNo ratings yet

- Generation V Technology Ultra Low On-Resistance Dual N-Channel MOSFET Surface Mount Fully Avalanche RatedDocument7 pagesGeneration V Technology Ultra Low On-Resistance Dual N-Channel MOSFET Surface Mount Fully Avalanche Rateddayne81sNo ratings yet

- Naive BayesDocument36 pagesNaive BayesgibthaNo ratings yet

- Formatted SBI Clerk Mains Previous Year Paper 2021Document78 pagesFormatted SBI Clerk Mains Previous Year Paper 2021shyamveer147No ratings yet

- Certiport Exam Administration Policies: Examination SecurityDocument2 pagesCertiport Exam Administration Policies: Examination SecurityrajputamitdNo ratings yet

- Ea 4 15 G PDFDocument22 pagesEa 4 15 G PDFshabanNo ratings yet

- What Is The Substation Automation System (SAS) and What You MUST Know About ItDocument24 pagesWhat Is The Substation Automation System (SAS) and What You MUST Know About Itዛላው መናNo ratings yet

- Cma Part 1 Mock 2Document44 pagesCma Part 1 Mock 2armaghan175% (8)

- The Untouchables and The Pax Britannica Dr. B.R.ambedkarDocument61 pagesThe Untouchables and The Pax Britannica Dr. B.R.ambedkarVeeramani ManiNo ratings yet

- Cases On EntrapmentDocument25 pagesCases On Entrapmentmarion914No ratings yet

- Anh - 10Document50 pagesAnh - 10Hưng PhúNo ratings yet

- I) Height of Retaining Wall H: Preliminary DataDocument10 pagesI) Height of Retaining Wall H: Preliminary DataOmPrakashNo ratings yet

- LRS Trading StrategyDocument24 pagesLRS Trading Strategybharatbaba363No ratings yet

- Quiz Bank Recon and Proof of CashDocument3 pagesQuiz Bank Recon and Proof of CashAlexander ONo ratings yet

- Question Bank AR VRDocument17 pagesQuestion Bank AR VRarambamranajsingh04No ratings yet

- For School PaperDocument7 pagesFor School PaperHanzelkris CubianNo ratings yet

- Middle Level Reading Part 3 PoemDocument10 pagesMiddle Level Reading Part 3 Poem이세희No ratings yet

- American Shooting - Journal March.2021Document108 pagesAmerican Shooting - Journal March.2021adawedlfNo ratings yet

- NEW Fees Record 2010-11Document934 pagesNEW Fees Record 2010-11manojchouhan2014No ratings yet

- Tahiti Vacation GuideDocument84 pagesTahiti Vacation GuideAlex D.No ratings yet

- Notes For OMDocument77 pagesNotes For OMmukesh jatNo ratings yet

- Form Jurnal JesikomDocument9 pagesForm Jurnal JesikomAhmad Hafiizh kudrawiNo ratings yet

- Week7Advanced Materials Electronic MaterialsDocument16 pagesWeek7Advanced Materials Electronic Materialsmarlon corpuzNo ratings yet

- 2019 2020 AEB Expression of InterestDocument1 page2019 2020 AEB Expression of InterestCentre AdministratorNo ratings yet

- SH Catalogue - Neuro & SpinalDocument17 pagesSH Catalogue - Neuro & SpinalSaqibullah ShahzadNo ratings yet

- VSX-830-K - Single Sheet - ENDocument2 pagesVSX-830-K - Single Sheet - ENEDNo ratings yet

- Adrian Cooke: LimerickDocument2 pagesAdrian Cooke: Limerickapi-401919939No ratings yet

- Introduction Main PDFDocument3 pagesIntroduction Main PDFshubhu11No ratings yet

- Describing The Impact of Massive Open Online Course: Darielle Apilas-Bacayan Developer LessonDocument5 pagesDescribing The Impact of Massive Open Online Course: Darielle Apilas-Bacayan Developer LessonJhunel FernandezNo ratings yet

- MANUAL DESENVOLVIMENTO BSSV E24218Document146 pagesMANUAL DESENVOLVIMENTO BSSV E24218valdirsaraujoNo ratings yet

- 102 192 1 SMDocument8 pages102 192 1 SMLinaNo ratings yet

- Physics 2018 Prelims NYJC Paper 2Document19 pagesPhysics 2018 Prelims NYJC Paper 2NG KAI EE EMMANUELLE NG KAI EE EMMANUELLENo ratings yet