Professional Documents

Culture Documents

Haswell Block Diagram

Haswell Block Diagram

Uploaded by

alastoridCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Haswell Block Diagram

Haswell Block Diagram

Uploaded by

alastoridCopyright:

Available Formats

Haswell Block Diagram

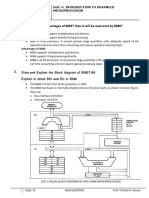

Front End

Instruction

Cache Tag

Branch 32KB 8-way

Prediction uOP Cache L1 Instruction Cache

Tag Instruction TLB

16Bytes

uOP Cache Instruction Fetch

Hit Logic and PreDecode

6 IA Instructions

Instruction Queue

5 IA Instructions

4-way Decode (Micro-Fusion/Macro-Fusion)

MicroCode

ROM Complex Simple Simple Simple

Decoder Decoder Decoder Decoder

Up to 4 Fused uOPs 4 Fused uOPs

uOP Cache Allocation Queue(56 uOPs)

(1.5k uOPs)

4 Fused uOPs

Rename/Allocate/Retirement

(ReOrder Buffer 192 entries) Zeroing Ideoms

uOPs

uOPs

uOPs

uOPs

uOPs

uOPs

uOPs

uOPs

Scheduler (Unified Reservation Station) (60 entries)

168 Integer Physical Register Files 168 Vector Physical Register Files

8-way, 11Cycle Latency

Port 0 Port 1 Port 5 Port 6 Port 2 Port 3 Port 4 Port 7

L2 Cache

Port 0

Port 1

Port 5

Port 6

Port 2

Port 3

Port 4

Port 7

L2 TLB

256KB

ALU&Shift ALU ALU ALU&Shift Load Address Load Address Store Address L3 and

Store Data beyond

Branch LEA(Load Effective Address) LEA(Load Effective Address) Branch Store Address Store Address

Divide Multiply Vector Shuffle

256-bit FMA(Multiply-Add) 256-bit FMA(Multiply-Add) Vector Integer ALU

256-bit FP Multiply 256-bit FP Add Vector Logicals

Vector Integer Multiply Vector Integer ALU

Store Buffer(42 entries)

Vector Logicals Vector Logicals And Forwarding

Vector Shift

32 Bytes/Cycle Store

L1 Data Cache Data TLB

72 Load Buffers

32KB 8-way

Execution 2x32 Bytes/Cycle 64 Bytes/Cycle

Engine Load

Memory

Copyright (c) 2013 Hiroshige Goto All rights reserved.

You might also like

- OSPF MyanmarDocument127 pagesOSPF MyanmarMin Min Zaw100% (12)

- LCD Operator: Installation ManualDocument58 pagesLCD Operator: Installation ManualCristian MartinezNo ratings yet

- Sdcs-03 Part 1 (Distribution Network Grounding) Rev01Document107 pagesSdcs-03 Part 1 (Distribution Network Grounding) Rev01Haytham BafoNo ratings yet

- ARM Cortex-A76 Block DiagramDocument1 pageARM Cortex-A76 Block Diagram文帅宋No ratings yet

- Parallelism (2) & Heterogeneous Computing & Future PerspetivesDocument50 pagesParallelism (2) & Heterogeneous Computing & Future Perspetivesacer smithNo ratings yet

- William Stallings Computer Organization and Architecture 10 EditionDocument40 pagesWilliam Stallings Computer Organization and Architecture 10 EditionFirmanNo ratings yet

- ARM Cortex-A57 Block DiagramDocument1 pageARM Cortex-A57 Block Diagram文帅宋No ratings yet

- ARM Cortex-A7 Core Block DiagramDocument1 pageARM Cortex-A7 Core Block Diagram文帅宋No ratings yet

- IT5551ComputerNetworks Test1 Sep2022Document7 pagesIT5551ComputerNetworks Test1 Sep2022gauthamNo ratings yet

- Microprocessor Systems Microprocessor Systems: BEE-11B Dr. Ahmad SalmanDocument26 pagesMicroprocessor Systems Microprocessor Systems: BEE-11B Dr. Ahmad SalmanNihal AhmadNo ratings yet

- Case Study of Assemblers For x85 and x86 Machines: by Aditya Bhardwaj Email: Aditya - Cse@nitttrchd - Ac.inDocument6 pagesCase Study of Assemblers For x85 and x86 Machines: by Aditya Bhardwaj Email: Aditya - Cse@nitttrchd - Ac.inRiteshNo ratings yet

- Ul T I Mat e Vi Deo PL Ayback Tool F or Prof Essi Onal S: FeaturesDocument1 pageUl T I Mat e Vi Deo PL Ayback Tool F or Prof Essi Onal S: FeaturesTKNo ratings yet

- E70 Knor R Breams Convent I Onall Oco: Dsllocodet Achi Ngofbr I Dgi NGDocument2 pagesE70 Knor R Breams Convent I Onall Oco: Dsllocodet Achi Ngofbr I Dgi NGsmmudakeNo ratings yet

- Patient Gas ModuleDocument12 pagesPatient Gas ModuleRobson BarrosNo ratings yet

- 8086 Microprocessor LEC - 1: Topic: Why 8086 Was Required? Various Features of 8086 MicroprocessorDocument58 pages8086 Microprocessor LEC - 1: Topic: Why 8086 Was Required? Various Features of 8086 MicroprocessorDivyes PNo ratings yet

- Time TableDocument3 pagesTime TableParul GuptaNo ratings yet

- Full Download PDF of (Original PDF) Becoming A Master Student 6th Edition All ChapterDocument43 pagesFull Download PDF of (Original PDF) Becoming A Master Student 6th Edition All Chapterhopaferds3100% (6)

- Knowledge Area Process Name InputsDocument19 pagesKnowledge Area Process Name Inputsarunpandey1686No ratings yet

- Knowledge Area Process Name InputsDocument10 pagesKnowledge Area Process Name InputsvijaymuruganGNo ratings yet

- University of Bristol MicroarchitectureDocument10 pagesUniversity of Bristol Microarchitecturehungck4567No ratings yet

- Puter ScienceDocument12 pagesPuter SciencePriya SNo ratings yet

- Procedure: Stack Operations Stack OperationsDocument21 pagesProcedure: Stack Operations Stack OperationsDaniel GastonNo ratings yet

- 8051 MicrocontrollerDocument20 pages8051 Microcontrollerbhoopesh_kumawatNo ratings yet

- OPeration & Maintenance ManualDocument23 pagesOPeration & Maintenance ManualMohammed Esheaba100% (1)

- Semantic Web Unit 2 NotesDocument19 pagesSemantic Web Unit 2 Notesnt1763No ratings yet

- WT WN Jntuh CseDocument178 pagesWT WN Jntuh CseAngel SweetyNo ratings yet

- A Beginners Guide To Oscp 2021 - OscpDocument1 pageA Beginners Guide To Oscp 2021 - OscpTara SuttonNo ratings yet

- RFNoC: Fosphor - How To Apply RFNoC To RTSA Display AccelerationDocument19 pagesRFNoC: Fosphor - How To Apply RFNoC To RTSA Display AccelerationmateusmaxiNo ratings yet

- Packet Data Convergence ProtocolDocument20 pagesPacket Data Convergence ProtocolNishantNo ratings yet

- MPMC Unit 2Document26 pagesMPMC Unit 2Akkina SowmyaNo ratings yet

- ARM Cortex-A72 Block DiagramDocument1 pageARM Cortex-A72 Block Diagram文帅宋No ratings yet

- Intoducion A OtnDocument72 pagesIntoducion A OtnGustavo CazaresNo ratings yet

- DVP-SX Multi-Function, Built-In Analog I - O, MultipleDocument2 pagesDVP-SX Multi-Function, Built-In Analog I - O, MultipleJulio Molina MuñozNo ratings yet

- 400 KV Kharghar Report 27 OctDocument4 pages400 KV Kharghar Report 27 Octraneshyamsunder37No ratings yet

- MP Unit1Document40 pagesMP Unit1lococo2836No ratings yet

- Lock Ating: Prof. Kaushik Roy at Purdue UnivDocument8 pagesLock Ating: Prof. Kaushik Roy at Purdue UnivDr. Sampatrao L PinjareNo ratings yet

- 8051 Chap3 Hardware (New)Document56 pages8051 Chap3 Hardware (New)Nguyen Quoc HuyNo ratings yet

- ACN Experiment 5-6Document11 pagesACN Experiment 5-6ShashankNo ratings yet

- EuroimmunDocument4 pagesEuroimmunDaria SereholaNo ratings yet

- Euroimmun ManualDocument4 pagesEuroimmun ManualAFWNo ratings yet

- Installation InstructionsDocument1 pageInstallation InstructionsPuji Faisal NawawiNo ratings yet

- Yp Sgna?: Learn PLC in HindiDocument4 pagesYp Sgna?: Learn PLC in HindiSantosh konduskarNo ratings yet

- Quagga Routing Configuration Guide 2.12Document171 pagesQuagga Routing Configuration Guide 2.12Tranh DongNo ratings yet

- OXO Connect 6.1 Global Product Limits ENT SMB 043132 01 EnDocument9 pagesOXO Connect 6.1 Global Product Limits ENT SMB 043132 01 Enleonardo333555No ratings yet

- Aixperf Part2Document26 pagesAixperf Part2emcviltNo ratings yet

- Experiment #2: To Glow Leds in Sequence For All PortsDocument8 pagesExperiment #2: To Glow Leds in Sequence For All PortsFahim RiazNo ratings yet

- Architecture 8iDocument1 pageArchitecture 8iPaul9268No ratings yet

- List of Vacant Positions in The Central Office17012022185625Document5 pagesList of Vacant Positions in The Central Office17012022185625Caryl FranceNo ratings yet

- Malp Unit 6 Marks 14Document10 pagesMalp Unit 6 Marks 14Khilan MendaparaNo ratings yet

- CH06-9780444543196 (2019 - 12 - 27 16 - 04 - 56 Utc)Document63 pagesCH06-9780444543196 (2019 - 12 - 27 16 - 04 - 56 Utc)tayyaba mehmoodNo ratings yet

- 15CS54 - FLAT - Properties of RGsDocument17 pages15CS54 - FLAT - Properties of RGsAnshul Kumar NeekharaNo ratings yet

- Push Andvpop Instructions in 8051 MicrocontrollerDocument6 pagesPush Andvpop Instructions in 8051 Microcontrolleree210150900103No ratings yet

- ReportDocument57 pagesReportJack MaynorNo ratings yet

- Special Activities of MAR Activities During Lockdown Period - MAKAUT PDFDocument1 pageSpecial Activities of MAR Activities During Lockdown Period - MAKAUT PDFmimi Chudi100% (1)

- Hedayatullah Saidy B21F0802CS055 COAL - LAB 02Document10 pagesHedayatullah Saidy B21F0802CS055 COAL - LAB 02Hedayatullah SaidyNo ratings yet

- Call TreeDocument2 pagesCall Treeayu anandaNo ratings yet

- ReeeDocument1 pageReeeSigit HimawanNo ratings yet

- MPMP Ass1Document14 pagesMPMP Ass1kirrakparty.chanduNo ratings yet

- Kurzweil Product Line November 2014Document1 pageKurzweil Product Line November 2014Indrek AarelaidNo ratings yet

- IT WorksheetDocument2 pagesIT WorksheetNominee OnlineNo ratings yet

- A Framework For Building Extensible C++ Class Libraries - 1993Document18 pagesA Framework For Building Extensible C++ Class Libraries - 1993alastoridNo ratings yet

- Alpha AXP Architecture - 1992 (Vol4num4art1)Document40 pagesAlpha AXP Architecture - 1992 (Vol4num4art1)alastoridNo ratings yet

- The Hideous Name - 1985 (Pike85hideous)Document8 pagesThe Hideous Name - 1985 (Pike85hideous)alastoridNo ratings yet

- Computer Systems ResearchDocument16 pagesComputer Systems ResearchalastoridNo ratings yet

- United States Patent: EilebrechtDocument12 pagesUnited States Patent: EilebrechtalastoridNo ratings yet

- Scsi Command Table (In Opcode Order)Document2 pagesScsi Command Table (In Opcode Order)alastoridNo ratings yet

- Introduction To Parallel Architectures - Josep Torrellas - CS533 (2012)Document14 pagesIntroduction To Parallel Architectures - Josep Torrellas - CS533 (2012)alastoridNo ratings yet

- Perfect Hash Functions - SlidesDocument5 pagesPerfect Hash Functions - SlidesalastoridNo ratings yet

- Intel I3Document14 pagesIntel I3AdamNo ratings yet

- Introduction To Emerging Technologies: Cloud ComputingDocument79 pagesIntroduction To Emerging Technologies: Cloud ComputingCherianXavierNo ratings yet

- SM VRF SystemsDocument332 pagesSM VRF SystemsNatalia Beglet100% (1)

- WaterGems WorkDocument41 pagesWaterGems WorkSameerMinhaj100% (2)

- So No Ma 32Document6 pagesSo No Ma 32Carlos Laza RodriguezNo ratings yet

- NE1101 Presentation-1 PDFDocument16 pagesNE1101 Presentation-1 PDFEnache GabrielNo ratings yet

- Lempel-Ziv-Welch (LZW) Compression AlgorithmDocument22 pagesLempel-Ziv-Welch (LZW) Compression AlgorithmRohitSharmaNo ratings yet

- PROJECT PROFILE ON COMPUTER CENTRE CYBER CAFE AT Imphal PDFDocument2 pagesPROJECT PROFILE ON COMPUTER CENTRE CYBER CAFE AT Imphal PDFWattaba HiromNo ratings yet

- EAS6800+ High Quality Composite Video Encoder/Synchronizer and Analog Audio DemultiplexerDocument90 pagesEAS6800+ High Quality Composite Video Encoder/Synchronizer and Analog Audio DemultiplexerTechne PhobosNo ratings yet

- Alle V-Infos EnglischDocument43 pagesAlle V-Infos EnglischMohamed Rashed50% (2)

- 1.BAPI - How To Use Standard BAPIDocument10 pages1.BAPI - How To Use Standard BAPIDionisis PanagopoulosNo ratings yet

- Codigo de Labview JimmyDocument3 pagesCodigo de Labview JimmyMuhammad NuzuluddinNo ratings yet

- Diwali CarnivalDocument2 pagesDiwali CarnivalUPPULANo ratings yet

- DVR Board Common Problems and Solutions-TTB Vision Co.Document4 pagesDVR Board Common Problems and Solutions-TTB Vision Co.TTB VisionNo ratings yet

- Eng DatasheetDocument2 pagesEng DatasheetMARIAMNo ratings yet

- Interface eDocument4 pagesInterface eمصطفى بلالNo ratings yet

- Model 53 Compression Load CellDocument3 pagesModel 53 Compression Load CellLi'sNo ratings yet

- AN7148Document4 pagesAN7148Alejandro Borrego DominguezNo ratings yet

- Report Text Report Text: Silmi Hayati Putri 31 Xmipa3Document8 pagesReport Text Report Text: Silmi Hayati Putri 31 Xmipa3Silmi Hayati PutriNo ratings yet

- KM-C2630 Service ManualDocument460 pagesKM-C2630 Service ManualAnonymous egTruyVdxvNo ratings yet

- W130hu/ W130HVDocument100 pagesW130hu/ W130HVAriel CazzanigaNo ratings yet

- Exploring Quattro Pro Formulas, Functions, and MacrosDocument267 pagesExploring Quattro Pro Formulas, Functions, and MacrosCommonLawyer100% (1)

- Wi XXXX-PXX Rev. x1 Pump TestingDocument14 pagesWi XXXX-PXX Rev. x1 Pump TestingJessie MazonNo ratings yet

- Victor: Network Deployment Testing For Up To 2 Mbit/sDocument4 pagesVictor: Network Deployment Testing For Up To 2 Mbit/sAnirudhaNo ratings yet

- Configure BSNL Broadband ModemDocument2 pagesConfigure BSNL Broadband ModemsarvessaiNo ratings yet

- Module 4 Implementing Storage Spaces and Data DeduplicationDocument65 pagesModule 4 Implementing Storage Spaces and Data DeduplicationMagno SolísNo ratings yet

- DLBT0802533EN00Document5 pagesDLBT0802533EN00shareyourfilesNo ratings yet

- Metal Steel Bending Press PlansDocument16 pagesMetal Steel Bending Press PlansFrenchwolf42080% (5)