Professional Documents

Culture Documents

L-6 (DK) (Pe) ( (Ee) Nptel) 5

L-6 (DK) (Pe) ( (Ee) Nptel) 5

Uploaded by

GagneOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

L-6 (DK) (Pe) ( (Ee) Nptel) 5

L-6 (DK) (Pe) ( (Ee) Nptel) 5

Uploaded by

GagneCopyright:

Available Formats

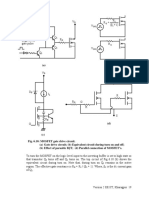

BJT the SOA of a MOSFET is plotted on a log-log graph.

On the top, the SOA is restricted

by the absolute maximum permissible value of the drain current (IDM) which should not be

exceeded even under pulsed operating condition. To the left, operating restriction arise due

to the non zero value of rDS(ON) corresponding to vGS = vGS(Max). To the right, the first

operating restriction is due to the limit on the maximum permissible junction temperature

rise which depends on the power dissipation inside the MOSFET. This limit is different for

DC (continuous) and pulsed operation of different pulse widths. As in the case of a BJT the

pulsed safe operating areas are useful for shaping the switching trajectory of a MOSFET. A

MOSFET does not undergo “second break down” and no corresponding operating limit

appears on the SOA. The final operation limit to the extreme right of the SOA arises due to

the maximum permissible drain source voltage (VDSS) which is decided by the avalanche

break down voltage of the drain -body p-n junction. This is an instantaneous limit. There is

no distinction between the forward biased and the reverse biased SOAs for the MOSFET.

They are identical.

Log (iD)

IDM

10-5sec

rDS(ON) limit 10-4sec

(VGS = VGS(max))

Max. 10-3sec

Power

Dissipation DC

Limit (Timax) Primary voltage breakdown

limit

VDSS Log (vDS)

Fig. 6.6: Safe operating area of a MOSFET.

Due to the presence of the anti parallel “body diode”, a MOSFET can not block any reverse

voltage. The body diode, however, can carry an RMS current equal to IDM. It also has a

substantial surge current carrying capacity. When reverse biased it can block a voltage

equal to VDSS.

For safe operation of a MOSFET, the maximum limit on the gate source voltage (VGS

(Max)) must be observed. Exceeding this voltage limit will cause dielectric break down of

the thin gate oxide layer and permanent failure of the device. It should be noted that even

static charge inadvertently put on the gate oxide by careless handling may destroy it. The

device user should ground himself before handling any MOSFET to avoid any static charge

related problem.

Exercise 6.2

Fill in the blank(s) with the appropriate word(s)

i. A MOSFET operates in the ________________ mode when vGS < vGS(th)

Version 2 EE IIT, Kharagpur 13

ii. In the ohmic region of operation of a MOSFET vGS – vGS (th) is greater than

________________.

iii. rDS (ON) of a MOSFET ________________ with increasing vGS.

iv. In the active region of operation the drain current iD is a function of ________________

alone and is independent of ________________.

v. The primary break down voltage of MOSFET is ________________ of the drain

current.

vi. Unlike BJT a MOSFET does not undergo ________________.

vii. ________________ temperature coefficient of rDS(ON) of MOSFETs facilitates easy

________________ of the devices.

viii. In a Power MOSFET the relation ship between iD and vGS – vGS(th) is almost

________________ in the active mode of operation.

ix. The safe operating area of a MOSFET is restricted on the left hand side by the

________________ limit.

Answer: (i) Cut off; (ii) vDS; (iii) decreases; (iv) vGS, vDS; (v) independent; (vi) second

break down; (vii) Positive, paralleling; (viii) linear; (ix) rDS (ON);

6.5 Switching characteristics of a MOSFET

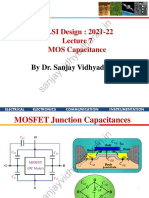

6.5.1 Circuit models of a MOSFET cell

Like any other power semiconductor device a MOSFET is used as a switch in all power

electronic converters. As a switch a MOSFET operates either in the cut off mode (switch

off) or in the ohmic mode (switch on). While making transition between these two states it

traverses through the active region. Being a majority carrier device the switching process in

a MOSFET does not involve any inherent delay due to redistribution of minority charge

carriers. However, formation of the conducting channel in a MOSFET and its

disappearance require charging and discharging of the gate-source capacitance which

contributes to the switching times. There are several other capacitors in a MOSFET

structure which are also involved in the switching process. Unlike bipolar devices,

however, these switching times can be controlled completely by the gate drive circuit

design.

Version 2 EE IIT, Kharagpur 14

G

S

Gate oxide

+

n CGD

CGS CGD

p Drain body CGD1 idealized

depletion

CDS layer Actual

n-

CGD2

n+

VGS – VGS (th) = VDS VDS

D

(a) (b)

D D D

CGD CGD CGD

G (cut off) G iD = f(vGS) G rDS(ON)

(Active) (Ohmic)

CGS CGS CGS

S S S

(c)

Fig. 6.7: Circuit model of a MOSFET

(a) MOSFET capacitances

(b) Variation of CGD with VDS

(c) Circuit models.

Fig 6.7 (a) shows three important capacitances inherent in a MOSFET structure. The most

prominent capacitor in a MOSFET structure is formed by the gate oxide layer between the

gate metallization and the n+ type source region. It has the largest value (a few nano farads)

and remains more or less constant for all values of vGS and vDS. The next largest capacitor

(a few hundred pico forwards) is formed by the drain – body depletion region directly

below the gate metallization in the n- drain drift region. Being a depletion layer capacitance

its value is a strong function of the drain source voltage vDS. For low values of vDS (vDS <

(vGS – vGS (th))) the value of CGD (CGD2) is considerably higher than its value for large vDS

as shown in Fig 6.7 (b). Although variation of CGD between CGD1 and CGD2 is continuous a

step change in the value of CGD at vDS = vGS – vGS(th) is assumed for simplicity. The lowest

value capacitance is formed between the drain and the source terminals due to the drain –

body depletion layer away form the gate metallization and below the source metallization.

Although this capacitance is important for some design considerations (such as snubber

design, zero voltage switching etc) it does not appreciably affect the “hard switching”

performance of a MOSFET. Consequently, it will be neglected in our discussion. From the

Version 2 EE IIT, Kharagpur 15

You might also like

- Unit 4 Assignment 2 PXS TEMPLATEDocument4 pagesUnit 4 Assignment 2 PXS TEMPLATEAnNo ratings yet

- Dokumen - Pub Sbas For The Frcstramporth Examination A Companion To Postgraduate Orthopaedics Candidates Guide 1stnbsped 1108789978 9781108789974 1108803644 9781108803649 9781108846790Document646 pagesDokumen - Pub Sbas For The Frcstramporth Examination A Companion To Postgraduate Orthopaedics Candidates Guide 1stnbsped 1108789978 9781108789974 1108803644 9781108803649 9781108846790sharan sambhwani0% (2)

- Breville BCI600 Ice Cream Maker User Manual PDFDocument40 pagesBreville BCI600 Ice Cream Maker User Manual PDFTon TonNo ratings yet

- Industrial Training at Jeha Numa Palace BhopalDocument17 pagesIndustrial Training at Jeha Numa Palace BhopalSoniaSingh100% (2)

- L-6 (DK) (Pe) ( (Ee) Nptel) 7Document3 pagesL-6 (DK) (Pe) ( (Ee) Nptel) 7GagneNo ratings yet

- L-6 (DK) (Pe) ( (Ee) Nptel) 4Document3 pagesL-6 (DK) (Pe) ( (Ee) Nptel) 4GagneNo ratings yet

- B.E.-vi Semester-Power Electronics LabDocument68 pagesB.E.-vi Semester-Power Electronics LabNanda Kishore PNNo ratings yet

- Unit 2 Part ADocument88 pagesUnit 2 Part AMohammad Anas MajidNo ratings yet

- Week 7 Chapter 3 FET Small Signal AnalysisDocument64 pagesWeek 7 Chapter 3 FET Small Signal AnalysisA.K.M.TOUHIDUR RAHMANNo ratings yet

- L-6 (DK) (Pe) ( (Ee) Nptel) 6Document3 pagesL-6 (DK) (Pe) ( (Ee) Nptel) 6GagneNo ratings yet

- 9.small Signal Analysis of MosfetsDocument27 pages9.small Signal Analysis of MosfetsNitin Mehta - 18-BEC-030No ratings yet

- CHAPTER 8 SMALL SIGNAL ANALYSIS OF MOSFETsDocument25 pagesCHAPTER 8 SMALL SIGNAL ANALYSIS OF MOSFETsshubhankar palNo ratings yet

- Unit III - MCQsDocument15 pagesUnit III - MCQsMission Gate2021No ratings yet

- MOSFET ExperimentDocument13 pagesMOSFET ExperimentsureshNo ratings yet

- Power MOSFET BasicsDocument6 pagesPower MOSFET BasicsNic NinjaelectricoNo ratings yet

- Lecture (8) ...Document27 pagesLecture (8) ...Kamal MohamedNo ratings yet

- MT-28-Ch17-2 (Mosfet Basics)Document8 pagesMT-28-Ch17-2 (Mosfet Basics)Mark JacksonNo ratings yet

- Lab Ix. Metal Oxide Semiconductor Field Effect Transistors: 1. ObjectiveDocument10 pagesLab Ix. Metal Oxide Semiconductor Field Effect Transistors: 1. Objectivesfdgfh ftyNo ratings yet

- Mosfet (Metal Oxide Semiconductor Field Effect Transitor) : ElektronikaDocument20 pagesMosfet (Metal Oxide Semiconductor Field Effect Transitor) : ElektronikaIrfan AlfandyNo ratings yet

- An 401Document27 pagesAn 401renatoNo ratings yet

- Lecture 31: Jfets As Variable Resistors: Automatic Gain ControlDocument7 pagesLecture 31: Jfets As Variable Resistors: Automatic Gain ControlUdBlNo ratings yet

- Irfz24n PDFDocument9 pagesIrfz24n PDFSergio ReyesNo ratings yet

- 320 Lecture 26Document8 pages320 Lecture 26marcelofilgueirasNo ratings yet

- Irfz 34 NDocument9 pagesIrfz 34 NVitorio LogoNo ratings yet

- 320 Lecture 28Document7 pages320 Lecture 28Kirubel MulugetaNo ratings yet

- Infineon IRF7495 DataSheet v01 - 01 ENDocument9 pagesInfineon IRF7495 DataSheet v01 - 01 ENSIBTEK GROUPNo ratings yet

- IRFRU120NDocument10 pagesIRFRU120NWilson Yecit OrtizNo ratings yet

- SOT-23-6L Plastic-Encapsulate MOSFETS: CJL8205ADocument5 pagesSOT-23-6L Plastic-Encapsulate MOSFETS: CJL8205AdexterNo ratings yet

- Irl530n IrfDocument8 pagesIrl530n IrfJuan De la cruzNo ratings yet

- 0.1 MOS Transistor at High Frequency: GS GDDocument2 pages0.1 MOS Transistor at High Frequency: GS GDSimone MolinaroNo ratings yet

- Infineon IRF8736 DataSheet v01 - 01 ENDocument10 pagesInfineon IRF8736 DataSheet v01 - 01 ENElbertt GonzalezNo ratings yet

- MOSFET Biasing Using A Single Power SupplyDocument9 pagesMOSFET Biasing Using A Single Power SupplySabaJavedNo ratings yet

- Advanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedMax RenanNo ratings yet

- Irf8736Pbf: ApplicationsDocument9 pagesIrf8736Pbf: ApplicationsAnilVarmaNo ratings yet

- Lec 7 MOS-CapacitanceDocument13 pagesLec 7 MOS-CapacitanceMainak TarafdarNo ratings yet

- Gate Drive Design For Large Mosfet Apt9302Document10 pagesGate Drive Design For Large Mosfet Apt9302Grzegorz WegnerNo ratings yet

- Irf520npbf PDFDocument9 pagesIrf520npbf PDFMbah NgepotNo ratings yet

- Restificter h2345Document8 pagesRestificter h2345gustavo coteNo ratings yet

- Mosfet CharacteristicsDocument8 pagesMosfet CharacteristicsTim PriceNo ratings yet

- Irf6644Pbf Irf6644Trpbf: V V R Q Q VDocument10 pagesIrf6644Pbf Irf6644Trpbf: V V R Q Q VDarwin SipayungNo ratings yet

- Lecture09 MOSFET (2) Model DC AnalysisDocument9 pagesLecture09 MOSFET (2) Model DC AnalysisRubén RodriguezNo ratings yet

- 64 2096pbf KNHuDWrv 2j6YLvwomDocument10 pages64 2096pbf KNHuDWrv 2j6YLvwomCh Jameel SidhuNo ratings yet

- Vlsi 2Document14 pagesVlsi 2Chris JonathanNo ratings yet

- Application Note Anp20Document15 pagesApplication Note Anp20Raka Satria PradanaNo ratings yet

- DatasheetDocument12 pagesDatasheetPoon Electronic Training CentreNo ratings yet

- ZXMN 6 A 07 FtaDocument8 pagesZXMN 6 A 07 FtaFakhri AliNo ratings yet

- IRFI4024H-117P: DescriptionDocument6 pagesIRFI4024H-117P: Descriptionjean grangeonNo ratings yet

- Lecture 2 Revision MOSFET Operation and ModellingDocument35 pagesLecture 2 Revision MOSFET Operation and ModellingDominiqueNo ratings yet

- Transistor Mosfet: Dr. Pham Nguyen Thanh LoanDocument77 pagesTransistor Mosfet: Dr. Pham Nguyen Thanh LoanhajjkaNo ratings yet

- IRFRU120 NLDocument10 pagesIRFRU120 NLWilson Yecit OrtizNo ratings yet

- Irf 530Document8 pagesIrf 53021524002No ratings yet

- Irf3808Pbf: Automotive MosfetDocument10 pagesIrf3808Pbf: Automotive Mosfetejdigger ejNo ratings yet

- IRF3710Document10 pagesIRF3710MaksumAbdullahNo ratings yet

- 1.2.2 Static Behaviour: Active RegionDocument7 pages1.2.2 Static Behaviour: Active RegionWaleedhasan HasanNo ratings yet

- ZXMN6A07Z 60V SOT89 N-Channel Enhancement Mode MosfetDocument8 pagesZXMN6A07Z 60V SOT89 N-Channel Enhancement Mode MosfetGuillermo TéllezNo ratings yet

- Datasheet Irf7380qpbfDocument8 pagesDatasheet Irf7380qpbfДрагиша Небитни ТрифуновићNo ratings yet

- ZXMP6A16K 60V DPAK P-Channel Enhancement Mode MOSFETDocument8 pagesZXMP6A16K 60V DPAK P-Channel Enhancement Mode MOSFETadityoNo ratings yet

- Infineon IRF1010EZPBF DatasheetDocument3 pagesInfineon IRF1010EZPBF DatasheetNdidi KennethNo ratings yet

- Infineon IRF1010E Aplication - ENDocument9 pagesInfineon IRF1010E Aplication - ENlaciNo ratings yet

- Chenming Hu ch7 SlidesDocument43 pagesChenming Hu ch7 SlideseleenaamohapatraNo ratings yet

- F9Z24N InternationalRectifierDocument8 pagesF9Z24N InternationalRectifierCristea GabrielNo ratings yet

- Automotive Mosfet: Typical ApplicationsDocument10 pagesAutomotive Mosfet: Typical ApplicationsSaikumarNo ratings yet

- Irsds11530 1Document11 pagesIrsds11530 1udaymachNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- 5 - L-17 (NKD) (Pe) ( (Ee) Nptel)Document1 page5 - L-17 (NKD) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 6 - L-17 (NKD) (Pe) ( (Ee) Nptel)Document1 page6 - L-17 (NKD) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 13 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page13 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 8 - L-17 (NKD) (Pe) ( (Ee) Nptel)Document1 page8 - L-17 (NKD) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 4 - L-17 (NKD) (Pe) ( (Ee) Nptel)Document1 page4 - L-17 (NKD) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 7 - L-17 (NKD) (Pe) ( (Ee) Nptel)Document1 page7 - L-17 (NKD) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 3 - L-17 (NKD) (Pe) ( (Ee) Nptel)Document1 page3 - L-17 (NKD) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 5 - L-12 (DK) (Pe) ( (Ee) Nptel)Document1 page5 - L-12 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 18 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page18 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 4 - L-12 (DK) (Pe) ( (Ee) Nptel)Document1 page4 - L-12 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 14 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page14 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 17 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page17 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 16 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page16 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 10 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page10 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 12 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page12 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 23 - L-10 (DK) (Pe) ( (Ee) Nptel)Document1 page23 - L-10 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 15 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page15 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 11 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page11 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 9 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page9 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 24 - L-10 (DK) (Pe) ( (Ee) Nptel)Document1 page24 - L-10 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 16 - L-10 (DK) (Pe) ( (Ee) Nptel)Document1 page16 - L-10 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 8 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page8 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 19 - L-10 (DK) (Pe) ( (Ee) Nptel)Document1 page19 - L-10 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 7 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page7 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 6 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page6 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 5 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page5 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 4 - L-11 (DK) (Pe) ( (Ee) Nptel)Document1 page4 - L-11 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 22 - L-10 (DK) (Pe) ( (Ee) Nptel)Document1 page22 - L-10 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 18 - L-10 (DK) (Pe) ( (Ee) Nptel)Document1 page18 - L-10 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- 15 - L-10 (DK) (Pe) ( (Ee) Nptel)Document1 page15 - L-10 (DK) (Pe) ( (Ee) Nptel)GagneNo ratings yet

- US Vs PinedaDocument1 pageUS Vs PinedaSan Pedro TeamNo ratings yet

- Sad Music Helps Mend Broken HeartsDocument2 pagesSad Music Helps Mend Broken HeartsRocio Rojas FariasNo ratings yet

- Multiple Choice Questions Section: Choose The Most Appropriate Single AnswerDocument3 pagesMultiple Choice Questions Section: Choose The Most Appropriate Single Answersepanta2002No ratings yet

- Penerapan Sistem Haccp Jurusan Gizi Poltekkes Kemenkes MalangDocument3 pagesPenerapan Sistem Haccp Jurusan Gizi Poltekkes Kemenkes MalangGita Martha VIndiartiNo ratings yet

- Chapter 2 ElectricityDocument31 pagesChapter 2 ElectricityArshad MalikNo ratings yet

- Nabl 400Document669 pagesNabl 400Apex IndiaNo ratings yet

- 16 August AI PharmaDocument3 pages16 August AI PharmahiteshguptaNo ratings yet

- Dipyridamole (Cardoxin Forte)Document6 pagesDipyridamole (Cardoxin Forte)asdwasdNo ratings yet

- Nursing Care Plan: DATE: March 2, 2021Document1 pageNursing Care Plan: DATE: March 2, 2021Grascia SchneiderNo ratings yet

- Boilere Solare BF 9Document1 pageBoilere Solare BF 9HitNo ratings yet

- The Excretory/ Urinary System: Lecture By: Marri Jmelou M. Roldan, MSCDocument29 pagesThe Excretory/ Urinary System: Lecture By: Marri Jmelou M. Roldan, MSCHeaven SolNo ratings yet

- PVC PDFDocument15 pagesPVC PDFsrabon1059No ratings yet

- Secondary RefrigerantsDocument15 pagesSecondary Refrigerantse4erkNo ratings yet

- Impact of Chinese Cusine in Indian CusineDocument15 pagesImpact of Chinese Cusine in Indian CusineAshish PatnaikNo ratings yet

- Ecodrain ED 2000 3000 enDocument8 pagesEcodrain ED 2000 3000 enClaudio TurlherNo ratings yet

- 7 Differential EquationsDocument12 pages7 Differential EquationsJuan Miguel GonzalesNo ratings yet

- Site Specific Safety PlanDocument4 pagesSite Specific Safety Planjithin shankarNo ratings yet

- Exercises For Lab Report 0 202133Document3 pagesExercises For Lab Report 0 202133Luis Giovanni Ortiz Rodríguez IINo ratings yet

- Gps PDFDocument1 pageGps PDFcyderNo ratings yet

- CBEN408 06 Field Operations Inlet ReceivingDocument59 pagesCBEN408 06 Field Operations Inlet ReceivingForcus onNo ratings yet

- Solid State13thDocument19 pagesSolid State13thRaju SinghNo ratings yet

- Goods Received Note Pharmacy 05-05-2023Document1 pageGoods Received Note Pharmacy 05-05-2023Innocent MissingsNo ratings yet

- Escaping Poverty and Becoming Poor: Who Gains, Who Loses, and Why?Document16 pagesEscaping Poverty and Becoming Poor: Who Gains, Who Loses, and Why?Hương NuNo ratings yet

- My Best Friend Just Became My ManagerDocument2 pagesMy Best Friend Just Became My ManagerBernardo John JambalosNo ratings yet

- PDV01 - CO1.1. Knowing-Oneself-and-Development-and-Self-awarenessDocument9 pagesPDV01 - CO1.1. Knowing-Oneself-and-Development-and-Self-awarenessChlarisse Gabrielle TanNo ratings yet

- Chapter 23 CommunicationsDocument16 pagesChapter 23 CommunicationsHrishikesh NarasimhanNo ratings yet