Professional Documents

Culture Documents

GA50JT12-247 SiC 1200V 50A

GA50JT12-247 SiC 1200V 50A

Uploaded by

RaduCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

GA50JT12-247 SiC 1200V 50A

GA50JT12-247 SiC 1200V 50A

Uploaded by

RaduCopyright:

Available Formats

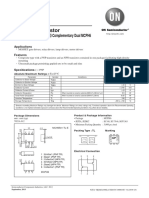

GA50JT12-247

Normally – OFF Silicon Carbide VDS = 1200 V

Junction Transistor RDS(ON) = 20 mΩ

ID (Tc = 25°C) = 100 A

ID (Tc > 125°C) = 50 A

hFE (Tc = 25°C) = 85

Features Package

• 175 °C Maximum Operating Temperature

• Gate Oxide Free SiC Switch D

• Exceptional Safe Operating Area

• Excellent Gain Linearity

• Temperature Independent Switching Performance

• Low Output Capacitance

• S

Positive Temperature Coefficient of RDS,ON D

• Suitable for Connecting an Anti-parallel Diode G

TO-247

Advantages Applications

• Compatible with Si MOSFET/IGBT Gate Drive ICs • Down Hole Oil Drilling, Geothermal Instrumentation

• > 20 µs Short-Circuit Withstand Capability • Hybrid Electric Vehicles (HEV)

• Lowest-in-class Conduction Losses • Solar Inverters

• High Circuit Efficiency • Switched-Mode Power Supply (SMPS)

• Minimal Input Signal Distortion • Power Factor Correction (PFC)

• High Amplifier Bandwidth • Induction Heating

• Uninterruptible Power Supply (UPS)

• Motor Drives

Table of Contents

Section I: Absolute Maximum Ratings .......................................................................................................... 1

Section II: Static Electrical Characteristics ................................................................................................... 2

Section III: Dynamic Electrical Characteristics ............................................................................................ 2

Section IV: Figures .......................................................................................................................................... 3

Section V: Driving the GA50JT12-247 ........................................................................................................... 7

Section VI: Package Dimensions ................................................................................................................. 11

Section VII: SPICE Model Parameters ......................................................................................................... 12

Section I: Absolute Maximum Ratings

Parameter Symbol Conditions Value Unit Notes

Drain – Source Voltage VDS VGS = 0 V 1200 V

Continuous Drain Current ID TC = 25°C 100 A Fig. 17

Continuous Drain Current ID TC = 145°C 50 A Fig. 17

Continuous Gate Current IG 3.5 A

TVJ = 175 oC, ID,max = 50

Turn-Off Safe Operating Area RBSOA A Fig. 19

Clamped Inductive Load @ VDS ≤ VDSmax

TVJ = 175 oC, IG = 1 A, VDS = 800 V,

Short Circuit Safe Operating Area SCSOA Non Repetitive

>20 µs

Reverse Gate – Source Voltage VSG 30 V

Reverse Drain – Source Voltage VSD 25 V

Power Dissipation Ptot TC = 25 °C / 145 °C, tp > 100 ms 583 / 116 W Fig. 16

Storage Temperature Tstg -55 to 175 °C

Dec 2015 Latest version of this datasheet at: http://www.genesicsemi.com/commercial-sic/sic-junction-transistors/ Pg 1 of 11

GA50JT12-247

Section II: Static Electrical Characteristics

Value

Parameter Symbol Conditions Unit Notes

Min. Typical Max.

A: On State

ID = 50 A, Tj = 25 °C 20

Drain – Source On Resistance RDS(ON) ID = 50 A, Tj = 150 °C 30 mΩ Fig. 5

ID = 50 A, Tj = 175 °C 35

ID = 50 A, ID/IG = 40, Tj = 25 °C 3.42

Gate – Source Saturation Voltage VGS,SAT ID = 50 A, ID/IG = 30, Tj = 175 °C

V Fig. 7

3.23

VDS = 8 V, ID = 50 A, Tj = 25 °C 85

DC Current Gain hFE VDS = 8 V, ID = 50 A, Tj = 125 °C 57 – Fig. 4

VDS = 8 V, ID = 50 A, Tj = 175 °C 51

B: Off State

VDS = 1200 V, VGS = 0 V, Tj = 25 °C 10

Drain Leakage Current IDSS VDS = 1200 V, VGS = 0 V, Tj = 150 °C 20 μA Fig. 8

VDS = 1200 V, VGS = 0 V, Tj = 175 °C 20

Gate Leakage Current ISG VSG = 20 V, Tj = 25 °C 20 nA

C: Thermal

Thermal resistance, junction - case RthJC 0.26 °C/W Fig. 20

Section III: Dynamic Electrical Characteristics

Value

Parameter Symbol Conditions Unit Notes

Min. Typical Max.

A: Capacitance and Gate Charge

Input Capacitance Ciss VGS = 0 V, VDS = 800 V, f = 1 MHz 7080 pF Fig. 9

Reverse Transfer/Output Capacitance Crss/Coss VDS = 800 V, f = 1 MHz 130 pF Fig. 9

Output Capacitance Stored Energy EOSS VGS = 0 V, VDS = 800 V, f = 1 MHz 50 µJ Fig. 10

Effective Output Capacitance,

Coss,tr ID = constant, VGS = 0 V, VDS = 0…800 V 230 pF

time related

Effective Output Capacitance,

Coss,er VGS = 0 V, VDS = 0…800 V 160 pF

energy related

Gate-Source Charge QGS VGS = -5…3 V 60 nC

Gate-Drain Charge QGD VGS = 0 V, VDS = 0…800 V 185 nC

Gate Charge - Total QG 245 nC

B: Switching1

Internal Gate Resistance – ON RG(INT-ON) VGS > 2.5 V, VDS = 0 V, Tj = 175 ºC 0.1 Ω

Turn On Delay Time td(on) Tj = 25 ºC, VDS = 800 V, 15 ns

Fall Time, VDS tf ID = 50 A, Resistive Load 35 ns Fig. 11, 13

Turn Off Delay Time td(off) Refer to Section V for additional 35 ns

Rise Time, VDS tr driving information. 20 ns Fig. 12, 14

Turn On Delay Time td(on) 15 ns

Fall Time, VDS tf Tj = 175 ºC, VDS = 800 V, 35 ns Fig. 11

Turn Off Delay Time td(off) ID = 50 A, Resistive Load 40 ns

Rise Time, VDS tr 20 ns Fig. 12

Turn-On Energy Per Pulse Eon Tj = 25 ºC, VDS = 800 V, 1070 µJ Fig. 11, 13

Turn-Off Energy Per Pulse Eoff ID = 50 A, Inductive Load 360 µJ Fig. 12, 14

Total Switching Energy Etot Refer to Section V. 1430 µJ

Turn-On Energy Per Pulse Eon 1030 µJ Fig. 11

Tj = 175 ºC, VDS = 800 V,

Turn-Off Energy Per Pulse Eoff ID = 50 A, Inductive Load

320 µJ Fig. 12

Total Switching Energy Etot 1350 µJ

1

– All times are relative to the Drain-Source Voltage VDS

Dec 2015 Latest version of this datasheet at: http://www.genesicsemi.com/commercial-sic/sic-junction-transistors/ Pg 2 of 11

GA50JT12-247

Section IV: Figures

A: Static Characteristics

Figure 1: Typical Output Characteristics at 25 °C Figure 2: Typical Output Characteristics at 150 °C

Figure 3: Typical Output Characteristics at 175 °C Figure 4: DC Current Gain vs. Drain Current

Figure 5: On-Resistance vs. Gate Current Figure 6: Normalized On-Resistance vs. Temperature

Dec 2015 Latest version of this datasheet at: http://www.genesicsemi.com/commercial-sic/sic-junction-transistors/ Pg 3 of 11

GA50JT12-247

Figure 7: Typical Gate – Source Saturation Voltage Figure 8: Typical Blocking Characteristics

B: Dynamic Characteristics

Figure 9: Input, Output, and Reverse Transfer Capacitance Figure 10: Energy Stored in Output Capacitance

Figure 11: Typical Switching Times and Turn On Energy Figure 12: Typical Switching Times and Turn Off Energy

Losses vs. Temperature Losses vs. Temperature

Dec 2015 Latest version of this datasheet at: http://www.genesicsemi.com/commercial-sic/sic-junction-transistors/ Pg 4 of 11

GA50JT12-247

Figure 13: Typical Switching Times and Turn On Energy Figure 14: Typical Switching Times and Turn Off Energy

Losses vs. Drain Current Losses vs. Drain Current

C: Current and Power Derating

Figure 15: Typical Hard Switched Device Power Loss vs.

2 Figure 16: Power Derating Curve

Switching Frequency

o

Figure 17: Drain Current Derating vs. Temperature Figure 18: Forward Bias Safe Operating Area at Tc= 25 C

2

– Representative values based on device conduction and switching loss. Actual losses will depend on gate drive conditions, device load, and circuit topology.

Dec 2015 Latest version of this datasheet at: http://www.genesicsemi.com/commercial-sic/sic-junction-transistors/ Pg 5 of 11

GA50JT12-247

Figure 19: Turn-Off Safe Operating Area Figure 20: Transient Thermal Impedance

Figure 21: Drain Current Derating vs. Pulse Width

Dec 2015 Latest version of this datasheet at: http://www.genesicsemi.com/commercial-sic/sic-junction-transistors/ Pg 6 of 11

GA50JT12-247

Section V: Driving the GA50JT12-247

Gate Drive Power Switching

Drive Topology Application Emphasis Availability

Consumption Frequency

TTL Logic High Low Wide Temperature Range Coming Soon

Constant Current Medium Medium Wide Temperature Range Coming Soon

High Speed – Boost Capacitor Medium High Fast Switching Production

High Speed – Boost Inductor Low High Ultra Fast Switching Coming Soon

Proportional Lowest High Wide Drain Current Range Coming Soon

Pulsed Power Medium N/A Pulse Power Coming Soon

A: Static TTL Logic Driving

The GA50JT12-247 may be driven using direct (5 V) TTL logic after current amplification. The (amplified) current level of the supply must meet

or exceed the steady state gate current (IG,steady) required to operate the GA50JT12-247. The power level of the supply can be estimated from

the target duty cycle of the particular application. IG,steady is dependent on the anticipated drain current ID through the SJT and the DC current

gain hFE, it may be calculated from the following equation. An accurate value of the hFE may be read from Figure 4.

𝐼𝐼𝐷𝐷

𝐼𝐼𝐺𝐺,𝑠𝑠𝑠𝑠𝑠𝑠𝑠𝑠𝑠𝑠𝑠𝑠 ≈ ∗ 1.5

ℎ𝐹𝐹𝐹𝐹 (𝑇𝑇, 𝐼𝐼𝐷𝐷 )

5V D

CG

TTL

Gate Signal

RG G

5/0V IG,steady

TTL i/p

S

Figure 22: TTL Gate Drive Schematic

B: High Speed Driving

The SJT is a current controlled transistor which requires a positive gate current for turn-on as well as to remain in on-state. An ideal gate

current waveform for ultra-fast switching of the SJT, while maintaining low gate drive losses, is shown in Figure 23 which features a positive

current peak during turn-on, a negative current peak during turn-off, and continuous gate current to remain on.

Figure 23: An idealized gate current waveform for fast switching of an SJT.

An SJT is rapidly switched from its blocking state to on-state, when the necessary gate charge, QG, for turn-on is supplied by a burst of high

gate current, IG,on, until the gate-source capacitance, CGS, and gate-drain capacitance, CGD, are fully charged.

𝑄𝑄𝑜𝑜𝑜𝑜 = 𝐼𝐼𝐺𝐺,𝑜𝑜𝑜𝑜 ∗ 𝑡𝑡1

𝑄𝑄𝑜𝑜𝑜𝑜 ≥ 𝑄𝑄𝑔𝑔𝑔𝑔 + 𝑄𝑄𝑔𝑔𝑔𝑔

Dec 2015 Latest version of this datasheet at: http://www.genesicsemi.com/commercial-sic/sic-junction-transistors/ Pg 7 of 11

GA50JT12-247

Ideally, IG,on should terminate when the drain voltage falls to its on-state value in order to avoid unnecessary drive losses during the steady on-

state. In practice, the rise time of the IG,on pulse is affected by the parasitic inductances, Lpar in the device package and drive circuit. A voltage

developed across the parasitic inductance in the source path, Ls, can de-bias the gate-source junction, when high drain currents begin to flow

through the device. The voltage applied to the gate pin should be maintained high enough, above the VGS,sat (see Figure 7) level to counter

these effects.

A high negative peak current, -IG,off is recommended at the start of the turn-off transition, in order to rapidly sweep out the injected carriers from

the gate, and achieve rapid turn-off. While satisfactory turn off can be achieved with VGS = 0 V, a negative gate voltage VGS may be used in

order to speed up the turn-off transition.

Two high-speed drive topologies for the SiC SJTs are presented below.

B:1: High Speed, Low Loss Drive with Boost Capacitor, GA15IDDJT22-FR4

The GA50JT12-247 may be driven using a High Speed, Low Loss Drive with Boost Capacitor topology in which multiple voltage levels, a gate

resistor, and a gate capacitor are used to provide fast switching current peaks at turn-on and turn-off and a continuous gate current while in

on-state. An evaluation gate drive board (GA15IDDJT22-FR4) utilizing this topology is commercially available for low-side driving, its

datasheet provides additional details.

Gate Driver Board

CG1

VGL VGL VGH D

Signal

R2 CG2 Gate IG G

R1 U4 U2

U1

R5 S

C6 SJT

Signal RTN

VEE C9 VEE C10 VEE C7

VGL

R3 RG1

VCC High

VGL U3

R4 RG2

+12 V C2 X2 C5 D1

R6

VCC High RTN

VEE C8

VGH

VCC Low

C21 Source

+12 V C1 X1

C4

VCC Low RTN

VEE

Figure 24: Topology of the GA03IDDJT30-FR4 Two Voltage Source gate driver.

The GA15IDDJT22-FR4 evaluation board comes equipped with two on board gate drive resistors (RG1, RG2) pre-installed for an effective

gate resistance of RG = 0.7 Ω. It may be necessary for the user to reduce RG1 and RG2 under high drain current conditions for safe operation

3

of the GA50JT12-247. The steady state current supplied to the gate pin of the GA50JT12-247 with on-board RG = 0.7 Ω, is shown in

Figure 25. The maximum allowable safe value of RG for the user’s required drain current can be read from Figure 26.

For the GA50JT12-247, RG must be reduced for ID ≥ ~60 A for safe operation with the GA15IDDJT22-FR4.

For operation at ID ≥ ~60 A, RG may be calculated from the following equation, which contains the DC current gain hFE (Figure 4) and the gate-

source saturation voltage VGS,sat (Figure 7).

�4.7𝑉𝑉 − 𝑉𝑉𝐺𝐺𝐺𝐺,𝑠𝑠𝑠𝑠𝑠𝑠 � ∗ ℎ𝐹𝐹𝐹𝐹 (𝑇𝑇, 𝐼𝐼𝐷𝐷 )

𝑅𝑅𝐺𝐺,𝑚𝑚𝑚𝑚𝑚𝑚 = − 0.1Ω

𝐼𝐼𝐷𝐷 ∗ 1.5

Dec 2015 Latest version of this datasheet at: http://www.genesicsemi.com/commercial-sic/sic-junction-transistors/ Pg 8 of 11

GA50JT12-247

Figure 25: Typical steady state gate current supplied by the Figure 26: Maximum gate resistance for safe operation of

GA15IDDJT22-FR4 board for the GA50JT12-247 with the on the GA50JT12-247 at different drain currents using the

board resistance of 0.7 Ω GA15IDDJT22-FR4 board.

B:2: High Speed, Low Loss Drive with Boost Inductor

A High Speed, Low-Loss Driver with Boost Inductor is also capable of driving the GA50JT12-247 at high-speed. It utilizes a gate drive inductor

instead of a capacitor to provide the high-current gate current pulses IG,on and IG,off. During operation, inductor L is charged to a specified IG,on

current value then made to discharge IL into the SJT gate pin using logic control of S1, S2, S3, and S4, as shown in Figure 27. After turn on,

while the device remains on the necessary steady state gate current IG,steady is supplied from source VCC through RG. Please refer to the article

“A current-source concept for fast and efficient driving of silicon carbide transistors” by Dr. Jacek Rąbkowski for additional information on this

4

driving topology.

VCC

S1

VCC

S2

L

VEE

S3 SiC SJT D

G

RG

S4 S

VEE

Figure 27: Simplified Inductive Pulsed Drive Topology

3

– RG = (1/RG1 +1/RG2)-1. Driver is pre-installed with RG1 = 2.2 Ω, RG2 = 1.0 Ω

4

– Archives of Electrical Engineering. Volume 62, Issue 2, Pages 333–343, ISSN (Print) 0004-0746, DOI: 10.2478/aee-2013-0026, June 2013

Dec 2015 Latest version of this datasheet at: http://www.genesicsemi.com/commercial-sic/sic-junction-transistors/ Pg 9 of 11

GA50JT12-247

C: Proportional Gate Current Driving

For applications in which the GA50JT12-247 will operate over a wide range of drain current conditions, it may be beneficial to drive the device

using a proportional gate drive topology to optimize gate drive power consumption. A proportional gate driver relies on instantaneous drain

current ID feedback to vary the steady state gate current IG,steady supplied to the GA50JT12-247

C:1: Voltage Controlled Proportional Driver

The voltage controlled proportional driver relies on a gate drive IC to detect the GA50JT12-247 drain-source voltage VDS during on-state to

sense ID. The gate drive IC will then increase or decrease IG,steady in response to ID. This allows IG,steady, and thus the gate drive power

consumption, to be reduced while ID is relatively low or for IG,steady to increase when is ID higher. A high voltage diode connected between the

drain and sense protects the IC from high-voltage when the driver and GA50JT12-247 are in off-state. A simplified version of this topology is

shown in Figure 29, additional information will be available in the future at http://www.genesicsemi.com/commercial-sic/sic-junction-transistors/

HV Diode

Sense

Proportional

Gate Signal Gate Current D

Driver G

Signal Output IG,steady

S

SiC SJT

Figure 28: Simplified Voltage Controlled Proportional Driver

C:2: Current Controlled Proportional Driver

The current controlled proportional driver relies on a low-loss transformer in the drain or source path to provide feedback ID of the GA50JT12-

247 during on-state to supply IG,steady into the device gate. IG,steady will then increase or decrease in response to ID at a fixed forced current gain

which is set be the turns ratio of the transformer, hforce = ID / IG = N2 / N1. GA50JT12-247 is initially tuned-on using a gate current pulse supplied

into an RC drive circuit to allow ID current to begin flowing. This topology allows IG,steady, and thus the gate drive power consumption, to be

reduced while ID is relatively low or for IG,steady to increase when is ID higher. A simplified version of this topology is shown in Figure 29,

additional information will be available in the future at http://www.genesicsemi.com/commercial-sic/sic-junction-transistors/.

N2

Gate Signal

SiC SJT D

G

N3 N1 N2

Figure 29: Simplified Current Controlled Proportional Driver

Dec 2015 Latest version of this datasheet at: http://www.genesicsemi.com/commercial-sic/sic-junction-transistors/ Pg 10 of 11

GA50JT12-247

Section VI: Package Dimensions

TO-247 PACKAGE OUTLINE

(15.748) 0.55 (13.97)

(4.318 REF.) 0.170 REF. 0.171 (4.699)

(16.256) 0.236 0.054 0.045

(5.486) 0.216 0.208 (5.283)

0.620 (5.99) (1.36) (1.14)

0.640

0.059 (1.498)

0.098 (2.489)

0.242 BSC. 0.22

(6.147 BSC.) (5.59) 0.012

(0.3)

0.819

0.844 0.652

(20.803) Ø 0.140 (3.556) (16.56)

(21.438) Ø 0.118 (3.00) 0.143 (3.632)

Ø 0.283 (7.19)

GA50JT12-247

XXXXXX

Lot code

0.177

0.780 MAX

0.800 (4.496)

(19.812)

(20.320)

0.065 (1.651)

0.083 (2.108)

0.016 (0.406)

0.040 (1.016) 0.031 (0.787) 0.075 (1.905)

0.055 (1.397) 0.2146 (5.451) BSC.

0.115 (2.921)

NOTE

1. CONTROLLED DIMENSION IS INCH. DIMENSION IN BRACKET IS MILLIMETER.

2. DIMENSIONS DO NOT INCLUDE END FLASH, MOLD FLASH, MATERIAL PROTRUSIONS

Revision History

Date Revision Comments Supersedes

2015/12/07 4 Updated Electrical Characteristics

2015/01/29 3 Updated Electrical Characteristics

2014/12/18 2 Updated Electrical Characteristics

2014/11/12 1 Updated Electrical Characteristics

2014/08/25 0 Initial release

Published by

GeneSiC Semiconductor, Inc.

43670 Trade Center Place Suite 155

Dulles, VA 20166

GeneSiC Semiconductor, Inc. reserves right to make changes to the product specifications and data in this document without notice.

GeneSiC disclaims all and any warranty and liability arising out of use or application of any product. No license, express or implied to any

intellectual property rights is granted by this document.

Unless otherwise expressly indicated, GeneSiC products are not designed, tested or authorized for use in life-saving, medical, aircraft

navigation, communication, air traffic control and weapons systems, nor in applications where their failure may result in death, personal

injury and/or property damage.

Dec 2015 Latest version of this datasheet at: http://www.genesicsemi.com/commercial-sic/sic-junction-transistors/ Pg 11 of 11

GA50JT12-247

Section VII: SPICE Model Parameters

This is a secure document. Please copy this code from the SPICE model PDF file on our website

(http://www.genesicsemi.com/images/products_sic/sjt/GA50JT12-247_SPICE.pdf) into LTSPICE

(version 4) software for simulation of the GA50JT12-247.

* MODEL OF GeneSiC Semiconductor Inc.

*

* $Revision: 3.0 $

* $Date: 07-DEC-2015 $

*

* GeneSiC Semiconductor Inc.

* 43670 Trade Center Place Ste. 155

* Dulles, VA 20166

*

* COPYRIGHT (C) 2015 GeneSiC Semiconductor Inc.

* ALL RIGHTS RESERVED

*

* These models are provided "AS IS, WHERE IS, AND WITH NO WARRANTY

* OF ANY KIND EITHER EXPRESSED OR IMPLIED, INCLUDING BUT NOT LIMITED

* TO ANY IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A

* PARTICULAR PURPOSE."

* Models accurate up to 2 times rated drain current.

*

.model GA50JT12 NPN

+ IS 9.833E-48

+ ISE 1.073E-26

+ EG 3.23

+ BF 89

+ BR 0.55

+ IKF 9000

+ NF 1

+ NE 2

+ RB 0.95

+ IRB 0.005

+ RBM 0.073

+ RE 0.004

+ RC 0.0125

+ CJC 2.124E-9

+ VJC 3.788

+ MJC 0.537

+ CJE 6.026E-09

+ VJE 3.1791

+ MJE 0.5295

+ XTI 3

+ XTB -1.5

+ TRC1 9.00E-3

+ VCEO 1200

+ ICRATING 50

+ MFG GeneSiC_Semiconductor

*

* End of GA50JT12 SPICE Model

Dec 2015 Latest version of this datasheet at: http://www.genesicsemi.com/commercial-sic/sic-junction-transistors/ Pg 1 of 1

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5820)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (898)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Java NC II Grade 11Document18 pagesJava NC II Grade 11Ronald Pacquiao Macasero50% (2)

- IRGR4045DPBFDocument11 pagesIRGR4045DPBFRaduNo ratings yet

- Afgy120t65spd B4Document11 pagesAfgy120t65spd B4RaduNo ratings yet

- Ixgx320n60b3 320a 600VDocument7 pagesIxgx320n60b3 320a 600VRaduNo ratings yet

- FGH40T65SHDF 1,45VDocument10 pagesFGH40T65SHDF 1,45VRaduNo ratings yet

- Ixgp48n60a3 To220 48a 1,3VDocument7 pagesIxgp48n60a3 To220 48a 1,3VRaduNo ratings yet

- Afghl75t65sqdc Gen4 SicDocument10 pagesAfghl75t65sqdc Gen4 SicRaduNo ratings yet

- Afghl50t65sqdc 650v 50a 1,6v SicDocument11 pagesAfghl50t65sqdc 650v 50a 1,6v SicRaduNo ratings yet

- AOK40B65H2ALDocument14 pagesAOK40B65H2ALRaduNo ratings yet

- Ikw75n60t TeslaDocument14 pagesIkw75n60t TeslaRaduNo ratings yet

- BC817Document7 pagesBC817RaduNo ratings yet

- Fgy120t65spd F085Document12 pagesFgy120t65spd F085RaduNo ratings yet

- FGH40T65SPDDocument9 pagesFGH40T65SPDRaduNo ratings yet

- Apt150gn60j Sot-227Document6 pagesApt150gn60j Sot-227RaduNo ratings yet

- IRGB30B60KPBFDocument14 pagesIRGB30B60KPBFRaduNo ratings yet

- MJL3281ADocument7 pagesMJL3281ARaduNo ratings yet

- MJW21195 MJW21196 Audio 250V 16A 200WDocument10 pagesMJW21195 MJW21196 Audio 250V 16A 200WRaduNo ratings yet

- Tip142t Tip147tDocument5 pagesTip142t Tip147tRaduNo ratings yet

- NJL3281D NJL1302D 260V 15A 200W DiodaDocument9 pagesNJL3281D NJL1302D 260V 15A 200W DiodaRaduNo ratings yet

- MCH6541 Dual 700ma 30V 500MhzDocument9 pagesMCH6541 Dual 700ma 30V 500MhzRaduNo ratings yet

- MJW3281A Audio Amplif 100WDocument9 pagesMJW3281A Audio Amplif 100WRaduNo ratings yet

- Mmpq6700 Quad BJTDocument7 pagesMmpq6700 Quad BJTRaduNo ratings yet

- Semiconductor KTD2499: Technical DataDocument2 pagesSemiconductor KTD2499: Technical DataRaduNo ratings yet

- NJW0281 NJW0302 Audio 250V 15A 150WDocument6 pagesNJW0281 NJW0302 Audio 250V 15A 150WRaduNo ratings yet

- MJW21193 MJW21194 Audio 250V 16A 200WDocument7 pagesMJW21193 MJW21194 Audio 250V 16A 200WRaduNo ratings yet

- KSD1691Document8 pagesKSD1691RaduNo ratings yet

- Datasheet PDFDocument4 pagesDatasheet PDFRichard MachadoNo ratings yet

- Capstone Paper (Rough Draft)Document15 pagesCapstone Paper (Rough Draft)lewis_kellerNo ratings yet

- Fullstack Developer GuideDocument111 pagesFullstack Developer GuideHABIB AL HASAN HIMELNo ratings yet

- Network Models: 4.0 ObjectivesDocument16 pagesNetwork Models: 4.0 ObjectivesMohammed SamiNo ratings yet

- C1815, NPN TransistorDocument2 pagesC1815, NPN Transistorabcx769No ratings yet

- SharcDocument20 pagesSharcSirisha KurakulaNo ratings yet

- UML 2: Additional Diagram Types: Object DiagramsDocument0 pagesUML 2: Additional Diagram Types: Object DiagramsJuan Miguel Gómez PalaciánNo ratings yet

- Synopsis - On Line ReminderDocument10 pagesSynopsis - On Line ReminderNitin Yadav100% (1)

- 68HC05H12 MotorolaDocument196 pages68HC05H12 MotorolaHebertAlexMamaniSalomaNo ratings yet

- Abap SystemsDocument28 pagesAbap SystemsneoNo ratings yet

- 2050xe Prod BrochureDocument2 pages2050xe Prod BrochureHossein ttNo ratings yet

- Expand Your Netapp Hci SystemDocument13 pagesExpand Your Netapp Hci SystemSalyo DrajatNo ratings yet

- Vmware Vsphere Networking: Nutanix Best PracticesDocument37 pagesVmware Vsphere Networking: Nutanix Best PracticesDavid Hernan Lira CarabantesNo ratings yet

- Image Upload Delete UpdateDocument5 pagesImage Upload Delete UpdateArvind KumarNo ratings yet

- Informatica PowerCenter Connect 8.1.1 For SAP NetWeaver User GuideDocument452 pagesInformatica PowerCenter Connect 8.1.1 For SAP NetWeaver User GuideDipankarNo ratings yet

- NO.1 A. B. C. D. E.: AnswerDocument4 pagesNO.1 A. B. C. D. E.: AnswerGourab BanikNo ratings yet

- Module 2 - Lecture 3 - Network Configuration - LAN SetupDocument28 pagesModule 2 - Lecture 3 - Network Configuration - LAN SetupZeeshan BhattiNo ratings yet

- Intel Case AnalysisDocument3 pagesIntel Case AnalysisRhea RejithNo ratings yet

- ModqnbnkDocument1 pageModqnbnkSanjay KumarNo ratings yet

- Indicate Whether The Sentence or Statement Is True or FalseDocument2 pagesIndicate Whether The Sentence or Statement Is True or FalsepbonakNo ratings yet

- AutoCAD Electrical 2017 IEC Symbols Guide-Miles NicholsonDocument58 pagesAutoCAD Electrical 2017 IEC Symbols Guide-Miles NicholsonTeto ScheduleNo ratings yet

- Assembly Language & CracksDocument9 pagesAssembly Language & CracksAna Ventura100% (1)

- Net E-Business ArchitectureDocument463 pagesNet E-Business Architecturedharbab100% (1)

- A Flexible X-Haul Network For 5G and Beyond: Jörg-Peter Elbers and Jim ZouDocument21 pagesA Flexible X-Haul Network For 5G and Beyond: Jörg-Peter Elbers and Jim ZouALEXANDRE JOSE FIGUEIREDO LOUREIRONo ratings yet

- Acer Travelmate 6410to 6460 User ManualDocument122 pagesAcer Travelmate 6410to 6460 User Manualsmudger1973No ratings yet

- LK110 Instruction Manual: High Speed 0.02s Delay Precise Positioning Bracket Fixed Free InstallationDocument9 pagesLK110 Instruction Manual: High Speed 0.02s Delay Precise Positioning Bracket Fixed Free InstallationDJ YaNoMiNo ratings yet

- Technical Overview 05 - ECEDocument33 pagesTechnical Overview 05 - ECETatiane RodriguesNo ratings yet

- B-64120en 02 070508Document462 pagesB-64120en 02 070508Reiko SakurakoNo ratings yet

- Siebel System Administration Guide 8.2 PDFDocument298 pagesSiebel System Administration Guide 8.2 PDFGouthambojja143No ratings yet

- 004 - Hadoop Daemons (HDFS Only)Document3 pages004 - Hadoop Daemons (HDFS Only)Srinivas ReddyNo ratings yet