Professional Documents

Culture Documents

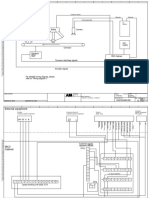

ARM Cortex-A57 Block Diagram

ARM Cortex-A57 Block Diagram

Uploaded by

文帅宋Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ARM Cortex-A57 Block Diagram

ARM Cortex-A57 Block Diagram

Uploaded by

文帅宋Copyright:

Available Formats

ARM Cortex-A57 Block Diagram

Non-Processor Cortex-A57 Processor Core

/Level 2

Coherency Port

Slave

L1 Instruction Cache Branch Prediction

Accelerator ITLB 48KB

(ACP)

(3-way set-associative Bi-mode Predictor

/64-Byte cache line/Parity)

5 Stages

Indirect Predictor

w/path history

Snoop

128 bits Global History Buffer

MicroBTB (64-entry)

Instruction Fetch Branch Target Buffer

Extensions (ACE)

(BTB)(2k-4k)

Master

AXI Coherency

Return Stack

12 Stage

Processor Arbitration (1ST Level)

In-Order

Pipeline

3-way Instruction Decode

7 Stages

Fill/Evict

Buffer

L2 Arbitration

(512-entry)

L2 TLB

32-entry Register Rename

Loop Buffer Virtual to Physical Register Pool

(16-way set-associative

Shared L2 Cache

512KB/1MB/2MB

CP14/CP15

1 Stage

Registers Dispatch States

Commit

TAG RAM TAG RAM

Register Files Issue (8-entry Queue per Issue port)

ECC)

Snoop

Up to 8 micro-ops Issue

1 Stage

Load/Store

Load/Store

Divide Cluster

Multiply,MAC

Complex Cluster (NEON/FPU)

Complex Cluster (NEON/FPU)

Branch

Cluster 1

Simple

Cluster 0

Simple

L2

4 Stages

4 Stages

Load-Store Unit

Prefetch

Engine

Store Buffer

2-10 Stages

3-12 Stage

1 Load & ARM Integer ALU & Out-of-Order

1 Store multiply & Shifter Pipeline

Load TLB L1 Data Cache per cycle Integer (includes v6-

(32-entry)

32KB ECC divide, SIMD)

Store TLB (2-way set-associative MAC

(32-entry) /64-byte cache line)

All NEON & FPU ops

48-bit Virtual Address QUad-FMAC

44-bit Physical Address

1 Stage

WriteBack

128 micro-ops in-flight Retirement Buffer

Copyright (c) 2013 Hiroshige Goto All rights reserved.

You might also like

- Digital Modulations using MatlabFrom EverandDigital Modulations using MatlabRating: 4 out of 5 stars4/5 (6)

- Winidea Build 9.17.172.0.109652 Test Report: Renesas Rh850Document2 pagesWinidea Build 9.17.172.0.109652 Test Report: Renesas Rh850mohammedNo ratings yet

- Arduino Cheat SheetDocument1 pageArduino Cheat SheetMC. Rene Solis R.100% (9)

- Revision BIOS Tweaking GuideDocument6 pagesRevision BIOS Tweaking GuideHeroLanderNo ratings yet

- Riso Ez 220 Service ManualDocument4 pagesRiso Ez 220 Service ManualMensah bonsu100% (2)

- ARM Cortex-A72 Block DiagramDocument1 pageARM Cortex-A72 Block Diagram文帅宋No ratings yet

- ARM Cortex-A76 Block DiagramDocument1 pageARM Cortex-A76 Block Diagram文帅宋No ratings yet

- ARM Cortex-A7 Core Block DiagramDocument1 pageARM Cortex-A7 Core Block Diagram文帅宋No ratings yet

- MPC7448 RISC Microprocessor Hardware Specifications: Freescale SemiconductorDocument60 pagesMPC7448 RISC Microprocessor Hardware Specifications: Freescale SemiconductorMurat GörükmezNo ratings yet

- TSL1401Document8 pagesTSL1401Chế ThiệnNo ratings yet

- KKDocument2 pagesKKzbhp zNo ratings yet

- 10gbps Po Lab TM Ae 01Document1 page10gbps Po Lab TM Ae 01Pham Thanh doNo ratings yet

- Spare Items BOM - Per SSDocument1 pageSpare Items BOM - Per SSTarek KhafagaNo ratings yet

- ACA Iitg Sahu Lec17Document4 pagesACA Iitg Sahu Lec17tamil_delhiNo ratings yet

- MPS DatasheetDocument2 pagesMPS DatasheetrajendrasoloniNo ratings yet

- Platform NodeDocument5 pagesPlatform NodeCaraka TriNo ratings yet

- NECMicrocontroller GuideDocument8 pagesNECMicrocontroller GuideAldemir Fernando BattagliaNo ratings yet

- University of Bristol MicroarchitectureDocument10 pagesUniversity of Bristol Microarchitecturehungck4567No ratings yet

- Main Items BOQ Per SS: 4. Ethernet Switch 1. Control Panel & Panel Accessories 2. RTU System 5. Maintenance ToolsDocument1 pageMain Items BOQ Per SS: 4. Ethernet Switch 1. Control Panel & Panel Accessories 2. RTU System 5. Maintenance ToolsTarek KhafagaNo ratings yet

- Aws Backup (Per 15 Minute) : Reverse FeedDocument1 pageAws Backup (Per 15 Minute) : Reverse FeedsiyakinNo ratings yet

- Evolution of Next-Generation Networks: SONET/SDH Meets Data Generic Framing Procedure (GFP)Document1 pageEvolution of Next-Generation Networks: SONET/SDH Meets Data Generic Framing Procedure (GFP)Djnsilva SilvaNo ratings yet

- MCC Iitg Sahu MPLec12Document4 pagesMCC Iitg Sahu MPLec12tamil_delhiNo ratings yet

- TIO Console: Stationary GantryDocument1 pageTIO Console: Stationary Gantryjairo castroNo ratings yet

- LPC9221 NXPDocument8 pagesLPC9221 NXPRicardo FantiniNo ratings yet

- Mpu Brochure 60001434 DDocument8 pagesMpu Brochure 60001434 DAbolfazl SaeedieNo ratings yet

- Front-End IC For INO ICAL DetectorDocument32 pagesFront-End IC For INO ICAL DetectorMohan RamNo ratings yet

- Cellular LineCard (UBX-13004714)Document4 pagesCellular LineCard (UBX-13004714)far.rhm2021No ratings yet

- QUBE-Servo Direct IO Quick Start GuideDocument4 pagesQUBE-Servo Direct IO Quick Start GuidealfredokpuNo ratings yet

- SCX-6345N XET SM EN 20070130090204078 08-Blockdiagram PDFDocument3 pagesSCX-6345N XET SM EN 20070130090204078 08-Blockdiagram PDFSoraphong NaknoppakoonNo ratings yet

- JavaMindMap 1Document1 pageJavaMindMap 1corona indiaNo ratings yet

- BLE Module Survey Filled PDFDocument1 pageBLE Module Survey Filled PDFfdsfsdfrgeNo ratings yet

- EL-Souab Al-Zerayaa 220-22-22KV-Arch Rev-B1Document2 pagesEL-Souab Al-Zerayaa 220-22-22KV-Arch Rev-B1Bader AhmedNo ratings yet

- MCU KornilinDocument51 pagesMCU KornilinMaría SpínolaNo ratings yet

- Learning Material - Painting RobotDocument43 pagesLearning Material - Painting RobotAlif PrayogaNo ratings yet

- BLE Module Selection Guide: Electronic ProductsDocument1 pageBLE Module Selection Guide: Electronic ProductsfdsfsdfrgeNo ratings yet

- Intel Core ComparsionDocument7 pagesIntel Core ComparsionFrancis PaloNo ratings yet

- JDSU Poster SDH Nextgen - Networks PDFDocument1 pageJDSU Poster SDH Nextgen - Networks PDFHoracio Betancourt Ruiz100% (2)

- Catalyst Makes It HappenDocument7 pagesCatalyst Makes It Happenwaikok jeffreyNo ratings yet

- FALLSEM2023-24 CSE2006 ETH VL2023240104104 2023-07-28 Reference-Material-IDocument22 pagesFALLSEM2023-24 CSE2006 ETH VL2023240104104 2023-07-28 Reference-Material-IFrankoNo ratings yet

- Modbus Register EL9000BHP KE2.29+ ENDocument1 pageModbus Register EL9000BHP KE2.29+ ENpushkarNo ratings yet

- Arduino CheatsheetDocument1 pageArduino Cheatsheetapi-408461912No ratings yet

- Diagrama Eléctrico Tractor D4GDocument4 pagesDiagrama Eléctrico Tractor D4GRimbertNo ratings yet

- OSPL 01 Exercise 3 - en - 2023Document8 pagesOSPL 01 Exercise 3 - en - 2023Guowei LanNo ratings yet

- AVR MCU Comparison Table (Mega & ATTiny) PDFDocument2 pagesAVR MCU Comparison Table (Mega & ATTiny) PDFit emmNo ratings yet

- JM20337 JMicronDocument2 pagesJM20337 JMicronRuben Perez AyoNo ratings yet

- 002-26642 CYW20721 Enhanced Low Power BR EDR BLE Bluetooth 5.0 SOC For AudioDocument48 pages002-26642 CYW20721 Enhanced Low Power BR EDR BLE Bluetooth 5.0 SOC For AudioKkNo ratings yet

- VolteDocument1 pageVoltemohamed100% (1)

- 1 Overview: STC8A8K64S4A12 Series ManualDocument18 pages1 Overview: STC8A8K64S4A12 Series Manualhossein gholamiNo ratings yet

- EJEMPLO 3HAC024480-008 - Rev02Document10 pagesEJEMPLO 3HAC024480-008 - Rev02ipmcmtyNo ratings yet

- ARM Cortex-A12 Block DiagramDocument1 pageARM Cortex-A12 Block Diagram文帅宋No ratings yet

- Jambaran Tiung Biru Project: Electrical Power and Control Cable Schedule - Substation No. 1Document2 pagesJambaran Tiung Biru Project: Electrical Power and Control Cable Schedule - Substation No. 1Alif AnsharNo ratings yet

- (TeamCast) Introduction To The Universal T2 CalculatorDocument4 pages(TeamCast) Introduction To The Universal T2 CalculatorWilson OrtizNo ratings yet

- 6020 SchematicsDocument10 pages6020 SchematicsGak TahuNo ratings yet

- Bm94715eku RohmDocument27 pagesBm94715eku Rohmdaniel SNo ratings yet

- Fast Firewall Linux EbpfDocument3 pagesFast Firewall Linux Ebpfal teNo ratings yet

- Confidential: Only For Training and Service PurposesDocument11 pagesConfidential: Only For Training and Service Purposesanh_sao_dem_92No ratings yet

- 30 Urban CruiserDocument1 page30 Urban CruiserHEMIL ROBERTO RODRIGUEZ HERRERANo ratings yet

- Versatile Routing and Services with BGP: Understanding and Implementing BGP in SR-OSFrom EverandVersatile Routing and Services with BGP: Understanding and Implementing BGP in SR-OSNo ratings yet

- Scanline Rendering: Exploring Visual Realism Through Scanline Rendering TechniquesFrom EverandScanline Rendering: Exploring Visual Realism Through Scanline Rendering TechniquesNo ratings yet

- Using the Standards - Number & Operations, Grade 8From EverandUsing the Standards - Number & Operations, Grade 8No ratings yet

- ARM Cortex-A76 Block DiagramDocument1 pageARM Cortex-A76 Block Diagram文帅宋No ratings yet

- ARM Cortex-A72 Block DiagramDocument1 pageARM Cortex-A72 Block Diagram文帅宋No ratings yet

- ARM Cortex-A7 Core Block DiagramDocument1 pageARM Cortex-A7 Core Block Diagram文帅宋No ratings yet

- ARM Cortex-A12 Block DiagramDocument1 pageARM Cortex-A12 Block Diagram文帅宋No ratings yet

- DIY NAS: 2014 Edition: Brian's Blog Blog Archives About MeDocument5 pagesDIY NAS: 2014 Edition: Brian's Blog Blog Archives About MePradeep Kumar Chandra SekarNo ratings yet

- STM32 Value LineDocument3 pagesSTM32 Value LineMihir MandsorwaleNo ratings yet

- LaptopDocument20 pagesLaptopNeeraj SinghNo ratings yet

- Computer Architecture MCQDocument8 pagesComputer Architecture MCQVishal ThakurNo ratings yet

- Acer Altos G310 - ServiceManDocument113 pagesAcer Altos G310 - ServiceManJonathan LongNo ratings yet

- LaptopDocument25 pagesLaptopPankaj AdhagaleNo ratings yet

- Gfk0265j CPU Instruction SetDocument521 pagesGfk0265j CPU Instruction SetIman TriwahyudiNo ratings yet

- ICT Lecture NoteDocument26 pagesICT Lecture NoteAbduletif Hebo0% (1)

- Lab Manual: Submmitted byDocument70 pagesLab Manual: Submmitted byMuhammad owais Muhammad munirNo ratings yet

- A Comparative Study of Different Printed Documents PDFDocument7 pagesA Comparative Study of Different Printed Documents PDFsandeep yadavNo ratings yet

- Iradv65xx Code ArticleDocument1 pageIradv65xx Code ArticleTony ChangNo ratings yet

- C++ PresentationDocument43 pagesC++ PresentationyaniyansoproNo ratings yet

- 2550CDTDocument2 pages2550CDTYangNo ratings yet

- RAID LevelsDocument10 pagesRAID LevelsJon SmithNo ratings yet

- Digital Equipment Corporation: Thomas J. Bergin ©computer History Museum American UniversityDocument32 pagesDigital Equipment Corporation: Thomas J. Bergin ©computer History Museum American UniversityRajesh KumarNo ratings yet

- Hard Disk Controller (HDC)Document5 pagesHard Disk Controller (HDC)Boobalan R100% (1)

- Using Cash Drawers - Version 4 - V4 Tutorial - SambaClub ForumDocument10 pagesUsing Cash Drawers - Version 4 - V4 Tutorial - SambaClub ForumFaiez LeeNo ratings yet

- 1065 Ion Chromatography PDFDocument1 page1065 Ion Chromatography PDFEki MegaraniNo ratings yet

- Targus ACP70AU - Quick Start GuideDocument2 pagesTargus ACP70AU - Quick Start GuideRenardNo ratings yet

- BIOSDocument11 pagesBIOSnitinhandaNo ratings yet

- Biod UpdateDocument5 pagesBiod UpdateGerry DamsikiNo ratings yet

- Fundamentals of Computer Hardware NotesDocument7 pagesFundamentals of Computer Hardware NotesSreemoyee RoyNo ratings yet

- Poweredge r960 Spec SheetDocument3 pagesPoweredge r960 Spec SheetRicardo PerezNo ratings yet

- Chap 3 - Hardware and SoftwareDocument47 pagesChap 3 - Hardware and SoftwareMoses ZasoNo ratings yet

- KW Úduvi Nvw©Iq Vi: Computer HardwareDocument18 pagesKW Úduvi Nvw©Iq Vi: Computer HardwareScientia Online CareNo ratings yet

- 2 (Types of Operating System)Document43 pages2 (Types of Operating System)dharmendra kumarNo ratings yet

- Sindoh D330 and D332 A3 Colour MFP'sDocument2 pagesSindoh D330 and D332 A3 Colour MFP'sbloodkhantalNo ratings yet

- CHENBRO. 12-Port 3.5 Mini-Sas Backplane With Expander 80H A0. User S Manual. December - 2010Document14 pagesCHENBRO. 12-Port 3.5 Mini-Sas Backplane With Expander 80H A0. User S Manual. December - 2010wschonellNo ratings yet