Professional Documents

Culture Documents

0 ratings0% found this document useful (0 votes)

5 viewsVlsi Port

Vlsi Port

Uploaded by

Darshan AherCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5834)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (350)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (824)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (405)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- EM May 2022Document3 pagesEM May 2022Darshan AherNo ratings yet

- SATCOM Dec 2022Document2 pagesSATCOM Dec 2022Darshan AherNo ratings yet

- OCN Dec 2019Document1 pageOCN Dec 2019Darshan AherNo ratings yet

- OCN May 2019Document1 pageOCN May 2019Darshan AherNo ratings yet

- SATCOM May 2023Document1 pageSATCOM May 2023Darshan AherNo ratings yet

- Practical 4 Wireshark EXTC 4Document8 pagesPractical 4 Wireshark EXTC 4Darshan AherNo ratings yet

- Practical 1 Crimping An RJ45 Plug On Cat6 Cable EXTC 1Document13 pagesPractical 1 Crimping An RJ45 Plug On Cat6 Cable EXTC 1Darshan AherNo ratings yet

- SATCOM Dec 2019Document1 pageSATCOM Dec 2019Darshan AherNo ratings yet

- Practical 3 Static Routing EXTC 3Document23 pagesPractical 3 Static Routing EXTC 3Darshan AherNo ratings yet

- Practical 5 EXTC PT OSPF RIPDocument21 pagesPractical 5 EXTC PT OSPF RIPDarshan AherNo ratings yet

- Practical 2 Netowrking Commands EXTC 2Document14 pagesPractical 2 Netowrking Commands EXTC 2Darshan AherNo ratings yet

- Dvlsi Easy SolutionDocument42 pagesDvlsi Easy SolutionDarshan AherNo ratings yet

- Be Electronics and Telecommunication Semester 4 2022 May Principles of Communication Engineeringrev 2019 C SchemeDocument3 pagesBe Electronics and Telecommunication Semester 4 2022 May Principles of Communication Engineeringrev 2019 C SchemeDarshan AherNo ratings yet

- Performance Evaluation of Carbon NanotubDocument45 pagesPerformance Evaluation of Carbon NanotubDarshan AherNo ratings yet

Vlsi Port

Vlsi Port

Uploaded by

Darshan Aher0 ratings0% found this document useful (0 votes)

5 views3 pagesOriginal Title

VLSI PORT

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

Download as pdf

0 ratings0% found this document useful (0 votes)

5 views3 pagesVlsi Port

Vlsi Port

Uploaded by

Darshan AherCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

Download as pdf

You are on page 1of 3

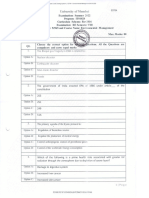

Course | Course Name Teaching Scheme Credits Assigned

Code (Contact Hours)

Theory | Practical | Tutorial | Theory | Practical | Tutorial | Total

ECC503_[ Digital VEST B = = 08 = = 03

Course | Course Examination Scheme

Code | Name Theory Marks Exam | Term | Practical | Total

Internal Assessment End Sem, | Duration | Work | and Oral

stl | Test2 | Avg. Exam. (Hrs.)

ECCS03_| Digital

VLSI 20 | 20 | 2 80 03 - - 100

Course Pre-requisite:

ECC302 — Electronic Devices and Circuits

ECC303 — Digital System Design

ECC403 — Linear Integrated Circuits

Course Objectives:

1, To introduce process flow of VLSI Design.

2, To understand MOSFET operation from VLSI design perspective.

3. To learn VLSI design performance metric and various tradeoffs.

4. To design, implement and verify combinational and sequential logic circuits using various MOS design styles.

5. To provides an exposure to RTL design and programming

Course Outcomes:

After successful completion of the course student will be able to:

Know vario s used in VLSI De

s tools and proc

ign

Relate performance parameters with design parameters of VLST circuits

Select suitable circuit and design style for given application

Design and realize various combinational and sequential circuits for given specifications.

PaRENa

Explain working of various CMOS combinational and sequential circuits used in VLSI Design.

Derive expressions for performance parameters of basic building blocks like CMOS inverter,

University of Mumbai-R2019-C-Scheme-TY Electronics and Telecommunication Engineering

Page 16 of 101

Module | Unit

Ne | Na Topics Hrs.

rn Review of MOSFET operation and Fabrication a

1 | Overview of VLSI Design Flow, Review of MOSFET operation, MOSFET | 4,

"T | Capacitances, MOSFET scaling, Short channel effects °

1.2 | Fabrication process flow of NMOS and CMOS, Lambda based design rules 03

13. | Novel MOSFET Architectures FinFET, GAA-FET, CNTFET 02

20 Combinational CMOS Logic Circuits 06

CMOS inverter operation, Voltage Transfer characteristics (VTC), Noise Margins,

2.1 | Propagation Delay, Power Dissipation, Design of CMOS Inverter, Layout of CMOS | 03

Inverter

Realization of CMOS NAND gate, NOR gate, Complex CMOS Logie Circuits,

Layout of CMOS NAND, NOR and complex CMOS circuits

22

3.0 ‘MOS Design Logie Styles 09

Static CMOS, Pass Transistor Logic, Transmission Gate, Pseudo NMOS, Dynamic

3.1 | Logic, Domino Logic, NORA, Zipper, CMOS 04

Setup time, Hold time, clocked CMOS SR Latch, CMOS IK Latch, MS—JK Flip Flop, | 93

32

Edge triggered D-Flip Flop and realization using design sty

Realization of Shift Register, MUX, Decoder using above design styles ,1-bit full

33 | adder 02

40 ‘Semiconductor Memories 06

41 | ROM array, 6T-SRAM (operation, design strategy, leakage currents, sense amplifier), | 4,

+I | layout of SRAM °

4.2 | Operation of IT and 3T DRAM Cell, NAND and NOR flash memory 03

50 Data path and system design issues 06

Ripple cary adder, CLA adder, carry save adder, carry select adder, carry skip adder,

SI 04

Array Multiplier

On chip clock generation and distribution, Interconnect delay model, interconnect

82 0

scaling and crosstalk

60 RTL Design 04

6.1 | High Level state machines, RTL design process o

6.2. | RTL design of Soda dispenser machine, FIR Filter o

Total | 39

University of Mumbai-R2019-C-Scheme-TY Electronics and Telecommunication Engineering Page 17 of 101

‘Text Books:

1, Sung-Mo Kang and Yusuf Leblebici, “CMOS Digital Integrated Circuits Analysis and

Design”, Tata McGraw Hill, 31d Edition, 2012.

2. Jan M. Rabaey, Anantha Chandrakasan and Borivoje Nikolic, “Digital Integrated

Circuits: A Design Perspective”, Pearson Education, 2nd Edition.

3. Frank Vahid, “Digital Design with RTL design, VHDL and VERILOG”, John Wiley

and Sons Publisher 2011

Reference Books:

1. Neil H. E. Weste, David Harris and Ayan Banerjee, CMOS VLSI Design: A Circuits

and Systems Perspectivel, Pearson Education, 3rd Edition

2. John P. Uyemura, “Introduction to VLSI Circuits and Systems”, Wiley, Student Edition,

2013.

3. R. Jacob Baker, “CMOS Circuit Design, Layout and Simulation”, Wiley, 2nd Edition,

2013

NPTEL/ Swayam Course:

4. https://nptel.ac.in/courses/117/101/117101058/

2. https://nptel.ac.in/courses/108/107/1 08107129)

Taternal Assessment (20-Marks):

Internal Ass

sment (IA) consists of two class tests of 20 marks each. 1A-1 is to be conducted

on completion of approximately 40% of the syllabus and IA-2 will be based on remaining

contents (approximately 40% syllabus but excluding contents covered in TA-I). Duration of

cach test shall be one hour, Average of the two tests will be considered as [A marks.

End Semester Examination (80-Marks):

Weightage to each of the modules in end-semester examination will be proportional to

number of respective lecture hours mentioned in the curriculum.

1. Question paper will comprise of total 06 questions, each carrying 20 marks.

2. Question No: 01 will be compulsory and based on entire syllabus wherein 4 to 5 sub-

questions will be asked,

3. Remaining questions will be mixed in nature and randomly selected from all the modules.

4, Weightage of each module will be proportional to number of respective lecture hours as

mentioned in the syllabus.

5. Total 04 questions need to be solved.

University of Mumbai-R2019-C-Scheme-TY Electronics and Telecommunication Engineering Page 18 of 101

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5834)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (350)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (824)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (405)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- EM May 2022Document3 pagesEM May 2022Darshan AherNo ratings yet

- SATCOM Dec 2022Document2 pagesSATCOM Dec 2022Darshan AherNo ratings yet

- OCN Dec 2019Document1 pageOCN Dec 2019Darshan AherNo ratings yet

- OCN May 2019Document1 pageOCN May 2019Darshan AherNo ratings yet

- SATCOM May 2023Document1 pageSATCOM May 2023Darshan AherNo ratings yet

- Practical 4 Wireshark EXTC 4Document8 pagesPractical 4 Wireshark EXTC 4Darshan AherNo ratings yet

- Practical 1 Crimping An RJ45 Plug On Cat6 Cable EXTC 1Document13 pagesPractical 1 Crimping An RJ45 Plug On Cat6 Cable EXTC 1Darshan AherNo ratings yet

- SATCOM Dec 2019Document1 pageSATCOM Dec 2019Darshan AherNo ratings yet

- Practical 3 Static Routing EXTC 3Document23 pagesPractical 3 Static Routing EXTC 3Darshan AherNo ratings yet

- Practical 5 EXTC PT OSPF RIPDocument21 pagesPractical 5 EXTC PT OSPF RIPDarshan AherNo ratings yet

- Practical 2 Netowrking Commands EXTC 2Document14 pagesPractical 2 Netowrking Commands EXTC 2Darshan AherNo ratings yet

- Dvlsi Easy SolutionDocument42 pagesDvlsi Easy SolutionDarshan AherNo ratings yet

- Be Electronics and Telecommunication Semester 4 2022 May Principles of Communication Engineeringrev 2019 C SchemeDocument3 pagesBe Electronics and Telecommunication Semester 4 2022 May Principles of Communication Engineeringrev 2019 C SchemeDarshan AherNo ratings yet

- Performance Evaluation of Carbon NanotubDocument45 pagesPerformance Evaluation of Carbon NanotubDarshan AherNo ratings yet