Professional Documents

Culture Documents

5DigitalTechniquesDTE 17333

5DigitalTechniquesDTE 17333

Uploaded by

Hitesh PatilCopyright:

Available Formats

You might also like

- DEC4000 Operation ManualDocument158 pagesDEC4000 Operation Manualthanhckctm100% (16)

- Ieee C37.20.1-1987Document36 pagesIeee C37.20.1-1987Febry Aryanto100% (1)

- Piezo Preamp and Buffer ReportDocument28 pagesPiezo Preamp and Buffer Reportsbrennan970100% (2)

- Technica Main TL Manual Sample TTDocument23 pagesTechnica Main TL Manual Sample TTpthakur234No ratings yet

- DE - KOE 039 - Question BankDocument6 pagesDE - KOE 039 - Question Bankyash vatsNo ratings yet

- 21 - 2010 - Nov - R09 - STLDDocument8 pages21 - 2010 - Nov - R09 - STLDvasuvlsiNo ratings yet

- Elec1041y 1 2007 2 PDFDocument7 pagesElec1041y 1 2007 2 PDFchetsNo ratings yet

- CS 2202 - Digital Principles and Systems DesignDocument3 pagesCS 2202 - Digital Principles and Systems DesignDhilip PrabakaranNo ratings yet

- 3CS3 04 PDFDocument3 pages3CS3 04 PDFprashantvlsiNo ratings yet

- 21 - 2011 - Dec - R09 - STLDDocument8 pages21 - 2011 - Dec - R09 - STLDvasuvlsiNo ratings yet

- EC8392-Digital EletronicsDocument2 pagesEC8392-Digital Eletronicssyed1188No ratings yet

- Subject: Applied Electronics - I, XII Electronics: Model Question Paper (2011)Document2 pagesSubject: Applied Electronics - I, XII Electronics: Model Question Paper (2011)mrityunjay_gupta_puneNo ratings yet

- Digital Circuits and Logic DesignDocument6 pagesDigital Circuits and Logic DesignSharukh BujjiNo ratings yet

- Principles of Digital Techniques On Web PDFDocument5 pagesPrinciples of Digital Techniques On Web PDFmdwalunjkar3095No ratings yet

- DLD Question BankDocument5 pagesDLD Question BankHarshad ThiteNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- Ec1312 QBDocument7 pagesEc1312 QBGopinathan MuthusamyNo ratings yet

- Dte QBDocument54 pagesDte QBitachisan973No ratings yet

- APR2013P21Document63 pagesAPR2013P21qsashutoshNo ratings yet

- Ec2203-Digital Electronics Question BankDocument22 pagesEc2203-Digital Electronics Question BankRamadhuraiNo ratings yet

- Digital Paper1Document5 pagesDigital Paper1Iyyakutti GanapathiNo ratings yet

- JanuaryFebruary 2021Document1 pageJanuaryFebruary 2021vishwatejkachu944No ratings yet

- ECE211 Digital ElectronicsDocument3 pagesECE211 Digital Electronicstejaputta6No ratings yet

- Ec3306 As01Document3 pagesEc3306 As01PRABHAT MISHRANo ratings yet

- Digital Electronics Question BankDocument11 pagesDigital Electronics Question BankS.Haribabu SNSNo ratings yet

- Logic Design Jan 2010 ESDocument2 pagesLogic Design Jan 2010 ESPrasad C MNo ratings yet

- Core-Iii-558-32511303-Digital Electronics and VHDL-21-12-2020Document4 pagesCore-Iii-558-32511303-Digital Electronics and VHDL-21-12-2020Sachin KumarNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- FY Btech - EX - Electrical & Electronics Engineering - SEM - I - JAN 2023Document3 pagesFY Btech - EX - Electrical & Electronics Engineering - SEM - I - JAN 2023kumbhalkarvalay8No ratings yet

- Digital Principles and System DesignDocument7 pagesDigital Principles and System DesignnofeelingrahulNo ratings yet

- DLD GTU Question Bank: Chapter-1 Binary SystemDocument5 pagesDLD GTU Question Bank: Chapter-1 Binary Systemnirav34No ratings yet

- DLD GTU Question Bank: Chapter-1 Binary SystemDocument129 pagesDLD GTU Question Bank: Chapter-1 Binary Systemnirav34No ratings yet

- Sample Question Paper - Principles of Digital Techniques-12069Document4 pagesSample Question Paper - Principles of Digital Techniques-12069Jackson AnthonyNo ratings yet

- Assignment EDES232CDocument3 pagesAssignment EDES232CPrakash DasNo ratings yet

- TE 2003&2008 PatternDocument623 pagesTE 2003&2008 PatternAshashwatmeNo ratings yet

- Instructions To StudentsDocument9 pagesInstructions To StudentsOmar Magdy AbdelbakyNo ratings yet

- KEE401 ASSIGNMENTS and QUESTION BANKDocument17 pagesKEE401 ASSIGNMENTS and QUESTION BANKPrince VermaNo ratings yet

- DE PaperDocument4 pagesDE Paperbhaveshgupta098No ratings yet

- 510Document8 pages510chenumallaNo ratings yet

- Digital Electronics Assignments Nirjari Desai 8q3VqbDocument8 pagesDigital Electronics Assignments Nirjari Desai 8q3VqbMuhammad BasitNo ratings yet

- UNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Document18 pagesUNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Deepak NaiduNo ratings yet

- BE Semester - III - IT - Question Bank (Fundamentals of Digital Electronics)Document3 pagesBE Semester - III - IT - Question Bank (Fundamentals of Digital Electronics)Arindam SenNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- EC2203 U Q BankDocument12 pagesEC2203 U Q Bankvlsi_satheeshNo ratings yet

- Digital Logic CircuitsDocument7 pagesDigital Logic CircuitsMATHANKUMAR.SNo ratings yet

- 07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrDocument8 pages07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrObula ReddyNo ratings yet

- DLC Series IaDocument1 pageDLC Series IaAnusha NatarajanNo ratings yet

- Dlda 2Document2 pagesDlda 2Manoj NaikNo ratings yet

- BE Semester-III (Instrumentation & Control) Question Bank (Digital Techniques) All Questions Carry Equal Marks (10 Marks)Document2 pagesBE Semester-III (Instrumentation & Control) Question Bank (Digital Techniques) All Questions Carry Equal Marks (10 Marks)abhishek pandaNo ratings yet

- Ade ImpqDocument2 pagesAde ImpqMadhanGopal MarthulaNo ratings yet

- Sura Group of Institutions, Lucknow: Q-2.2 Determine The Following For The Given NetworkDocument2 pagesSura Group of Institutions, Lucknow: Q-2.2 Determine The Following For The Given NetworkSaurabh SinghNo ratings yet

- F.M. - 50 Time: 2 Hours Answer Any FiveDocument3 pagesF.M. - 50 Time: 2 Hours Answer Any FiveProbir MondalNo ratings yet

- BET-C414: B. Tech. Semester Iv Examination, 2021Document3 pagesBET-C414: B. Tech. Semester Iv Examination, 2021NamanNo ratings yet

- Digital Logic CircuitsDocument20 pagesDigital Logic CircuitsrameshsophidarlaNo ratings yet

- r05220403 Switching Theory and Logic DesignDocument8 pagesr05220403 Switching Theory and Logic DesignSRINIVASA RAO GANTANo ratings yet

- Switching Theory and Logic DesignDocument6 pagesSwitching Theory and Logic DesignVijay MNo ratings yet

- De QBDocument4 pagesDe QBAzim KhanNo ratings yet

- DLD Ques1Document2 pagesDLD Ques1mahbub mitulNo ratings yet

- Digital Electronics Question BankDocument6 pagesDigital Electronics Question BankReshna ShowkathNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysFrom EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysNo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Department of Electronic Engineering: Final Year Project ReportDocument63 pagesDepartment of Electronic Engineering: Final Year Project ReportfarrukhshafiqueNo ratings yet

- Project ReportDocument14 pagesProject ReportMr hackerNo ratings yet

- Galvanized Ground Rod PDFDocument4 pagesGalvanized Ground Rod PDFAmiableimpexNo ratings yet

- Restricted Earth Fault Relay-AHQDocument4 pagesRestricted Earth Fault Relay-AHQEnpak Arsalan100% (1)

- Telemecanique Sensors - Reliability Data For PL Calculation - MTTFD - B10D - April 21,2021 - 10th Release - SistemaV2Document24 pagesTelemecanique Sensors - Reliability Data For PL Calculation - MTTFD - B10D - April 21,2021 - 10th Release - SistemaV2jucivanio10No ratings yet

- Sounder PDFDocument2 pagesSounder PDFPercy GoitsemangNo ratings yet

- 10 - Mini ProjectsDocument20 pages10 - Mini ProjectsMohammed Bin JafarullahNo ratings yet

- S800 I O Modules Ans800 - I - O - Modules - and - Termination - Unitsd Termination UnitsDocument668 pagesS800 I O Modules Ans800 - I - O - Modules - and - Termination - Unitsd Termination UnitsdleonarenNo ratings yet

- Single-Phase Seven-Level Grid-Connected InverterDocument23 pagesSingle-Phase Seven-Level Grid-Connected InverterVaggu ChandanNo ratings yet

- SM T561 PDFDocument47 pagesSM T561 PDFÉp Kính Phú QuốcNo ratings yet

- Solar Power Provision - Electrical Installation ContinuedDocument2 pagesSolar Power Provision - Electrical Installation ContinuedKassim Nderi100% (1)

- 1SAP140300R0271 pm583 Ethac500 Prog Log Controller 1mbDocument3 pages1SAP140300R0271 pm583 Ethac500 Prog Log Controller 1mbAymen TrabelsiNo ratings yet

- Ficha Solarnova 550W - EngDocument2 pagesFicha Solarnova 550W - EngHugo AngelesNo ratings yet

- ISWCS 2014 Program Web1Document31 pagesISWCS 2014 Program Web1ace.kris8117No ratings yet

- Manual GST-M200Document2 pagesManual GST-M200Mauricio Fuentes Abarzua100% (1)

- Soda Can Paper - TamannaDocument12 pagesSoda Can Paper - TamannaYoussef NasserNo ratings yet

- Pin Dual Mode 6 Cyl SequentialDocument2 pagesPin Dual Mode 6 Cyl Sequentialdeni andriasyahNo ratings yet

- Wireless Communication Systems, Services & RequirementsDocument45 pagesWireless Communication Systems, Services & RequirementsMuhammad Daniyal Ahmed BaigNo ratings yet

- ExternalSpecialist SEARCH RESULTDocument6 pagesExternalSpecialist SEARCH RESULTSea RouteNo ratings yet

- vm1700 En2Document6 pagesvm1700 En2Oliver Evans Mauriel RocabadoNo ratings yet

- Dr. HENG, Chun Huat Teaching Assistant Dr. BA MyintDocument7 pagesDr. HENG, Chun Huat Teaching Assistant Dr. BA MyintNixNo ratings yet

- Day 4th LearningDocument51 pagesDay 4th Learningpathakrr7No ratings yet

- PHYS 100B (Prof. Congjun Wu) Solution To HW 6: March 4, 2011Document4 pagesPHYS 100B (Prof. Congjun Wu) Solution To HW 6: March 4, 2011nagendra_gmNo ratings yet

- ADS Momentum Tutorial HL KY Final W09Document18 pagesADS Momentum Tutorial HL KY Final W09Pragash SangaranNo ratings yet

- Instruction and Service Manual Adjustable Frequency Crane ControlDocument9 pagesInstruction and Service Manual Adjustable Frequency Crane ControlJoss Maykol Mundaca VasquezNo ratings yet

- MFC 5850e EngDocument66 pagesMFC 5850e EngJair EduardoNo ratings yet

5DigitalTechniquesDTE 17333

5DigitalTechniquesDTE 17333

Uploaded by

Hitesh PatilOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

5DigitalTechniquesDTE 17333

5DigitalTechniquesDTE 17333

Uploaded by

Hitesh PatilCopyright:

Available Formats

Attempt any four of the following each carry 4 Marks:

Q 1] Realize the following expression using basic gates

.

y = (A+ B) (AB) ii) y = A B + C +DE

Q 2] Perform binary multiplication of (11001)2 X (10011)2

Q 3] convert the following expression into standard SOP form?

1) y =AB + AC+ BC

2) y=X+XY+Y

Q 4] Compare TTL and CMOS and ECL logic families (any four points

Q 5] State and prove De-Morgan‘s First and second theorem for two variables

Q 6] Draw AND, gate using NAND gate only and NOR gate only

Q 7] Draw symbol, logical equation and truth table of 3 i/p AND gate and 3 i/p OR gates?

Q 8] Convert following octal into Hexadecimal

i) (626)8

ii) (1245)8

Q 9] Define min and max term.

Q 10] Write Boolean laws

Q11] Find 2’s complement of:

i) (110110)2 ii) (010100)2

Q 12] Define power dissipation and figure of merit.

Q 13] Perform binary subtraction

i) (101011)2 - (10110)2 ii) (11001)2 - (10101)2

Attempt any four of the following each carry 3Marks:

Q 14] Write the symbol, Truth –table and logical expression of EX-NOR gate

Q 15] Simplify the Boolean expression given below

Y=Σm(1,3,5,9,11,13).

Q 16] Convert (78.5ABCD) into octal.

Q17] Convert (0.6875) into binary

Q18] Reduce the following expressions and implement using logic gates only.

____ __ __

Y=ABCD +ABC D +ABCD+ABCD

Q19] which are the advantages of digital circuits

Q20] Draw logic circuit using universal gates for following logic equation :

_ _

Y =ABC+AC+BC

Q21] If (396)10 = (A)2 = (B)16 , find A and B.

Q22] convert the expression Y=AB+AC+BC into the canonical SOP form.

Q23] Simplify the following three variable Boolean expression : Y=PiM(2,4,6)

Q24] Explain principle of duality theorm.

Q25] Perform BCD addition for the following:

i) (85)10 + (39)10 or

ii) (368)10 + (427)10

Attempt any four of the following each carry 4 Marks:

Q 1] Design Full Adder Circuit

Q 2] Draw the Logical block diagram of 4:1 MUX and describe its working using gates.

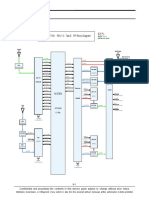

Q 3] Implement 1:32 DEMUX using 1:8 DEMUX.

Q 4] Draw the Block Diagram of BCD to SEVEN Segment Decoder with working.

Q 5] Implement the following function using 16:1 MUX

Y=∑m(0,1,3,4,7,12,15).

Q 6] Draw the logical circuit diagram of clocked S-R Flip Flop using NAND gates.Describe its working.

Q 7] Explain Race Around condition in J-K Flip Flop.

Q 8] Give two Advantages and Dis-Advantages of ADC.

Q 9] Draw the Circuit Diagram of R-2R Ladder method of DAC.

Q 10] Draw the block Diagram of Successive Approximation method of ADC.

Q11] Explain the Specifications of DAC.

Q 12] Draw the Block Diagram of sequential logic circuit and state the importance of clock signal.

Q 13] Explain the triggering methods of Flip Flop.

Attempt any four of the following each carry 3Marks:

Q 14] Design Half Adder Circuit

Q 15] Compare Weighted Register DAC and R2R Ladder type DAC.

Q 16]An 8 bit ADC has maximum voltage of 15V.What voltage change would each bit represent?

Q17] Classify the memories. What are the mechanism used for erasing EPROM?

Q18] Explain 1-bit memory cell with working.

Q19] Implement the following function using 8:1 MUX

Y=∑m(0,1,3,4,7).

Q20] Draw the neat diagram of Master Slave J-K Flip Flop .

Q21] Explain Half Subtractor with logic implementation of gates.

Q22] Design 4:1 MUX using 2:1 MUX

Q23] Explain J-K Flip Flop.

Q24]Design clocked S-R Flip Flop with Preset and Clear.

Q25] Explain the significance of Preset and Clear in JK Flip Flop.

You might also like

- DEC4000 Operation ManualDocument158 pagesDEC4000 Operation Manualthanhckctm100% (16)

- Ieee C37.20.1-1987Document36 pagesIeee C37.20.1-1987Febry Aryanto100% (1)

- Piezo Preamp and Buffer ReportDocument28 pagesPiezo Preamp and Buffer Reportsbrennan970100% (2)

- Technica Main TL Manual Sample TTDocument23 pagesTechnica Main TL Manual Sample TTpthakur234No ratings yet

- DE - KOE 039 - Question BankDocument6 pagesDE - KOE 039 - Question Bankyash vatsNo ratings yet

- 21 - 2010 - Nov - R09 - STLDDocument8 pages21 - 2010 - Nov - R09 - STLDvasuvlsiNo ratings yet

- Elec1041y 1 2007 2 PDFDocument7 pagesElec1041y 1 2007 2 PDFchetsNo ratings yet

- CS 2202 - Digital Principles and Systems DesignDocument3 pagesCS 2202 - Digital Principles and Systems DesignDhilip PrabakaranNo ratings yet

- 3CS3 04 PDFDocument3 pages3CS3 04 PDFprashantvlsiNo ratings yet

- 21 - 2011 - Dec - R09 - STLDDocument8 pages21 - 2011 - Dec - R09 - STLDvasuvlsiNo ratings yet

- EC8392-Digital EletronicsDocument2 pagesEC8392-Digital Eletronicssyed1188No ratings yet

- Subject: Applied Electronics - I, XII Electronics: Model Question Paper (2011)Document2 pagesSubject: Applied Electronics - I, XII Electronics: Model Question Paper (2011)mrityunjay_gupta_puneNo ratings yet

- Digital Circuits and Logic DesignDocument6 pagesDigital Circuits and Logic DesignSharukh BujjiNo ratings yet

- Principles of Digital Techniques On Web PDFDocument5 pagesPrinciples of Digital Techniques On Web PDFmdwalunjkar3095No ratings yet

- DLD Question BankDocument5 pagesDLD Question BankHarshad ThiteNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- Ec1312 QBDocument7 pagesEc1312 QBGopinathan MuthusamyNo ratings yet

- Dte QBDocument54 pagesDte QBitachisan973No ratings yet

- APR2013P21Document63 pagesAPR2013P21qsashutoshNo ratings yet

- Ec2203-Digital Electronics Question BankDocument22 pagesEc2203-Digital Electronics Question BankRamadhuraiNo ratings yet

- Digital Paper1Document5 pagesDigital Paper1Iyyakutti GanapathiNo ratings yet

- JanuaryFebruary 2021Document1 pageJanuaryFebruary 2021vishwatejkachu944No ratings yet

- ECE211 Digital ElectronicsDocument3 pagesECE211 Digital Electronicstejaputta6No ratings yet

- Ec3306 As01Document3 pagesEc3306 As01PRABHAT MISHRANo ratings yet

- Digital Electronics Question BankDocument11 pagesDigital Electronics Question BankS.Haribabu SNSNo ratings yet

- Logic Design Jan 2010 ESDocument2 pagesLogic Design Jan 2010 ESPrasad C MNo ratings yet

- Core-Iii-558-32511303-Digital Electronics and VHDL-21-12-2020Document4 pagesCore-Iii-558-32511303-Digital Electronics and VHDL-21-12-2020Sachin KumarNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- FY Btech - EX - Electrical & Electronics Engineering - SEM - I - JAN 2023Document3 pagesFY Btech - EX - Electrical & Electronics Engineering - SEM - I - JAN 2023kumbhalkarvalay8No ratings yet

- Digital Principles and System DesignDocument7 pagesDigital Principles and System DesignnofeelingrahulNo ratings yet

- DLD GTU Question Bank: Chapter-1 Binary SystemDocument5 pagesDLD GTU Question Bank: Chapter-1 Binary Systemnirav34No ratings yet

- DLD GTU Question Bank: Chapter-1 Binary SystemDocument129 pagesDLD GTU Question Bank: Chapter-1 Binary Systemnirav34No ratings yet

- Sample Question Paper - Principles of Digital Techniques-12069Document4 pagesSample Question Paper - Principles of Digital Techniques-12069Jackson AnthonyNo ratings yet

- Assignment EDES232CDocument3 pagesAssignment EDES232CPrakash DasNo ratings yet

- TE 2003&2008 PatternDocument623 pagesTE 2003&2008 PatternAshashwatmeNo ratings yet

- Instructions To StudentsDocument9 pagesInstructions To StudentsOmar Magdy AbdelbakyNo ratings yet

- KEE401 ASSIGNMENTS and QUESTION BANKDocument17 pagesKEE401 ASSIGNMENTS and QUESTION BANKPrince VermaNo ratings yet

- DE PaperDocument4 pagesDE Paperbhaveshgupta098No ratings yet

- 510Document8 pages510chenumallaNo ratings yet

- Digital Electronics Assignments Nirjari Desai 8q3VqbDocument8 pagesDigital Electronics Assignments Nirjari Desai 8q3VqbMuhammad BasitNo ratings yet

- UNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Document18 pagesUNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Deepak NaiduNo ratings yet

- BE Semester - III - IT - Question Bank (Fundamentals of Digital Electronics)Document3 pagesBE Semester - III - IT - Question Bank (Fundamentals of Digital Electronics)Arindam SenNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- EC2203 U Q BankDocument12 pagesEC2203 U Q Bankvlsi_satheeshNo ratings yet

- Digital Logic CircuitsDocument7 pagesDigital Logic CircuitsMATHANKUMAR.SNo ratings yet

- 07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrDocument8 pages07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrObula ReddyNo ratings yet

- DLC Series IaDocument1 pageDLC Series IaAnusha NatarajanNo ratings yet

- Dlda 2Document2 pagesDlda 2Manoj NaikNo ratings yet

- BE Semester-III (Instrumentation & Control) Question Bank (Digital Techniques) All Questions Carry Equal Marks (10 Marks)Document2 pagesBE Semester-III (Instrumentation & Control) Question Bank (Digital Techniques) All Questions Carry Equal Marks (10 Marks)abhishek pandaNo ratings yet

- Ade ImpqDocument2 pagesAde ImpqMadhanGopal MarthulaNo ratings yet

- Sura Group of Institutions, Lucknow: Q-2.2 Determine The Following For The Given NetworkDocument2 pagesSura Group of Institutions, Lucknow: Q-2.2 Determine The Following For The Given NetworkSaurabh SinghNo ratings yet

- F.M. - 50 Time: 2 Hours Answer Any FiveDocument3 pagesF.M. - 50 Time: 2 Hours Answer Any FiveProbir MondalNo ratings yet

- BET-C414: B. Tech. Semester Iv Examination, 2021Document3 pagesBET-C414: B. Tech. Semester Iv Examination, 2021NamanNo ratings yet

- Digital Logic CircuitsDocument20 pagesDigital Logic CircuitsrameshsophidarlaNo ratings yet

- r05220403 Switching Theory and Logic DesignDocument8 pagesr05220403 Switching Theory and Logic DesignSRINIVASA RAO GANTANo ratings yet

- Switching Theory and Logic DesignDocument6 pagesSwitching Theory and Logic DesignVijay MNo ratings yet

- De QBDocument4 pagesDe QBAzim KhanNo ratings yet

- DLD Ques1Document2 pagesDLD Ques1mahbub mitulNo ratings yet

- Digital Electronics Question BankDocument6 pagesDigital Electronics Question BankReshna ShowkathNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysFrom EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysNo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Department of Electronic Engineering: Final Year Project ReportDocument63 pagesDepartment of Electronic Engineering: Final Year Project ReportfarrukhshafiqueNo ratings yet

- Project ReportDocument14 pagesProject ReportMr hackerNo ratings yet

- Galvanized Ground Rod PDFDocument4 pagesGalvanized Ground Rod PDFAmiableimpexNo ratings yet

- Restricted Earth Fault Relay-AHQDocument4 pagesRestricted Earth Fault Relay-AHQEnpak Arsalan100% (1)

- Telemecanique Sensors - Reliability Data For PL Calculation - MTTFD - B10D - April 21,2021 - 10th Release - SistemaV2Document24 pagesTelemecanique Sensors - Reliability Data For PL Calculation - MTTFD - B10D - April 21,2021 - 10th Release - SistemaV2jucivanio10No ratings yet

- Sounder PDFDocument2 pagesSounder PDFPercy GoitsemangNo ratings yet

- 10 - Mini ProjectsDocument20 pages10 - Mini ProjectsMohammed Bin JafarullahNo ratings yet

- S800 I O Modules Ans800 - I - O - Modules - and - Termination - Unitsd Termination UnitsDocument668 pagesS800 I O Modules Ans800 - I - O - Modules - and - Termination - Unitsd Termination UnitsdleonarenNo ratings yet

- Single-Phase Seven-Level Grid-Connected InverterDocument23 pagesSingle-Phase Seven-Level Grid-Connected InverterVaggu ChandanNo ratings yet

- SM T561 PDFDocument47 pagesSM T561 PDFÉp Kính Phú QuốcNo ratings yet

- Solar Power Provision - Electrical Installation ContinuedDocument2 pagesSolar Power Provision - Electrical Installation ContinuedKassim Nderi100% (1)

- 1SAP140300R0271 pm583 Ethac500 Prog Log Controller 1mbDocument3 pages1SAP140300R0271 pm583 Ethac500 Prog Log Controller 1mbAymen TrabelsiNo ratings yet

- Ficha Solarnova 550W - EngDocument2 pagesFicha Solarnova 550W - EngHugo AngelesNo ratings yet

- ISWCS 2014 Program Web1Document31 pagesISWCS 2014 Program Web1ace.kris8117No ratings yet

- Manual GST-M200Document2 pagesManual GST-M200Mauricio Fuentes Abarzua100% (1)

- Soda Can Paper - TamannaDocument12 pagesSoda Can Paper - TamannaYoussef NasserNo ratings yet

- Pin Dual Mode 6 Cyl SequentialDocument2 pagesPin Dual Mode 6 Cyl Sequentialdeni andriasyahNo ratings yet

- Wireless Communication Systems, Services & RequirementsDocument45 pagesWireless Communication Systems, Services & RequirementsMuhammad Daniyal Ahmed BaigNo ratings yet

- ExternalSpecialist SEARCH RESULTDocument6 pagesExternalSpecialist SEARCH RESULTSea RouteNo ratings yet

- vm1700 En2Document6 pagesvm1700 En2Oliver Evans Mauriel RocabadoNo ratings yet

- Dr. HENG, Chun Huat Teaching Assistant Dr. BA MyintDocument7 pagesDr. HENG, Chun Huat Teaching Assistant Dr. BA MyintNixNo ratings yet

- Day 4th LearningDocument51 pagesDay 4th Learningpathakrr7No ratings yet

- PHYS 100B (Prof. Congjun Wu) Solution To HW 6: March 4, 2011Document4 pagesPHYS 100B (Prof. Congjun Wu) Solution To HW 6: March 4, 2011nagendra_gmNo ratings yet

- ADS Momentum Tutorial HL KY Final W09Document18 pagesADS Momentum Tutorial HL KY Final W09Pragash SangaranNo ratings yet

- Instruction and Service Manual Adjustable Frequency Crane ControlDocument9 pagesInstruction and Service Manual Adjustable Frequency Crane ControlJoss Maykol Mundaca VasquezNo ratings yet

- MFC 5850e EngDocument66 pagesMFC 5850e EngJair EduardoNo ratings yet