Professional Documents

Culture Documents

Bai Giang MDT - Chuong 4 - 2019

Bai Giang MDT - Chuong 4 - 2019

Uploaded by

Phú Trần ThiênOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Bai Giang MDT - Chuong 4 - 2019

Bai Giang MDT - Chuong 4 - 2019

Uploaded by

Phú Trần ThiênCopyright:

Available Formats

Chương 4.

Mạch khuếch đại ghép liên tầng

Chương 4.

MẠCH KHUẾCH ĐẠI GHÉP LIÊN TẦNG

Mục tiêu:

- Tính toán được phân cực DC cho các dạng mạch khếch đại vi sai cơ bản

- Vẽ được mạch tương đương tín hiệu nhỏ tần số thấp cho mạch

- Thiết lập được phương trình toán học mô tả hệ số khuếch đại dòng và áp của mạch

điện.

- Tính toán được trở kháng vào và ra của mạch

Yêu cầu: Sinh viên ôn tập kiến thức về

- Mạch khuếch đại dung BJT & FET

Nội dung: Trang

4.1. Mạch khuếch đại ghép liên tầng dạng nối tiếp (Cascading) ...................................... 2

4.2. Mạch khếch đại ghép Cascode. .................................................................................. 4

4.3. Mạch khếch đại ghép Darlington. .............................................................................. 5

4.4. Mạch khếch đại vi sai. ................................................................................................ 7

Biên soạn: TS. Bùi Thư Cao 1

Chương 4. Mạch khuếch đại ghép liên tầng

4.1. Mạch khuếch đại ghép liên tầng dạng nối tiếp (cascading)

Mạch khuếch đại cascading có dạng ghép nối tiếp các mạch khuếch đại đơn, ngõ ra của

khuếch đại mạch này là ngõ vào của mạch khuếch đại kia, như Hình 4.1. Các tụ bypass

được chọn với giá trị phù hợp, sao cho xem như nối tắt ở tần số làm việc. Các tụ liên lạc

được chọn sao cho giảm tối đa tổn hao của tín hiệu khi truyền qua các tụ liên lạc, nhưng

vẫn giữ được khả năng đáp ứng băng thông của mạch.

Hình 4. 1. Mô hình mạch khuếch đại ghép Cascading

Tính chất:

1) 𝐴𝑣 = 𝐴𝑣1 𝐴𝑣2 . . 𝐴𝑣𝑛

2) Zi = Zi1

3) Zo = Zon

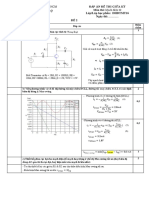

Bài tập: Cho mạch khuếch đại như hình vẽ. Biết mạch BJT và MOSFET được phân cực

tĩnh. Ri = 50Ω, R2 = R3 = 10KΩ, R5= R4 =R9 = R8 = 1KΩ, R7=R6=20KΩ, β = 100,

hie1 = 1kΩ, gm2 = 2m(1/Ω), rds2 = 30KΩ.

Hình 4. 2. Mạch khuếch đại ghép BJT & FET

a) Vẽ mạch tương đương tín hiệu nhỏ tần số thấp

b) Tính Av, Zi, Zo.

Biên soạn: TS. Bùi Thư Cao 2

Chương 4. Mạch khuếch đại ghép liên tầng

Biên soạn: TS. Bùi Thư Cao 3

Chương 4. Mạch khuếch đại ghép liên tầng

4.2. Mạch khếch đại ghép cascode.

Mạch khuếch đại cascode có dạng ghép song song các mạch khuếch đại đơn, ngõ vào của

khuếch đại mạch này cũng là ngõ vào của mạch khuếch đại kia.

Bài tập: Cho mạch khuếch đại cascade như hình vẽ.

Biết mạch BJT và MOSFET được

phân cực tĩnh. Ri = 50Ω, R1=R2 = R3

= 10KΩ, RC = RE = RL = 1KΩ, β1 =

β1 = 120, VCC = 12V.

a) Tính phân cực DC cho mạch.

b) Vẽ mạch tương đương tín hiệu

nhỏ tần số thấp

c) Tính Av, Zi, Zo.

Hình 4. 3. Mạch khuếch đại ghép casdcode cơ bản

Biên soạn: TS. Bùi Thư Cao 4

Chương 4. Mạch khuếch đại ghép liên tầng

4.3. Mạch khếch đại ghép Darlington.

Mạch khuếch đại Darlington có dạng ghép trực tiếp các cực của 2 transistor, như Hình 4.4.

Mạch tương đương tín hiệu nhỏ,

Hình 4. 4. Mạch transistor ghép darlington

Bài tập: Cho mạch khuếch đại như hình vẽ.

Biết mạch BJT được phân cực tĩnh.

Ri = 50Ω, R1=R2 = R3 = 10KΩ, RC

= RE = RL = 1KΩ, β1 = β1 = 120,

VCC = 12V.

d) Tính phân cực DC cho

mạch.

e) Vẽ mạch tương đương tín

hiệu nhỏ tần số thấp

f) Tính Av, Zi, Zo.

Hình 4. 5. Mạch khuếch đại ghép Darlington cơ bản

Biên soạn: TS. Bùi Thư Cao 5

Chương 4. Mạch khuếch đại ghép liên tầng

Biên soạn: TS. Bùi Thư Cao 6

Chương 4. Mạch khuếch đại ghép liên tầng

4.4. Mạch khếch đại vi sai.

Mạch khuếch đại vi sai có dạng ghép cặp 2 mạch khuếch đại transistor, như Hình 4.4. Trong

đó các giá trị cặp điện trở bằng nhau, R1=R1’, R2 = R2’, Rc = Rc’ và xem như cặp nội trợ

nguồn ngõ vào cũng bằng nhau, Ri = Ri’.

Hình 4. 6. Sơ đồ mạch khuếch đại vi sai cơ bản

Hình 4. 7. Biến đổi tương đương

Hình 4. 8. Mạch khuếch đại vi sai thực tế

Biên soạn: TS. Bùi Thư Cao 7

Chương 4. Mạch khuếch đại ghép liên tầng

Phân tích mạch tín hiệu nhỏ tần số thấp

Biên soạn: TS. Bùi Thư Cao 8

You might also like

- Bai Giang MDT - Chuong 3 - 03 - 2022Document11 pagesBai Giang MDT - Chuong 3 - 03 - 2022Phú Trần ThiênNo ratings yet

- Bai Giang MDT - Chuong 2 - 2019Document14 pagesBai Giang MDT - Chuong 2 - 2019Phú Trần ThiênNo ratings yet

- Mạch Điện TửDocument37 pagesMạch Điện TửPhú Trần ThiênNo ratings yet

- Chương 2 - Cơ bản về cao tầnDocument26 pagesChương 2 - Cơ bản về cao tầnNguyễn Võ Phước TríNo ratings yet

- Chuong 6 Dap Ung Tan So (01-9-21)Document37 pagesChuong 6 Dap Ung Tan So (01-9-21)Phước Phan VănNo ratings yet

- Phan Minh QuanDocument5 pagesPhan Minh Quan0308221065No ratings yet

- Phan Minh QuanDocument5 pagesPhan Minh Quan0308221065No ratings yet

- Bai Giang DTNC - Chuong 2 - 28 - 05Document19 pagesBai Giang DTNC - Chuong 2 - 28 - 05Khang ĐinhNo ratings yet

- Hocnq VAT LY BAN DAN THAP CHIEU C4Document56 pagesHocnq VAT LY BAN DAN THAP CHIEU C4Hiro ChanNo ratings yet

- 2023.2024 Fe GHK1 Congnghe K12 DecuongDocument8 pages2023.2024 Fe GHK1 Congnghe K12 Decuongluuhuubinh21No ratings yet

- 2 DTTTDocument7 pages2 DTTTSimple LifeNo ratings yet

- Giai-Tich-Mach - Le-Minh-Cuong - Eca - ch3 - 6a-Circuit-Theorems-Cac-Dinh-Ly-Co-Ban-Cua-Mach-Dien - (Cuuduongthancong - Com)Document8 pagesGiai-Tich-Mach - Le-Minh-Cuong - Eca - ch3 - 6a-Circuit-Theorems-Cac-Dinh-Ly-Co-Ban-Cua-Mach-Dien - (Cuuduongthancong - Com)Nguyên NgọcNo ratings yet

- 1. Bài tập tính điện trở tương đươngDocument2 pages1. Bài tập tính điện trở tương đươngMai NguyenNo ratings yet

- 6. Chương 2 Mạch điện tử 2Document39 pages6. Chương 2 Mạch điện tử 2lehy16022002No ratings yet

- On - Tap - TH - Anten - Truyen - Song (AutoRecovered)Document10 pagesOn - Tap - TH - Anten - Truyen - Song (AutoRecovered)Dương Thành ĐạtNo ratings yet

- Bài Phúc Trình 1Document12 pagesBài Phúc Trình 1tran anh tuanNo ratings yet

- Bài giảng Kỹ thuật điện tử C3 - Gửi sinh viênDocument101 pagesBài giảng Kỹ thuật điện tử C3 - Gửi sinh viênLục LinhNo ratings yet

- TH 01Document3 pagesTH 01Yusaku KudoNo ratings yet

- Bo de Thi Giua Hoc Ki 1 Lop 9 Mon Vat LyDocument16 pagesBo de Thi Giua Hoc Ki 1 Lop 9 Mon Vat LyLinh TrầnNo ratings yet

- Lab 03 Hand-OutDocument2 pagesLab 03 Hand-OutMinh DucNo ratings yet

- Chuong 4 KD VI Sai (01-9-21)Document41 pagesChuong 4 KD VI Sai (01-9-21)Tuấn Nguyễn VănNo ratings yet

- 2-2 SĐĐ dây quấn máy điện xoay chiềuDocument13 pages2-2 SĐĐ dây quấn máy điện xoay chiềuVu NghiaNo ratings yet

- Vat Ly Chuyen NganhDocument6 pagesVat Ly Chuyen Nganhthee zenerNo ratings yet

- TNMĐT B2Document30 pagesTNMĐT B2Khoa ĐăngNo ratings yet

- Ngân Hàng Cau Hoi SBVL PDFDocument6 pagesNgân Hàng Cau Hoi SBVL PDFLương Văn TuânNo ratings yet

- C1.1.Dap Tuyen Tan So ThapDocument89 pagesC1.1.Dap Tuyen Tan So ThapAn ĐinhNo ratings yet

- Chuong 34Document2 pagesChuong 34Nguyễn DũngNo ratings yet

- PP chia nhỏ trong điệnDocument4 pagesPP chia nhỏ trong điệnsomew.td7No ratings yet

- Bài Báo Cáo 1 - Phan Thanh HuyDocument4 pagesBài Báo Cáo 1 - Phan Thanh HuyTiến PhanNo ratings yet

- Thi Nghiem Mach Dien Tu Lab2 Diode Powersp (Cuuduongthancong - Com)Document12 pagesThi Nghiem Mach Dien Tu Lab2 Diode Powersp (Cuuduongthancong - Com)Thong QuocNo ratings yet

- 2.1 Giới thiệu cách sử dụng Oscilliscope (OSC) 2.2 Mạch chỉnh lưu bán kì a. Mạch không có tụ lọcDocument9 pages2.1 Giới thiệu cách sử dụng Oscilliscope (OSC) 2.2 Mạch chỉnh lưu bán kì a. Mạch không có tụ lọcThái PhiênNo ratings yet

- (2 ĐỀ) ĐỀ THI + Đáp án KTĐT ĐĐT 12 lần 1 PDFDocument6 pages(2 ĐỀ) ĐỀ THI + Đáp án KTĐT ĐĐT 12 lần 1 PDFVü PhämNo ratings yet

- Huong Dan Giai Bai Tap Chuong 2Document16 pagesHuong Dan Giai Bai Tap Chuong 2Mau Binh NguyenNo ratings yet

- Lab 03Document4 pagesLab 03Vũ MạnhNo ratings yet

- Nhóm - 05 KTMDTDocument8 pagesNhóm - 05 KTMDTvolinzz3No ratings yet

- 3.7 Dien Tu Mach Dien TuDocument2 pages3.7 Dien Tu Mach Dien TuLinh NguyenNo ratings yet

- TH VĐKDocument25 pagesTH VĐKtrường phạm vănNo ratings yet

- Đây là bài báo cáo về thiết kế mạch tạo chuỗi xung 1Hz chuẩn từ mạch dao động đa hài phi ổn dùng thạch anh kết hợp cổng logic. Mạch gồm hai khối: khối mạch dao động đa hài phi ổn mắc theo kiểu song song và khối mạch chia tần số dùng IC 4060 và IC 4013.Document10 pagesĐây là bài báo cáo về thiết kế mạch tạo chuỗi xung 1Hz chuẩn từ mạch dao động đa hài phi ổn dùng thạch anh kết hợp cổng logic. Mạch gồm hai khối: khối mạch dao động đa hài phi ổn mắc theo kiểu song song và khối mạch chia tần số dùng IC 4060 và IC 4013.Bá HuyNo ratings yet

- Chuong 4Document25 pagesChuong 4hai anhNo ratings yet

- Bai Tap Vat Ly Chat RanDocument7 pagesBai Tap Vat Ly Chat RanQuách Gia Bảo100% (1)

- đề 14 - 15 hk1Document4 pagesđề 14 - 15 hk1Phúc Thiên PhạmNo ratings yet

- Bai 1 Mach RLCDocument8 pagesBai 1 Mach RLCnguyendangt740No ratings yet

- Ngan Hang Cau Hoi TDT Va Anten de OnlyDocument8 pagesNgan Hang Cau Hoi TDT Va Anten de OnlyNgô NamNo ratings yet

- Báo Cáo Thí Nghiệm Bài 4Document25 pagesBáo Cáo Thí Nghiệm Bài 4hoangy12a26No ratings yet

- Baitap DTCBDocument30 pagesBaitap DTCBThế giới điện tửNo ratings yet

- Đề 1Document3 pagesĐề 1Tiên NguyễnNo ratings yet

- Kỷ thuật điện tửDocument20 pagesKỷ thuật điện tửThanh TrúcNo ratings yet

- BT Vat Ly 11cb-Chuong I I - Day He-hs-OnlineDocument4 pagesBT Vat Ly 11cb-Chuong I I - Day He-hs-OnlineHuy GMNo ratings yet

- PHDocument24 pagesPHyumyumuniversityNo ratings yet

- BÀI TẬP LÝ THUYẾT TRƯỜNG ĐIỆN TỪ MỚIDocument8 pagesBÀI TẬP LÝ THUYẾT TRƯỜNG ĐIỆN TỪ MỚIPhat VanNo ratings yet

- Thuc Hanh 1.SVDocument29 pagesThuc Hanh 1.SVThành Tá NguyễnNo ratings yet

- Bien-Doi-Nang-Luong-Dien-Co - Nguyen-Ngoc-Tu - Midterm - Ex - (Cuuduongthancong - Com) PDFDocument5 pagesBien-Doi-Nang-Luong-Dien-Co - Nguyen-Ngoc-Tu - Midterm - Ex - (Cuuduongthancong - Com) PDFjohnNo ratings yet

- Bien-Doi-Nang-Luong-Dien-Co - Nguyen-Ngoc-Tu - Midterm - Ex - (Cuuduongthancong - Com) PDFDocument5 pagesBien-Doi-Nang-Luong-Dien-Co - Nguyen-Ngoc-Tu - Midterm - Ex - (Cuuduongthancong - Com) PDFFUNNY MOMENTS OF TRUONG MAPNo ratings yet

- VatLy11 BaiTapTongHop (Chuong2)Document70 pagesVatLy11 BaiTapTongHop (Chuong2)Đỗ Thị Bích ThủyNo ratings yet

- DCMH Mach Dien Tu - 27 3 23Document4 pagesDCMH Mach Dien Tu - 27 3 23An ĐinhNo ratings yet

- LTM Nganhang 2016Document29 pagesLTM Nganhang 2016tan vuNo ratings yet

- Report Analog1Document9 pagesReport Analog1Thế DuyNo ratings yet

- Chương 2Document56 pagesChương 2Phú Trần ThiênNo ratings yet

- CH 1Document61 pagesCH 1Phú Trần ThiênNo ratings yet

- DCMH Mach Dien Tu AUN 2018Document4 pagesDCMH Mach Dien Tu AUN 2018Phú Trần ThiênNo ratings yet

- Dap An - Rubic - de Thi 1 GK - MDT - 2022Document2 pagesDap An - Rubic - de Thi 1 GK - MDT - 2022Phú Trần ThiênNo ratings yet

- Dap An - Rubic - de Thi 2 GK - MDT - 2022Document2 pagesDap An - Rubic - de Thi 2 GK - MDT - 2022Phú Trần ThiênNo ratings yet

- Bai Giang MDT - Chuong 3 - 03 - 2022Document11 pagesBai Giang MDT - Chuong 3 - 03 - 2022Phú Trần ThiênNo ratings yet

- Bai Giang MDT - Chuong 2 - 2019Document14 pagesBai Giang MDT - Chuong 2 - 2019Phú Trần ThiênNo ratings yet

- Bai Giang MDT - Chuong 1 - 2022Document9 pagesBai Giang MDT - Chuong 1 - 2022Phú Trần ThiênNo ratings yet

- Mạch Điện TửDocument37 pagesMạch Điện TửPhú Trần ThiênNo ratings yet