Professional Documents

Culture Documents

14CS2005 - 2april May 2018

14CS2005 - 2april May 2018

Uploaded by

Property RequestOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

14CS2005 - 2april May 2018

14CS2005 - 2april May 2018

Uploaded by

Property RequestCopyright:

Available Formats

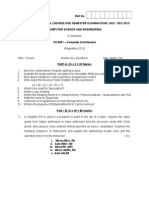

Reg.No.

____________

End Semester Examination – Apr/May – 2018

Code : 14CS2005 Duration : 3hrs

Sub. Name : COMPUTER ARCHITECTURE Max. marks : 100

ANSWER ALL QUESTIONS (5 x 20 = 100 Marks)

Q. Sub Questions Course Marks

No. Div. Outcome

1. a. The following diagram shows the initial positions of memory and CO1 15

CPU registers. An addition program is stored in memory locations

300, 301 and 302. The values are stored in memory locations 940

and 941.

Explain the steps during program execution and show the final

values in all these memory locations after program execution.

Note : 0001 – 1 ; 0010 – 2; 0101 – 5

b. Contrast the dedicated and multiplexed bus types. CO1 5

(OR)

2. a. Discuss any two mechanisms to handle simultaneously occurring CO1 10

multiple interrupts with suitable examples.

b. Discuss the procedure of associative mapping technique that maps CO3 10

each main memory block into any cache memory line, with

hardware configuration diagram.

3. a. Consider that an 8-bit data word 11000010 is stored in memory. CO3 15

Using the Hamming code, calculate the check bits to be stored in

memory along with the data word. Apply the single bit error

correction technique to detect the error in this word if the word is

read out as 10000010.

b. Discuss the various cache replacement policies with appropriate CO1 5

examples.

(OR)

4. a. The Direct Memory Access technique requires the least CO2 15

involvement of the processor than programmed I/O and interrupt

driven I/O techniques, in any input output process. Justify the above

statement with suitable examples.

b. Discuss Interrupt Driven I/O mechanism which deals the I/O CO2 5

operation in a program execution.

5. a. Evaluate the capability of Booth’s algorithm to multiply the CO1 15

negative numbers -7 and -3.

b. Differentiate logical right shift and arithmetic shift for the following CO2 5

example.

1 0 0 1 0 0 1 1

(OR)

6. a. Consider the following instructions: CO3 15

EA = (A) 1

EA = A + (R) 2

EA = R 3

Identify the addressing modes used in the above instructions and

explain the addressing modes.

b. How will you identify which address instruction format is suitable CO2 5

for high performance in program execution?

7. a. CO2 15

Identify the hazard in the above mentioned instruction pipeline.

Explain that hazard in detail and propose solutions for the same.

b. Draw and explain the instruction cycle state diagram which has CO3 5

indirect cycle.

(OR)

8. a. Elaborate the control hazards with suitable programming examples CO3 15

and discuss the various branch prediction techniques to reduce the

branch penalty.

b. Outline the various flags and their functions available in the PSW CO2 5

register.

Compulsory:

9. Discuss the microinstruction sequencing and its execution in detail CO3 20

with suitable diagrams.

You might also like

- 14CS2005 Nov 2019Document2 pages14CS2005 Nov 2019Property RequestNo ratings yet

- 14CS2005 2017Document1 page14CS2005 2017Property RequestNo ratings yet

- 14CS2005 2018 NovDocument2 pages14CS2005 2018 NovProperty RequestNo ratings yet

- 14CS2005 April May 2018Document2 pages14CS2005 April May 2018Property RequestNo ratings yet

- Question Paper Code: 18041: Reg. NoDocument4 pagesQuestion Paper Code: 18041: Reg. NoSivakumar NNo ratings yet

- Pdfjoiner PDFDocument26 pagesPdfjoiner PDFbakosey323No ratings yet

- CSC219 - 356 - 132 CSC219 Dec 15Document5 pagesCSC219 - 356 - 132 CSC219 Dec 15Aniket AmbekarNo ratings yet

- Tutorial 3 2022 StudentsDocument5 pagesTutorial 3 2022 StudentsIndongo EliaserNo ratings yet

- CO MP CS45O JUNE 2020Document2 pagesCO MP CS45O JUNE 2020shrinidhipawar09No ratings yet

- DCSFinal II April21 AssignmenrtDocument45 pagesDCSFinal II April21 AssignmenrtChirantan BiswasNo ratings yet

- Coa Ese Q (2022)Document2 pagesCoa Ese Q (2022)Aayush Kumar DubeyNo ratings yet

- MCS (S) Dec 2005Document46 pagesMCS (S) Dec 2005amritanshuuNo ratings yet

- DDCO UPDATED QUESTION BANKttttDocument4 pagesDDCO UPDATED QUESTION BANKttttbrahmareddy.22iseNo ratings yet

- Ca 13Document3 pagesCa 13krishnasankar95No ratings yet

- B.TECH. (Model Paper) : (Sem I) Theory Examination 2020-21 Programming For Problem SolvingDocument2 pagesB.TECH. (Model Paper) : (Sem I) Theory Examination 2020-21 Programming For Problem SolvingTushar SaxenaNo ratings yet

- KCS101T - QP 2020 21Document2 pagesKCS101T - QP 2020 21manishNo ratings yet

- Os - Set 2Document2 pagesOs - Set 2saraswathiNo ratings yet

- Model QP Os Set 3 UpdatedDocument3 pagesModel QP Os Set 3 Updatednarenmadhavan5No ratings yet

- Embedded System DesignDocument23 pagesEmbedded System DesignlosssssssssNo ratings yet

- HMK 4 ARCDocument3 pagesHMK 4 ARCskeletorfearsmeNo ratings yet

- Comp Architecture Sample QuestionsDocument9 pagesComp Architecture Sample QuestionsMohamaad SihatthNo ratings yet

- CS211 ExamDocument10 pagesCS211 ExamTetzNo ratings yet

- COA Question PaperDocument2 pagesCOA Question PaperwahidNo ratings yet

- LDCA Previous Year PaperDocument4 pagesLDCA Previous Year Paperflipkart6392No ratings yet

- Computer Architecture and OrganizationDocument6 pagesComputer Architecture and OrganizationRahmantic SwatzNo ratings yet

- Computer Organization and ArchitectureDocument3 pagesComputer Organization and ArchitecturecoolshubupaunikarNo ratings yet

- IP - PVP23 Question BankDocument9 pagesIP - PVP23 Question Bank23501a0568No ratings yet

- COA Question Bank - CO MappingDocument3 pagesCOA Question Bank - CO MappingKomalNo ratings yet

- Sathyabama: Register NumberDocument4 pagesSathyabama: Register Numberanonymousgamer485No ratings yet

- Solutions To Set 8Document18 pagesSolutions To Set 8kitana_sectNo ratings yet

- Ce 419Document4 pagesCe 419all workNo ratings yet

- Questions 4 1Document95 pagesQuestions 4 1Anik PaulNo ratings yet

- Cadcam Model Question PaperDocument2 pagesCadcam Model Question PaperSelvaraj GNo ratings yet

- CST202 QPDocument2 pagesCST202 QPSreedevi R KrishnanNo ratings yet

- Vlsi QP 21,22Document11 pagesVlsi QP 21,22Arunitha ArulnathanNo ratings yet

- Acseh0304 (DLD) 2Document5 pagesAcseh0304 (DLD) 2yt608118No ratings yet

- MPMC 1Document27 pagesMPMC 1AAKASH CSNo ratings yet

- Computer Organization: Sandeep KumarDocument117 pagesComputer Organization: Sandeep KumarGaurav NNo ratings yet

- Microprocessor and Architecture Solution PDFDocument23 pagesMicroprocessor and Architecture Solution PDFKarmaveer Bhaurao Patil CollegeNo ratings yet

- Veermata Jijabai Technological Institute: End Semester Examination December 2018 SEM-I, First Year MCADocument3 pagesVeermata Jijabai Technological Institute: End Semester Examination December 2018 SEM-I, First Year MCApradnya kingeNo ratings yet

- Rns Institute of Technology: Electronics and Communication EngineeringDocument1 pageRns Institute of Technology: Electronics and Communication EngineeringVinaykumar ANo ratings yet

- 15CS44 MM Question BankDocument5 pages15CS44 MM Question BankDarshanNo ratings yet

- Sample PapersDocument6 pagesSample PapersHirkanipatilNo ratings yet

- DD&CO Model Set1 Paper 2022 SchemeDocument2 pagesDD&CO Model Set1 Paper 2022 Schemeanveshrao024No ratings yet

- BCS302 Set 1Document2 pagesBCS302 Set 1Mina KimNo ratings yet

- C G192056 Pages:3: Answer All Questions, Each Carries 4 MarksDocument3 pagesC G192056 Pages:3: Answer All Questions, Each Carries 4 MarksVicNo ratings yet

- 2020 09 14SupplementaryCS405CS405 D Ktu QbankDocument3 pages2020 09 14SupplementaryCS405CS405 D Ktu QbankCigi ManojNo ratings yet

- Cadcam Iat - 3 Question PaperDocument1 pageCadcam Iat - 3 Question PaperSelvaraj GNo ratings yet

- COA Question Bank With SolutionDocument145 pagesCOA Question Bank With SolutionSandeep Kumar YadavNo ratings yet

- Se, All Branches. C A - oDocument2 pagesSe, All Branches. C A - oanuragnair377No ratings yet

- Microprocessor (ECE-3153)Document2 pagesMicroprocessor (ECE-3153)RAHUL RTRNo ratings yet

- Mca31 Jan2020Document2 pagesMca31 Jan2020Nikhil SnNo ratings yet

- Course Code: MET 406 Azby/Ms - 18 / 4656 Eighth Semester B. E. (Mechanical Engineering) ExaminationDocument23 pagesCourse Code: MET 406 Azby/Ms - 18 / 4656 Eighth Semester B. E. (Mechanical Engineering) ExaminationMubarika SabirNo ratings yet

- Computer Organization and Design (CSE-201) (Makeup)Document2 pagesComputer Organization and Design (CSE-201) (Makeup)damoy28211No ratings yet

- BTCS403 End Sem With CODocument4 pagesBTCS403 End Sem With COeverlovingmansiNo ratings yet

- SSCDDocument12 pagesSSCDJovan JacobNo ratings yet

- Btech Cs 3 Sem Computer Organization and Architecture kcs302 2022Document2 pagesBtech Cs 3 Sem Computer Organization and Architecture kcs302 2022Harshit dubeyNo ratings yet

- MCS 012Document118 pagesMCS 012SongYak YamNo ratings yet

- Question Bank CompleteDocument5 pagesQuestion Bank CompleteSaurabh SenNo ratings yet

- Mathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsFrom EverandMathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsRoderick MelnikNo ratings yet

- 14CS2005 2018 NovDocument2 pages14CS2005 2018 NovProperty RequestNo ratings yet

- 14CS2005 Nov 2019Document2 pages14CS2005 Nov 2019Property RequestNo ratings yet

- 14CS2005 2017Document1 page14CS2005 2017Property RequestNo ratings yet

- 14CS2005 April May 2018Document2 pages14CS2005 April May 2018Property RequestNo ratings yet

- Error Codes InspexionDocument18 pagesError Codes InspexionPopescu Emanuel IonutNo ratings yet

- Computer Architecture 1Document4 pagesComputer Architecture 1Shidqi Amirul HaqNo ratings yet

- Module 1 - Intro To Computer SystemDocument44 pagesModule 1 - Intro To Computer SystemKhysval WalkerNo ratings yet

- Alarm List - E1102000106GB02Document582 pagesAlarm List - E1102000106GB02Ismael50% (2)

- 1718 Ex I/O: Intrinsically Safe Distributed I/O For Zone 1 ApplicationsDocument3 pages1718 Ex I/O: Intrinsically Safe Distributed I/O For Zone 1 Applicationscnrk777No ratings yet

- MX 4000 Series User ManualDocument38 pagesMX 4000 Series User Manualkruna12350% (2)

- Proline Prosonic Flow 90P, 93P: Technical InformationDocument32 pagesProline Prosonic Flow 90P, 93P: Technical InformationMiladinm1No ratings yet

- AC-225x-B Hardware Installation and User Manual 270618Document41 pagesAC-225x-B Hardware Installation and User Manual 270618Daniel RiveraNo ratings yet

- Bergerlahr Wdp3 01x ManualDocument114 pagesBergerlahr Wdp3 01x ManualAmit SharmaNo ratings yet

- ABBAC500 - Hot-Standby RedundancyDocument2 pagesABBAC500 - Hot-Standby Redundancygetintouch jdaNo ratings yet

- Computer Architecture: Chapter # 05Document7 pagesComputer Architecture: Chapter # 05Samiullah FazalNo ratings yet

- Problem Solving ExerciseDocument2 pagesProblem Solving ExerciseHariz HazwanNo ratings yet

- VT-VSPD - Digital Valve Amplifier For Proportional Valves Without Position FeedbackDocument80 pagesVT-VSPD - Digital Valve Amplifier For Proportional Valves Without Position FeedbacklekavetosNo ratings yet

- DLive Wings 2ppDocument2 pagesDLive Wings 2ppKolyaYNo ratings yet

- 17ME754 Mechatronics PLC and 8085Document9 pages17ME754 Mechatronics PLC and 8085Abhishek KumarNo ratings yet

- Computer Application 1st Yr LMDocument183 pagesComputer Application 1st Yr LMPatson BandaNo ratings yet

- DLP 3 Roles FunctionsDocument2 pagesDLP 3 Roles FunctionsThe Basics by RaeNo ratings yet

- 01-Introduction To The User InterfaceDocument29 pages01-Introduction To The User InterfaceMario Vila NovaNo ratings yet

- RFID Door Security SystemDocument23 pagesRFID Door Security SystemJayant meenaNo ratings yet

- Chapter 1 - Introduction - Slides - 2Document48 pagesChapter 1 - Introduction - Slides - 2Fvck OffNo ratings yet

- Fs-Uae LogDocument22 pagesFs-Uae LogResidencia de Nefrologia Aula virtualNo ratings yet

- Cutler Hammer Eaton D50 Manual 2017911111536Document228 pagesCutler Hammer Eaton D50 Manual 2017911111536patrickNo ratings yet

- IT0007-Laboratory-Exercise-4 - What's Going OnDocument7 pagesIT0007-Laboratory-Exercise-4 - What's Going OnDenise JaoNo ratings yet

- CbmsDocument5 pagesCbmsmadhurivithanala07No ratings yet

- 1 - Siemens Open Library - Library Overview and ArchitectureDocument22 pages1 - Siemens Open Library - Library Overview and ArchitectureThành Vinh PhạmNo ratings yet

- PIC16F87X Tutorial by Example: Document HistoryDocument69 pagesPIC16F87X Tutorial by Example: Document Historymytran1325No ratings yet

- Train Win 1 XRayDocument3 pagesTrain Win 1 XRayawichi chediNo ratings yet

- BarcodeDocument4 pagesBarcodeVirag PatilNo ratings yet

- Intel 8042Document25 pagesIntel 8042Imos Lonxe100% (1)

- Relationship Between Operating System Computer HarDocument6 pagesRelationship Between Operating System Computer HarHusain AliNo ratings yet