Professional Documents

Culture Documents

Shit 1 Heheheheeeee

Shit 1 Heheheheeeee

Uploaded by

Maher Gomaa Ismaeel0 ratings0% found this document useful (0 votes)

26 views10 pagessheet

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentsheet

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

Download as pdf

0 ratings0% found this document useful (0 votes)

26 views10 pagesShit 1 Heheheheeeee

Shit 1 Heheheheeeee

Uploaded by

Maher Gomaa Ismaeelsheet

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

Download as pdf

You are on page 1of 10

stra ahmed sheet

Sheet Lecture (1)

1. Give Course Objectives and Course Outcomes?

1, Definition of TC's (integrated cireuit}?,

2 GivnlG Suesifcationst

3, What isthe Integrated circuit Seale?

4, Whats Gordon low prediction of integrated Circuit

4, Whats the manufacturing of Integrated Circuits (C) consists of Four

Steps?

6. What the steps of planar technology?

7. Why Silicon not Ge?

8, "The crystal orientation defines its electrical properties” Explain

9, What sixprocesses fabrication of bipolar layers junction transistor (BJT)?

1+ Explain Wafer Preparation(Silicon purification and 2-Single Crt Growth

) fo obtain the final wafers

12. Exalsin Crochuakhisinek coatalzcamth?

1. Calculate the theoretical value of mn silicon at raom temperature temperate (200

oH.

Where Eo=1.12 eV.

And From The Text book

e-Bolemnm's constant, £46238 10° UK

‘B= Material dependent parameter, 1.08 x10" K*. Car for Si.

16-Find the mobility and resitvtyofntintecom at 400 K and casi it as

an insulator, semiconductor, or conductor B=1.08 x10", E=100 V/Cm, ve

13510 Caineg, Where Eo=1.12-€V and vy=2100 Cin

Anowers: mobility values je= 4300 cns/s gpd ty= 2100 emo, , 1450 0° ex,

semiconductor,

* Calculate the resistivity of intrinsic silicon at 50 K if the electron mobility is 6500

em? +5 and the hale mobility is 2000 cam" s. Clasify the material

Answer: 1.69 x 10" Q cm, insulator

‘From the text book.

@ = 4.65 +2) Geomy*

1. Course Objectives:

© To understand VESI circuit dasion processes,

+ To understand basic eicuit concepis and desiewing Arithmetic Building Blocks

© To have an oversaw of Low poner VLSI.

(Course Outeomet:

© Coumplete Knoniedze about Fabrication process of Iss

© Ableto dasign VLSI circuits as per specifications given,

© Capable of optimizing the design of Arithmetic | logic building Blocks at all

level: of Design Falrication,

# Alkmowledge of CMOS cizeaits and SPICE simulation is desirable (Micsomind

55, LTsnice)

12. Definition of IC's (integrated circuit)?

Integrated Circuit is a miniaturized Ait electronic cixcuit consisting mainly of active

slemants censiconductor davices, (Bipolar and MOSFET and BiCMOS transistors) 5

‘roll as passive elements (Dioda, resistance, and capacitance) that has heen manish

inthe surface of shin subetrate of semiconductor material,

(+ Higher speed, due to significant reduces intercomnection length

+ Loweost,

+ Lass testing requizen

© Higher raliability de

te

mainly due to improve on-chip interconnects,

‘What we will Study in IC Technologies?

‘Fabrication of

> BiCMOS

Mos

NMOS

PMOS

CMOS &

Inverters Technologies

yuRYy

Basic Electrical Properties of MOS Cents

> IDS-VDS relationships

> MOS transistor Threshold Voltage-VT

Trane conductance gm, gly

> Pass transistor

> NMOS Inverter, Resistive Load, Depleted.

Load, Psendo load, CMOS Inverters

analysis and desien

4. What isthe Integrated civenit Seale?

Show evaluation of logic complexity in intezrated circuits?

year ‘Chaifieation ‘No, of active

devices per chip

T8T I Seale Tetageaion (SS) Too

1966 | Madina Seale Integration (MSI) TOO-EOOT.

THT | Lange Seale Intezration UST) TOE TOOT

Ta Tay args Seale Tnteraton WES aga

S50 | Ula Lange Seale Integration TLS) | aga)

TO | Sper Large Seale Iteration SLED] 99%a0

0 “Extra Large Seale Integration (ELSI) 99 30°

TD aig Sale SA TCT] ait

‘What is Integrated Cirenit Seale?

+ Small-Scale Integration (881) ICs contained 2 few (n=10 to 100) logic gate

‘whore k=log m=log10 to log 100, k= J to=2, available for NAND gates, NOR

gates, and so on have few tens of transistors.

+ Madium-Scale Integration (MSI) increased the range of (a=100 to 1000, k=2 to

3) inteztated logic available to counters and sinuilar, larger scale, logic

‘Simetions

+ Large-seale integration (LSD) packed even large: losic functions (2=1000 to

20000, K=3 to), such as the first microprocessors, nto a single chip.

«Very Large-Scale Integration (VLSD) contain a large mumber of logic gztas

(2=20000 to 2000000, r= to 6), now offers 64-bit microprocessors, complete

with cache memory and floating-point arithmetic units—well over a muillion

transistors—on a single piace of silicon.

+ Ultra large Scale Integration (ULSD, contain saore large integrated circuit (a=

2,000,000 to 210,000,000, K=6 to 7) but most people stop atthe term VLSI,

ofberwise we have to start inventing mew words.

©. What is Cordon low prediction of integrated Cireuit?

(Cordon Maore’s Law

4 Whats the Integrated cinenit Seale?

Show evaluation of logic complexity in integrated circuits?

vex ‘Claeafcation Wo stactive

devices per chip

181 jraall Scale Tntezration (S51) TO

1586 ___[ Medium Seale Integration OS THETOOT

TST Large Seale Integration (CST) TOO TOOT

TSE very Large Scale Integration (VLSIY

TS ‘Ula Large Seale Tntexration (ULSI)

0] Super Cage Seale Integration STS1)

om ‘Extra Large Scale Intezration (ELST)

TH | Giga Seale Tneration (CEI

‘What is Integrated Cireuit Seale?

Small-Scale Integration (SSL) ICs contained a few (n=104o 100) logic gates,

where k-loz mlog10 to log 100, k= [to k=2, available for NAND gates, NOR,

gates, and 20 on— have fiw tons of transistors.

‘Medium-Seale Integration (MSD) increased the ranze of (n=100 fo 1000, I=2 40

3) integrated logic available to counters and similar, larger scale, legic

fimetions

‘Large-scale integration (LSI) packed even larger losic functions (o=1000 to

20000 , K=3 to 4), such as the first microprocessors, into a single chip.

Very Large Seale Integration (VLSI) contain a large number of logis estes

(=20000 to 2000000, I= to 6), now offars 64-bit microprocessors, complete

‘with cache memory and floating-point arithmetic units—wall over a million

‘transistors—on a single piece af silicon.

Ultra large Seale Integration (ULSI), contain more large integrated circuit

2,000,000 to 210,000,000, K=6 to 7) but most people stop at the tenm VLSI,

ctherwise we have to start inventing new words.

& What is Gordon low prediction of integrated Cireuit?

Gordon Moore's Law

Moore made the observation, and the prediction that the mimber of components being,

plagadom.2 chip was d times growth every three vears, and would contims to do so.

© Whatis the manufacturing of Integrated Circuits (IC) consists of Four Steps?

~ Cireuit Desien

+ Physical Desien

+ Fabrication

~ Packaging, Testing and Debugging

7 The steps of planar technology are:

* Silicon crystal growth

Thermal oxidation

Lithography:

Doping diffusion

‘Tonic implantation

sevitaxial

& Why Silicon not Ge?

‘When compured to germanium, silicon preferred for the following reasons:

~ Silhas- larger bandeap (1.1 2V for Si versus 0.66 pox. Ge)

- Sidevices can operate at'z higher temperature (130°Cv2 100°C),

- Intrinsic resistivity is hicher (2.3 x 10*@-em For Si vs 47 9-cm to Ge)

= 810; is more stable than GeO, which is also water-cohuble

~ Siis less costly.

HOWEVER:

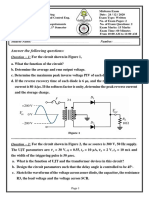

9 "The erystal orientation defines its electrical properties” Explain?

Devices fabricated on wafers with different orientations will exhibit different bekavior,

‘even ifthe material of both wafers is the same! The Miller indices isa notation

commonly used to refar to crystal planas. The three most common erystal crientations

‘used insilicom are chown in the following figure. Different interface density, current

sheer vis

density and electrical field.

(200) (110) aaa)

a

Si ceystal orientation for BIT (Bipolex Function Transistor) i (111),

Si crystal orientation for MOS is (100)

10- Explain Wafer Preparation(Silicon purification and 2-Single Crystal Gromth

) to obtain the final wafers

‘There are two main techniques for converting polyerystalline Si info sinele crystal

ingot Depand on orientation

+ (IU) for Bipolar Junction Transistor) and

+ (00) for MOS transistor,

tp obtain the final waftre we have five mamafictune prosase 22 follows:

1 Silicon purification

Single Crystal Growth

1. Silicon Purification

Toabtain pure silicon.

+ Silicon is grated from silica sand (SiO),

‘To separate Si fom the initial SiO: at high temperature (round 190°C)

$10; () +2C@) + +200 ©)

$i0:63) + C13) + Si+CO2 i)

‘This process results im 99% pure 8i inown as metallurgical-grade silicon (MGS),

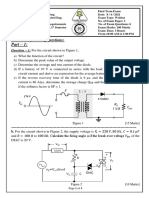

2-Single Crystal Growth,

Denessamahmed

G

‘To obtain single erystal wafer we have two method:

i: Caoehvalsksi <4.5° or crucible grown crystals (CZ erystale).,

jg manufacturing single erystale for large wafers

Si loat 2one or FZ crystals

11- Explain Grochralshisinele cotal exomth? (in the BOOK)

= The famace bated shove 1500a C, since Simsting poet s 1412 5C,

~~ Aprecisaly oriented rod: mounted seed crystal dipped imto the molten Silicou.

‘The seed crystals rod slowly pulled upwards and rotated simaltaneously. The furnace

vofated inthe direction oppose to tha crys puller.

~ The molten Si sticks tothe seed cystel nd stars to solidify withthe same oriartation a:

the seed cystal is withdraw,

+ Thay, asingla aystal ingot chained

> CZ process commonly used. for commercial suberate

Aatiloettes

+ Rowing

chuck

RE Heatag calls

cruete

oocoones

900000000

Apa ‘S.mannted vertically side a chamber, with the single crystal

seed of desired orientation,

- The rod is under vacuum or filled of am inert gas furnace

~ A radio frequency (RF) coil iy used to melt aloug the length of the rod, starts from the

fused region, containing the seed, and travels up, as shown in figure.

= Impurities in che molten region stay in the molten region rather than be incorporated

{into the solidified region, thus allowing a very pure single crystal region

~ When the molten rerion solidifies, it has the same orientation as the seed.

Armed

Sheeritl

Insert Gas

(intet Argon)

|

[> Floatzene puiting.

fj) see

Hh

Ey cau stid

<>

‘13. Discuss wafer size

Wafer Size

‘The ingot is thon szwm 35 into thin vrafix slicas, each of which will be subjected to

further etching and polishing until it is ready for use as substrates for VLSI

fabrication

Linch @5 mm)

Zinch (61 mum). Thickness 275 um.

3-inch (76 mm). Thickness 375 pum.

4-ineh (100 mm). Thickness 5

-inch (130 mm) or 12 mm (4,9 inch). Thickness 625 pum.

150 mum (£.9 inch, usually referred to as "6 inch"), Thickness 675 jum.

200 mim (7.9 inch, usually referred to as "§ inch"). Thickness 725 um,

300 mim (11.8 inch, usually referred to as "12 inch". Thickness 775 um.

450 mum (17.7 inch, usually referred to as "18 inch"). Thickness 925 ym

(expected).

ees

414 Calculate the theoretical value of yin silicon at room temperature, Calculate the value

of uin silicon at room temperature (200 2).

Where Eg =1.12 eV.

From The Text book:

rz)

BT exp 52 Cat an

Aly

was

= BP esp( 22) cart

" Par)

Where Es = semiconductor bandgap energy in eV (electron Volts)

‘Ke Boltamam’s constant, §.622 10° eVK

+ absolute temperature, K

‘B= Material- dependent parameter, 1.08 x10" K”. Cus* for $i.

‘Unknowns: Intrinsic cartier concentration ri,

Approach: Calculate ad by evaluating Eq (2.1).

Assumptions: T= 300K 3troom temperature

magitgiagtn an

108 m0 a cavty300 1 ap|

e ieee coorcar

Feed

pe dazassxtn® fer

16 Find the mobility and resistivity of intrinsic silicon at 400K and classify it as an

insulator, semiconductor, or conductor B=1.08 x10”, F=100 V/Cm, v- =4.3x1 0°

Cenlsee , Where Ee = 1.42 eV and vy =2100 Cure

Auewees: mobility values (a= 4300 cma’/s and_Up=2100 em’. , 1480.0 em,

semiconductor,

* Caleulate the resistivity of intrinsic silicom at £0 K if the electron mobility is 6500

cem/V' - s and the hole mobility is 2000 cm'/V - s. Classify the material.

‘Soeects) vist

Answer: 1.69 x 10" O- em, insulator

‘From the text book

o = 6.futs +e.) deem}

Solution:

‘

43x10 C15 yagget

1007 cm 5

‘ 2

”, Ixt0'cm/s _ 5 gmt

£ 100K Jom s

s.40x10"/em® | n,-2.32x107 fem"

08x10" (400) exp] —— Et? _

62x10" (400)

pele ei tus em

© 1.60x10"|(2.32x10 1350) + (2.32x10"\$00)|

a112

8.62x10°(50)

34810 | cn?

1,08s10"/50)° “|

pale «1.60310 em

> isa + [ao ) 2000)

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5823)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (898)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (823)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Mazen Mohamed RezkDocument18 pagesMazen Mohamed RezkMaher Gomaa IsmaeelNo ratings yet

- Midterm Exam Model 2Document2 pagesMidterm Exam Model 2Maher Gomaa IsmaeelNo ratings yet

- Quiz 1 - 1Document2 pagesQuiz 1 - 1Maher Gomaa IsmaeelNo ratings yet

- Midterm Exam Model 2 - Answer ModelDocument4 pagesMidterm Exam Model 2 - Answer ModelMaher Gomaa IsmaeelNo ratings yet

- Quiz 1 - 1 Model AnswerDocument2 pagesQuiz 1 - 1 Model AnswerMaher Gomaa IsmaeelNo ratings yet

- Midterm Exam Model 1Document2 pagesMidterm Exam Model 1Maher Gomaa IsmaeelNo ratings yet

- Midterm Exam Model 1 - Answer ModelDocument3 pagesMidterm Exam Model 1 - Answer ModelMaher Gomaa IsmaeelNo ratings yet

- Final Exam تخلفات - Part 1Document3 pagesFinal Exam تخلفات - Part 1Maher Gomaa IsmaeelNo ratings yet

- Final Exam تخلفات - Model Answer - Part 1Document6 pagesFinal Exam تخلفات - Model Answer - Part 1Maher Gomaa IsmaeelNo ratings yet