Professional Documents

Culture Documents

Buses and Network Topologies

Buses and Network Topologies

Uploaded by

Aakriti DubeyCopyright:

Available Formats

You might also like

- Dynamic Interconnection Networks Buses: CEG 4131 Computer Architecture III Miodrag BolicDocument27 pagesDynamic Interconnection Networks Buses: CEG 4131 Computer Architecture III Miodrag BolicSreekanth PagadapalliNo ratings yet

- PDF ICT114-Sem5Document52 pagesPDF ICT114-Sem5Shirley LohNo ratings yet

- Computer Organization: Lec # 9: Bus System Bnar MustafaDocument29 pagesComputer Organization: Lec # 9: Bus System Bnar Mustafazara qojo (زارا)No ratings yet

- CSCI 4717/5717 Computer Architecture Buses - Common CharacteristicsDocument9 pagesCSCI 4717/5717 Computer Architecture Buses - Common CharacteristicsAsjsjsjsNo ratings yet

- Computer Architeture Bus StructureDocument33 pagesComputer Architeture Bus StructureJbr RaheemNo ratings yet

- CH 03 p2 BusStructureDocument37 pagesCH 03 p2 BusStructureAnanda Haykel IskandarNo ratings yet

- Asynchronous Buses: Handshake Protocol Between A Master and A Slave DeviceDocument20 pagesAsynchronous Buses: Handshake Protocol Between A Master and A Slave Deviceiamvijay_123No ratings yet

- Interfacing Processors and Peripherals: CS151B/EE M116C Computer Systems ArchitectureDocument31 pagesInterfacing Processors and Peripherals: CS151B/EE M116C Computer Systems ArchitecturetinhtrilacNo ratings yet

- Cache CoherenceDocument39 pagesCache Coherencevivek srivastavNo ratings yet

- CO2202 L13 MultiProcessorDocument31 pagesCO2202 L13 MultiProcessorvidsa2002No ratings yet

- Unit 15 Bus StructureDocument32 pagesUnit 15 Bus StructureRennie KawanguNo ratings yet

- Regulation - 2018 (CBCS Scheme) 18CS733-Advanced Computer ArchitectureDocument48 pagesRegulation - 2018 (CBCS Scheme) 18CS733-Advanced Computer ArchitectureBharath N Reddy100% (1)

- 03-Bus-Bus Sistem (5-6)Document28 pages03-Bus-Bus Sistem (5-6)Viranata DarmaNo ratings yet

- System Bus in Computer Architecture: Goran Wnis Hama AliDocument34 pagesSystem Bus in Computer Architecture: Goran Wnis Hama AliGoran WnisNo ratings yet

- CS716 Advanced Computer Networks: by Dr. Amir QayyumDocument40 pagesCS716 Advanced Computer Networks: by Dr. Amir QayyumMr HaseebNo ratings yet

- Computer ArchitectureDocument31 pagesComputer ArchitectureFaisal ShehzadNo ratings yet

- 03 On-Chip Bus PDFDocument54 pages03 On-Chip Bus PDFAnnapurna KamadiNo ratings yet

- Computer Organization, Bus StructureDocument7 pagesComputer Organization, Bus StructureNaresh MundraNo ratings yet

- AVR Memory Mapped I-ODocument16 pagesAVR Memory Mapped I-OEmin KültürelNo ratings yet

- ACA Mod 3Document45 pagesACA Mod 3avi003No ratings yet

- Aca 1.2Document60 pagesAca 1.2Abhijeet Kumar SinghNo ratings yet

- 04 BusDocument23 pages04 BusAnonymous uUFY09No ratings yet

- T3 Serial CommunicationsDocument67 pagesT3 Serial Communicationschaudhary kiranNo ratings yet

- 2 02 - Serial Bus Communication ProtocolsDocument62 pages2 02 - Serial Bus Communication ProtocolsChristy PollyNo ratings yet

- Lecture 9 - Multimedia Buses - Inter-IC Sound (I2S), Domestic DIgital Bus (D2B), Media Oriented System Transport (MOST)Document20 pagesLecture 9 - Multimedia Buses - Inter-IC Sound (I2S), Domestic DIgital Bus (D2B), Media Oriented System Transport (MOST)김건정No ratings yet

- 02 - Lecture - part2-INDocument34 pages02 - Lecture - part2-INAhmedNo ratings yet

- Direct Memory AccessDocument26 pagesDirect Memory AccessEswin AngelNo ratings yet

- Microprocessor & Computer Architecture (Μpca) : Unit 4: Usb, Pci, Scsi,Amba And Asb Bus ArchitectureDocument12 pagesMicroprocessor & Computer Architecture (Μpca) : Unit 4: Usb, Pci, Scsi,Amba And Asb Bus ArchitecturePranathi PraveenNo ratings yet

- Input Output Organization Computer Architecture Organization NotesDocument49 pagesInput Output Organization Computer Architecture Organization Notesyguide97No ratings yet

- Lecture 2Document27 pagesLecture 2Mohsin AliNo ratings yet

- Lecture 2 - Bus Architecture, Types of BusesDocument29 pagesLecture 2 - Bus Architecture, Types of BusesHarsh OjhaNo ratings yet

- William Stallings Computer Organization and Architecture 6 Edition System BusesDocument34 pagesWilliam Stallings Computer Organization and Architecture 6 Edition System BusesShakeel AwanNo ratings yet

- LAN Part1Document32 pagesLAN Part1fares moradNo ratings yet

- Interconnection Networks: Prof. Varsha Poddar Department of CSEDocument18 pagesInterconnection Networks: Prof. Varsha Poddar Department of CSEArghasree BanerjeeNo ratings yet

- Transmission Modes: CECS 474 Computer Network InteroperabilityDocument13 pagesTransmission Modes: CECS 474 Computer Network InteroperabilityRatnakar BabuNo ratings yet

- DQDBDocument10 pagesDQDBAniket RajputNo ratings yet

- Switching and Forwarding: OutlineDocument25 pagesSwitching and Forwarding: OutlineGokulnath ReddyNo ratings yet

- 20 IoDocument21 pages20 IoKarthi KeyanNo ratings yet

- FALLSEM2021-22 ECE3004 TH VL2021220101856 Reference Material I 20-10-2021 Module 5 - 3 DMADocument31 pagesFALLSEM2021-22 ECE3004 TH VL2021220101856 Reference Material I 20-10-2021 Module 5 - 3 DMABharath P NairNo ratings yet

- Computer Organization and ArchitectureDocument25 pagesComputer Organization and ArchitectureNeel RavalNo ratings yet

- Data Comn and Computer NWDocument47 pagesData Comn and Computer NWpurushothama1970No ratings yet

- Io BusesDocument56 pagesIo Buseslalokew375No ratings yet

- USB Universal Serial BusDocument36 pagesUSB Universal Serial BusSuman PatraNo ratings yet

- 8051 Serial CommunicationDocument28 pages8051 Serial CommunicationDrWhoFNo ratings yet

- Multivibrators: The Generators of Rectangular WaveformsDocument20 pagesMultivibrators: The Generators of Rectangular Waveformsgeet_battaNo ratings yet

- Ecs 401 - Computer Organization Unit - I: BusesDocument8 pagesEcs 401 - Computer Organization Unit - I: BusesSannu KumarNo ratings yet

- Week 3Document28 pagesWeek 3shahzadjaffarNo ratings yet

- Interconnection Structures: Collection of Paths Connecting Various Modules Is Called As Interconnection StructureDocument22 pagesInterconnection Structures: Collection of Paths Connecting Various Modules Is Called As Interconnection Structuredomainname9No ratings yet

- CSDBDocument23 pagesCSDBSBRNo ratings yet

- Asynchronous and Synchronous TransmissionDocument18 pagesAsynchronous and Synchronous TransmissionPiyush Suthar100% (1)

- Network Layer Delivery, Forwarding, and Routing: Computer Networks 22-1Document31 pagesNetwork Layer Delivery, Forwarding, and Routing: Computer Networks 22-1Karan MaanNo ratings yet

- Visit:: Join Telegram To Get Instant Updates: Contact: MAIL: Instagram: Instagram: Whatsapp ShareDocument43 pagesVisit:: Join Telegram To Get Instant Updates: Contact: MAIL: Instagram: Instagram: Whatsapp Shareomeshwar vNo ratings yet

- ACFrOgBUHfSs5JJq8qhMAidgxGlhI1PVhDENxJ5Nvvf40LLrXAfXbAyXJvb16wu0NpVGnPnIEmvas8EAzCMG6hBW3FrQm4u33xPLThfDWODff8 jHUC-N9Jgo3XEpPc PDFDocument76 pagesACFrOgBUHfSs5JJq8qhMAidgxGlhI1PVhDENxJ5Nvvf40LLrXAfXbAyXJvb16wu0NpVGnPnIEmvas8EAzCMG6hBW3FrQm4u33xPLThfDWODff8 jHUC-N9Jgo3XEpPc PDFshifa khanNo ratings yet

- Lecture 10Document22 pagesLecture 10Abraham GadissaNo ratings yet

- External MemoryDocument73 pagesExternal Memoryvivek srivastavNo ratings yet

- USB Universal Serial Bus: Omid Fatemi Interface DesignDocument47 pagesUSB Universal Serial Bus: Omid Fatemi Interface DesigndilinipereraNo ratings yet

- Lec21 NetworkingDocument26 pagesLec21 Networkingapi-3761983No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Input Output TechniquesDocument65 pagesInput Output Techniquesvivek srivastavNo ratings yet

- Cache CoherenceDocument39 pagesCache Coherencevivek srivastavNo ratings yet

- External MemoryDocument73 pagesExternal Memoryvivek srivastavNo ratings yet

- Memory Subsystem and Memory HierarchyDocument44 pagesMemory Subsystem and Memory Hierarchyvivek srivastavNo ratings yet

- User Manual For LightBurnDocument11 pagesUser Manual For LightBurnLucas BritoNo ratings yet

- Acuson Aspen - Configuring The Aspen™ SystemDocument16 pagesAcuson Aspen - Configuring The Aspen™ SystemHarold MartinezNo ratings yet

- 2023 09 12T19 07 07 - R3dlogDocument4 pages2023 09 12T19 07 07 - R3dlogAgolenNo ratings yet

- IBM 5155 5160 Technical Reference 6280089 MAR86Document422 pagesIBM 5155 5160 Technical Reference 6280089 MAR86Luis TavisNo ratings yet

- Specification For ICT EquipmentsDocument21 pagesSpecification For ICT EquipmentsHannah Esey Aquino PaquinNo ratings yet

- Important Questions of Information Technology BBA & B.Com With AnswersDocument60 pagesImportant Questions of Information Technology BBA & B.Com With AnswersRishit GoelNo ratings yet

- Ebox4300 SpecDocument1 pageEbox4300 Spechaiso25No ratings yet

- Computer Assembly: Department of Computer Science, RUPPDocument28 pagesComputer Assembly: Department of Computer Science, RUPPOudom 22No ratings yet

- Partition Entries (LBA 2-33)Document2 pagesPartition Entries (LBA 2-33)scribdbookdlNo ratings yet

- Part of System UnitDocument35 pagesPart of System UnitEd ManalangNo ratings yet

- Memory Organization CAODocument11 pagesMemory Organization CAOArslan AliNo ratings yet

- HP-UX - Boot Time Troubleshooting - FrankieDocument3 pagesHP-UX - Boot Time Troubleshooting - Frankieachilles7No ratings yet

- 2U Firmware Programing LPC2387 PDFDocument5 pages2U Firmware Programing LPC2387 PDFAntoni MonteroNo ratings yet

- Brosur Wincom 2023Document4 pagesBrosur Wincom 2023Saeful FahmiNo ratings yet

- Additional Programming Software Instructions VXR-7000Document2 pagesAdditional Programming Software Instructions VXR-7000bbarinkNo ratings yet

- stm32f10x PWRDocument6 pagesstm32f10x PWRaykut ulusanNo ratings yet

- CP1E CPU Unit Software Users ManualDocument400 pagesCP1E CPU Unit Software Users ManualLoghanathan Issakkiramamurthy100% (1)

- Acer EmachinesDocument86 pagesAcer EmachinesOleg Garcia KarobaNo ratings yet

- Go4Mobility Accessories For Tablet Kiosk Sahara Slate and Netslate Tablet PcsDocument23 pagesGo4Mobility Accessories For Tablet Kiosk Sahara Slate and Netslate Tablet Pcsjbloggs2007No ratings yet

- Hbjc365f3a 2930 B SeriesDocument2 pagesHbjc365f3a 2930 B SeriesbelNo ratings yet

- B450M Pro4Document93 pagesB450M Pro4santiagoNo ratings yet

- Apple Management ProjectDocument18 pagesApple Management ProjectAyushmaan Gurung100% (1)

- uCOS TheoryDocument5 pagesuCOS Theoryabhinav.gamerNo ratings yet

- N50 Implen NanoPhotometer Data SheetDocument2 pagesN50 Implen NanoPhotometer Data SheetZhang NickNo ratings yet

- Booting and PartitioningDocument9 pagesBooting and PartitioningKusiima John BaptistNo ratings yet

- حلول الاختبارDocument32 pagesحلول الاختبارساره احمدNo ratings yet

- NASM: Data and Bss Examples and Sample Problems: Machine-Level and Systems ProgrammingDocument41 pagesNASM: Data and Bss Examples and Sample Problems: Machine-Level and Systems Programmingemnet81No ratings yet

- Instructions To CandidatesDocument17 pagesInstructions To Candidatessivakumar67538No ratings yet

- 4 Computer-Programming-CS101Document12 pages4 Computer-Programming-CS101Muhammad Abuzar KhanNo ratings yet

- Cache Memory MappingDocument8 pagesCache Memory MappingAman DubeyNo ratings yet

Buses and Network Topologies

Buses and Network Topologies

Uploaded by

Aakriti DubeyCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Buses and Network Topologies

Buses and Network Topologies

Uploaded by

Aakriti DubeyCopyright:

Available Formats

BCS-29

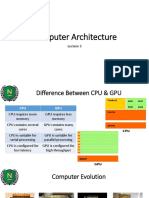

Advanced Computer Architecture

Interconnection Topologies and

Synchronization

Connecting Processors and Memories

• Buses

• Interconnection Networks

– Static Networks

– Dynamic Networks

M M M M M M M M

P P P P P P P P

Interconnection Network Interconnection Network

M M M M M M

Global Interconnection Network

M M M

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-2

Buses – Common Characteristics

• Multiple devices communicating over a single set of

wires

• Only one device can talk at a time or the message is

garbled

• Each line or wire of a bus can at any one time contain

a single binary digit. Over time, however, a sequence

of binary digits may be transferred

• These lines may and often do send information in

parallel

• A computer system may contain a number of

different buses

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-3

Buses – Structure

• Serial versus parallel

• Around 50-100 lines although it's possible to have as few as 3 or 4

• Lines can be classified into one of four groups

• Data lines

• Address Lines

• Control Lines

• Power

• Bus lines (parallel)

• Data

• Address

• Control

• Power

• Bus lines (serial)

• Data, address, and control are sequentially sent down single wire

• There may be additional control lines

• Power

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-4

Parallel Data Transmission

Receiver • Simultaneous

transmission

• Requires separate data

lines

• Bits must stay

synchronized

• Fast

• Expensive

One Word • Example: Printer

Transmitter connections

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-5

Serial Data Transmission

Receiver • Transfers one bit at a

time

• Requires only one data

line Bits must stay

synchronized

• Slow compared to

parallel transmission

One Word • Less Expensive

• Example: USB

Transmitter

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-6

Serial Data Communication

• Two basic types of Serial Data Communication:

• Synchronous Communication

• Asynchronous Communication

• Synchronous Communication

• Transmitter and receiver have their clocks synchronized

• Data rates are dependent on clock rates

• Continuously transmitting characters to remain in sync.

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-7

Asynchronous Communication

• NO synchronization

• No need to send idle characters

• Transmitter and receiver operate independently

• Transmitter can send data at any time

• Receiver is always ready to accept data

• Requires a start and stop bit to identify each byte of

data

• How does receiver know that data is arriving?

• If the line is idle, it is sending a constant ‚1‘ (mark state)

• The receiver is able to recognize a jump from ‚1‘ to ‚0‘

with the start bit and is alerted that data is about to be

sent.

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-8

Bus Operation

• Sending Data

• Obtain the use of the bus

• Transfer the data via the bus

• Possible acknowledgement

• Requesting Data

• Obtain the use of the bus

• Transfer the data request via the bus

• Wait for other module to send data

• Possible acknowledgement

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-9

Bus System

• A bus system is a hierarchy of buses connection

various system and subsystem components.

• Each bus has a complement of control, signal, and

power lines.

• There is usually a variety of buses in a system:

• Local bus – (usually integral to a system board) connects

various major system components (chips)

• Memory bus – used within a memory board to connect

the interface, the controller, and the memory cells

• Data bus – might be used on an I/O board or VLSI chip to

connect various components

• Backplane – like a local bus, but with connectors to which

other boards can be attached

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-10

System Bus (An Abstract View)

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-11

System Bus (A Technical View)

Most processors use a two-layer approach to

system bus communication.

FSB (Front Side Bus) for traditional system bus tasks

BSB (Back Side Bus) for CPU-memory cache tasks

The FSB is normally

implemented using two

sets of chips:

1. Northbridges and

2. Southbridge as

shown

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-12

System Bus (A Modern Example)

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-13

Bus Types

• Dedicated

• Separate data & address lines

• Time multiplexed

• Shared lines

• Address valid or data valid control line

• Advantage - fewer lines

• Disadvantages

• More complex control

• Degradation of performance

• Physical Dedication

• Physically separating buses and controlling them with a

"channel changer“

• Advantages – faster

• Disadvantages – physically larger

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-14

Bus Arbitration

• Listening to the bus is not usually a problem

• Talking on the bus is a problem – need arbitration to

allow more than one module to control the bus at

one time

• Centralised Arbitration

• Single hardware device controlling bus access – Bus

Controller/Arbiter

• May be part of CPU or separate

• Distributed Arbitration

• Each module may claim the bus

• Access control logic is on all modules

• Modules work together to control bus

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-15

Bus Arbitration and Control

• Bus arbitration is a process by which contention due to the

use of bus by more than one device is prevented. For

instance, a DMA transfer uses the same address, data, and

control lines used by the processor to communicate with the

memory and the I/O device. Therefore we need to have a

means to coordinate the use of these lines, to prevent 2

devices from initiating transfers at the same time.

• A device that is allowed to initiate data transfers on the bus is

called the master. Clearly, only one master can exists at a

time.

• When the master relinquishes the control, the other devices

can acquire this status. The bus arbiter performs the required

scheduling function.

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-16

DMA transfer arbitration

\BBSY

C

P

U \BR

DMA Ctrl1 DMA Ctrl2

BG1

BG2

• The above figure indicates a basic arrangement when the CPU contains

the bus arbiter circuitry.

• In this case, the processor is normally the bus master, unless it grants the

ownership to any of the devices.

• A DMA controller indicates that it needs to become a bus master by

activating the bus request line \BR (‘BR bar’). The signal on the BR line is a

logical OR of the requests from all the devices connected to it. When BR

line is activated.

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-17

Bus Timing

• Co-ordination of events on bus

• Synchronous – controlled by a clock

• Asynchronous – timing is handled by well-defined

specifications, i.e., a response is delivered within a

specified time after a request

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-18

Synchronous Bus Timing

• Events determined by clock signals

• Control Bus includes clock line

• A single 1-0 cycle is a bus cycle

• All devices can read clock line

• Usually sync on leading/rising edge

• Usually a single cycle for an event

• Analogy – Orchestra conductor with baton

• Usually stricter in terms of its timing requirements

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-19

Synchronous Bus Timing

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-20

Asynchronous Timing

• Devices must have certain tolerances to provide responses to

signal stimuli

• More flexible allowing slower devices to communicate on

same bus with faster devices.

• Performance of faster devices, however, is limited to speed of

bus

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-21

Asynchronous Timing – Read

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-22

Asynchronous Timing – Write

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-23

ISA BUS

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-24

Switched Networks

BUS

• Shared media

• Lower Cost

• Lower throughput

• Scalability poor

Switched Network

• Switched paths

• Higher cost

• Higher throughput

• Scalability better

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-25

Interconnection Networks

• Topology: who is connected to whom

• Direct / Indirect: where is switching done

• Static / Dynamic: when is switching done

• Circuit switching / packet switching: how are

connections established

• Store & forward / worm hole routing: how is the path

determined

• Centralized / distributed: how is switching controlled

• Synchronous/asynchronous: mode of operation

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-26

Direct and Indirect Networks

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-27

Static and Dynamic Networks

• Static Networks

• fixed point to point connections

• usually direct

• each node pair may not have a direct connection

• routing through nodes

• Dynamic Networks

• connections established as per need

• usually indirect

• path can be established between any pair of nodes

• routing through switches

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-28

Static Network Topologies

Non-uniform connectivity

Linear 2D-Mesh

Tree

Star

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-29

Static Networks Topologie

• Uniform connectivity

Ring

Torus

Fully Connected

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-30

Dynamic Networks

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-31

Crossbar Switch and Multiport Memory

• Single stage networks are sometimes called

re_circulating networks because data items may

have to pass through the single stage many times.

• The crossbar switch and the multiported memory

organization (seen later) are both single-stage

networks.

• This is because even if two processors attempted to

access the same memory module (or I/O device) at

the same time, only one of the requests is serviced

at a time.

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-32

Multistage Networks

• Multistage networks consist of multiple sages of

switch boxes, and should be able to connect any

input to any output.

• A multistage network is called blocking if the

simultaneous connections of some multiple input-

output pairs may result in conflicts in the use of

switches or communication links.

• A nonblocking multistage network can perform all

possible connections between inputs and outputs by

rearranging its connections.

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-33

Crossbar Networks

• Crossbar networks connect every input to every

output through a crosspoint switch.

• A crossbar network is a single stage, non-blocking

permutation network.

• In an n-processor, m-memory system, n m

crosspoint switches will be required. Each crosspoint

is a unary switch which can be open or closed,

providing a point-to-point connection path between

the processor and a memory module.

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-34

Crosspoint Switch Design

• Out of n crosspoint switches in each column of an n

m crossbar mesh, only one can be connected at a

time.

• Crosspoint switches must be designed to handle the

potential contention for each memory module.

• Each processor provides a request line, a read/write

line, a set of address lines, and a set of data lines to a

crosspoint switch for a single column.

• The crosspoint switch eventually responds with an

acknowledgement when the access has been

completed.

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-35

Schematic of a Crosspoint Switch

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-36

Multiport Memory

• Since crossbar switches are expensive, and not suitable for

systems with many processors or memory modules, multiport

memory modules may be used instead.

• A multiport memory module has multiple connections points

for processors (or I/O devices), and the memory controller in

the module handles the arbitration and switching that might

otherwise have been accomplished by a crosspoint switch.

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-37

Baseline Network

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-38

Benes Network

non-blocking

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-39

Switching Mechanism

• Circuit Switching (connection-oriented

communication)

• A circuit is established between the source and the

destination

• Packet Switching (connectionless communication)

• Information is divided into packets and each packet is sent

independently from node to node

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-40

Omega Networks

• N-input Omega networks, in general, have log2n stages, with the input stage

labeled 0.

• The inter-stage connection (ISC) pattern is a perfect shuffle.

• Routing is controlled by inspecting the destination address. When the i-th

highest order bit is 0, the 22 switch in stage i connects the input to the upper

output. Otherwise it connects the input to the lower output.

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-41

Blocking Effects

• Blocking exists in an Omega network when the requested permutation would

require that a single switch be set in two positions simultaneously.

• Obviously this is impossible, and requires that one of the permutation requests

be blocked and tried in a later pass.

• In general, with 22 switches, an Omega network can implement n n/2

permutations in a single pass. For n = 8, this is about 10% of all possible

permutations.

• In general, a maximum of log2n passes are needed for an n-input Omega

network.

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-42

Omega Broadcast

• An Omega network can be used to broadcast data to multiple destinations.

• The switch to which the input is connected is set to the broadcast position (input

connected to both outputs).

• Each additional switch (in later stages) to which an output is directed is also set

to the broadcast position.

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-43

Larger Switches

• Larger switches (more inputs and outputs, and more switching patterns) can be

used to build an Omega network, resulting in fewer stages.

• For example, with 44 switches, only log416 stages are required for a 16-input

switch.

• A k-way perfect shuffle is used as the ISC for an Omega network using k k

switches.

Dr P K Singh BCS-29 Advanced Computer Architecture BCS-29(!)-44

You might also like

- Dynamic Interconnection Networks Buses: CEG 4131 Computer Architecture III Miodrag BolicDocument27 pagesDynamic Interconnection Networks Buses: CEG 4131 Computer Architecture III Miodrag BolicSreekanth PagadapalliNo ratings yet

- PDF ICT114-Sem5Document52 pagesPDF ICT114-Sem5Shirley LohNo ratings yet

- Computer Organization: Lec # 9: Bus System Bnar MustafaDocument29 pagesComputer Organization: Lec # 9: Bus System Bnar Mustafazara qojo (زارا)No ratings yet

- CSCI 4717/5717 Computer Architecture Buses - Common CharacteristicsDocument9 pagesCSCI 4717/5717 Computer Architecture Buses - Common CharacteristicsAsjsjsjsNo ratings yet

- Computer Architeture Bus StructureDocument33 pagesComputer Architeture Bus StructureJbr RaheemNo ratings yet

- CH 03 p2 BusStructureDocument37 pagesCH 03 p2 BusStructureAnanda Haykel IskandarNo ratings yet

- Asynchronous Buses: Handshake Protocol Between A Master and A Slave DeviceDocument20 pagesAsynchronous Buses: Handshake Protocol Between A Master and A Slave Deviceiamvijay_123No ratings yet

- Interfacing Processors and Peripherals: CS151B/EE M116C Computer Systems ArchitectureDocument31 pagesInterfacing Processors and Peripherals: CS151B/EE M116C Computer Systems ArchitecturetinhtrilacNo ratings yet

- Cache CoherenceDocument39 pagesCache Coherencevivek srivastavNo ratings yet

- CO2202 L13 MultiProcessorDocument31 pagesCO2202 L13 MultiProcessorvidsa2002No ratings yet

- Unit 15 Bus StructureDocument32 pagesUnit 15 Bus StructureRennie KawanguNo ratings yet

- Regulation - 2018 (CBCS Scheme) 18CS733-Advanced Computer ArchitectureDocument48 pagesRegulation - 2018 (CBCS Scheme) 18CS733-Advanced Computer ArchitectureBharath N Reddy100% (1)

- 03-Bus-Bus Sistem (5-6)Document28 pages03-Bus-Bus Sistem (5-6)Viranata DarmaNo ratings yet

- System Bus in Computer Architecture: Goran Wnis Hama AliDocument34 pagesSystem Bus in Computer Architecture: Goran Wnis Hama AliGoran WnisNo ratings yet

- CS716 Advanced Computer Networks: by Dr. Amir QayyumDocument40 pagesCS716 Advanced Computer Networks: by Dr. Amir QayyumMr HaseebNo ratings yet

- Computer ArchitectureDocument31 pagesComputer ArchitectureFaisal ShehzadNo ratings yet

- 03 On-Chip Bus PDFDocument54 pages03 On-Chip Bus PDFAnnapurna KamadiNo ratings yet

- Computer Organization, Bus StructureDocument7 pagesComputer Organization, Bus StructureNaresh MundraNo ratings yet

- AVR Memory Mapped I-ODocument16 pagesAVR Memory Mapped I-OEmin KültürelNo ratings yet

- ACA Mod 3Document45 pagesACA Mod 3avi003No ratings yet

- Aca 1.2Document60 pagesAca 1.2Abhijeet Kumar SinghNo ratings yet

- 04 BusDocument23 pages04 BusAnonymous uUFY09No ratings yet

- T3 Serial CommunicationsDocument67 pagesT3 Serial Communicationschaudhary kiranNo ratings yet

- 2 02 - Serial Bus Communication ProtocolsDocument62 pages2 02 - Serial Bus Communication ProtocolsChristy PollyNo ratings yet

- Lecture 9 - Multimedia Buses - Inter-IC Sound (I2S), Domestic DIgital Bus (D2B), Media Oriented System Transport (MOST)Document20 pagesLecture 9 - Multimedia Buses - Inter-IC Sound (I2S), Domestic DIgital Bus (D2B), Media Oriented System Transport (MOST)김건정No ratings yet

- 02 - Lecture - part2-INDocument34 pages02 - Lecture - part2-INAhmedNo ratings yet

- Direct Memory AccessDocument26 pagesDirect Memory AccessEswin AngelNo ratings yet

- Microprocessor & Computer Architecture (Μpca) : Unit 4: Usb, Pci, Scsi,Amba And Asb Bus ArchitectureDocument12 pagesMicroprocessor & Computer Architecture (Μpca) : Unit 4: Usb, Pci, Scsi,Amba And Asb Bus ArchitecturePranathi PraveenNo ratings yet

- Input Output Organization Computer Architecture Organization NotesDocument49 pagesInput Output Organization Computer Architecture Organization Notesyguide97No ratings yet

- Lecture 2Document27 pagesLecture 2Mohsin AliNo ratings yet

- Lecture 2 - Bus Architecture, Types of BusesDocument29 pagesLecture 2 - Bus Architecture, Types of BusesHarsh OjhaNo ratings yet

- William Stallings Computer Organization and Architecture 6 Edition System BusesDocument34 pagesWilliam Stallings Computer Organization and Architecture 6 Edition System BusesShakeel AwanNo ratings yet

- LAN Part1Document32 pagesLAN Part1fares moradNo ratings yet

- Interconnection Networks: Prof. Varsha Poddar Department of CSEDocument18 pagesInterconnection Networks: Prof. Varsha Poddar Department of CSEArghasree BanerjeeNo ratings yet

- Transmission Modes: CECS 474 Computer Network InteroperabilityDocument13 pagesTransmission Modes: CECS 474 Computer Network InteroperabilityRatnakar BabuNo ratings yet

- DQDBDocument10 pagesDQDBAniket RajputNo ratings yet

- Switching and Forwarding: OutlineDocument25 pagesSwitching and Forwarding: OutlineGokulnath ReddyNo ratings yet

- 20 IoDocument21 pages20 IoKarthi KeyanNo ratings yet

- FALLSEM2021-22 ECE3004 TH VL2021220101856 Reference Material I 20-10-2021 Module 5 - 3 DMADocument31 pagesFALLSEM2021-22 ECE3004 TH VL2021220101856 Reference Material I 20-10-2021 Module 5 - 3 DMABharath P NairNo ratings yet

- Computer Organization and ArchitectureDocument25 pagesComputer Organization and ArchitectureNeel RavalNo ratings yet

- Data Comn and Computer NWDocument47 pagesData Comn and Computer NWpurushothama1970No ratings yet

- Io BusesDocument56 pagesIo Buseslalokew375No ratings yet

- USB Universal Serial BusDocument36 pagesUSB Universal Serial BusSuman PatraNo ratings yet

- 8051 Serial CommunicationDocument28 pages8051 Serial CommunicationDrWhoFNo ratings yet

- Multivibrators: The Generators of Rectangular WaveformsDocument20 pagesMultivibrators: The Generators of Rectangular Waveformsgeet_battaNo ratings yet

- Ecs 401 - Computer Organization Unit - I: BusesDocument8 pagesEcs 401 - Computer Organization Unit - I: BusesSannu KumarNo ratings yet

- Week 3Document28 pagesWeek 3shahzadjaffarNo ratings yet

- Interconnection Structures: Collection of Paths Connecting Various Modules Is Called As Interconnection StructureDocument22 pagesInterconnection Structures: Collection of Paths Connecting Various Modules Is Called As Interconnection Structuredomainname9No ratings yet

- CSDBDocument23 pagesCSDBSBRNo ratings yet

- Asynchronous and Synchronous TransmissionDocument18 pagesAsynchronous and Synchronous TransmissionPiyush Suthar100% (1)

- Network Layer Delivery, Forwarding, and Routing: Computer Networks 22-1Document31 pagesNetwork Layer Delivery, Forwarding, and Routing: Computer Networks 22-1Karan MaanNo ratings yet

- Visit:: Join Telegram To Get Instant Updates: Contact: MAIL: Instagram: Instagram: Whatsapp ShareDocument43 pagesVisit:: Join Telegram To Get Instant Updates: Contact: MAIL: Instagram: Instagram: Whatsapp Shareomeshwar vNo ratings yet

- ACFrOgBUHfSs5JJq8qhMAidgxGlhI1PVhDENxJ5Nvvf40LLrXAfXbAyXJvb16wu0NpVGnPnIEmvas8EAzCMG6hBW3FrQm4u33xPLThfDWODff8 jHUC-N9Jgo3XEpPc PDFDocument76 pagesACFrOgBUHfSs5JJq8qhMAidgxGlhI1PVhDENxJ5Nvvf40LLrXAfXbAyXJvb16wu0NpVGnPnIEmvas8EAzCMG6hBW3FrQm4u33xPLThfDWODff8 jHUC-N9Jgo3XEpPc PDFshifa khanNo ratings yet

- Lecture 10Document22 pagesLecture 10Abraham GadissaNo ratings yet

- External MemoryDocument73 pagesExternal Memoryvivek srivastavNo ratings yet

- USB Universal Serial Bus: Omid Fatemi Interface DesignDocument47 pagesUSB Universal Serial Bus: Omid Fatemi Interface DesigndilinipereraNo ratings yet

- Lec21 NetworkingDocument26 pagesLec21 Networkingapi-3761983No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Input Output TechniquesDocument65 pagesInput Output Techniquesvivek srivastavNo ratings yet

- Cache CoherenceDocument39 pagesCache Coherencevivek srivastavNo ratings yet

- External MemoryDocument73 pagesExternal Memoryvivek srivastavNo ratings yet

- Memory Subsystem and Memory HierarchyDocument44 pagesMemory Subsystem and Memory Hierarchyvivek srivastavNo ratings yet

- User Manual For LightBurnDocument11 pagesUser Manual For LightBurnLucas BritoNo ratings yet

- Acuson Aspen - Configuring The Aspen™ SystemDocument16 pagesAcuson Aspen - Configuring The Aspen™ SystemHarold MartinezNo ratings yet

- 2023 09 12T19 07 07 - R3dlogDocument4 pages2023 09 12T19 07 07 - R3dlogAgolenNo ratings yet

- IBM 5155 5160 Technical Reference 6280089 MAR86Document422 pagesIBM 5155 5160 Technical Reference 6280089 MAR86Luis TavisNo ratings yet

- Specification For ICT EquipmentsDocument21 pagesSpecification For ICT EquipmentsHannah Esey Aquino PaquinNo ratings yet

- Important Questions of Information Technology BBA & B.Com With AnswersDocument60 pagesImportant Questions of Information Technology BBA & B.Com With AnswersRishit GoelNo ratings yet

- Ebox4300 SpecDocument1 pageEbox4300 Spechaiso25No ratings yet

- Computer Assembly: Department of Computer Science, RUPPDocument28 pagesComputer Assembly: Department of Computer Science, RUPPOudom 22No ratings yet

- Partition Entries (LBA 2-33)Document2 pagesPartition Entries (LBA 2-33)scribdbookdlNo ratings yet

- Part of System UnitDocument35 pagesPart of System UnitEd ManalangNo ratings yet

- Memory Organization CAODocument11 pagesMemory Organization CAOArslan AliNo ratings yet

- HP-UX - Boot Time Troubleshooting - FrankieDocument3 pagesHP-UX - Boot Time Troubleshooting - Frankieachilles7No ratings yet

- 2U Firmware Programing LPC2387 PDFDocument5 pages2U Firmware Programing LPC2387 PDFAntoni MonteroNo ratings yet

- Brosur Wincom 2023Document4 pagesBrosur Wincom 2023Saeful FahmiNo ratings yet

- Additional Programming Software Instructions VXR-7000Document2 pagesAdditional Programming Software Instructions VXR-7000bbarinkNo ratings yet

- stm32f10x PWRDocument6 pagesstm32f10x PWRaykut ulusanNo ratings yet

- CP1E CPU Unit Software Users ManualDocument400 pagesCP1E CPU Unit Software Users ManualLoghanathan Issakkiramamurthy100% (1)

- Acer EmachinesDocument86 pagesAcer EmachinesOleg Garcia KarobaNo ratings yet

- Go4Mobility Accessories For Tablet Kiosk Sahara Slate and Netslate Tablet PcsDocument23 pagesGo4Mobility Accessories For Tablet Kiosk Sahara Slate and Netslate Tablet Pcsjbloggs2007No ratings yet

- Hbjc365f3a 2930 B SeriesDocument2 pagesHbjc365f3a 2930 B SeriesbelNo ratings yet

- B450M Pro4Document93 pagesB450M Pro4santiagoNo ratings yet

- Apple Management ProjectDocument18 pagesApple Management ProjectAyushmaan Gurung100% (1)

- uCOS TheoryDocument5 pagesuCOS Theoryabhinav.gamerNo ratings yet

- N50 Implen NanoPhotometer Data SheetDocument2 pagesN50 Implen NanoPhotometer Data SheetZhang NickNo ratings yet

- Booting and PartitioningDocument9 pagesBooting and PartitioningKusiima John BaptistNo ratings yet

- حلول الاختبارDocument32 pagesحلول الاختبارساره احمدNo ratings yet

- NASM: Data and Bss Examples and Sample Problems: Machine-Level and Systems ProgrammingDocument41 pagesNASM: Data and Bss Examples and Sample Problems: Machine-Level and Systems Programmingemnet81No ratings yet

- Instructions To CandidatesDocument17 pagesInstructions To Candidatessivakumar67538No ratings yet

- 4 Computer-Programming-CS101Document12 pages4 Computer-Programming-CS101Muhammad Abuzar KhanNo ratings yet

- Cache Memory MappingDocument8 pagesCache Memory MappingAman DubeyNo ratings yet