Professional Documents

Culture Documents

DLC Model I

DLC Model I

Uploaded by

EEE DEPT0 ratings0% found this document useful (0 votes)

15 views2 pagesThis document contains exam questions for a Digital Logic Circuits course. It is divided into three parts:

Part A contains 10 multiple choice questions worth 2 marks each, covering topics like fan in/fan out, number systems, logic gate types, shift registers, hazards, PROM, and VHDL.

Part B contains 5 questions worth 5-13 marks each, involving binary to gray code conversion, TTL NAND gate operation, full adder/subtractor design, demultiplexer design, JK flip-flop explanation, shift register types, PLA design, and asynchronous circuit design.

Part C contains 2 questions worth 15 marks each, about hazards in sequential circuits and 8 to 1 multiple

Original Description:

Original Title

dlc model i

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document contains exam questions for a Digital Logic Circuits course. It is divided into three parts:

Part A contains 10 multiple choice questions worth 2 marks each, covering topics like fan in/fan out, number systems, logic gate types, shift registers, hazards, PROM, and VHDL.

Part B contains 5 questions worth 5-13 marks each, involving binary to gray code conversion, TTL NAND gate operation, full adder/subtractor design, demultiplexer design, JK flip-flop explanation, shift register types, PLA design, and asynchronous circuit design.

Part C contains 2 questions worth 15 marks each, about hazards in sequential circuits and 8 to 1 multiple

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

0 ratings0% found this document useful (0 votes)

15 views2 pagesDLC Model I

DLC Model I

Uploaded by

EEE DEPTThis document contains exam questions for a Digital Logic Circuits course. It is divided into three parts:

Part A contains 10 multiple choice questions worth 2 marks each, covering topics like fan in/fan out, number systems, logic gate types, shift registers, hazards, PROM, and VHDL.

Part B contains 5 questions worth 5-13 marks each, involving binary to gray code conversion, TTL NAND gate operation, full adder/subtractor design, demultiplexer design, JK flip-flop explanation, shift register types, PLA design, and asynchronous circuit design.

Part C contains 2 questions worth 15 marks each, about hazards in sequential circuits and 8 to 1 multiple

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

You are on page 1of 2

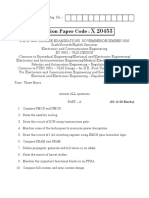

Reg No :

6214-MAHABARATHI ENGINEERING COLLEGE - CHINNASALEM

B.E./B.Tech. DEGREE EXAMINATION, OCT-2021

Third Semester / Electrical and Electronics Engineering

EE-8351 DIGITAL LOGIC CIRCUITS

(Regulation 2017)

Model EXAM -1

DATE: 15.11.2021(AN) Maximum Marks:100

TIME: 3.00 Hours

Answer ALL Questions

PART A — (10 × 2 = 20 Marks)

1. Define Fan in and Fan out.

2. Convert (19.625)10 to Binary,Octal and Hexadecimal Number System.

3. Define min term and max term.

4. Differentiate decoder and demultiplexer.

5. Give the design steps for synchronous sequential circuit.

6. What are the types of Shift Registers?

7. Define hazards and its types.

8. Define PROM.

9. What is VHDL.

10. Write the program for half adder using in VHDL.

PART-B (13*5=65 Marks)

11. a)i)Explain about binary to gray code conversion. (06)

ii)Explain the operation of TTL NAND gate with a neat circuit diagram. (07)

(OR)

b) Name and Briefly Explain About Characteristics Of Digital IC’s. (13)

12.a) Design and implement the full adder and full subtractor circuit using only NAND Gates.

(OR)

b) Design and implement 1 to 8 demultiplexer using AND Gates. (13)

13.a) With neat digram .explain about JK flip-flop. (13)

(OR)

b)Explain about different types of shift registers. (13)

14.a)Draw the block diagram of a PLA device and briefly explain each block. . (13)

(OR)

b).summarize the design procedure for asynchronous sequential circuit. (13)

15.a)Explain the structure and working principles of TTL based Totem-pole output

configuration. (13)

(OR)

b) Write a VHDL code to realize a half adder using behavioral modeling and structural modeling

(13)

PART-C (15*1=15 Marks)

16. a)Illustrate about hazards in sequential circuits and the steps to avoid hazards in it. (15)

(OR)

b) Design and implement 8 to 1 multiplexer using AND Gates (15)

Reg No :

6214-MAHABARATHI ENGINEERING COLLEGE - CHINNASALEM

B.E./B.Tech. DEGREE EXAMINATION, OCT-2021

Third Semester

Electrical and Electronics Engineering

EE-8351 DIGITAL LOGIC CIRCUITS

(Regulation 2017)

Common Internal Assessment Test-I

DATE: 22 .10.2021(AN) Maximum Marks: 50

TIME: 1.30 Hours

Answer ALL Questions

PART A — (09 × 2 = 18 Marks)

1. List out the Numbering System.

2. Convert (19.625)10 to Binary,Octal and Hexadecimal Number System.

3. Convert (3A.2F)16 to Decimal,Binary and Octal Number System.

4. Convert (1100.1011)2 to Decimal, Hexadecimal and Octal Number System.

5. How you will represent signed binary numbers in computers?

6. Give A=1010 B=1111 perform (a)A-B (b)B-A using 1’s complement.

7. Using 2’s Complement Perform (42)10 – (68)10.

8. Define Fan in and Fan out.

9. Define Noise Margin Noise Immunity.

PART-B (10*2=20 Marks)

10. a) Explain About Different Types Of Logic Gates. (10)

(OR)

b) Briefly Explain About Characteristics Of Digital IC’s. (10)

11.a) Briefly Explain About Different Types Of Bipolar Logic Families. (10)

(OR)

b) Briefly Explain About Different Types Of Mos Families.(10)

PART-C (12*1=12 Marks)

12. Explain About Different Types Of Numbering System. Give Example For Each. (12)

You might also like

- Structured Digital System Design Question PaperDocument1 pageStructured Digital System Design Question PaperSatish Bojjawar50% (2)

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- Question Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodeDocument2 pagesQuestion Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodePrabu KumarNo ratings yet

- Nov - Dec 2021Document3 pagesNov - Dec 2021Pandyselvi BalasubramanianNo ratings yet

- QBank DPSD cs2202Document6 pagesQBank DPSD cs2202kunarajNo ratings yet

- Mr3492 Esp Model QN PaperDocument3 pagesMr3492 Esp Model QN PaperKeerthana SahadevanNo ratings yet

- Vlsi QP 21,22Document11 pagesVlsi QP 21,22Arunitha ArulnathanNo ratings yet

- B Tech. Degree Examination, November 20: Answer Al Questions. Uest On Arr Es 3 MarksDocument2 pagesB Tech. Degree Examination, November 20: Answer Al Questions. Uest On Arr Es 3 MarksVargheseMartinNo ratings yet

- EC2354 - VLSI DesignDocument2 pagesEC2354 - VLSI DesignSriramNo ratings yet

- R5 210504 Digital Logic DesignDocument1 pageR5 210504 Digital Logic DesignsivabharathamurthyNo ratings yet

- 9A04504 Digital IC Applications6Document4 pages9A04504 Digital IC Applications6subbuNo ratings yet

- Bharath Niketan Engineering College: HoursDocument2 pagesBharath Niketan Engineering College: HourseeeNo ratings yet

- Digital ElectronicsDocument7 pagesDigital ElectronicsAlakaaa PromodNo ratings yet

- Question Paper Code: X10348: Reg. NoDocument2 pagesQuestion Paper Code: X10348: Reg. NoJaikumar RajendranNo ratings yet

- MechatronicsDocument2 pagesMechatronicsSaravanan MathiNo ratings yet

- Nov - Dec 2018Document5 pagesNov - Dec 2018Pandyselvi BalasubramanianNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)kenny kannaNo ratings yet

- DSP Integrated Circuits 3Document3 pagesDSP Integrated Circuits 3brindkowsiNo ratings yet

- D G192071 Pages: 2: Answer Any Three Full Questions, Each Carries 10 MarksDocument2 pagesD G192071 Pages: 2: Answer Any Three Full Questions, Each Carries 10 MarksvivekNo ratings yet

- EE3302-DLC MODEL QP UpdatedDocument3 pagesEE3302-DLC MODEL QP UpdatedKeerthana SahadevanNo ratings yet

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDocument3 pagesEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYANo ratings yet

- FPGA Based System DesignDocument2 pagesFPGA Based System Designammayi9845_930467904No ratings yet

- Ec 1401 Vlsi DesignDocument2 pagesEc 1401 Vlsi DesignsubhazNo ratings yet

- Question Paper CodeDocument2 pagesQuestion Paper CodeDinesh SrinivasanNo ratings yet

- DPSDDocument24 pagesDPSDdigital1206No ratings yet

- 08ab303 - Digital Logic CircuitsDocument3 pages08ab303 - Digital Logic CircuitsChandru RamaswamyNo ratings yet

- Question Paper Code:: Y Abcababc + + +Document3 pagesQuestion Paper Code:: Y Abcababc + + +karthick VijayanNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document3 pagesQuestion Paper Code:: (10×2 20 Marks)rajkumarsac100% (1)

- Question Paper Code:: (10 2 20 Marks)Document2 pagesQuestion Paper Code:: (10 2 20 Marks)AbdulAzizNo ratings yet

- Ae Paper GtuDocument9 pagesAe Paper GtuMehta HarshNo ratings yet

- Stucor QP Ee8551Document8 pagesStucor QP Ee8551NagendranNo ratings yet

- Erts - Model 1Document3 pagesErts - Model 1Ece DeptNo ratings yet

- Answer All Questions PART A - (5 2 10)Document3 pagesAnswer All Questions PART A - (5 2 10)Anonymous NV7nnJDeNo ratings yet

- 6C0065Document4 pages6C0065Joshua prabuNo ratings yet

- Nov 2019Document6 pagesNov 2019ponniNo ratings yet

- Smart Materials, Sensors and ActuatorsDocument2 pagesSmart Materials, Sensors and ActuatorsmanojNo ratings yet

- 2EC6302-Digital Electronics QBDocument12 pages2EC6302-Digital Electronics QBSurendar PNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)Shri VarshaNo ratings yet

- Stucor Qp-Me8791Document6 pagesStucor Qp-Me8791sramalingam288953No ratings yet

- 22323-2019-Winter-Question-Paper (Msbte Study Resources)Document3 pages22323-2019-Winter-Question-Paper (Msbte Study Resources)Parth patkarNo ratings yet

- Digital Nov 07Document6 pagesDigital Nov 07skssushNo ratings yet

- JanuaryFebruary 2021Document1 pageJanuaryFebruary 2021vishwatejkachu944No ratings yet

- Vlsi Model 4-QPDocument2 pagesVlsi Model 4-QPsanthoshNo ratings yet

- 2008 Anna UniversityDocument1 page2008 Anna UniversitysasitsnNo ratings yet

- Computer Architecture Question BankDocument10 pagesComputer Architecture Question BankMalk Malik0% (1)

- DLC Series IaDocument1 pageDLC Series IaAnusha NatarajanNo ratings yet

- Cs PaperDocument37 pagesCs PaperAshish BokilNo ratings yet

- Department of Ece Model Examination Vl9261 - Asic Design: PART B - (5 × 16 80 Marks)Document2 pagesDepartment of Ece Model Examination Vl9261 - Asic Design: PART B - (5 × 16 80 Marks)Anandhi SrinivasanNo ratings yet

- VL 7201 Cad For Vlsi CircuitsDocument2 pagesVL 7201 Cad For Vlsi CircuitsAnonymous NV7nnJDeNo ratings yet

- Q 6Document3 pagesQ 6Saranya MohanNo ratings yet

- Cao Previous QNDocument9 pagesCao Previous QNanusha deviNo ratings yet

- 15A04509 Linear & Digital IC ApplicationsDocument1 page15A04509 Linear & Digital IC ApplicationsMODERN TELUGAMMAYINo ratings yet

- Sathyabama: Register NumberDocument3 pagesSathyabama: Register NumberBoopalanElumalaiNo ratings yet

- Second Internal Assessment Test, March 2017: B.E./B.TechDocument1 pageSecond Internal Assessment Test, March 2017: B.E./B.TechChristoNo ratings yet

- Digital Electronics Exam 2012Document7 pagesDigital Electronics Exam 2012Meluami J. ParoriNo ratings yet

- Ee2255 Digital Logic CircuitsDocument3 pagesEe2255 Digital Logic CircuitsecessecNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionFrom EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionNo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- DSP Model-2Document3 pagesDSP Model-2EEE DEPTNo ratings yet

- DSP Iat-1Document2 pagesDSP Iat-1EEE DEPTNo ratings yet

- DSPDocument1 pageDSPEEE DEPTNo ratings yet

- DSP (Ee8591) - Model 2Document2 pagesDSP (Ee8591) - Model 2EEE DEPTNo ratings yet

- DSP Model-1Document2 pagesDSP Model-1EEE DEPTNo ratings yet

- Xo 91Document2 pagesXo 91Philip El ProfiNo ratings yet

- ECG Circuit PDFDocument6 pagesECG Circuit PDFarduino signaux cardiaquesNo ratings yet

- Ktechlab: George John 11 June, 2007Document39 pagesKtechlab: George John 11 June, 2007Skain RkNo ratings yet

- VCO, PLL Principles and ApplicationsDocument9 pagesVCO, PLL Principles and ApplicationsPrasitNo ratings yet

- Mains Interruption Counter With Indicator Circuit DiagramDocument6 pagesMains Interruption Counter With Indicator Circuit DiagramSelvy SalfitriNo ratings yet

- Equation Chapter (Next) Section 1Document26 pagesEquation Chapter (Next) Section 1Aidan PinardNo ratings yet

- AM Demodulator MC1496Document5 pagesAM Demodulator MC1496John MensahNo ratings yet

- Taller de CircuitosDocument9 pagesTaller de CircuitosSteven SantosNo ratings yet

- Gen - Phy2 12-q3 Slm-13-Kirchoff's Law Student'sDocument10 pagesGen - Phy2 12-q3 Slm-13-Kirchoff's Law Student'sjoshandersonbutoy08No ratings yet

- 7912CT EtcDocument13 pages7912CT EtcCuong TranNo ratings yet

- Exper6 - 2012 D-Type JK-type Flip-FlopsDocument4 pagesExper6 - 2012 D-Type JK-type Flip-FlopsMELANIE LLONANo ratings yet

- 144520177651761 (1)Document4 pages144520177651761 (1)Ashish MalikNo ratings yet

- Integrated CircuitsDocument204 pagesIntegrated CircuitsvipinNo ratings yet

- Notch: Sallen-Key Double T (Active Filter)Document4 pagesNotch: Sallen-Key Double T (Active Filter)LUIS EDUARDO OROZCO QUINTERONo ratings yet

- AMEM 314 Labs Strain GaugesDocument12 pagesAMEM 314 Labs Strain GaugesZamri NasirNo ratings yet

- Numericals On Nodal Loop AnalysisDocument7 pagesNumericals On Nodal Loop AnalysisShivam ModiNo ratings yet

- Time Borrowing and Time StealingDocument9 pagesTime Borrowing and Time StealingPradeep JagathratchaganNo ratings yet

- Experiment No 2 (Fet)Document4 pagesExperiment No 2 (Fet)Jaideep Singh100% (1)

- Converter 4 20maDocument19 pagesConverter 4 20mabnurkholis100% (1)

- IR2153 Parte1Document1 pageIR2153 Parte1FRANK NIELE DE OLIVEIRANo ratings yet

- 8th Edition Hayt SolutionsDocument4 pages8th Edition Hayt Solutionstash7827No ratings yet

- Lalanne Sene VcosDocument23 pagesLalanne Sene VcosSenthil SivakumarNo ratings yet

- Ccopt Rak For Beginners: Product - Innovus 16.20 April 2017Document71 pagesCcopt Rak For Beginners: Product - Innovus 16.20 April 2017Akshat Pathak100% (1)

- Vlsi 2-Marks With AnswerDocument23 pagesVlsi 2-Marks With Answerk poornimaNo ratings yet

- Assignment 8Document9 pagesAssignment 8vidhya dsNo ratings yet

- EE-231 Electronics I: Engr. Dr. Hadeed Ahmed SherDocument15 pagesEE-231 Electronics I: Engr. Dr. Hadeed Ahmed SherHadeedAhmedSherNo ratings yet

- D FF Using JOHNSON COUNTERDocument5 pagesD FF Using JOHNSON COUNTERcNeeraNo ratings yet

- Tidrbe 1Document11 pagesTidrbe 1Om VermaNo ratings yet

- Temperature Sensor Report PDFDocument3 pagesTemperature Sensor Report PDFlibrian_30005821No ratings yet

- Ujt and PutDocument35 pagesUjt and Putisraeljumbo100% (1)