Professional Documents

Culture Documents

Coa R4it2004s MST Nov2021

Coa R4it2004s MST Nov2021

Uploaded by

Pranav ShuklaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Coa R4it2004s MST Nov2021

Coa R4it2004s MST Nov2021

Uploaded by

Pranav ShuklaCopyright:

Available Formats

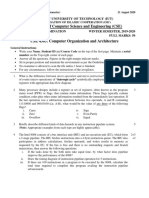

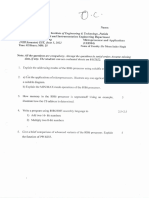

VEERMATA JIJABAI TECHNOLOGICAL INSTITUTE (VJTI)

[Central Technological Institute, Maharashtra State]

Matunga, Mumbai-400 019

EXAMINATION MST - ODD Semester 2021 DATE 12/11/2021

OF

EXAM

SEMESTER & III & Second Year B Tech Information TIME 12:00 PM to 01:00 PM

PROGRAM Technology

TIME ALLOWED 1 Hrs MARKS 20

COURSE (Course Computer organization and Architecture (R4IT2004S)

Code)

Instructions: All questions are Compulsory

Q. Question Marks CO

No

Q.1 Describe in detail IEEE 754 floating point format and apply the IEEE 754 single 6 1

precision format on +105.7

Q.2 Design hardwired control unit for the GCD processor. Illustrate and implement the 6 2

state table for the control unit and classical method

Q.3 Consider a 16-bit processor in which the following appears in main memory, 8 1

starting at location 200:

The first part of the first word indicates that this instruction loads a value into an

accumulator. The Mode field specifies an addressing mode and, if appropriate,

indicates a source register; assume that when used, the source register is R1, which

has a value of 400. There is also a base register that contains the value 100. The

value of 500 in location 201 may be part of the address calculation. Assume that

location 399 contains the value 999, location 400 contains the value 1000, and so

on. Determine the effective address and the operand to be loaded for the following

address modes:

a. Direct d. PC relative g. Register indirect

b. Immediate e. Displacement h. Autoindexing with

c. Indirect f. Register increment, using R1

You might also like

- From GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandFrom EverandFrom GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandNo ratings yet

- COA R4CO2004S R4IT2004S MST DSY June 2022Document1 pageCOA R4CO2004S R4IT2004S MST DSY June 2022Pranav ShuklaNo ratings yet

- ETC Raisoni Endsem PaperDocument14 pagesETC Raisoni Endsem PaperYogesh Jounjalkar100% (1)

- Coa Test 1 Paper Set B 2020-21Document1 pageCoa Test 1 Paper Set B 2020-21Roshan WarriorNo ratings yet

- Emcs NBKR1Document5 pagesEmcs NBKR1BhaskarReddyVangalaNo ratings yet

- Shri Ramdeobaba College of Engineering and Management, Nagpur - 440013Document2 pagesShri Ramdeobaba College of Engineering and Management, Nagpur - 440013Test IngNo ratings yet

- Assignment Unit 04Document1 pageAssignment Unit 04Apurva JarwalNo ratings yet

- R7320202 Microprocessors & Microcontrollers12Document1 pageR7320202 Microprocessors & Microcontrollers12subbuNo ratings yet

- EC604 Assignment - 1682053761Document1 pageEC604 Assignment - 1682053761Gopi PawarNo ratings yet

- List of Experim Ents: Charotar University of Science & Technology Faculty of Technology & EngineeringDocument4 pagesList of Experim Ents: Charotar University of Science & Technology Faculty of Technology & Engineeringsharath h sNo ratings yet

- PMC211Document1 pagePMC211SwapnilNo ratings yet

- Et ZC323 Ec-3r First Sem 2022-2023Document1 pageEt ZC323 Ec-3r First Sem 2022-2023irfanNo ratings yet

- Jntuworld: M.Tech - II Semester Regular & Supplementary Examinations November 2012Document1 pageJntuworld: M.Tech - II Semester Regular & Supplementary Examinations November 2012Jyothsna VayyalaNo ratings yet

- Compro Dec 20 Reg - WKDDocument3 pagesCompro Dec 20 Reg - WKDDesmond Owusu- AnsahNo ratings yet

- Exp 5 MMDocument8 pagesExp 5 MMSamrudhi PatilNo ratings yet

- Mts Lab ManualDocument84 pagesMts Lab Manual18MECH4020 P.PONMALAI PANDINo ratings yet

- Seven TutorialDocument3 pagesSeven TutorialMudit SinhaNo ratings yet

- Semester IDocument17 pagesSemester IAnnantNo ratings yet

- CSE PUT Paper MicroprocessorDocument3 pagesCSE PUT Paper Microprocessorrachit koundalNo ratings yet

- Microprocessors and Interfacing PaperDocument3 pagesMicroprocessors and Interfacing PaperYaar RaiderNo ratings yet

- 9A04602 Microprocessors & Microcontrollers5Document1 page9A04602 Microprocessors & Microcontrollers5subbuNo ratings yet

- CSA Test PaperDocument65 pagesCSA Test Paperhimanshumis2022No ratings yet

- NB:-Write The Answers in Your Own Way and Do Not Copy From OtherDocument2 pagesNB:-Write The Answers in Your Own Way and Do Not Copy From OtherSayanMaitiNo ratings yet

- SS 9A04602 Microprocessors & Microcontrollers6Document1 pageSS 9A04602 Microprocessors & Microcontrollers6subbuNo ratings yet

- CLAT-2-Answer Key-SET-BDocument8 pagesCLAT-2-Answer Key-SET-BVikram ChaudharyNo ratings yet

- Experiment 5Document8 pagesExperiment 5Samrudhi PatilNo ratings yet

- MPMC MID 1 2020Document1 pageMPMC MID 1 2020Virang PatelNo ratings yet

- Assignment 02 - (Computer Organization and Architecture)Document1 pageAssignment 02 - (Computer Organization and Architecture)English words BY Utkarsh johriNo ratings yet

- A 179 Exp 6 MPMCDocument8 pagesA 179 Exp 6 MPMCSamrudhi PatilNo ratings yet

- Microprocessor and Microcontroller July 2021Document3 pagesMicroprocessor and Microcontroller July 2021mysticalnucleus369No ratings yet

- WirelessDocument1 pageWirelessSoumet Das SoumetNo ratings yet

- MCMP Lab Record 1919106016Document98 pagesMCMP Lab Record 1919106016Dhanush DhoniNo ratings yet

- Eee-Iii-Ii Lesson Plans (A & B)Document31 pagesEee-Iii-Ii Lesson Plans (A & B)JeronimoNo ratings yet

- SSCD CH 02 AssignmentsDocument1 pageSSCD CH 02 AssignmentsSumit SutarNo ratings yet

- Government College of Engineering, AmravatiDocument2 pagesGovernment College of Engineering, AmravatiyashNo ratings yet

- Mid 1-MPMCDocument1 pageMid 1-MPMCDr.R.RAMANNo ratings yet

- Rr322203 Microprocessors MicrocontrollersDocument8 pagesRr322203 Microprocessors Microcontrollersgeddam06108825No ratings yet

- Our Official Android App - REJINPAUL NETWORK FromDocument1 pageOur Official Android App - REJINPAUL NETWORK From_hrithik_rkNo ratings yet

- Department of Computer Science and Engineering (CSE) : Islamic University of Technology (Iut)Document3 pagesDepartment of Computer Science and Engineering (CSE) : Islamic University of Technology (Iut)Manus HumanNo ratings yet

- Diploma IT 3rd Sem SylDocument20 pagesDiploma IT 3rd Sem Sylshriram1082883No ratings yet

- (Autonomous Institute) IV B.Tech Ist MID-II Subjective Examinations, Nov-2018 Instrumentation and Control SystemDocument1 page(Autonomous Institute) IV B.Tech Ist MID-II Subjective Examinations, Nov-2018 Instrumentation and Control SystemAditya SowriNo ratings yet

- rr321402 MicroprocessorsDocument8 pagesrr321402 MicroprocessorsSRINIVASA RAO GANTANo ratings yet

- Department of Computer Science and Engineering Lab Manual Academic Year: 2015-16 ODD SEMESTERDocument58 pagesDepartment of Computer Science and Engineering Lab Manual Academic Year: 2015-16 ODD SEMESTERSivateja ChowdaryNo ratings yet

- Chhattisgarh Swami Vivekanand Technical University, BhilaiDocument22 pagesChhattisgarh Swami Vivekanand Technical University, Bhilaibheshram janghelNo ratings yet

- MP Model QP Set1Document26 pagesMP Model QP Set1Jai MohanNo ratings yet

- Jntuworld: R07 Set No. 2Document7 pagesJntuworld: R07 Set No. 2Kasarla Shiva SjNo ratings yet

- UEI504Document1 pageUEI504Lets clear Jee mathsNo ratings yet

- MechatronicsDocument83 pagesMechatronicsGOPAL SNo ratings yet

- MPMC Lab Maual EXP 1,2sDocument29 pagesMPMC Lab Maual EXP 1,2s727821tuit025No ratings yet

- ESE Q Paper - ITDocument2 pagesESE Q Paper - ITWoya MaNo ratings yet

- Ee32005-Lab ManualDocument45 pagesEe32005-Lab ManualPriyanshu SinghNo ratings yet

- rr420402 Radar EngineeringDocument8 pagesrr420402 Radar EngineeringSRINIVASA RAO GANTANo ratings yet

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionFrom EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionNo ratings yet

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysFrom EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysNo ratings yet

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesFrom EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesNo ratings yet

- Multicore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCFrom EverandMulticore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCNo ratings yet

- COA R4CO2004S R4IT2004S MST DSY June 2022Document1 pageCOA R4CO2004S R4IT2004S MST DSY June 2022Pranav ShuklaNo ratings yet

- Coa R4it2004s Ese Dec2021 Paper2Document2 pagesCoa R4it2004s Ese Dec2021 Paper2Pranav ShuklaNo ratings yet

- Unit 6-Part2 - Parallel - ProcessingDocument21 pagesUnit 6-Part2 - Parallel - ProcessingPranav ShuklaNo ratings yet

- Unit 6 Part1 IlpDocument39 pagesUnit 6 Part1 IlpPranav ShuklaNo ratings yet

- Unit 5 Input Output OrganizationDocument37 pagesUnit 5 Input Output OrganizationPranav ShuklaNo ratings yet

- Unit 4 - Memory OrganizationDocument127 pagesUnit 4 - Memory OrganizationPranav ShuklaNo ratings yet