Professional Documents

Culture Documents

Calculo de Amplificadores

Calculo de Amplificadores

Uploaded by

Ferreira NetoCopyright:

Available Formats

You might also like

- Objective: The Common Emitter AmplifierDocument14 pagesObjective: The Common Emitter AmplifierJohn Joshua Miclat100% (1)

- ENGN 2218 - HLab 1Document10 pagesENGN 2218 - HLab 1varshav_4No ratings yet

- 2.basic Electrical Engineering Lecture Part 2Document22 pages2.basic Electrical Engineering Lecture Part 2Cedric Zamora100% (1)

- Alternate Class AB Amplifier DesignDocument14 pagesAlternate Class AB Amplifier DesignrrbulataoNo ratings yet

- Intermediate Lab PHYS 3140 CircuitsDocument36 pagesIntermediate Lab PHYS 3140 CircuitsHighway RiderNo ratings yet

- ELE222E 2006 FinalDocument4 pagesELE222E 2006 Finalugurgul123No ratings yet

- Tutorial 4 PDFDocument6 pagesTutorial 4 PDFAkshay RamrekhaNo ratings yet

- HW 4 Fall 2023 EEE313Document3 pagesHW 4 Fall 2023 EEE313dnthrtm3No ratings yet

- STI PAC1 2019 Fall SolvedDocument3 pagesSTI PAC1 2019 Fall SolvedMarta Bordonaba Del RioNo ratings yet

- DC Circuits 9 SibuloDocument9 pagesDC Circuits 9 Sibulonoah.sibulo2014No ratings yet

- Tutorial 1Document3 pagesTutorial 1Putrevu SaiprakashNo ratings yet

- Experiment 3Document8 pagesExperiment 3mahinshahriar20No ratings yet

- 01 Resistor2Document9 pages01 Resistor2dhinarNo ratings yet

- 1 - Model Question Paper - Aec2024Document3 pages1 - Model Question Paper - Aec2024Rakesh MNo ratings yet

- EE230 Lab 5Document3 pagesEE230 Lab 5AnnirudhNo ratings yet

- V Ir (1 Way) I V/R (2 Way) R V/I (3 Way)Document14 pagesV Ir (1 Way) I V/R (2 Way) R V/I (3 Way)bipotor149No ratings yet

- Op Amp and Transistor-Based Analog Square Wave Generator DesignDocument10 pagesOp Amp and Transistor-Based Analog Square Wave Generator DesignAto Triyono MetroNo ratings yet

- Experiment 1-Analog Diode Application CircuitsDocument8 pagesExperiment 1-Analog Diode Application Circuitsnaim yuslieNo ratings yet

- Review Problems: 40 k Ω 4 kΩ Vo +Document16 pagesReview Problems: 40 k Ω 4 kΩ Vo +NajmoAdenNo ratings yet

- Lab #10: Sensor Signal ConditioningDocument10 pagesLab #10: Sensor Signal ConditioningNioNo ratings yet

- Assignment OpampDocument3 pagesAssignment OpampRamNo ratings yet

- Experiment 7 AC Circuits: ObjectivesDocument6 pagesExperiment 7 AC Circuits: ObjectivesMujtabaAliNo ratings yet

- PART A: Power Factor CorrectionDocument5 pagesPART A: Power Factor CorrectionShajedur RahmanNo ratings yet

- Lab 2 - Transistor BiasDocument12 pagesLab 2 - Transistor Biascrackintheshat100% (1)

- Lab 08Document3 pagesLab 08Juan TarquiNo ratings yet

- EE 230 - Analog Lab - 2021-22/I (Autumn) Experiment 6: Opamp AmplifiersDocument6 pagesEE 230 - Analog Lab - 2021-22/I (Autumn) Experiment 6: Opamp AmplifiersSruthiNo ratings yet

- 12 6 CMPLX Impedance PDFDocument4 pages12 6 CMPLX Impedance PDFKhaled BazaNo ratings yet

- Short Questions: (Chapter 13) Current ElectricityDocument15 pagesShort Questions: (Chapter 13) Current ElectricityM n NoorNo ratings yet

- Homework#5 For Microelectronics (I)Document12 pagesHomework#5 For Microelectronics (I)Bruno IensenNo ratings yet

- EC 21008 Analog Electronic Circuits: (Given: RGI 10 KG, RG2 20 KG, Ro 10 KG, RL 1 KG, Rs 1 KG, CDocument4 pagesEC 21008 Analog Electronic Circuits: (Given: RGI 10 KG, RG2 20 KG, Ro 10 KG, RL 1 KG, Rs 1 KG, Cbrahma2deen2chaudharNo ratings yet

- Undamentals of Ircuits: I VR V I V I V I V IDocument36 pagesUndamentals of Ircuits: I VR V I V I V I V IHanzala TahirNo ratings yet

- EC Lab ManualDocument29 pagesEC Lab ManualAshwath NadahalliNo ratings yet

- LECTURE - 6 MekatronikaDocument10 pagesLECTURE - 6 MekatronikaAditya Putu PramanaNo ratings yet

- Midterm 11 2022Document4 pagesMidterm 11 2022kunghsiangyuNo ratings yet

- Department of Electrical and Systems Engineering ESE 206: Electrical Circuits and Systems II - Lab Junction Diode Basics I. PurposeDocument6 pagesDepartment of Electrical and Systems Engineering ESE 206: Electrical Circuits and Systems II - Lab Junction Diode Basics I. Purposekstu1112No ratings yet

- EEE 104 LS 01 MDS March2020Document50 pagesEEE 104 LS 01 MDS March2020Sharmin Rini100% (1)

- EE 419 Module 2Document46 pagesEE 419 Module 2Reyven ReconNo ratings yet

- Electrical Technology Lab: Dronacharya College of Engineering Khentawas, Gurgaon - 123506Document46 pagesElectrical Technology Lab: Dronacharya College of Engineering Khentawas, Gurgaon - 123506Shreyansh RajNo ratings yet

- Midterm 2013 SolutionDocument5 pagesMidterm 2013 SolutionArunabh BhattacharyaNo ratings yet

- 01 TutorialDocument3 pages01 Tutorialee23m052No ratings yet

- EE 306 ManualDocument55 pagesEE 306 Manualzain khuramNo ratings yet

- SCR Sample Problem - RevDocument9 pagesSCR Sample Problem - RevDonna ComissionNo ratings yet

- RC Snubber Design in Synchronous Buck ConverterDocument3 pagesRC Snubber Design in Synchronous Buck ConvertersnvvNo ratings yet

- Clipper Clamper CircuitsDocument15 pagesClipper Clamper CircuitsAnilaSaghirNo ratings yet

- Experiment 5Document5 pagesExperiment 5mohammad alaliNo ratings yet

- Engineering Science - DC and AC TheoryDocument15 pagesEngineering Science - DC and AC TheorySteven Goddard75% (4)

- U2 l5 Approximate AnalysisDocument8 pagesU2 l5 Approximate AnalysisRavish BangreNo ratings yet

- Exp9 s04Document8 pagesExp9 s04SITI HAJAR AzizNo ratings yet

- BEEE Lab Manual CSVTUDocument44 pagesBEEE Lab Manual CSVTUMulty TalantedNo ratings yet

- Circuits Laboratory Experiment 7: Design of A Single Transistor AmplifierDocument18 pagesCircuits Laboratory Experiment 7: Design of A Single Transistor Amplifierconference RequirementsNo ratings yet

- EXPERIMENT #2 Frequency Response of Common Emitter AmplierDocument6 pagesEXPERIMENT #2 Frequency Response of Common Emitter AmplierGhabriel Javier SembranoNo ratings yet

- BEE-Module-2 Series and Parallel NetworksDocument36 pagesBEE-Module-2 Series and Parallel NetworksMARK JOHN AL RODAVIANo ratings yet

- Experiment 2 Circuit Simplification A. Series and Parallel Circuit. B. Star and Delta TransformationDocument12 pagesExperiment 2 Circuit Simplification A. Series and Parallel Circuit. B. Star and Delta TransformationronakNo ratings yet

- ES330 Laboratory Experiment No. 1: NPN Common-Emitter AmplifierDocument7 pagesES330 Laboratory Experiment No. 1: NPN Common-Emitter AmplifierAhmed SalehNo ratings yet

- Operational Amplifier (Oscillator) : Pattanan Amatanon EE1A3Document6 pagesOperational Amplifier (Oscillator) : Pattanan Amatanon EE1A3pamatanonNo ratings yet

- Temasek Polytechnic School of Engineering AY 2015/2016 TERM TEST (Apr Semester)Document6 pagesTemasek Polytechnic School of Engineering AY 2015/2016 TERM TEST (Apr Semester)Justin NgNo ratings yet

- Easy(er) Electrical Principles for General Class Ham License (2019-2023)From EverandEasy(er) Electrical Principles for General Class Ham License (2019-2023)No ratings yet

- Easy(er) Electrical Principles for General Class Ham License (2015-2019)From EverandEasy(er) Electrical Principles for General Class Ham License (2015-2019)Rating: 5 out of 5 stars5/5 (1)

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterFrom EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterNo ratings yet

- RPM Block DiagramDocument1 pageRPM Block DiagramJuniorNo ratings yet

- TIME - TABLE - July - DEC - 2021 - ECE - BTech - Mtech - PhD-27.07.2021Document12 pagesTIME - TABLE - July - DEC - 2021 - ECE - BTech - Mtech - PhD-27.07.2021HarshNo ratings yet

- Amplificadores OperacionlesDocument10 pagesAmplificadores Operacionlesatorresh090675No ratings yet

- Integrated Differential Amplifier 1-1 Difference VoltageDocument106 pagesIntegrated Differential Amplifier 1-1 Difference VoltageMian Waqar HussainNo ratings yet

- Experiment No. 1 Logic Inverter I. ObjectiveDocument6 pagesExperiment No. 1 Logic Inverter I. Objectivexoxoxoxox11No ratings yet

- Asynchronous Counter Lab ExperimentDocument2 pagesAsynchronous Counter Lab ExperimentShristi Sinha100% (1)

- Valve & Amplifier Design, Mullard Maintenance Manual (1961)Document112 pagesValve & Amplifier Design, Mullard Maintenance Manual (1961)Valve Data83% (6)

- Analysis of Low Power 6T SRAM Using 45 NM Technology: Shatrughan SinghDocument5 pagesAnalysis of Low Power 6T SRAM Using 45 NM Technology: Shatrughan SinghShruti DasNo ratings yet

- IC 045 Embedded Sys Design PPT 5Document51 pagesIC 045 Embedded Sys Design PPT 5RajendraPrasadSahuNo ratings yet

- CfbampDocument1 pageCfbampIr GarNo ratings yet

- Slrs 027 QDocument40 pagesSlrs 027 QramkumarNo ratings yet

- By Introducing Electrical Reactance Into The Feedback Loops of OpDocument4 pagesBy Introducing Electrical Reactance Into The Feedback Loops of OpAnil KumarNo ratings yet

- Experiment-11: Chalamala Sujith Reddy 19CS01009Document8 pagesExperiment-11: Chalamala Sujith Reddy 19CS01009Sujith ReddyNo ratings yet

- PIC24F16KL402 Family Data Sheet DS30001037DDocument264 pagesPIC24F16KL402 Family Data Sheet DS30001037DDaniNo ratings yet

- Ac Controller Using Mosfets: Summer CircuitscollectionDocument1 pageAc Controller Using Mosfets: Summer CircuitscollectionRadunNo ratings yet

- Features Description: 4 / Digit LCD Display CounterDocument7 pagesFeatures Description: 4 / Digit LCD Display CounterTim73No ratings yet

- Mapua D3 TransresoDocument1 pageMapua D3 TransresoEmanuel GabrielNo ratings yet

- Vlsi Lesson PlanDocument3 pagesVlsi Lesson Planeshwar_worldNo ratings yet

- EladAlon LDO AnalysisDocument12 pagesEladAlon LDO Analysisabhi_nxpNo ratings yet

- Digital Logic Design Course and LAB OutlineDocument3 pagesDigital Logic Design Course and LAB Outlinesalman100% (1)

- LM 348 NDocument6 pagesLM 348 NbilarodrigoNo ratings yet

- Introduction To The PIC32 - The Basics, Getting Started, IO Ports and The First ProgramDocument17 pagesIntroduction To The PIC32 - The Basics, Getting Started, IO Ports and The First Programtahmidmc100% (1)

- Pam, PPM, PWMDocument9 pagesPam, PPM, PWMShathis Kumar100% (2)

- 2 To 4 Line DecoderDocument5 pages2 To 4 Line DecoderMalith DeemanthaNo ratings yet

- Weekly Plan of StudyDocument2 pagesWeekly Plan of Studyjudysabbagh23No ratings yet

- PCB Wizard - Sun TrackerDocument2 pagesPCB Wizard - Sun TrackerArunkumar Murugappan100% (1)

- RF Inductance MeterDocument5 pagesRF Inductance MeterTibor NemethNo ratings yet

- 741 Design LabDocument8 pages741 Design LabTuan Vo100% (1)

- Atmel-42735-8-bit-AVR-Microcontroller-ATmega328-328P - Datasheet (1) - 304-317Document14 pagesAtmel-42735-8-bit-AVR-Microcontroller-ATmega328-328P - Datasheet (1) - 304-317JuanNo ratings yet

Calculo de Amplificadores

Calculo de Amplificadores

Uploaded by

Ferreira NetoOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Calculo de Amplificadores

Calculo de Amplificadores

Uploaded by

Ferreira NetoCopyright:

Available Formats

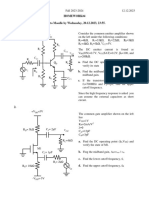

Lab 5.

Audio Amplifier - Appendix

1. The VBE Multiplier

A VBE multiplier, sometimes called an amplified diode, (Figure 2) is used to provide a

tunable voltage between the bases of the Darlingtons X1 and X2. The purpose of this voltage is to

bias the bases of the two Darlingtons, keeping them in a “slightly” ON state - a quiescent current

of about 20 mA is desirable. Tuning is obtained through the use of potentiometer XRV1. The

quiescent current minimizes the zero crossing distortion associated with the power stage emitter

followers. Since VBE is a function of temperature, Q3 should be mounted on the same heat sink

as X1 and X2 to minimize voltage drift.

Figure 2. Vbe Multiplier

The value of the bias should be about 4 x VBE 2.8V, enough to forward bias each of the

four base-emitter junctions in the pair of Darlingtons.

Operation

Assume a current I flows down out of node 2. Assume the gain of Q3 is high, so Ib3 can

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

be ignored. A current I’ = I - IE flows through R1 and R2.

V R 1 = I' R 1

R 2

V R 2 = I' R 2 = V BE 3

R 1

R 2

V ()Τϕ

2 , 3/Φ3 =7.305

V R 1Τφ+ 1 V0 R0 2 1 =105.36

1 + 657.09 Τµ

()

V BE 3

R 1

Thus the voltage drop is a multiple of VBE3, and is not restricted to being an integral

multiple.

By placing a potentiometer at the base of Q3 we can adjust the bias to accommodate

tolerance variations between Darlingtons. A capacitor can be used between nodes 2 and 3 to

bypass ac signals so that the VBE multiplier provides a simple dc bias.

Example 1

Design a VBE multiplier to provide a 3.0 V bias. Assume I = 2.5 mA, ß =

100, and VBE = 0.7 V.

R 2

V = 1 + V

R 1 BE 3

R 2 V 3 .0 V

= − 1 = − 1 = 3 . 29

R 1 V BE 3 0 .7 V

Let the resistors have standard values R2 = 3.3 k , R1 = 1.0 k . Or we

could let R2 be a 2.7 k fixed resistor and a 1 k potentiometer in series.

This would allow bias adjustment from 2.59 V to 3.29 V.

Note that since the 2N2222 transistor does not have the ideal VBE of 0.7

V, the voltage drop across the VBE multiplier is not exactly 3.0 V.

Note that in Example 1 the calculation produced the ratio of R2 to R1. How do you

choose unique values? To get a better feel for the range of appropriate values, look at the ac

resistance of the VBE multiplier:

R 2 R 2 0 . 025 V

r = + 1 + r , where r =

β R 1 e e

Ic

This can be derived from the ac equivalent circuit of the VBE multiplier. To produce a

nearly pure dc voltage drop of a given value you would want R2 small, ß large and Ic large.

Example 2

Calculate the ac resistance of the VBE multiplier in the previous example.

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

0 . 7 V

IE = I − I' = 2 . 5 mA − = 1 . 8 mA

1. 0 k Ω

0 . 025 V

r e = = 13 . 9 Ω

1 . 8 mA

3 .3 k Ω 3 .3

r = + 1 + 13 .9 = 33 .0 Ω + 59 . 8 Ω = 92 .8 Ω

100 1. 0

If this value of r is too high you could lower R2 (and R1), raise I, or add a

capacitor between nodes 2 and 3 with an impedance much less than r at the

frequencies of interest.

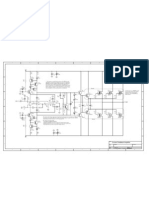

2. Bootstrapping

[Reference: Transistor Circuit Techniques - Discrete and Integrated, 3rd ed., G.J. Ritchie,

Chapman and Hall, London, 1993]

Bootstrapping is a method of increasing the open loop [no feedback] gain of an amplifier.

In this amplifier, capacitor C4 is the bootstrap capacitor. The higher the open loop gain, the more

accurately the equation AV = – RB/RA will predict the closed loop [with feedback] gain of the

audio amplifier using this design style. Consider the circuit below, where Q1 is used in a common

emitter amplifier and Q2 is an emitter follower, or common collector (CC), amplifier.

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

Figure 3. Bootstrapping Example

If the ac voltage at the collector of Q1 is v, then voltage Av is present at the emitter of Q2

and also at the common terminals of R3 and R4, assuming that the impedance of C4 is very small

at the frequencies of interest.

The gain A of the common emitter amplifier is

R 0 . 025 V

A = , where R = RE || R 3 , and re =

re 2 + R 2

Ic 2

The voltage across resistor R4 is v – Av = (1 – A) v.

So for ac signals, the resistance of R4 appears to be R4’ = R4 / (1 – A), which is much higher

than R4 since A is typically just slightly less than 1 for the emitter follower.

Since R4’ is the collector resistance for the common emitter stage, the gain of the CE

stage will become

R 4 ' | | r in (follower

()Τϕ

1 + β /Φ3

R ≈ β12.586 Τφ 1 0 0 1

)

A V = − , where r in ( follower ) = rπ + R

r e1

Without the bootstrapping, the gain would be

()Τϕ

R 3 + /Φ3

R 4 10.066 Τφ 1 )0 0 1 304.08 284.61 Τµ ()

|| r in ( follower

A V = −

re 1

a value much less than that seen if C4 is used.

Example 3. Bootstrapping

Design a CE/CC amplifier pair. Compare the voltage gains with and

without bootstrapping.

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

Assumptions and Design Parameters

Vcc = 12 V

Ic for each transistor is 2.5 mA

ß for each transistor is 100

RL = 1 k

low frequency cutoff 20 Hz

Use 2N2222 for simulations

See appendix for detailed component calculations and PSpice files

Figure 4. Common emitter, common collector amplifiers without

bootstrapping.

Without bootstrapping (Figure 4), the voltage gain is the product of the

gains of the CE stage and the CC stage:

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

RC || ()Τϕ

β × /Φ3

RE 28.684 Τφ RE

1 02 0 1 235.44 709.17 ΤµV ()

t 25 mV

A v = − × , where r ei = =

r e1 RE 2 + r e 2 I ci I ci

1. 6 k Ω | | 290 k Ω 2 . 9 k Ω

A v = − ×

10 Ω 2 . 9 k Ω + 10 Ω

2900

A v = − 159 × = − 158 .6

2910

A v ()Τϕ

PSpice/Φ3 8.684

= − 129Τφ 1 0 0 1 172.08 647.97 Τµ ()

ß x RE2 represents the input resistance of the common collector amplifier,

and is the load for the common emitter amp.

With bootstrapping (Figure 5), the collector resistor of the common

emitter is split into two pieces and the bootstrap capacitor C4 is added.

The impedance of C4 should be small in the audio frequency band.

Figure 5. Common emitter, common collector amplifiers with

bootstrapping. RC was split in half and capacitor C4 added. The amplitude

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

of the sine wave input was reduced in anticipation of higher gain.

The voltage gain of the amplifier pair is Av, and the voltage gain of the

common collector stage is A.

RC 2 ' | | r ( follower )

A v = − in

× A

r e1

V t 25 mV R

where r ei = = , A = ,

I ci I ci R + r e2

R = RE 2 | | RC 1, and r in ( follower ) = βR

Plug in the component values and solve for the bootstrap gain:

R = RE

2 | | RC 1 = 2 . 9 k Ω | | 800 Ω = 627 Ω

25 mV

r e2 = = 10 Ω

2 . 5 mA

R 627 Ω

A = = = 0 . 984

R + r e2 637 Ω

RC 2 800 Ω

RC 2 ' = = = 50 k Ω

1 − A 1 − 0 . 984

50 k Ω | | 62 . 7 k Ω

A v = − × 0 . 984

10 Ω

A v = − 2782 × 0 . 984 = − 2737

A v ()Τϕ

PSpice/Φ3 9.211 Τφ 1 0 0 1 225.6 400.29 Τµ ()

= − 1300

While we can show a large increase in gain (a factor of nearly 20) from

the no bootstrap case, the calculation and simulation do not match. The

reason for this is not yet known.

Feedback

Your textbook can give you a much more detailed description of feedback in amplifier

design than will be presented here. You are encouraged to read the appropriate sections.

Why use feedback in an amplifier design?

• The gain is stabilized against variations in the parameters of the active devices, so no

tuning is needed regardless of which TIP120 Darlington transistor I choose from the bin,

for example. The gain of the amplifier is also protected from variations in temperature,

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

supplies, or degradation with age.

• The input and output impedance may be selectively increased or decreased.

• Non-linear signal distortion is reduced.

• The midband frequency range is increased.

These last two properties make feedback very advantageous for audio circuits.

Possible disadvantages of using negative feedback

• The gain is reduced greatly from the open loop case. If high gain is needed, additional

amplification stages will be needed, with the penalties of size and cost.

• The circuit is more likely to go into oscillation.

There are several types of feedback and several ways they can be implemented. Positive

feedback results when the signal being feed back is in phase with the input signal. Negative

feedback occurs when the signal being feed back is 180 degrees out of phase with the input signal.

In a common emitter or common collector amplifier, feedback is introduced into the base of the

first stage transistor. In a common base design, feedback is introduced into the emitter of the first

stage.

Shunt Feedback vs. Series Feedback

Using an opamp with open loop gain Ao to represent the amplifier, we can illustrate

several feedback options.

Figure 6. Shunt negative feedback (left), and series negative feedback (right). The opamps have

open loop gain Ao .

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

For shunt negative feedback,

R A

A o

R R + R B

A v = − B A

R R A

A 1 + A o

R A + R B

For series negative feedback,

R A

A o

R + R R + R B

A v = A B A

R R A

A 1 + A o

R A + R B

Considering the shunt case, we can simplify the gain equation and remove (or nearly so)

the sensitivity of Av to variations in Ao by making Ao very large. In this case, Av = -RB / RA, an

opamp expression you probably remember from your introductory course and lab on circuits.

The audio amplifier in Figure 1 makes use of shunt feedback. A portion of the output

signal is fed back to the base of Q4 in the CE amplifier. Note that another change is to remove the

top of resistor R5 from the dc supply (compare to figure 4 or 5). The bias network now depends

on the dc level of the Class AB amplifier output (node 1 in figure 1), a value slightly higher than

Vcc/2. Resistor R7 determines the input resistance of the amplifier.

Design

The best plan for getting the most understanding of the sudio amplifier would be to

design, simulate and build the circuit of figure 4, modify it with bootstrapping (figure 5) and then

add feedback. For the sake of time, I am going to go directly to the design of the audio amp of

figure 1.

Design Steps

1) Determine the gain needed. This will help decide if you need a preamp. Typical project

specifications are to produce 4 W into an 8 speaker from a 50 mV peak to peak input.

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

Av = - Vout / Vin

Find the peak voltage needed at the load and compare it to the peak input voltage. A JFET

preamp stage can produce a gain of 2 to 4.

2) Determine the power supply voltage needed. If a preamp is needed it would also use this

supply voltage. To get good symmetrical swing, we set the dc voltage at node 1 to be Vcc/2.

Look at the voltage drops from the supply to the output.

V

V cc = ()Τϕ

V CEX 1/Φ3

sat 12.074

+ V RE 1 + Τφ

cc

2

1+ 0 0 1 205.92 512.61

V load (1 ) Τµ ()

where all the dc voltage drops across the output capacitor. Then

V cc = 2 [()Τϕ

V CEX 1/Φ3

sat 11.477

+ V RE 1 +Τφ

()Τϕ

I load1 0peak

/Φ3 R load ]Τφ

0 1×11.477

215.76 427.17

1 0 ( 20)Τµ

1 319.92

() 427.17 Τµ (

Assume:

X1 = TIP120 NPN Darlington

X2 = TIP125 PNP Darlington

Keep the voltage drops across RE1 and RE2 small. These resistors are present for thermal

stability only, and you should not waste power in them. Let 0.5 VRE1, VRE2 1 V.

What is the peak load current? What is the VCE(sat) for the NPN Darlington? The output

power equals the product of the rms current and the load resistance:

()Τϕ /Φ3 10.156 Τφ 1 0 0 1 266.88 178.53 Τµ ()

2

P o = R load × I load rms

2P

()Τϕ

I load /Φ3

peak 10.156

= Τφ

o

1 0 0 1 192.96 159.33 ( Τµ

3 ) ()

R load

The TIP120 Darlington is rated for a continuous IC current of 5.0 A.

10

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

The saturation value of VCE depends on the collector current. For the TIP120 Darlington (see a

data sheet):

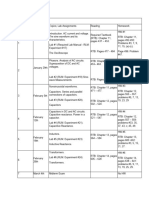

Table 1. (VCE)sat vs Collector Current data for TIP120 NPN Darlington Transistor

IC (VCE)sat

(A) (V)

0.5 0.75

1.0 0.85

3.0 1.15

5.0 1.40

Plug your values of (Iload)peak, VRE1, Rload, and (VCEX1)sat into equation 2, and solve for

Vcc. Round the supply to a common value (5V, 12V, 15V, etc.). Since each Darlington

transistor must be able to withstand the full Vcc voltage, check that the VCEO specification is at

least equal to Vcc plus 10 to 20 % safety margin. In this case, the TIP120 and TIP125 each have

VCEO = 60 V.

RE1 and RE2:

Choose a value between 0.5 and 1.0 V for VRE1.

V RE

= RE =

1

RE 1 2

()Τϕ

I load /Φ3

peak

9.449 Τφ 1 0 0 1 335.04 269.49 Τµ ()

The power dissipation in the emitter resistors will be (Iload)peak2 x RE1, and may be a

watt or more.

R1 and R2:

The VBE Multiplier design must take into account both the VBE drops across the

Darlingtons and the drops across RE1 and RE2. So, V(2,3) = 2.8 V + 2VBE1. Use the design

procedure discussed earlier to find R1 and R2.

11

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

R3 and R4:

The base current required for the Darlingtons depends on their minimum hFE or b.

()Τϕ

h FE /Φ3

min 9.703

= 1000 Τφ 1 0 0 1 215.52

for TIP120, TIP125 646.05 Τµ ()

()Τϕ

I load /Φ3 10.246 Τφ 1 0 0 1 361.44 631.89 Τµ

()Τϕ

I BX1 /Φ3

peak 9.703

= ()Τϕ

I BX2Τφ /Φ3

1 0 9.703

peak 0= 1 215.52

Τφ 1peak0624.45

0 1 288.48

Τµ () 624.45 Τµ ()

1000

The current through Q3 and Q4 should exceed this value by a margin of 2 to 10.

The voltage at node 2 should be V(2) = V(1) + VBE1 + 1.4 V. Then

R3 + R4 = (Vcc - V(2)) / Ic3. Split this value about equally between R3 and R4.

RE4:

In a normal CE amplifier design, we would have several volts dropped across RE4. In this

case, since the collector of Q4 drives a PNP Darlington, we have to keep the drop across RE4

small, otherwise the voltage swing of the negative phase of the output will be limited (clipped).

Let V(9) be about 0.5 V. Then RE4 = (0.5 V) / Ic3.

R5 and R6:

The value of R5 effects several circuit properties: base bias of Q4, gain, and input

resistance. The voltage at node Vin and the required base bias of Q4 are:

V ( Vin ) = IE 4 × RE 4 + 0 .7 V

Ie4 Ie 4

Ib 4 (max) = =

β 4 100

The current in the divider consisting of R5 and R6 must exceed Ib4(max) by a factor of 2 to 10.

For a reasonable input resistance, we want R7 on the order of 1 k . For a gain in the 100’s, R5

will have to be on the order of 100 k . If R5 is too large you will not have sufficient base drive

current. If R5 is too small, the input resistance (R7) will fall below acceptable values.

Choose several possible values of R5, and try the following calculations:

12

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

V ( 1 ) − V ( Vin )

IR 5 =

R 5

IR 6 (min) = I R 5 − I b 4 (max)

V ( Vin )

R 6 =

I R 6 (min)

R 5

R 7 =

A v

IR5 must be greater than Ib4(max) by a factor of at least 2. If not, adjust R5. If R7 is much below

1 k , you might want to consider adding the JFET preamp to increase the input resistance and

decrease the gain requirement of this audio amplifier to about 100. An alternative would be to

reduce the collector current through Q4. This reduces the base bias requirement, and allows larger

values of R5 and R7.

References

Gibilisco, S. and N. Sclater, ed., Encyclopedia of Electronics, 2nd ed., TAB Professional

Reference Books, Blue Ridge Summit, PA, 1990.

Ritchie G.J., Transistor Circuit Techniques - Discrete and Integrated, 3rd ed., Chapman and

Hall, London, 1993.

Schubert, T. and E. Kim, Active and Non-Linear Electronics, John Wiley, New York, 1996.

Sedra, A., and K. Smith, Microelectronic Circuits, 3rd ed., Saunders, Philadelphia, 1991.

13

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

Appendix

Amplifier Calculations (Figures 4 and 5)

Ic = 2.5 mA, ß = 100, RL = 1k , Vcc = 12 V.

Let the voltage at the base of Q1, VB, be about Vcc/3 or 4 V for good output swing

Then at the emitter of Q1, VE = 4 - VBE = 3.3 V.

Let IE = IC to simplify calculations.

V E 3 .3 V

RE 1 = = = 1. 32 k Ω

IE 2 . 5 mA

Let the current through the divider consisting of R1 and R2 be about ten times the Q1 base

current, or about 0.1IE when ß = 100.

12 V

R 1 + R 2 = = 48 k Ω

0 . 25 mA

R 2

V cc = 4 V

R 1 + R 2

4 V 4 V

R 2 = ()Τϕ

R 1 +/Φ3

R 28.715

= Τφ 1 48

0 0k Ω1 180.48

= 16 k Ω376.53 Τµ ()

V cc 12 V

R 1 = 32 k Ω

Let the drop across Q1’s collector resistor be about Vcc/3.

V cc − V c 4 V

RC = = = 1. 6 k Ω

I c 2 . 5 mA

The dc bias at the base of Q2 should be 8 V. The emitter voltage should be 7.3 V.

7.3 V

RE 2 = = 2. 9kΩ

2 . 5 mA

PSpice Input Files

CE/CC Amplifier - no bootstrapping

* nominal gain = -160

* Spice extraction from McLogic

14

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

C1 1 b1 91uF

C2 e2 Vout 33uF

RC Vcc c1 1.6k

RE1 e1 0 1.32k

RE2 e2 0 2.9k

Vin Vin 0 sin(0V 10mV 1kHz)

Vcc Vcc 0 12V

Q1 c1 b1 e1 Q2N2222

CE e1 0 1000uF

R1 Vcc b1 32k

R2 b1 0 16k

RL Vout 0 1k

Q2 Vcc c1 e2 Q2N2222

Rs Vin 1 100

* Pull the transistor models from the eval library

.lib eval.lib

.probe

* Run simulation for 2 cycles, 200 points minimum

.tran 0.02ms 2ms 0 10us

* Show the output voltage in the dialog box as sim runs

.watch tran V([Vout])

.end

******************************************************************************

*********

Bootstrapped CC/CE amplifier

* Nominal gain = -2700

* Spice extraction from McLogic

C1 1 b1 91uF

C2 e2 Vout 33uF

15

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

RC1 Vcc 2 800

RC2 2 c1 800

RE1 e1 0 1.32k

Vin Vin 0 sin(0V 1mV 1kHz)

Vcc Vcc 0 12V

Q1 c1 b1 e1 Q2N2222

CE e1 0 1000uF

R1 Vcc b1 32k

R2 b1 0 16k

RL Vout 0 1k

Q2 Vcc c1 e2 Q2N2222

RE2 e2 0 2.9k

Rs Vin 1 100

C4 2 e2 4000uF

* Pull the transistor models from the eval library

.lib eval.lib

.probe

* Run simulation for 2 cycles, 200 points minimum

.tran 0.02ms 2ms 0 10us

* Show the output voltage in the dialog box as sim runs

.watch tran V([Vout])

.end

16

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

You might also like

- Objective: The Common Emitter AmplifierDocument14 pagesObjective: The Common Emitter AmplifierJohn Joshua Miclat100% (1)

- ENGN 2218 - HLab 1Document10 pagesENGN 2218 - HLab 1varshav_4No ratings yet

- 2.basic Electrical Engineering Lecture Part 2Document22 pages2.basic Electrical Engineering Lecture Part 2Cedric Zamora100% (1)

- Alternate Class AB Amplifier DesignDocument14 pagesAlternate Class AB Amplifier DesignrrbulataoNo ratings yet

- Intermediate Lab PHYS 3140 CircuitsDocument36 pagesIntermediate Lab PHYS 3140 CircuitsHighway RiderNo ratings yet

- ELE222E 2006 FinalDocument4 pagesELE222E 2006 Finalugurgul123No ratings yet

- Tutorial 4 PDFDocument6 pagesTutorial 4 PDFAkshay RamrekhaNo ratings yet

- HW 4 Fall 2023 EEE313Document3 pagesHW 4 Fall 2023 EEE313dnthrtm3No ratings yet

- STI PAC1 2019 Fall SolvedDocument3 pagesSTI PAC1 2019 Fall SolvedMarta Bordonaba Del RioNo ratings yet

- DC Circuits 9 SibuloDocument9 pagesDC Circuits 9 Sibulonoah.sibulo2014No ratings yet

- Tutorial 1Document3 pagesTutorial 1Putrevu SaiprakashNo ratings yet

- Experiment 3Document8 pagesExperiment 3mahinshahriar20No ratings yet

- 01 Resistor2Document9 pages01 Resistor2dhinarNo ratings yet

- 1 - Model Question Paper - Aec2024Document3 pages1 - Model Question Paper - Aec2024Rakesh MNo ratings yet

- EE230 Lab 5Document3 pagesEE230 Lab 5AnnirudhNo ratings yet

- V Ir (1 Way) I V/R (2 Way) R V/I (3 Way)Document14 pagesV Ir (1 Way) I V/R (2 Way) R V/I (3 Way)bipotor149No ratings yet

- Op Amp and Transistor-Based Analog Square Wave Generator DesignDocument10 pagesOp Amp and Transistor-Based Analog Square Wave Generator DesignAto Triyono MetroNo ratings yet

- Experiment 1-Analog Diode Application CircuitsDocument8 pagesExperiment 1-Analog Diode Application Circuitsnaim yuslieNo ratings yet

- Review Problems: 40 k Ω 4 kΩ Vo +Document16 pagesReview Problems: 40 k Ω 4 kΩ Vo +NajmoAdenNo ratings yet

- Lab #10: Sensor Signal ConditioningDocument10 pagesLab #10: Sensor Signal ConditioningNioNo ratings yet

- Assignment OpampDocument3 pagesAssignment OpampRamNo ratings yet

- Experiment 7 AC Circuits: ObjectivesDocument6 pagesExperiment 7 AC Circuits: ObjectivesMujtabaAliNo ratings yet

- PART A: Power Factor CorrectionDocument5 pagesPART A: Power Factor CorrectionShajedur RahmanNo ratings yet

- Lab 2 - Transistor BiasDocument12 pagesLab 2 - Transistor Biascrackintheshat100% (1)

- Lab 08Document3 pagesLab 08Juan TarquiNo ratings yet

- EE 230 - Analog Lab - 2021-22/I (Autumn) Experiment 6: Opamp AmplifiersDocument6 pagesEE 230 - Analog Lab - 2021-22/I (Autumn) Experiment 6: Opamp AmplifiersSruthiNo ratings yet

- 12 6 CMPLX Impedance PDFDocument4 pages12 6 CMPLX Impedance PDFKhaled BazaNo ratings yet

- Short Questions: (Chapter 13) Current ElectricityDocument15 pagesShort Questions: (Chapter 13) Current ElectricityM n NoorNo ratings yet

- Homework#5 For Microelectronics (I)Document12 pagesHomework#5 For Microelectronics (I)Bruno IensenNo ratings yet

- EC 21008 Analog Electronic Circuits: (Given: RGI 10 KG, RG2 20 KG, Ro 10 KG, RL 1 KG, Rs 1 KG, CDocument4 pagesEC 21008 Analog Electronic Circuits: (Given: RGI 10 KG, RG2 20 KG, Ro 10 KG, RL 1 KG, Rs 1 KG, Cbrahma2deen2chaudharNo ratings yet

- Undamentals of Ircuits: I VR V I V I V I V IDocument36 pagesUndamentals of Ircuits: I VR V I V I V I V IHanzala TahirNo ratings yet

- EC Lab ManualDocument29 pagesEC Lab ManualAshwath NadahalliNo ratings yet

- LECTURE - 6 MekatronikaDocument10 pagesLECTURE - 6 MekatronikaAditya Putu PramanaNo ratings yet

- Midterm 11 2022Document4 pagesMidterm 11 2022kunghsiangyuNo ratings yet

- Department of Electrical and Systems Engineering ESE 206: Electrical Circuits and Systems II - Lab Junction Diode Basics I. PurposeDocument6 pagesDepartment of Electrical and Systems Engineering ESE 206: Electrical Circuits and Systems II - Lab Junction Diode Basics I. Purposekstu1112No ratings yet

- EEE 104 LS 01 MDS March2020Document50 pagesEEE 104 LS 01 MDS March2020Sharmin Rini100% (1)

- EE 419 Module 2Document46 pagesEE 419 Module 2Reyven ReconNo ratings yet

- Electrical Technology Lab: Dronacharya College of Engineering Khentawas, Gurgaon - 123506Document46 pagesElectrical Technology Lab: Dronacharya College of Engineering Khentawas, Gurgaon - 123506Shreyansh RajNo ratings yet

- Midterm 2013 SolutionDocument5 pagesMidterm 2013 SolutionArunabh BhattacharyaNo ratings yet

- 01 TutorialDocument3 pages01 Tutorialee23m052No ratings yet

- EE 306 ManualDocument55 pagesEE 306 Manualzain khuramNo ratings yet

- SCR Sample Problem - RevDocument9 pagesSCR Sample Problem - RevDonna ComissionNo ratings yet

- RC Snubber Design in Synchronous Buck ConverterDocument3 pagesRC Snubber Design in Synchronous Buck ConvertersnvvNo ratings yet

- Clipper Clamper CircuitsDocument15 pagesClipper Clamper CircuitsAnilaSaghirNo ratings yet

- Experiment 5Document5 pagesExperiment 5mohammad alaliNo ratings yet

- Engineering Science - DC and AC TheoryDocument15 pagesEngineering Science - DC and AC TheorySteven Goddard75% (4)

- U2 l5 Approximate AnalysisDocument8 pagesU2 l5 Approximate AnalysisRavish BangreNo ratings yet

- Exp9 s04Document8 pagesExp9 s04SITI HAJAR AzizNo ratings yet

- BEEE Lab Manual CSVTUDocument44 pagesBEEE Lab Manual CSVTUMulty TalantedNo ratings yet

- Circuits Laboratory Experiment 7: Design of A Single Transistor AmplifierDocument18 pagesCircuits Laboratory Experiment 7: Design of A Single Transistor Amplifierconference RequirementsNo ratings yet

- EXPERIMENT #2 Frequency Response of Common Emitter AmplierDocument6 pagesEXPERIMENT #2 Frequency Response of Common Emitter AmplierGhabriel Javier SembranoNo ratings yet

- BEE-Module-2 Series and Parallel NetworksDocument36 pagesBEE-Module-2 Series and Parallel NetworksMARK JOHN AL RODAVIANo ratings yet

- Experiment 2 Circuit Simplification A. Series and Parallel Circuit. B. Star and Delta TransformationDocument12 pagesExperiment 2 Circuit Simplification A. Series and Parallel Circuit. B. Star and Delta TransformationronakNo ratings yet

- ES330 Laboratory Experiment No. 1: NPN Common-Emitter AmplifierDocument7 pagesES330 Laboratory Experiment No. 1: NPN Common-Emitter AmplifierAhmed SalehNo ratings yet

- Operational Amplifier (Oscillator) : Pattanan Amatanon EE1A3Document6 pagesOperational Amplifier (Oscillator) : Pattanan Amatanon EE1A3pamatanonNo ratings yet

- Temasek Polytechnic School of Engineering AY 2015/2016 TERM TEST (Apr Semester)Document6 pagesTemasek Polytechnic School of Engineering AY 2015/2016 TERM TEST (Apr Semester)Justin NgNo ratings yet

- Easy(er) Electrical Principles for General Class Ham License (2019-2023)From EverandEasy(er) Electrical Principles for General Class Ham License (2019-2023)No ratings yet

- Easy(er) Electrical Principles for General Class Ham License (2015-2019)From EverandEasy(er) Electrical Principles for General Class Ham License (2015-2019)Rating: 5 out of 5 stars5/5 (1)

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterFrom EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterNo ratings yet

- RPM Block DiagramDocument1 pageRPM Block DiagramJuniorNo ratings yet

- TIME - TABLE - July - DEC - 2021 - ECE - BTech - Mtech - PhD-27.07.2021Document12 pagesTIME - TABLE - July - DEC - 2021 - ECE - BTech - Mtech - PhD-27.07.2021HarshNo ratings yet

- Amplificadores OperacionlesDocument10 pagesAmplificadores Operacionlesatorresh090675No ratings yet

- Integrated Differential Amplifier 1-1 Difference VoltageDocument106 pagesIntegrated Differential Amplifier 1-1 Difference VoltageMian Waqar HussainNo ratings yet

- Experiment No. 1 Logic Inverter I. ObjectiveDocument6 pagesExperiment No. 1 Logic Inverter I. Objectivexoxoxoxox11No ratings yet

- Asynchronous Counter Lab ExperimentDocument2 pagesAsynchronous Counter Lab ExperimentShristi Sinha100% (1)

- Valve & Amplifier Design, Mullard Maintenance Manual (1961)Document112 pagesValve & Amplifier Design, Mullard Maintenance Manual (1961)Valve Data83% (6)

- Analysis of Low Power 6T SRAM Using 45 NM Technology: Shatrughan SinghDocument5 pagesAnalysis of Low Power 6T SRAM Using 45 NM Technology: Shatrughan SinghShruti DasNo ratings yet

- IC 045 Embedded Sys Design PPT 5Document51 pagesIC 045 Embedded Sys Design PPT 5RajendraPrasadSahuNo ratings yet

- CfbampDocument1 pageCfbampIr GarNo ratings yet

- Slrs 027 QDocument40 pagesSlrs 027 QramkumarNo ratings yet

- By Introducing Electrical Reactance Into The Feedback Loops of OpDocument4 pagesBy Introducing Electrical Reactance Into The Feedback Loops of OpAnil KumarNo ratings yet

- Experiment-11: Chalamala Sujith Reddy 19CS01009Document8 pagesExperiment-11: Chalamala Sujith Reddy 19CS01009Sujith ReddyNo ratings yet

- PIC24F16KL402 Family Data Sheet DS30001037DDocument264 pagesPIC24F16KL402 Family Data Sheet DS30001037DDaniNo ratings yet

- Ac Controller Using Mosfets: Summer CircuitscollectionDocument1 pageAc Controller Using Mosfets: Summer CircuitscollectionRadunNo ratings yet

- Features Description: 4 / Digit LCD Display CounterDocument7 pagesFeatures Description: 4 / Digit LCD Display CounterTim73No ratings yet

- Mapua D3 TransresoDocument1 pageMapua D3 TransresoEmanuel GabrielNo ratings yet

- Vlsi Lesson PlanDocument3 pagesVlsi Lesson Planeshwar_worldNo ratings yet

- EladAlon LDO AnalysisDocument12 pagesEladAlon LDO Analysisabhi_nxpNo ratings yet

- Digital Logic Design Course and LAB OutlineDocument3 pagesDigital Logic Design Course and LAB Outlinesalman100% (1)

- LM 348 NDocument6 pagesLM 348 NbilarodrigoNo ratings yet

- Introduction To The PIC32 - The Basics, Getting Started, IO Ports and The First ProgramDocument17 pagesIntroduction To The PIC32 - The Basics, Getting Started, IO Ports and The First Programtahmidmc100% (1)

- Pam, PPM, PWMDocument9 pagesPam, PPM, PWMShathis Kumar100% (2)

- 2 To 4 Line DecoderDocument5 pages2 To 4 Line DecoderMalith DeemanthaNo ratings yet

- Weekly Plan of StudyDocument2 pagesWeekly Plan of Studyjudysabbagh23No ratings yet

- PCB Wizard - Sun TrackerDocument2 pagesPCB Wizard - Sun TrackerArunkumar Murugappan100% (1)

- RF Inductance MeterDocument5 pagesRF Inductance MeterTibor NemethNo ratings yet

- 741 Design LabDocument8 pages741 Design LabTuan Vo100% (1)

- Atmel-42735-8-bit-AVR-Microcontroller-ATmega328-328P - Datasheet (1) - 304-317Document14 pagesAtmel-42735-8-bit-AVR-Microcontroller-ATmega328-328P - Datasheet (1) - 304-317JuanNo ratings yet