Professional Documents

Culture Documents

Memory Technologies

Memory Technologies

Uploaded by

Naresh KumarOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Memory Technologies

Memory Technologies

Uploaded by

Naresh KumarCopyright:

Available Formats

R19 M.Tech.

Embedded Systems

JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

M.TECH.- II YEAR- I SEMESTER

EMBEDDED SYSTEMS

MEMORY TECHNOLOGIES (PE – V)

Course Outcomes: At the end of the course, students will be able to:

1. Select architecture and design semiconductor memory circuits and subsystems.

2. Identify various fault models, modes and mechanisms in semiconductor memories and their

testing procedures.

3. Know, how of the state-of-the-art memory chip design

UNIT- I

Random Access Memory Technologies: Static Random-Access Memories (SRAMs), SRAM Cell

Structures, MOS SRAM Architecture, MOS SRAM Cell and Peripheral Circuit, Bipolar SRAM,

Advanced SRAM Architectures, Application Specific SRAMs.

UNIT-II

DRAMs, MOS DRAM Cell, BiCMOS DRAM, Error Failures in DRAM, Advanced DRAM Design and

Architecture, Application Specific DRAMs. SRAM and DRAM Memory controllers.

UNIT-III

Non-Volatile Memories: Masked ROMs, PROMs, Bipolar & CMOS PROM, EEPROMs, Floating Gate

EPROM Cell, OTP EPROM, EEPROMs, Non-volatile SRAM, Flash Memories.

UNIT-IV

Advanced Memory Technologies and High-density Memory Packing Technologies: Ferroelectric

Random Access Memories (FRAMs), Gallium Arsenide (GaAs) FRAMs, Analog Memories, Magneto

Resistive Random Access Memories (MRAMs), Experimental Memory Devices.

UNIT-V

Memory Hybrids (2D & 3D), Memory Stacks, Memory Testing and Reliability Issues, Memory Cards,

High Density Memory Packaging.

TEXTBOOKS:

1. Ashok K Sharma, “Advanced Semiconductor Memories: Architectures, Designs and

Applications”, Wiley Interscience

2. Kiyoo Itoh, “VLSI memory chip design”, Springer International Edition

REFERENCES:

1. Ashok K Sharma,” Semiconductor Memories: Technology, Testing and Reliability , PHI

You might also like

- EASA Part 66 Module 5 Digital Techniques Electronic Instrument Systems 4 Days PDFDocument4 pagesEASA Part 66 Module 5 Digital Techniques Electronic Instrument Systems 4 Days PDFRaj MohanNo ratings yet

- EMW QuizDocument7 pagesEMW QuizNaresh Kumar100% (3)

- EC574Document1 pageEC574utkarsh rajwanshNo ratings yet

- 18vlpe07 Design of Semiconductor MemoriesDocument2 pages18vlpe07 Design of Semiconductor Memorieskruthikah apNo ratings yet

- Lesson Plan MEDocument4 pagesLesson Plan MEsonsfhsdlfhsadhNo ratings yet

- Embedded System: Shibu K VDocument24 pagesEmbedded System: Shibu K Vharish100% (1)

- Ece5023 Memory-Design-And-testing TH 1.1 47 Ece5023Document2 pagesEce5023 Memory-Design-And-testing TH 1.1 47 Ece5023Bhargavi PatilNo ratings yet

- Electronics: Challenges and Applications of Emerging Nonvolatile Memory DevicesDocument24 pagesElectronics: Challenges and Applications of Emerging Nonvolatile Memory DevicesGio SssNo ratings yet

- 02 - R20 I Yr M.Tech (Embedded Systems) I Sem - SyllabusDocument36 pages02 - R20 I Yr M.Tech (Embedded Systems) I Sem - SyllabusmohanNo ratings yet

- Vlsi DesignDocument2 pagesVlsi DesignShribala NagulNo ratings yet

- UntitledDocument2 pagesUntitledDr. M Kiran KumarNo ratings yet

- ARM Based Development SyllabusDocument3 pagesARM Based Development SyllabusMANIKANDANNo ratings yet

- IEEE-Spin Transfer Torque MemoriesDocument40 pagesIEEE-Spin Transfer Torque MemoriesScott Backster ClarckNo ratings yet

- r19 Mtech Emb Full-30-39Document10 pagesr19 Mtech Emb Full-30-39saikanna427No ratings yet

- r19 Mtech Emb Full-10-19Document10 pagesr19 Mtech Emb Full-10-19saikanna427No ratings yet

- Module 12345Document110 pagesModule 12345Paul StarkNo ratings yet

- Module 123Document56 pagesModule 123Paul StarkNo ratings yet

- Digital SynopsisDocument4 pagesDigital SynopsisSunny KumarNo ratings yet

- COAVITDocument3 pagesCOAVITnikshithNo ratings yet

- M.Tech. VLSI Design (OU) Syllabus I+II+III+IV SemDocument15 pagesM.Tech. VLSI Design (OU) Syllabus I+II+III+IV SemMs. Bhavini KumawatNo ratings yet

- Vlsi System DesignDocument12 pagesVlsi System DesignMahender GoudNo ratings yet

- Embedded Systems NotesDocument115 pagesEmbedded Systems NotesJayamurugan MookkanNo ratings yet

- Sathya Narayanan P Saveetha Engineering College: Assistant Professor, Dept. of EEEDocument7 pagesSathya Narayanan P Saveetha Engineering College: Assistant Professor, Dept. of EEEsathyatnNo ratings yet

- Vlsi DesignDocument12 pagesVlsi DesignTanveer AhmedNo ratings yet

- Embedded and Real Time SystemsDocument6 pagesEmbedded and Real Time Systemsjayarajan0% (1)

- M-Ram: Submitted To: Submitted byDocument27 pagesM-Ram: Submitted To: Submitted byAnand RajaNo ratings yet

- Esd Unit II Part3Document14 pagesEsd Unit II Part3Manoj GuptaNo ratings yet

- Comparative Study of Technology in Semiconductor Memories-A ReviewDocument5 pagesComparative Study of Technology in Semiconductor Memories-A ReviewAlexis RodríguezNo ratings yet

- Teaching Plan: RGM College of Engineering & Technology, Nandyal-518 501Document6 pagesTeaching Plan: RGM College of Engineering & Technology, Nandyal-518 501Tara GonzalesNo ratings yet

- RTM Emulator FPL PDFDocument8 pagesRTM Emulator FPL PDFB37Vinita KumariNo ratings yet

- HDocument2 pagesH;(No ratings yet

- B.E. ECE FinalDocument45 pagesB.E. ECE FinalKesav RameshKumarNo ratings yet

- SUMSEM-2021-22 ECE5025 TH VL2021220701096 Reference Material I 09-07-2022 11 12Document108 pagesSUMSEM-2021-22 ECE5025 TH VL2021220701096 Reference Material I 09-07-2022 11 12prakhar vishwakarmaNo ratings yet

- VLSI2014 T6B Abstract PDFDocument2 pagesVLSI2014 T6B Abstract PDFPD AneeshNo ratings yet

- 11L504 EMBEDDED SYSTEMS SyllabusDocument2 pages11L504 EMBEDDED SYSTEMS SyllabusveerakumarsNo ratings yet

- Memristor - Report 2019 06 27Document52 pagesMemristor - Report 2019 06 27Kleon TriantafillidisNo ratings yet

- Course Pre-Requisite: BE Electronics Engineering (R-2012)Document24 pagesCourse Pre-Requisite: BE Electronics Engineering (R-2012)Hannan SatopayNo ratings yet

- Ec6703 Embedded and Real Time SystemsDocument1 pageEc6703 Embedded and Real Time SystemsVijayaraghavan VNo ratings yet

- KTU MTech CSE 2015scheme S1 2015 SyllabusDocument17 pagesKTU MTech CSE 2015scheme S1 2015 SyllabusSurya KotamrajaNo ratings yet

- JNTU Anantapur M.tech Syllabus For Embedded Systems 2009 10Document19 pagesJNTU Anantapur M.tech Syllabus For Embedded Systems 2009 10RajeshNo ratings yet

- IC Design TechniquesDocument1 pageIC Design TechniqueskoushikNo ratings yet

- Ec 2203 Digital ElectronicsDocument1 pageEc 2203 Digital ElectronicsMaheswaran UmaiyorupaganNo ratings yet

- Embedded - Systems - II SemDocument24 pagesEmbedded - Systems - II SemravinarsingojuNo ratings yet

- Teaching Plan: RGM College of Engineering & Technology, Nandyal-518 501Document6 pagesTeaching Plan: RGM College of Engineering & Technology, Nandyal-518 501Tara GonzalesNo ratings yet

- Nvsim: A Circuit-Level Performance, Energy, and Area Model For Emerging Nonvolatile MemoryDocument14 pagesNvsim: A Circuit-Level Performance, Energy, and Area Model For Emerging Nonvolatile MemorytakahashikeyakiNo ratings yet

- Lecture 6 PDFDocument14 pagesLecture 6 PDFtestscribd9898No ratings yet

- تركيب فصل ثالث_mergedDocument5 pagesتركيب فصل ثالث_mergedameeralsaidy2No ratings yet

- Embedded System: Shibu K VDocument29 pagesEmbedded System: Shibu K VharishNo ratings yet

- Embedded Systems DesignDocument138 pagesEmbedded Systems DesignAsante WilliamNo ratings yet

- 8 Cse R13 Iv-IiDocument12 pages8 Cse R13 Iv-IiKranthi KumarNo ratings yet

- MTech VLSI Design 1st Sem SyllabusDocument5 pagesMTech VLSI Design 1st Sem SyllabusPrakash Sinha100% (1)

- Embedded Systems DesignDocument141 pagesEmbedded Systems DesignAryan Hrushik SharmaNo ratings yet

- CSCI 8150 Advanced Computer ArchitectureDocument19 pagesCSCI 8150 Advanced Computer ArchitectureHarsh BhardwajNo ratings yet

- An Hybrid EDRAM SRAM Macrocell To ImplemDocument9 pagesAn Hybrid EDRAM SRAM Macrocell To ImplemYAAKOV SOLOMONNo ratings yet

- CS82 Advanced Computer Architecture: Parallel Computer Models 1.2 Multiprocessors and MulticomputersDocument19 pagesCS82 Advanced Computer Architecture: Parallel Computer Models 1.2 Multiprocessors and MulticomputersamithaNo ratings yet

- Advanced Test Methods for SRAMs: Effective Solutions for Dynamic Fault Detection in Nanoscaled TechnologiesFrom EverandAdvanced Test Methods for SRAMs: Effective Solutions for Dynamic Fault Detection in Nanoscaled TechnologiesNo ratings yet

- Embedded Deep Learning: Algorithms, Architectures and Circuits for Always-on Neural Network ProcessingFrom EverandEmbedded Deep Learning: Algorithms, Architectures and Circuits for Always-on Neural Network ProcessingNo ratings yet

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- Computer Science: Learn about Algorithms, Cybersecurity, Databases, Operating Systems, and Web DesignFrom EverandComputer Science: Learn about Algorithms, Cybersecurity, Databases, Operating Systems, and Web DesignNo ratings yet

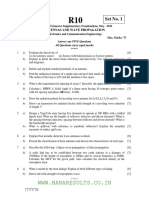

- WWW Manaresults Co inDocument2 pagesWWW Manaresults Co inNaresh KumarNo ratings yet

- WWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksDocument2 pagesWWW - Manaresults.Co - In: Answer Any FIVE Questions All Questions Carry Equal MarksNaresh KumarNo ratings yet

- Criterion 3 UG NBADocument39 pagesCriterion 3 UG NBANaresh KumarNo ratings yet

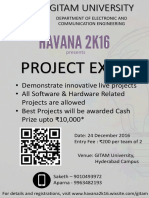

- HAVANA Brochure 1 FinalDocument12 pagesHAVANA Brochure 1 FinalNaresh KumarNo ratings yet

- Scada Systems and Its Applications: Instructions To CandidatesDocument1 pageScada Systems and Its Applications: Instructions To CandidatesNaresh KumarNo ratings yet

- 19ecs431 - Embedded SystemsDocument18 pages19ecs431 - Embedded SystemsNaresh KumarNo ratings yet

- Scada Systems and ApplicationsDocument2 pagesScada Systems and ApplicationsNaresh KumarNo ratings yet

- Scada Systems and Applications Jun 2020Document1 pageScada Systems and Applications Jun 2020Naresh KumarNo ratings yet

- Scheme - I Sample Question PaperDocument4 pagesScheme - I Sample Question PaperNaresh KumarNo ratings yet

- JNTUK - M Tech - 2017 - 2nd Semester-H6810052017 SEMICONDUCTOR MEMORY DESIGN AND TESTINGDocument1 pageJNTUK - M Tech - 2017 - 2nd Semester-H6810052017 SEMICONDUCTOR MEMORY DESIGN AND TESTINGNaresh KumarNo ratings yet

- JNTU Kakinada - M.Tech - EMBEDDED REAL TIME OPERATING SYSTEMSDocument7 pagesJNTU Kakinada - M.Tech - EMBEDDED REAL TIME OPERATING SYSTEMSNaresh KumarNo ratings yet

- IoT Lesson PlanDocument2 pagesIoT Lesson PlanNaresh KumarNo ratings yet

- JNTU ANANTAPUR - 2016 - 9A04701 Embedded Real Time Operating SystemsDocument1 pageJNTU ANANTAPUR - 2016 - 9A04701 Embedded Real Time Operating SystemsNaresh KumarNo ratings yet

- System Design Using FPGAsDocument1 pageSystem Design Using FPGAsNaresh KumarNo ratings yet

- CV 2 MarksDocument9 pagesCV 2 MarksNaresh KumarNo ratings yet

- AWP Question Paper 2015Document4 pagesAWP Question Paper 2015Naresh KumarNo ratings yet

- Triple DES Using 3 Key MethodDocument3 pagesTriple DES Using 3 Key MethodNaresh KumarNo ratings yet

- Malla Reddy Engineering College: B. Tech. Iv Semester (Mr15) Regular End ExaminationsDocument2 pagesMalla Reddy Engineering College: B. Tech. Iv Semester (Mr15) Regular End ExaminationsNaresh KumarNo ratings yet

- Eec207: Electromagnetic Waves L T P C 3 1 0 4Document2 pagesEec207: Electromagnetic Waves L T P C 3 1 0 4Naresh KumarNo ratings yet

- School of Technology GITAM Deemed To Be UniversityDocument3 pagesSchool of Technology GITAM Deemed To Be UniversityNaresh KumarNo ratings yet

- Project Expo PosterDocument1 pageProject Expo PosterNaresh KumarNo ratings yet

- AWP Question Paper2 2016Document1 pageAWP Question Paper2 2016Naresh KumarNo ratings yet

- B.Tech. DEGREE Examination Electronics & Communication EngineeringDocument2 pagesB.Tech. DEGREE Examination Electronics & Communication EngineeringNaresh KumarNo ratings yet

- AWP Question Paper 2016Document1 pageAWP Question Paper 2016Naresh KumarNo ratings yet

- Malla Reddy Engineering College: B. Tech. Iv Semester (Mr15) Regular End ExaminationsDocument2 pagesMalla Reddy Engineering College: B. Tech. Iv Semester (Mr15) Regular End ExaminationsNaresh KumarNo ratings yet

- Eec403: Microwave EngineeringDocument1 pageEec403: Microwave EngineeringNaresh KumarNo ratings yet

- M.Tech. Degree Examination Embedded Systems: (EPRES 233)Document2 pagesM.Tech. Degree Examination Embedded Systems: (EPRES 233)Naresh KumarNo ratings yet

- Teacher Course FeedbackDocument1 pageTeacher Course FeedbackNaresh KumarNo ratings yet

- 6438nr-Digital System DesignDocument2 pages6438nr-Digital System DesignNaresh KumarNo ratings yet