Professional Documents

Culture Documents

Cascode High Swing Precise

Cascode High Swing Precise

Uploaded by

lorisCopyright:

Available Formats

You might also like

- LAB4Document9 pagesLAB4Juan Camilo Guarnizo Bermudez100% (1)

- Knowledge Management Applied For British AirwaysDocument7 pagesKnowledge Management Applied For British AirwaysAlexandra GalloNo ratings yet

- D&T Department Handbook 2014 05112014Document83 pagesD&T Department Handbook 2014 05112014designmra100% (1)

- Pages From Microelectronic Circuits, 7th EditionDocument11 pagesPages From Microelectronic Circuits, 7th Editionguduru babuNo ratings yet

- 2009 10 15 LIME Appendix B Erlang B TableDocument4 pages2009 10 15 LIME Appendix B Erlang B TableSardar A A KhanNo ratings yet

- Co2 S8Document17 pagesCo2 S8Lakshmi JagupillaNo ratings yet

- 320 Lecture 29Document8 pages320 Lecture 29Kirubel MulugetaNo ratings yet

- Ee618 PDFDocument39 pagesEe618 PDFfilmfilmfNo ratings yet

- Differential AmplifierDocument24 pagesDifferential AmplifierT H ChoudhuryNo ratings yet

- Varun Sharma 2018eeb1193 Analog Lab Exp - 2 ReportDocument16 pagesVarun Sharma 2018eeb1193 Analog Lab Exp - 2 ReportVarun SharmaNo ratings yet

- Wide Swing Cascode Current MirrorDocument4 pagesWide Swing Cascode Current MirrorSunil M. PaiNo ratings yet

- 320 Lecture 27Document8 pages320 Lecture 27Gathy BrayohNo ratings yet

- Mosfet CharacteristicsDocument8 pagesMosfet CharacteristicsTim PriceNo ratings yet

- Assignment 4Document10 pagesAssignment 4Arnon PukhrambamNo ratings yet

- 320 Lecture 26Document8 pages320 Lecture 26marcelofilgueirasNo ratings yet

- Sedra8e Solvedproblems ch09-2 PDFDocument24 pagesSedra8e Solvedproblems ch09-2 PDFJoh CheNo ratings yet

- Analog Circuit Design Notes-3Document22 pagesAnalog Circuit Design Notes-3itsnirosNo ratings yet

- Opamp 24Document111 pagesOpamp 24api-3750190No ratings yet

- Tutorial 2023 - AnsDocument3 pagesTutorial 2023 - Anschetannp121No ratings yet

- Analog IcDocument3 pagesAnalog IcPraveen kumarNo ratings yet

- ENEE 3543 - Homework 4 - SolutionsDocument4 pagesENEE 3543 - Homework 4 - SolutionsTSwayNo ratings yet

- Chapter 11Document15 pagesChapter 11Bengt HörbergNo ratings yet

- Basic MOS Device Physics: Zou Zhige 2007 HUSTDocument62 pagesBasic MOS Device Physics: Zou Zhige 2007 HUSTSHIVA VERMANo ratings yet

- Unit 2Document89 pagesUnit 2Jatin AgarwalNo ratings yet

- 320 Lecture 28Document7 pages320 Lecture 28Kirubel MulugetaNo ratings yet

- Biasing Methods For MOSFET: Unit IDocument33 pagesBiasing Methods For MOSFET: Unit IAkashranjan SinghNo ratings yet

- Practice ProblemsDocument8 pagesPractice ProblemsAnonymous 3iKnfLKVMNo ratings yet

- Differential Amplifier 1Document4 pagesDifferential Amplifier 1Eslam ElnagarNo ratings yet

- 320 Lecture 37Document10 pages320 Lecture 37shivaniNo ratings yet

- Applied Electronics II (Chapter 2)Document29 pagesApplied Electronics II (Chapter 2)Ermias Mesfin100% (2)

- Threshold Voltage MosfetDocument6 pagesThreshold Voltage MosfetsantoshineepandaNo ratings yet

- Mos Field-Effect Transistors (Mosfets) : Section 5.1: Device Structure and Physical OperationDocument16 pagesMos Field-Effect Transistors (Mosfets) : Section 5.1: Device Structure and Physical OperationJohn Paul Alcantara Nidoy100% (1)

- High-Swing Cascode Biasing: SizingDocument1 pageHigh-Swing Cascode Biasing: SizingDebolina GhoshNo ratings yet

- Lec02 Ae Ms14Document59 pagesLec02 Ae Ms14Mohsin Abbas ZafarNo ratings yet

- Differential & Multistage Amplifiers: Electronic Circuit Design 1Document25 pagesDifferential & Multistage Amplifiers: Electronic Circuit Design 1Nam zzzNo ratings yet

- MOSFET Output ResistanceDocument2 pagesMOSFET Output ResistanceMerlin SkariahNo ratings yet

- MOSFET Small Signal Analysy and BiasingDocument6 pagesMOSFET Small Signal Analysy and BiasingECHAVEZ TRILLOS FRANCISCO JAVIERNo ratings yet

- Self Biased Complementary Folded Cascode Op AmpDocument3 pagesSelf Biased Complementary Folded Cascode Op AmpCapitaneanu StefanNo ratings yet

- CS AmplifierDocument7 pagesCS AmplifierBruce van NiekerkNo ratings yet

- CMOS Current Mirror With Enhanced Input Dynamic Range: Letter To The EditorDocument9 pagesCMOS Current Mirror With Enhanced Input Dynamic Range: Letter To The Editor15151516No ratings yet

- Session 4 - MOSFET - ExercisesDocument4 pagesSession 4 - MOSFET - ExercisesAjay Sampath100% (1)

- Example4 PDFDocument5 pagesExample4 PDFsarim rizviNo ratings yet

- Example 4Document5 pagesExample 4Mai Anh ThưNo ratings yet

- Example 4Document5 pagesExample 4Aiden An CamreNo ratings yet

- Example 4Document5 pagesExample 4salman1992No ratings yet

- Soln Midsem 20Document10 pagesSoln Midsem 20Akul Kumar SinghNo ratings yet

- 3.3.3 CS Stage With Current-Source Load: V m1 m2 O1 O2Document2 pages3.3.3 CS Stage With Current-Source Load: V m1 m2 O1 O2Nguyễn HiếuNo ratings yet

- EC-537 CMOS Design of Analog Integrated Circuits: X X X DD XDocument5 pagesEC-537 CMOS Design of Analog Integrated Circuits: X X X DD XTamilmani NatarajanNo ratings yet

- 2024 Advanced VLSI Design MEL G623 Spring Semester 2024: Tutorial 06 Date: Sat 24 Feb 2024Document6 pages2024 Advanced VLSI Design MEL G623 Spring Semester 2024: Tutorial 06 Date: Sat 24 Feb 2024Eashwer TenNo ratings yet

- Tutorial-3 With SolutionsDocument3 pagesTutorial-3 With SolutionsSandesh RSNo ratings yet

- EeeDocument15 pagesEeeSoma SinhaNo ratings yet

- Layout of The Cmos InverterDocument20 pagesLayout of The Cmos InvertercngindiNo ratings yet

- AE Final Term AssignmentDocument1 pageAE Final Term AssignmentxdbenerobeNo ratings yet

- Mosfet DC AnalysisDocument13 pagesMosfet DC AnalysiswaqarNo ratings yet

- Electronics Design MOSFETDocument14 pagesElectronics Design MOSFETbhanuNo ratings yet

- HW4Document11 pagesHW4dingdongitsdeb0% (1)

- BR Magzine3Document4 pagesBR Magzine3Chau Nguyen MinhNo ratings yet

- Chapter (5) Part (2) (Long Channel MOSFET)Document22 pagesChapter (5) Part (2) (Long Channel MOSFET)Ahmed SalehNo ratings yet

- Sheet 2Document3 pagesSheet 2ebramNo ratings yet

- Analog VLSI Test PaperDocument1 pageAnalog VLSI Test Paperwaibhav sonewaneNo ratings yet

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterFrom EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterNo ratings yet

- Semiconducting III–V Compounds: International Series of Monographs on SemiconductorsFrom EverandSemiconducting III–V Compounds: International Series of Monographs on SemiconductorsNo ratings yet

- Akash S Resume PDFDocument1 pageAkash S Resume PDFAkashNo ratings yet

- XnViewMP For BeginnersDocument13 pagesXnViewMP For BeginnersFarhanNo ratings yet

- W11 Server Active SyncDocument116 pagesW11 Server Active Syncapi-3708138No ratings yet

- Vission 20 20 Micro Controller Operation Service Manual 35391sc 2 6 en Us 1574754 PDFDocument342 pagesVission 20 20 Micro Controller Operation Service Manual 35391sc 2 6 en Us 1574754 PDFMario PerezNo ratings yet

- Signiant File Transfer ApplicationDocument5 pagesSigniant File Transfer ApplicationGyas AhmadNo ratings yet

- Slci Ug PDFDocument75 pagesSlci Ug PDFOingo BoingoNo ratings yet

- 2008-2009 Ssang Yong Rexton Y285 Owner ManualDocument623 pages2008-2009 Ssang Yong Rexton Y285 Owner Manualbogdanxp2000No ratings yet

- QoS in 2G Abis Over IPDocument9 pagesQoS in 2G Abis Over IPIrwansyahYoga100% (1)

- 21110-Fillable Application ElecDocument1 page21110-Fillable Application ElecWillie “Junnies” DiazNo ratings yet

- l04 Introduction To Factorytalk MeDocument264 pagesl04 Introduction To Factorytalk MeElbari OmarNo ratings yet

- User Manual For Naxys Ethernet Hydrophone Model 02345 Manual - February 2008Document20 pagesUser Manual For Naxys Ethernet Hydrophone Model 02345 Manual - February 2008JAIME CIFUENTESNo ratings yet

- Engine Control System Alt. Japanese Transaltion PDFDocument160 pagesEngine Control System Alt. Japanese Transaltion PDFscott glackenNo ratings yet

- Planar URL136-TDocument3 pagesPlanar URL136-Tnatehc7No ratings yet

- 50+ Handy Facebook Abbreviations For Texting & ChattingDocument10 pages50+ Handy Facebook Abbreviations For Texting & ChattingKathryn DiazNo ratings yet

- Introduction To DNP3: TutorialDocument3 pagesIntroduction To DNP3: TutorialWesleyNahNo ratings yet

- Sraf Lite Browser OverviewDocument2 pagesSraf Lite Browser OverviewFrancesco Antonioli DottiNo ratings yet

- A Vertical Search Engine For Medical StandardsDocument3 pagesA Vertical Search Engine For Medical StandardskumarraviranchiNo ratings yet

- Pizza HutDocument2 pagesPizza HutHarjeet KourNo ratings yet

- Digital Logic Design - Good - 05 - Building Blocks With MemoryDocument52 pagesDigital Logic Design - Good - 05 - Building Blocks With MemoryAkanksha PandeNo ratings yet

- GP 1245Document2 pagesGP 1245api-170472102No ratings yet

- Mosunmola Tech. Writing 2Document15 pagesMosunmola Tech. Writing 2falanahedowuNo ratings yet

- Technology ResourcesDocument3 pagesTechnology Resourcesapi-520247537No ratings yet

- Working With Power Queries Using Blue PrismDocument11 pagesWorking With Power Queries Using Blue Prismemail2mesuryaNo ratings yet

- 2K18 PS 007 Cbcs REG Slip PDFDocument1 page2K18 PS 007 Cbcs REG Slip PDFAkash Rai 2k18ps007No ratings yet

- Production and Supply Chain Management Information SystemsDocument20 pagesProduction and Supply Chain Management Information SystemsBilal IftikharNo ratings yet

- F 7611872Document2 pagesF 7611872Farhad MeharNo ratings yet

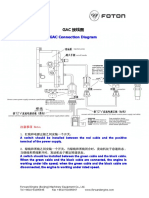

- GAC Connection Diagram PDFDocument1 pageGAC Connection Diagram PDFThomasRudyNo ratings yet

Cascode High Swing Precise

Cascode High Swing Precise

Uploaded by

lorisOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cascode High Swing Precise

Cascode High Swing Precise

Uploaded by

lorisCopyright:

Available Formats

P. Bruschi: Notes on Mixed Signal Design Chap 3, Part.

Wide swing cascode with precise current gain.

The six MOSFET mirror shown in Fig. 9 solves the problem of the output voltage range, since Vmin can

be designed to be as small as 2VDSAT. Unfortunately, its precision is poor, since M2 and M1 has different

VDS. Furthermore, the input voltage is still 2VGS.

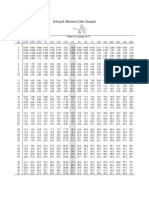

Figure 9. Low precision, wide swing cascode current mirror

Figure 10. (a) High precision, wide swing cascode current mirror with low input voltage. (b) Generation of bias voltage VK

The cascode mirror shown in Fig.10 (a) solves all these problems. It requires an auxiliary voltage, Vk,

to bias the gates of M3 and M4. To study this circuit, we can start by writing VDS1 and VDS2:

VDS 1 Vk VGS 3

(31)

VDS 2 Vk VGS 4

Choosing 4/3=2/1=kM we obtain VGS3=VGS4, as in a conventional cascode, so that VDS1=VDS2. This

relationship guarantees that the mirror is precise, in the sense that the actual current gain is equal to the

ratio 2/1.

Voltage Vk should be chosen to keep M1 and M2 in saturation region. Therefore:

1

P. Bruschi: Notes on Mixed Signal Design Chap 3, Part.1

Vk VDSAT 2 VGS 4 (32)

Voltage Vk can be properly chosen to make VDS1 and VDS2 close to the transition to triode region, so

that:

VDS 2 VDSAT 2 VGS 2 Vt Vmin VDSAT 2 VDSAT 4 (33)

In this way Vmin is only equal to 2VDSAT. The condition on Vk becomes:

Vk VDS 2 VGS 4 VGS Vt 2 VGS Vt 4 Vt 4 (34)

Voltage Vk can be produced by the circuit shown in Fig.10 (b). Considering Eq.(34) we can write:

Vk VGS 5 Vt 5 VGS Vt 5 VGS Vt 2 VGS Vt 4 Vt 4 (35)

Note that the source of M5 is grounded, while M4 source is at potential VDS2, which, being close to

VDSAT2, is of the order of a few hundred millivolts. Therefore, the body effect on Vt4 is small and we can

consider that Vt 4 Vt 5 . Then:

VGS Vt 5 VGS Vt 2 VGS Vt 4 (36)

Current Ibias and M4 aspect ratio (W/L) should be properly designed to obtain the equality (36). Voltage

Vk should also keep M3 in saturation region. Note that VD3=VGS1. Therefore, we must guarantee that:

VD 3 VGS1 Vk Vt 3 (37)

Finally, we note that the input voltage is simply equal to VGS1, like in simple current mirrors.

Final considerations.

The precision, wide swing cascode current mirror shown in Fig.10 offers a low Vmin

(Vmin=2VDSAT), relatively low input voltage (Vin=VGS), and also precise current gains.

This mirror requires accurate design in order to satisfy conditions (32) and (37) over the whole

range of input currents.

You might also like

- LAB4Document9 pagesLAB4Juan Camilo Guarnizo Bermudez100% (1)

- Knowledge Management Applied For British AirwaysDocument7 pagesKnowledge Management Applied For British AirwaysAlexandra GalloNo ratings yet

- D&T Department Handbook 2014 05112014Document83 pagesD&T Department Handbook 2014 05112014designmra100% (1)

- Pages From Microelectronic Circuits, 7th EditionDocument11 pagesPages From Microelectronic Circuits, 7th Editionguduru babuNo ratings yet

- 2009 10 15 LIME Appendix B Erlang B TableDocument4 pages2009 10 15 LIME Appendix B Erlang B TableSardar A A KhanNo ratings yet

- Co2 S8Document17 pagesCo2 S8Lakshmi JagupillaNo ratings yet

- 320 Lecture 29Document8 pages320 Lecture 29Kirubel MulugetaNo ratings yet

- Ee618 PDFDocument39 pagesEe618 PDFfilmfilmfNo ratings yet

- Differential AmplifierDocument24 pagesDifferential AmplifierT H ChoudhuryNo ratings yet

- Varun Sharma 2018eeb1193 Analog Lab Exp - 2 ReportDocument16 pagesVarun Sharma 2018eeb1193 Analog Lab Exp - 2 ReportVarun SharmaNo ratings yet

- Wide Swing Cascode Current MirrorDocument4 pagesWide Swing Cascode Current MirrorSunil M. PaiNo ratings yet

- 320 Lecture 27Document8 pages320 Lecture 27Gathy BrayohNo ratings yet

- Mosfet CharacteristicsDocument8 pagesMosfet CharacteristicsTim PriceNo ratings yet

- Assignment 4Document10 pagesAssignment 4Arnon PukhrambamNo ratings yet

- 320 Lecture 26Document8 pages320 Lecture 26marcelofilgueirasNo ratings yet

- Sedra8e Solvedproblems ch09-2 PDFDocument24 pagesSedra8e Solvedproblems ch09-2 PDFJoh CheNo ratings yet

- Analog Circuit Design Notes-3Document22 pagesAnalog Circuit Design Notes-3itsnirosNo ratings yet

- Opamp 24Document111 pagesOpamp 24api-3750190No ratings yet

- Tutorial 2023 - AnsDocument3 pagesTutorial 2023 - Anschetannp121No ratings yet

- Analog IcDocument3 pagesAnalog IcPraveen kumarNo ratings yet

- ENEE 3543 - Homework 4 - SolutionsDocument4 pagesENEE 3543 - Homework 4 - SolutionsTSwayNo ratings yet

- Chapter 11Document15 pagesChapter 11Bengt HörbergNo ratings yet

- Basic MOS Device Physics: Zou Zhige 2007 HUSTDocument62 pagesBasic MOS Device Physics: Zou Zhige 2007 HUSTSHIVA VERMANo ratings yet

- Unit 2Document89 pagesUnit 2Jatin AgarwalNo ratings yet

- 320 Lecture 28Document7 pages320 Lecture 28Kirubel MulugetaNo ratings yet

- Biasing Methods For MOSFET: Unit IDocument33 pagesBiasing Methods For MOSFET: Unit IAkashranjan SinghNo ratings yet

- Practice ProblemsDocument8 pagesPractice ProblemsAnonymous 3iKnfLKVMNo ratings yet

- Differential Amplifier 1Document4 pagesDifferential Amplifier 1Eslam ElnagarNo ratings yet

- 320 Lecture 37Document10 pages320 Lecture 37shivaniNo ratings yet

- Applied Electronics II (Chapter 2)Document29 pagesApplied Electronics II (Chapter 2)Ermias Mesfin100% (2)

- Threshold Voltage MosfetDocument6 pagesThreshold Voltage MosfetsantoshineepandaNo ratings yet

- Mos Field-Effect Transistors (Mosfets) : Section 5.1: Device Structure and Physical OperationDocument16 pagesMos Field-Effect Transistors (Mosfets) : Section 5.1: Device Structure and Physical OperationJohn Paul Alcantara Nidoy100% (1)

- High-Swing Cascode Biasing: SizingDocument1 pageHigh-Swing Cascode Biasing: SizingDebolina GhoshNo ratings yet

- Lec02 Ae Ms14Document59 pagesLec02 Ae Ms14Mohsin Abbas ZafarNo ratings yet

- Differential & Multistage Amplifiers: Electronic Circuit Design 1Document25 pagesDifferential & Multistage Amplifiers: Electronic Circuit Design 1Nam zzzNo ratings yet

- MOSFET Output ResistanceDocument2 pagesMOSFET Output ResistanceMerlin SkariahNo ratings yet

- MOSFET Small Signal Analysy and BiasingDocument6 pagesMOSFET Small Signal Analysy and BiasingECHAVEZ TRILLOS FRANCISCO JAVIERNo ratings yet

- Self Biased Complementary Folded Cascode Op AmpDocument3 pagesSelf Biased Complementary Folded Cascode Op AmpCapitaneanu StefanNo ratings yet

- CS AmplifierDocument7 pagesCS AmplifierBruce van NiekerkNo ratings yet

- CMOS Current Mirror With Enhanced Input Dynamic Range: Letter To The EditorDocument9 pagesCMOS Current Mirror With Enhanced Input Dynamic Range: Letter To The Editor15151516No ratings yet

- Session 4 - MOSFET - ExercisesDocument4 pagesSession 4 - MOSFET - ExercisesAjay Sampath100% (1)

- Example4 PDFDocument5 pagesExample4 PDFsarim rizviNo ratings yet

- Example 4Document5 pagesExample 4Mai Anh ThưNo ratings yet

- Example 4Document5 pagesExample 4Aiden An CamreNo ratings yet

- Example 4Document5 pagesExample 4salman1992No ratings yet

- Soln Midsem 20Document10 pagesSoln Midsem 20Akul Kumar SinghNo ratings yet

- 3.3.3 CS Stage With Current-Source Load: V m1 m2 O1 O2Document2 pages3.3.3 CS Stage With Current-Source Load: V m1 m2 O1 O2Nguyễn HiếuNo ratings yet

- EC-537 CMOS Design of Analog Integrated Circuits: X X X DD XDocument5 pagesEC-537 CMOS Design of Analog Integrated Circuits: X X X DD XTamilmani NatarajanNo ratings yet

- 2024 Advanced VLSI Design MEL G623 Spring Semester 2024: Tutorial 06 Date: Sat 24 Feb 2024Document6 pages2024 Advanced VLSI Design MEL G623 Spring Semester 2024: Tutorial 06 Date: Sat 24 Feb 2024Eashwer TenNo ratings yet

- Tutorial-3 With SolutionsDocument3 pagesTutorial-3 With SolutionsSandesh RSNo ratings yet

- EeeDocument15 pagesEeeSoma SinhaNo ratings yet

- Layout of The Cmos InverterDocument20 pagesLayout of The Cmos InvertercngindiNo ratings yet

- AE Final Term AssignmentDocument1 pageAE Final Term AssignmentxdbenerobeNo ratings yet

- Mosfet DC AnalysisDocument13 pagesMosfet DC AnalysiswaqarNo ratings yet

- Electronics Design MOSFETDocument14 pagesElectronics Design MOSFETbhanuNo ratings yet

- HW4Document11 pagesHW4dingdongitsdeb0% (1)

- BR Magzine3Document4 pagesBR Magzine3Chau Nguyen MinhNo ratings yet

- Chapter (5) Part (2) (Long Channel MOSFET)Document22 pagesChapter (5) Part (2) (Long Channel MOSFET)Ahmed SalehNo ratings yet

- Sheet 2Document3 pagesSheet 2ebramNo ratings yet

- Analog VLSI Test PaperDocument1 pageAnalog VLSI Test Paperwaibhav sonewaneNo ratings yet

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterFrom EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterNo ratings yet

- Semiconducting III–V Compounds: International Series of Monographs on SemiconductorsFrom EverandSemiconducting III–V Compounds: International Series of Monographs on SemiconductorsNo ratings yet

- Akash S Resume PDFDocument1 pageAkash S Resume PDFAkashNo ratings yet

- XnViewMP For BeginnersDocument13 pagesXnViewMP For BeginnersFarhanNo ratings yet

- W11 Server Active SyncDocument116 pagesW11 Server Active Syncapi-3708138No ratings yet

- Vission 20 20 Micro Controller Operation Service Manual 35391sc 2 6 en Us 1574754 PDFDocument342 pagesVission 20 20 Micro Controller Operation Service Manual 35391sc 2 6 en Us 1574754 PDFMario PerezNo ratings yet

- Signiant File Transfer ApplicationDocument5 pagesSigniant File Transfer ApplicationGyas AhmadNo ratings yet

- Slci Ug PDFDocument75 pagesSlci Ug PDFOingo BoingoNo ratings yet

- 2008-2009 Ssang Yong Rexton Y285 Owner ManualDocument623 pages2008-2009 Ssang Yong Rexton Y285 Owner Manualbogdanxp2000No ratings yet

- QoS in 2G Abis Over IPDocument9 pagesQoS in 2G Abis Over IPIrwansyahYoga100% (1)

- 21110-Fillable Application ElecDocument1 page21110-Fillable Application ElecWillie “Junnies” DiazNo ratings yet

- l04 Introduction To Factorytalk MeDocument264 pagesl04 Introduction To Factorytalk MeElbari OmarNo ratings yet

- User Manual For Naxys Ethernet Hydrophone Model 02345 Manual - February 2008Document20 pagesUser Manual For Naxys Ethernet Hydrophone Model 02345 Manual - February 2008JAIME CIFUENTESNo ratings yet

- Engine Control System Alt. Japanese Transaltion PDFDocument160 pagesEngine Control System Alt. Japanese Transaltion PDFscott glackenNo ratings yet

- Planar URL136-TDocument3 pagesPlanar URL136-Tnatehc7No ratings yet

- 50+ Handy Facebook Abbreviations For Texting & ChattingDocument10 pages50+ Handy Facebook Abbreviations For Texting & ChattingKathryn DiazNo ratings yet

- Introduction To DNP3: TutorialDocument3 pagesIntroduction To DNP3: TutorialWesleyNahNo ratings yet

- Sraf Lite Browser OverviewDocument2 pagesSraf Lite Browser OverviewFrancesco Antonioli DottiNo ratings yet

- A Vertical Search Engine For Medical StandardsDocument3 pagesA Vertical Search Engine For Medical StandardskumarraviranchiNo ratings yet

- Pizza HutDocument2 pagesPizza HutHarjeet KourNo ratings yet

- Digital Logic Design - Good - 05 - Building Blocks With MemoryDocument52 pagesDigital Logic Design - Good - 05 - Building Blocks With MemoryAkanksha PandeNo ratings yet

- GP 1245Document2 pagesGP 1245api-170472102No ratings yet

- Mosunmola Tech. Writing 2Document15 pagesMosunmola Tech. Writing 2falanahedowuNo ratings yet

- Technology ResourcesDocument3 pagesTechnology Resourcesapi-520247537No ratings yet

- Working With Power Queries Using Blue PrismDocument11 pagesWorking With Power Queries Using Blue Prismemail2mesuryaNo ratings yet

- 2K18 PS 007 Cbcs REG Slip PDFDocument1 page2K18 PS 007 Cbcs REG Slip PDFAkash Rai 2k18ps007No ratings yet

- Production and Supply Chain Management Information SystemsDocument20 pagesProduction and Supply Chain Management Information SystemsBilal IftikharNo ratings yet

- F 7611872Document2 pagesF 7611872Farhad MeharNo ratings yet

- GAC Connection Diagram PDFDocument1 pageGAC Connection Diagram PDFThomasRudyNo ratings yet