Professional Documents

Culture Documents

W 2019 DSD Gtu

W 2019 DSD Gtu

Uploaded by

Sandeep kumarOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

W 2019 DSD Gtu

W 2019 DSD Gtu

Uploaded by

Sandeep kumarCopyright:

Available Formats

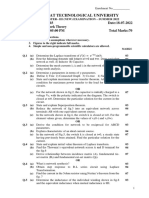

Seat No.: ________ Enrolment No.

___________

GUJARAT TECHNOLOGICAL UNIVERSITY

BE - SEMESTER– III (New) EXAMINATION – WINTER 2019

Subject Code: 3131102 Date: 30/11/2019

Subject Name: Digital System Design

Time: 02:30 PM TO 05:00 PM Total Marks: 70

Instructions:

1. Attempt all questions.

2. Make suitable assumptions wherever necessary.

3. Figures to the right indicate full marks.

MARKS

Q.1 (a) State and prove De Morgan’s theorem for 2 variables. 03

(b) Differentiate between combinational and sequential circuits. 04

(c) Design 4-bit binary to Grey code converter circuit and draw the logic 07

diagram.

Q.2 (a) Define canonical and standard forms of Boolean function and give their 03

examples.

(b) Convert 375.125 into base 2, base 8, base 16 and BCD. 04

(c) Simplify the Boolean function F(A,B,C,D)= ∑(1,3,7,11,15) using K- 07

map if don’t care conditions are 0, 2 and 5. Draw the simplified logic

diagram only using NAND gates.

OR

(c) Compare TTL, ECL and CMOS logic families and draw CMOS 07

inverter logic circuit.

Q.3 (a) Define: Encoder, Decoder, De-multiplexer. 03

(b) Describe full adder circuit with truth table and logic diagram. 04

(c) Implement the Boolean function F(W,X,Y,Z)= ∑(0,1,3,4,8,9,15) using 07

suitable multiplexer.

OR

Q.3 (a) Briefly explain the steps for VLSI design flow. 03

(b) Define a parity bit and design 3-bit odd parity generator circuit. 04

(c) Describe working principle of Programmable Logic Array with block 07

diagrams.

Q.4 (a) Derive excitation tables for R-S, J-K and T flip-flops. 03

(b) Discuss working of clocked delay type flip-flop with characteristic 04

table and logic diagram.

(c) Describe the operation of 4-bit bidirectional shift register with logic 07

diagram.

OR

Q.4 (a) Define: Register, Ripple counter, Synchronous counter. 03

(b) Explain working of Toggle flip-flop with characteristic table and logic 04

diagram.

(c) Design a counter that counts the sequence as 0, 1, 2, 4, 5, 6 and rolls 07

over to 0 again. Use +ve edge triggered J-K flip-flops.

Q.5 (a) Compare asynchronous and synchronous state machines. 03

(b) Discuss general state machine architecture. 04

(c) Define state table & state diagram. Draw state diagram of a state 07

1

machine with state table as given in Table-1. The state machine

contains input variable X and output variable Y and two flip-flops A &

B.

OR

Q.5 (a) Discuss working fundamentals behind FINFET. 03

(b) State various types of D/A converters and briefly explain any one of 04

them.

(c) Explain dual slope type A/D converter in detail. 07

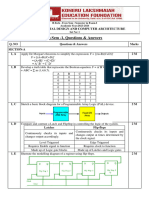

Present State Next State Output Y

AB AB

X=0 X=1 X=0 X=1

00 00 01 0 0

01 11 01 0 0

10 10 00 0 1

11 10 11 0 0

Table-1.

*************

You might also like

- Asset List For ISO 27001 Risk Assessment: Asset Table Example Asset Category Asset Element Asset OwnerDocument3 pagesAsset List For ISO 27001 Risk Assessment: Asset Table Example Asset Category Asset Element Asset OwnerDostfijiNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityKetan PatelNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityKetan PatelNo ratings yet

- Digital Electronics Circuits EC 33 SE EXAM 3RD SEM JAN 2017Document2 pagesDigital Electronics Circuits EC 33 SE EXAM 3RD SEM JAN 2017vinayakNo ratings yet

- Elec103p Exam 2015Document8 pagesElec103p Exam 2015cweqingNo ratings yet

- Addc hdlec234AIDocument6 pagesAddc hdlec234AIabhaysk1023No ratings yet

- W22 3130907Document2 pagesW22 3130907Daily GameNo ratings yet

- Nov 2019Document6 pagesNov 2019ponniNo ratings yet

- Be Winter 2020Document2 pagesBe Winter 2020SonuNo ratings yet

- Gtu Computer 3130704 Summer 2023Document2 pagesGtu Computer 3130704 Summer 2023madhavjani06No ratings yet

- Switching Theory and Logic DesignDocument10 pagesSwitching Theory and Logic DesignRajkumarBattuNo ratings yet

- Answer Two Questions, Question No. 3 Is CompulsoryDocument3 pagesAnswer Two Questions, Question No. 3 Is CompulsoryABHILESH G KNo ratings yet

- Gujarat Technological UniversityDocument4 pagesGujarat Technological UniversityParamveersinh DabhiNo ratings yet

- Summer 2019Document2 pagesSummer 2019vaxac99760No ratings yet

- Apr - May 2023Document3 pagesApr - May 2023Pandyselvi BalasubramanianNo ratings yet

- Gujarat Technological University: InstructionsDocument3 pagesGujarat Technological University: InstructionsRamesh ParmarNo ratings yet

- Solution PDFDocument5 pagesSolution PDFCedric SunNo ratings yet

- Rr210203 Switching Theory and Logic DesignDocument8 pagesRr210203 Switching Theory and Logic DesignSrinivasa Rao G100% (2)

- EE8351 Iq 16 Marks PDFDocument7 pagesEE8351 Iq 16 Marks PDFdeepika senthilNo ratings yet

- BMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsDocument3 pagesBMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsrameshNo ratings yet

- Gujarat Technological UniversityDocument4 pagesGujarat Technological UniversityRamesh ParmarNo ratings yet

- STLD Regular Jntu Question Papers 2008Document9 pagesSTLD Regular Jntu Question Papers 2008anjaneyulud100% (1)

- Question Paper Code:: Y Abcababc + + +Document3 pagesQuestion Paper Code:: Y Abcababc + + +karthick VijayanNo ratings yet

- R13 Nov 2016Document2 pagesR13 Nov 2016Anil Kumar BNo ratings yet

- 19EC303 QP RepositoryDocument4 pages19EC303 QP RepositoryssfjvhsffsNo ratings yet

- Electronics PaperDocument4 pagesElectronics Papershanelsulakkana1No ratings yet

- Hours /-: ThirdDocument3 pagesHours /-: ThirdAhmad UmarNo ratings yet

- DDCA - CO-1 & 2 - Terminal Questions & AnswersDocument15 pagesDDCA - CO-1 & 2 - Terminal Questions & AnswerskumarnandantummalaNo ratings yet

- DellDocument6 pagesDellamu_manuNo ratings yet

- Gujarat Technological University: InstructionsDocument1 pageGujarat Technological University: InstructionsmkollamNo ratings yet

- DF - Summer 2020Document2 pagesDF - Summer 2020Logo StudioNo ratings yet

- Sample - Final Exam - DLDDocument5 pagesSample - Final Exam - DLDadlinarashid03No ratings yet

- Logic Design Jan 2010 ESDocument2 pagesLogic Design Jan 2010 ESPrasad C MNo ratings yet

- Gujarat Technological UniversityDocument3 pagesGujarat Technological UniversitypatelNo ratings yet

- 5S1NVQ 303 2020Document4 pages5S1NVQ 303 2020hemantha dalugamaNo ratings yet

- S23 3130907Document2 pagesS23 3130907Daily GameNo ratings yet

- VLSI PapersDocument6 pagesVLSI PapersSandip SolankiNo ratings yet

- Be Summer 2013Document2 pagesBe Summer 2013babaf79912No ratings yet

- 15es3gcdec Jan 2018Document2 pages15es3gcdec Jan 2018MAHESHA GNo ratings yet

- Question Bank For DLCDocument8 pagesQuestion Bank For DLCAvina AshNo ratings yet

- APR2013P21Document63 pagesAPR2013P21qsashutoshNo ratings yet

- Be Summer 2015Document2 pagesBe Summer 2015babaf79912No ratings yet

- E186Document2 pagesE186asit kumarNo ratings yet

- DDCA Set-1 Insem-1 KeyDocument5 pagesDDCA Set-1 Insem-1 Keyt.harshiharshithaNo ratings yet

- Be Winter 2020Document2 pagesBe Winter 2020Chihaya FuruNo ratings yet

- Module-1: Set No. 1Document2 pagesModule-1: Set No. 1Omkar MutalikNo ratings yet

- UFMFF8-30-1 Exam Paper 2016-2017Document8 pagesUFMFF8-30-1 Exam Paper 2016-2017Irfan MemonNo ratings yet

- Be Winter 2020Document1 pageBe Winter 2020KuthjdgNo ratings yet

- BSC CSA Assignment 1Document1 pageBSC CSA Assignment 1Nagendra DuhanNo ratings yet

- De Important QuestionsDocument6 pagesDe Important QuestionsParameshwar ReddyNo ratings yet

- DeDocument2 pagesDeUrvishNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityJMehtNo ratings yet

- STLD Question BankDocument6 pagesSTLD Question Bankrachasaikiran0% (1)

- DLD QuestionsDocument3 pagesDLD QuestionsManikyarajuNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversitySuraj ThakurNo ratings yet

- EE-342 Digital ElectronicsDocument2 pagesEE-342 Digital ElectronicsDeepesh KumarNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Modeling and Simulation of Logistics Flows 3: Discrete and Continuous Flows in 2D/3DFrom EverandModeling and Simulation of Logistics Flows 3: Discrete and Continuous Flows in 2D/3DNo ratings yet

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyFrom EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNo ratings yet

- Cs Winter 21 GtuDocument3 pagesCs Winter 21 GtuSandeep kumarNo ratings yet

- DSD w20dsd GtuDocument1 pageDSD w20dsd GtuSandeep kumarNo ratings yet

- P and S Gtu Pyq Past 3 YearsDocument19 pagesP and S Gtu Pyq Past 3 YearsSandeep kumarNo ratings yet

- DSD Syll - Merged DSD GtuDocument8 pagesDSD Syll - Merged DSD GtuSandeep kumarNo ratings yet

- NT Winter 2021 Gtu PyqDocument3 pagesNT Winter 2021 Gtu PyqSandeep kumarNo ratings yet

- NT 2022 Gtu PyqDocument3 pagesNT 2022 Gtu PyqSandeep kumarNo ratings yet

- NT Pyq Combined Past 5 YearsDocument16 pagesNT Pyq Combined Past 5 YearsSandeep kumarNo ratings yet

- Netwok Theory Pyq GtuDocument2 pagesNetwok Theory Pyq GtuSandeep kumarNo ratings yet

- Change in Market and Consumer Mindset in Telecommunication Industry Because of Jio Revolution Using BCG MatrixDocument6 pagesChange in Market and Consumer Mindset in Telecommunication Industry Because of Jio Revolution Using BCG Matrixapoorv agarwalNo ratings yet

- Embedded System Lab Manual: B.Tech (Cse) Vi SemesterDocument56 pagesEmbedded System Lab Manual: B.Tech (Cse) Vi Semesterjesudosss0% (1)

- School Ict - Action PlanDocument4 pagesSchool Ict - Action PlanEmilia MalabananNo ratings yet

- Task3 Types of ComputersDocument3 pagesTask3 Types of ComputersAlfred JacobNo ratings yet

- IMTC-191 Lab 4Document6 pagesIMTC-191 Lab 4Alex 1001No ratings yet

- Comparison Analysis On Feasible Solutions For LTE Based Next Generation Railway Mobile PDFDocument7 pagesComparison Analysis On Feasible Solutions For LTE Based Next Generation Railway Mobile PDFTele KomunikaceNo ratings yet

- Expert Veri Ed, Online, Free.: Custom View SettingsDocument10 pagesExpert Veri Ed, Online, Free.: Custom View SettingsShivarajNo ratings yet

- Seminar ReportDocument47 pagesSeminar ReportPraveen YadavNo ratings yet

- Timers, Counters, Hour Meters, Time Switches: General CatalogDocument164 pagesTimers, Counters, Hour Meters, Time Switches: General CatalogyanobuntuNo ratings yet

- Category (6) - Cabling Installation (Telecommunication) : Contractors Name (E) Address Telephone Fax Email Contact PersonDocument4 pagesCategory (6) - Cabling Installation (Telecommunication) : Contractors Name (E) Address Telephone Fax Email Contact Personahmedsaber2007No ratings yet

- Inotek Antenna 5101Document1 pageInotek Antenna 5101Irfan Aziz ChNo ratings yet

- Samsung BD h5900 BD h5500 BD Hm59 BD Hm59cDocument65 pagesSamsung BD h5900 BD h5500 BD Hm59 BD Hm59cMiguel Angel CarbonellNo ratings yet

- By Bob Eckweiler, AF6C: Heathkit of The Month: #30Document7 pagesBy Bob Eckweiler, AF6C: Heathkit of The Month: #30Rafael Suarez0% (1)

- P 660hnu T1 - 1.02 PDFDocument372 pagesP 660hnu T1 - 1.02 PDFEdciel EbuenNo ratings yet

- WP1-SOP WL Q3-2019: Huawei Technologies Co., LTDDocument22 pagesWP1-SOP WL Q3-2019: Huawei Technologies Co., LTDrahmanmanNo ratings yet

- Maritime VHF-DSC Monitoring With Low Cost SDR Receiver: ISSUE No.1 MBNA Publishing House Constanta 2018Document7 pagesMaritime VHF-DSC Monitoring With Low Cost SDR Receiver: ISSUE No.1 MBNA Publishing House Constanta 2018mercury7k29750No ratings yet

- Computer Operator Mcqs With AnswersDocument6 pagesComputer Operator Mcqs With Answersraju 0400No ratings yet

- TraceDocument32 pagesTraceog9949No ratings yet

- Live Migration @alibaba Cloud - Issues Settled & Challenges Remain - 0Document19 pagesLive Migration @alibaba Cloud - Issues Settled & Challenges Remain - 0AvneeshÜbermenschBalyanNo ratings yet

- Guideline: G1117 VHF Data Exchange System (Vdes)Document29 pagesGuideline: G1117 VHF Data Exchange System (Vdes)Яков МыкольниковNo ratings yet

- DIR-2150 Ds Reva 1-01 All en 20200401Document3 pagesDIR-2150 Ds Reva 1-01 All en 20200401chujamujaNo ratings yet

- Defected Microstrip Structure Based Bandpass FilterDocument4 pagesDefected Microstrip Structure Based Bandpass FilterSubhashini MurugesanNo ratings yet

- Mikrotik FundamentalDocument126 pagesMikrotik Fundamentalkurikulum smk tel sidoarjo100% (1)

- High Performance 802.11ac Wave 2 (Wi-Fi 5) Access PointDocument4 pagesHigh Performance 802.11ac Wave 2 (Wi-Fi 5) Access PointCromNo ratings yet

- Econolite EOS Controller SoftwareDocument2 pagesEconolite EOS Controller SoftwareehsanparsonsNo ratings yet

- Mobile Code SecurityDocument39 pagesMobile Code SecurityNarender KumarNo ratings yet

- Harman Kardon AVR 132-EnDocument36 pagesHarman Kardon AVR 132-EnPascalau GeorgeNo ratings yet

- Reyee FAQ V1.0Document138 pagesReyee FAQ V1.0Prima RespatiNo ratings yet

- KPI Formulae Change Approval 1Document5 pagesKPI Formulae Change Approval 1nathaniel07No ratings yet