Professional Documents

Culture Documents

Ee619a FCH

Ee619a FCH

Uploaded by

Arshwin KumarOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ee619a FCH

Ee619a FCH

Uploaded by

Arshwin KumarCopyright:

Available Formats

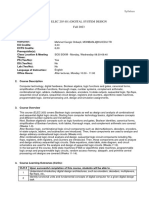

Department of Electrical Engineering

Indian Institute of Technology, Kanpur

EE 619A: VLSI System Design 2022-23 Semester II

Instructor: Dr. Rik Dey (email id: rikdey@iitk.ac.in)

Objectives: This course will cover the aspects of analysis, design and synthesis of Very Large Scale Integrated

(VLSI) circuits using Complementary Metal Oxide Semiconductor (CMOS) technology. Complex digital VLSI

systems are designed and built in a hierarchical way using integrated circuits (IC) as building blocks. This course

will provide an insight into basics of digital IC design at logic, layout, schematic, and physical levels. An emphasis

will be given on the synthesis-based approach to digital IC design starting from designing basic building blocks

of combinatorial and sequential circuits to ending with designing bigger digital systems. At the end of the course,

the student should be able to develop an understanding of the digital IC design techniques, the basic design flow

in VLSI system design automation, the trade-offs associated with the design methodologies, and methods to

systematically design complex digital VLSI systems based on the current trend and technology.

Pre-requisite: There is no official pre-requisite for the course.

Special Emphasis: This is a graduate level course on digital IC design. Hence, it is expected that the student must

have sound knowledge on undergraduate level digital circuit design. Also, the student should know the basics of

how to write simple codes.

Course Content: The content for the course has been divided in several modules as follows:

Module Content Outline Tentative Number of Lectures

Introduction, why digital, future prospects 1

CMOS transistors, models, scaling 2

CMOS fabrication and layout 1

Interconnects (wires) in CMOS technology 1

Basic CMOS logic gate characteristics 2

Circuit optimization, Method of Logical Effort 2

Combinational circuit design: CMOS logic style 1

Combinational circuit design: Pass transistor logic 1

Combinational circuit design: Logic optimization, Technology Mapping 1

Nanoscale Design, Low Power Design 1

Mid-Semester Examination

Sequential elements, Dynamic CMOS Logic 1

Design of latches and flip-flops 2

Timing analysis 1

Memory, Programmable Logic 2

Physical design: Floor planning, Routing 2

Design and Testability 1

Review, Future directions 1

End-Semester Examination

Reserved for covering other topics, Verliog, Layout, etc. 2

Schedule and Venue:

Class Timing: Tuesday and Friday from 3:30 pm – 04:45 pm. Venue: L03 in LHC (Lecture Hall Complex).

The materials related to the course will be uploaded in Mookit (Hello IITK portal) from time to time.

All the classes will be in offline mode. No video/audio recording of materials will be available.

Office Hours: Monday/Wednesday/Thursday from 3:30 pm – 5:00 pm in WL121 (Western Lab).

Please send me an email if you need any help. Extra office hours will be scheduled upon your requests.

Evaluation Components and Policies:

Attendance in class (total): 5%

Homework/Assignment (total): 15%

Two Quizzes (total): 10% (5% each)

Two Projects (total): 20% (10% each)

Mid-Semester Examination: 20%

End-Semester Examination: 30%

Policies:

• All the evaluations will be in offline mode.

• Bio-metric attendance will be taken in class and will contribute towards the total marks as mentioned above.

Only sanctioned leave from the appropriate authority will be considered if absent.

• Marks will be deducted for late submission of homework/assignment and projects. The exact scheme for

deduction of marks on late submission will be announced with each homework/assignment and project.

• One of the quizzes will be before the mid-semester examination, and one of them will be between the mid-

semester examination and the end-semester examination. The date of conducting each quiz will be announced

only a week before.

• Only the projects (not homework/assignments) should be submitted in groups of no more than 5 students, and

the details regarding the project and group formation will be announced in due time.

• There will be no make-up for any of the quizzes.

• Final grading will be relative based on the overall statistics of the class.

Course Policies: Involvement in copying and/or cheating and/or use of unfair means and/or encouraging such

behaviours will be strictly penalized and reported to the appropriate authority. If someone is found guilty in such

cases, that person may either be de-registered from the course or be awarded an F grade.

Books and References:

1. CMOS VLSI Design by Neil H.E. Weste and David Harris, 4th edition, Addison-Wesley/Pearson. Or

CMOS VLSI Design by Neil H.E. Weste, David Harris and Ayan Banerjee, 3rd Edition, Pearson Education.

2. Digital Integrated Circuits by Jan M. Rabaey, Anantha Chandrakasan and Borivoje Nikolic, 2nd Edition,

Prentice Hall India.

You might also like

- Setting Up Call Center in Pakistan - A GuideDocument49 pagesSetting Up Call Center in Pakistan - A Guideshahzor30100% (10)

- Comflex Pro Software Manual-EN PDFDocument85 pagesComflex Pro Software Manual-EN PDFjavdvelaquez100% (1)

- BECE303LDocument3 pagesBECE303LKAVIYA DIASNo ratings yet

- Fall 2023 ELEC 205 (01) Syllabus 08 09 2023Document3 pagesFall 2023 ELEC 205 (01) Syllabus 08 09 2023caggllayan47No ratings yet

- SP 507 Course ContentsDocument3 pagesSP 507 Course ContentsSoftware EngineerNo ratings yet

- Lecture 1 - Course Overview - 112053Document6 pagesLecture 1 - Course Overview - 112053rumbidzai.nyikadzinasheNo ratings yet

- Ece5015 Digital-Ic-Design Eth 1.0 40 Ece5015Document2 pagesEce5015 Digital-Ic-Design Eth 1.0 40 Ece5015Sivanantham SadhasivamNo ratings yet

- CP - COA - B.Tech CSBS - 2023 - 24Document9 pagesCP - COA - B.Tech CSBS - 2023 - 24Akshata MoreNo ratings yet

- Unit5 - COA (Autosaved)Document78 pagesUnit5 - COA (Autosaved)Sam SamNo ratings yet

- Unit2 - COA Shikha SinghDocument106 pagesUnit2 - COA Shikha SinghSam SamNo ratings yet

- MS in Embedded Systems and IOTsDocument8 pagesMS in Embedded Systems and IOTsSamir KingaNo ratings yet

- Syllabus 5th SemDocument17 pagesSyllabus 5th Semsayan.transcuratorsNo ratings yet

- ME (Updated)Document2 pagesME (Updated)AanjanayshatmaNo ratings yet

- ECE3002Document2 pagesECE3002Ritayan PatraNo ratings yet

- SoC SyllabusDocument2 pagesSoC SyllabuslokeshNo ratings yet

- ME SyllabusDocument3 pagesME Syllabusaryankamboj025No ratings yet

- Vlsi SyllabusDocument3 pagesVlsi SyllabusmadhurNo ratings yet

- ECEE 401-IntroToVLSIDocument8 pagesECEE 401-IntroToVLSIChristiensen ArandillaNo ratings yet

- VlsiDocument3 pagesVlsiMayank Karwa 16BEC0067No ratings yet

- Vlsi Circuit Design - SyllabusDocument8 pagesVlsi Circuit Design - SyllabusRiyas ANNo ratings yet

- VLSI Design Course OutlineDocument3 pagesVLSI Design Course OutlineSoftware EngineerNo ratings yet

- Unit 1Document241 pagesUnit 1jatinsingh150815No ratings yet

- Proposed - BE E & TC 2019 - VLSI SyllabusDocument3 pagesProposed - BE E & TC 2019 - VLSI SyllabusRavindra DabhadeNo ratings yet

- ELEC5402 Digital Integrated Circuit Design 2010Document4 pagesELEC5402 Digital Integrated Circuit Design 2010tssandeepkumarchoudhary@scribd0% (1)

- 2022 Ch0-Course IntroductionDocument10 pages2022 Ch0-Course IntroductionSư LưuNo ratings yet

- 5th Sem Syllabus Iem 2023Document17 pages5th Sem Syllabus Iem 2023ransom3009No ratings yet

- CA CourseFile AssignmentDocument14 pagesCA CourseFile AssignmentLaxman SinghNo ratings yet

- Unit1 COADocument135 pagesUnit1 COASam SamNo ratings yet

- Ece MT SylDocument79 pagesEce MT Sylpermiable permissionNo ratings yet

- CourseOutline VLSI - 2Document2 pagesCourseOutline VLSI - 2FaHeem KhanNo ratings yet

- Final Updated New Syllabus Mtech BPUT 2009-10 VLSI Embeded System DesignDocument11 pagesFinal Updated New Syllabus Mtech BPUT 2009-10 VLSI Embeded System Designarunbinay04No ratings yet

- SUMSEM2-2017-18 ECE5025 TH TT530A VL2017189000177 Reference Material I ECE5025 System-On-Chip-Design TH 1 AC40Document2 pagesSUMSEM2-2017-18 ECE5025 TH TT530A VL2017189000177 Reference Material I ECE5025 System-On-Chip-Design TH 1 AC40DarshilShahNo ratings yet

- Digital Systems DesignDocument7 pagesDigital Systems DesignaminhdlNo ratings yet

- CSEN3001 SyllabusDocument2 pagesCSEN3001 SyllabusAjitesh SinghNo ratings yet

- VLSI System Design SyllabusDocument2 pagesVLSI System Design SyllabusGaneshChandraNo ratings yet

- Unit1 COADocument135 pagesUnit1 COAlostNo ratings yet

- Ece 2003Document3 pagesEce 2003gokulNo ratings yet

- DLCA OutlineDocument2 pagesDLCA OutlineNaima NaeemNo ratings yet

- 17ec63 Vlsi Design SyllabusDocument2 pages17ec63 Vlsi Design SyllabusKulandaivel MurugeshNo ratings yet

- Unit 5 CNDocument160 pagesUnit 5 CNnehape4366No ratings yet

- DAA NotesDocument161 pagesDAA NotesasminumdeepmathematicsNo ratings yet

- 21ec503 Vlsi Design Unit 1Document110 pages21ec503 Vlsi Design Unit 1santhoshiniNo ratings yet

- NIT 1 4 7040 Lecture 1 VLSI EC601Document26 pagesNIT 1 4 7040 Lecture 1 VLSI EC601SANDIP PODDARNo ratings yet

- For Bachelor of Science in Information Technology (2022 Course) (With Effect From 2022-23)Document6 pagesFor Bachelor of Science in Information Technology (2022 Course) (With Effect From 2022-23)Mit MakwanaNo ratings yet

- Syllabus VLSI Technology ApplicationsDocument2 pagesSyllabus VLSI Technology ApplicationsPrajwalAgarwalNo ratings yet

- ECE 374 TsybeskovDocument2 pagesECE 374 TsybeskovMeryam BakkarNo ratings yet

- EEE F313 INSTR F313 AnalogandDigitalVLSIDesignFIrstSem 2014 15Document2 pagesEEE F313 INSTR F313 AnalogandDigitalVLSIDesignFIrstSem 2014 15Harsha DuttaNo ratings yet

- VLSI Workshop ContentDocument2 pagesVLSI Workshop ContentRavindra RathoreNo ratings yet

- Course Syllabus: United International UniversityDocument3 pagesCourse Syllabus: United International UniversityMd Sujan ArafatNo ratings yet

- VLSI ModulesDocument28 pagesVLSI Modulessai_karthik89No ratings yet

- Rutgers University, Department of Electrical and Computer Engineering Abet Course Syllabus COURSE: 14:332:366Document3 pagesRutgers University, Department of Electrical and Computer Engineering Abet Course Syllabus COURSE: 14:332:366HUANG YINo ratings yet

- Rutgers University, Department of Electrical and Computer Engineering Abet Course Syllabus COURSE: 14:332:366Document3 pagesRutgers University, Department of Electrical and Computer Engineering Abet Course Syllabus COURSE: 14:332:366HUANG YINo ratings yet

- EE 460R - Introduction To VLSIDocument3 pagesEE 460R - Introduction To VLSItrashdnpNo ratings yet

- Cmpe223 Sylabi AbetDocument3 pagesCmpe223 Sylabi AbetStrt SandyNo ratings yet

- Institute of Business Management (Iobm) : College of Engineering & Sciences (Ces)Document3 pagesInstitute of Business Management (Iobm) : College of Engineering & Sciences (Ces)Lal ChandNo ratings yet

- AEM and DE SYLLABUS 3rd SEMESTERDocument1 pageAEM and DE SYLLABUS 3rd SEMESTERAR OFFICIALNo ratings yet

- EEU33C02Document4 pagesEEU33C02Anibal SegoviaNo ratings yet

- A Dic Scripts S 2011 CompleteDocument411 pagesA Dic Scripts S 2011 CompleteAhmed TarhanNo ratings yet

- Vlsi DesignDocument3 pagesVlsi Designkumarrajivranjan440No ratings yet

- CSC204, OBE Course OutlineDocument8 pagesCSC204, OBE Course Outlineharun hakshiNo ratings yet

- Top-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsFrom EverandTop-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsNo ratings yet

- Unit 1 PythonDocument248 pagesUnit 1 Pythonviveksharma50011No ratings yet

- HONOR Watch GS Pro OnlineHelp - (KAN-B19,01, En)Document42 pagesHONOR Watch GS Pro OnlineHelp - (KAN-B19,01, En)Game BellNo ratings yet

- Philips Sharp LCD 2k9 SMDocument26 pagesPhilips Sharp LCD 2k9 SMGaby GeligeNo ratings yet

- Sharda dss10 PPT 03Document50 pagesSharda dss10 PPT 03zeid100% (1)

- Yin Et Al. - 2018 - The Implementation of IEEE 1588 Clock Synchronization Protocol BaseDocument6 pagesYin Et Al. - 2018 - The Implementation of IEEE 1588 Clock Synchronization Protocol Base张奔No ratings yet

- Ict551 (Proposal) - Cambridge Sport ApplicationDocument7 pagesIct551 (Proposal) - Cambridge Sport ApplicationAmni SyamimiNo ratings yet

- As 4071-1992 Software Project Management PlansDocument7 pagesAs 4071-1992 Software Project Management PlansSAI Global - APACNo ratings yet

- Phillip Capita On EMS Industry The Story of Local ManufacturingDocument141 pagesPhillip Capita On EMS Industry The Story of Local ManufacturingChirag ShahNo ratings yet

- Korg WavestationDocument146 pagesKorg WavestationDRAGOS BILGANo ratings yet

- F900got Connection 4 of 6Document116 pagesF900got Connection 4 of 6chaubinhkhang110686No ratings yet

- List of Game Engines - WikipediaDocument15 pagesList of Game Engines - WikipediaYash RajputNo ratings yet

- Computer Notes PDFDocument69 pagesComputer Notes PDFAyush SharmaNo ratings yet

- Content Basic MathDocument119 pagesContent Basic MathAlastair Harris100% (1)

- UNIT 7 Number System and Bases CSEC Revision TestDocument3 pagesUNIT 7 Number System and Bases CSEC Revision TestNicola NichelleNo ratings yet

- SDN in Wide-Area Networks A SurveyDocument6 pagesSDN in Wide-Area Networks A SurveyAbizwagNo ratings yet

- TONE TOTKE AUR UPAY Planets Upay GeneralDocument194 pagesTONE TOTKE AUR UPAY Planets Upay Generalajay khannaNo ratings yet

- DC LED Lights and Solar LightsDocument4 pagesDC LED Lights and Solar LightsNaldo da GraçaNo ratings yet

- Qubino Flush 1D Relay PLUS Extended Manual Eng 2.2 1Document55 pagesQubino Flush 1D Relay PLUS Extended Manual Eng 2.2 1Jan StruhačNo ratings yet

- EndResult - EnglishDocument49 pagesEndResult - EnglishKylieNo ratings yet

- Pci Compliance Guidelines: Thoroughly ExplainedDocument29 pagesPci Compliance Guidelines: Thoroughly ExplainedSyed Mohib Haider KazmiNo ratings yet

- Ahmed Samir Mohamed: Production Engineer (Plastic Injection Engineer)Document2 pagesAhmed Samir Mohamed: Production Engineer (Plastic Injection Engineer)Ahmed SamirNo ratings yet

- CAD of Geneva Mechanism: ObjectiveDocument5 pagesCAD of Geneva Mechanism: ObjectiveShamsheer HaiderNo ratings yet

- Social Media Strategies For Choruses PresentationDocument84 pagesSocial Media Strategies For Choruses PresentationEveryman EleanyaNo ratings yet

- 2024 Factsheet Bachelor of Science in Computer ScienceDocument8 pages2024 Factsheet Bachelor of Science in Computer SciencewizzytrippzNo ratings yet

- Project Title:: Submitted byDocument7 pagesProject Title:: Submitted byM shayan JavedNo ratings yet

- QW-QAL-626 - (Rev-00) - Prod. and QC Process Flow Chart - Ventura Motor No. 13 (35804)Document6 pagesQW-QAL-626 - (Rev-00) - Prod. and QC Process Flow Chart - Ventura Motor No. 13 (35804)Toso BatamNo ratings yet

- Electronic Remote Control: Operation ManualDocument30 pagesElectronic Remote Control: Operation ManualSurendran PattineyapanNo ratings yet

- 5.ECE 301 - Structural ModelingDocument32 pages5.ECE 301 - Structural ModelingenzuekNo ratings yet