Professional Documents

Culture Documents

4, Robert

4, Robert

Uploaded by

Anala MOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

4, Robert

4, Robert

Uploaded by

Anala MCopyright:

Available Formats

Gate Dielectric Scaling for High-Performance CMOS: from SiOl to High-K

Robert Chaq Suman Datta, Mark Doczy, Jack Kavalieros and Matthew Metz

Intel Corporation

5200 N.E. Elam Young Parkway, Hillshoro, OR 97124, USA. Mail-stop: RA3-252

m -

503-613-6141,

Abstract optical (SO) phonon modes arising from the polarization of

We have successfully demonstrated VeV high-performance the high-K to the inversion channel charge carriers [ref. 131,

PMOS and NMOS transistors with high-Wmetal-gate gate and that metal gate may be more effective in screening the

stacks with the right threshold V o k W for both P and high.K so phonons fro,,, coupling to the channel ,,,,der

channels on bulk Si. We believe that high-Wmetal-gate is an

inversion conditions [ref, 13-141, On the other hand, the use

option for the 45nm high-performance logic technology node.

of high-WmetaLgate requires a ptype metal and a -type

metal with the right work functions for high-performance

1. Introduction

The silicon industry has been scaling Si02 aggressively for logic applications On "Ik si [Ief. "1.

the past 15 years for low-power, high-performance CMOS We have successfully fabricated high-performance PMOS

logic as thin as 1 . 2 (physical

~ ~ Tax) has and NMOS transistors with high-Wmetabgate stacks. The

already been successfully implemented in the 90nm logic transistors have physical gate length (k) of 80nm and the

technology node [ref. I]. Research transistors with 0.8nm electrical oxide thickness (Toxe) is 1.45nm measured at

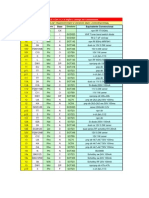

Si02 have also been demonstrated in the laboratory [ref. 2-31. inversion. Figure 8 compares the leakage characteristics of

However, continual gate dielectric scaling will require high- the high-WmetaLgate stacks with the conventional

k as si02 Will eventually OUf of atoms for further SiqipolySi. Figures 910 show the device characteristics of

scaling. Most of the high-K gate dielectrics investigated are the PMOS transistor with high-l(/metal-gate, while ~i~~~~~

Hf-hased and &based [ref. 461. Both PobSi and metals are 11-12 show the device characteristics ofthe NMOS

being evaluated as gate electrodes for the high-K dielectrics

with high-Wmetabgate, Both the high-l</metal-gate PMOS

[ref. 7-91, There are many challenges repotted in literature in

replacing with high-l( for high.perf,,rmance cM0s[ref, and NMOS transistors show very high drive performance

IO-121. This paper will present results on the 0.8nm Si02 and (Idsat) with the right Vth both p and n-ehannel

very high-performance PMOS and NMOS transistors with devices on bulk Si, with very low gate leakage.

high-Wmetal-gate for high-performance logic applications.

4. F'rom Si02 to High-K

2. Si% Scaling We have implemented 1.2nm physical Si02 in our 90nm

The physical thickness of Sio2has been scaled aggressively logic technology node 111, and have scaled physical Si02

for low.power, high.perfomance logic appl,cat,ons, ~i~~~~ 1 further down to 0.8nm and integrated it in research transistors

shows the physical thickness trend of Si02 for the various with 15nm Physical gate length which show well-controlled

logic 1 . 2 ~ physical si02 has already been short-channel characteristics. We have also successfully

successfully implemented in the 90nm logic node [ref. I]. In demonstrated high-Performance and

addition, 0.8nm physical S i 0 2 has also been produced [ref. 2- transiston with W - W m e t a k a t e gate Stacks with the right

31. TEM cross sections of the 1.2nm and 0.8nm si% gate Vfh for both P- and n-channels on bulk Si, with very low gate

oxides are shown in ~i~~~~~ 2-3, The cv and lg. leakage. We believe high-Wmetal-gate is an option for the

Vg characteristics of the 0 . 8 m Si02 are shown in ~ i g u r e s4 45nm logic technology node for high-performance CMOS,

5. Figures 6-7 show the device characteristics of the

experimental 15nm (physical gate length) NMOS transistor 5. References

with 0.8m Si@. The data shows that the 15nm transistor [I] S. Thompsonetal.,lEDMTechnicalD;~~~tgest,p.6I,2OO2.

with 0.8nm physical Si02 has well-controlled shortshannel [2] R. Chauctal., I E D M T ~ C ~ige~t,p.45,2000.

~~~C~I

characteristics. [3] R. Chau et al., Physica E, Low-dimensional Systems and N m o m c h r e ~ ,

Vol. 19,lssues 1-2,p.1,2003.

3. HighK Dielectrics [4] R. Choi et al., IEDM Technical Digcsl, p.613,2002.

It has been reported in literature [ref. 121 that Fermi level [SI G. L U C O V S ~et ai., IEDM rehnical Digest, p.617.2002.

pinning at the high-WpolySi interface causes high threshold [6] s. humiya et al., s p p . ofVLS1 Technology, p.17,2003.

voltages in MOSFET transistors. It has also been reported [7]Y. ~ i eta!.,

m s ~ pofVLsi~echnology,p.l67,2003.

.

that high-WpolySi transisbr exhibits severely degraded [XI J.H.Lee et al., IEDM Technical Digest, p.359.2002.

channel mobility due to the coupling of low energy surface [9]S.B. samavedam et al., IEDM Technical Digat, p.433,2002.

4-89114-037-2?/03 124 IWGI2003, Tokyo

[IO] R.M. Wallace, G. W i l t MRS Bulletm. Vol. 27, NO. 3. p.192. 2002. [I31 M. Fmheni et al., J. Appl. Phys.,Vol. 90,p.4587,2001

[1I]V.Misrraetal.,MRSBulletin.Vol.27,No.3,p.212.2002. [I41 S. Dam et al.. to be prcsented at 2003 IEDM.

[ I21 C. Hobbs et al., Symp. ofVLSl Technology,p.9.2003. [I 51 I. D? at al., Solid State Electron., Vol. 44,p.1077. 2000.

E E E @

Fig. 1 Scaling of physical thickness of S O 2 gale oxide Fig. 2 High resolution TEM cross section of 1.2nm

across technology generations. physical S O i gate oxide at the 90nm logic technology

node.

1 -05 0 0.5 1

vg M

Inversion Capacitance

F i g . 3 High resolution TEM cross section of 0.8nm Fig. 4 Inversion split C-V measurements o f 0.8nm

physical S O 2 gate oxide. physical S O 2 gate oxide for NMOS and PMOS.

"1'

E

,,. .

1-,

\ sal 15nmNMOS

,--

"I * 0.8"

,E-l

,I-@

4.5

y 0.5

0 O Z Q A M O d

vs (v*)

DWnVoltaaoM

Fig. 5 Inversion gate leakage measurements of 0.8nm Fig. 6 Id-Vds characteristics of 15nm Lg experimental

physical S i 0 2 gate oxide for NMOS and PMOS. NMOS transistor with 0.8nm physical S O 2 gate oxide

125 IWGI 2003,Tokyo

4

5,02,pol'rs, ',

I.E+Ql

'.L

I

- 1.ElOO

.

l

l

3

i l . E Q 6 Y S.S. ,= 95mVldecade

,

-3 HigbWmatal-gab

DlBL = 100mVN

1.M3

.-Ca 1.EQ loff = 180nAlum

r3

6 1.EQ 1.e04 1

0 5 10 15 20 25

0 0.2 0.4 0.6 0.8

bx,a,.ss I'[

Gate Voltage 0 Fig. 8 Accumulation gate leakage as a function o f electrical

Fig. 1 Id-Vg charactenstics of 15nm Lg expenmental thickness for high-Wmetal-gategate stacks. Also shown for

NMOS transntor with 0 8nm physical SiO, gate oxide comparison is leakage for Si0,ipolySi gate stack.

1E-03 -7.E-04

Vdr1.3

1E -04 -6.E-04

- 1E-05 -5.E-04

a9f 1E-06

1E-07

Ion = 693 pAlpm

loff = 25 nAlpm

f

3

9

-4.E-04

-3.E-04

1E-08 Lg = 80nm -2.E-04

1E-09 Toxe =14.5A

-l.E-04

1E-10

O.E+OO

-0.1 -0.3 -0.5 -0.7 -0.9 -1.1 -1.3

-0.1 -0.3 -0.5 -0.7 -0.9 -1.1 -1.3

v g (V)

Vds (4

Fig. 9 Id-Vg characteristics of the 80 nm Lg PMOS Fig. 10 Id-Vds characteristics ofthe 80 nm Lg PMOS

transistors with high-Wmetal-gate gate stack at Vcc=1.3V. trmsistors with high-Wmetal-gate gate stack.

l.E-02 0.0016

1.GO3 0.0014

1.E-04 0.0012

E l.E-05 g 0.001

5 l.E-06

I

p l.E-07

Ion = 1.5 mAlpm

loff = 43 nA/pm

-

a

p 0.0006

0.0008

l.E-08 Lg = 80nm 0.0004

I.E-09 Toxe =14.5A 0.0002

l.E-IO 0

0 0.2 0.4.0.6 0.8 I 1.2 1.4 0 0.2 0.4 0.6 0.8 I 1.2 1.4

Vd (V)

' vg (VI

Fig. 1 1 Id-Vg characteristics o f the 80 nm Lg NMOS Fig. 12 Id-Vds characteristics of the 80 nm Lg NMOS

transistors with high-Wmetal-gate gate stack at Vcc=I.3V. transistors with high-Wmeta-gate gate stack.

4-89114-037-2/03 126 IWGIZOO3, Tokyo

You might also like

- Vdoc - Pub Finfet Devices For Vlsi Circuits and SystemsDocument339 pagesVdoc - Pub Finfet Devices For Vlsi Circuits and Systemswork067No ratings yet

- Equivalentes SMD X ConvencionalDocument126 pagesEquivalentes SMD X Convencionaledaoeletronica100% (1)

- Effects of High-K Dielectrics With Metal Gate For Electrical Characteristics of Soi Tri-Gate Finfet TransistorDocument4 pagesEffects of High-K Dielectrics With Metal Gate For Electrical Characteristics of Soi Tri-Gate Finfet TransistordebmallyNo ratings yet

- High-/Metal-Gate Stack and Its MOSFET CharacteristicsDocument3 pagesHigh-/Metal-Gate Stack and Its MOSFET Characteristicstameem_786No ratings yet

- 90 NM K SramDocument4 pages90 NM K SramVLSISD36 Edwin DominicNo ratings yet

- Lecture05 de CmosDocument5 pagesLecture05 de CmosHector Baez MedinaNo ratings yet

- Future MOSFET Devices Using High-K (TiO2) DielectricDocument6 pagesFuture MOSFET Devices Using High-K (TiO2) DielectricIJRASETPublicationsNo ratings yet

- Robert Chau ICSICT Paper 101904Document5 pagesRobert Chau ICSICT Paper 101904yassirkelNo ratings yet

- MR 46 Gate TunnelingDocument18 pagesMR 46 Gate TunnelingdgfnjmfgNo ratings yet

- A High Performance 180 NM Generation Logic Technology: B. ArcotDocument4 pagesA High Performance 180 NM Generation Logic Technology: B. ArcotkeerthiNo ratings yet

- The Charge Plasma P-N DiodeDocument4 pagesThe Charge Plasma P-N DiodePriscilla ScarletNo ratings yet

- Junctionless CMOS Transistors With Independent Double GatesDocument3 pagesJunctionless CMOS Transistors With Independent Double GatesBiswajit BeheraNo ratings yet

- Dynamic Threshold-Voltage MOSFET (DTMOS) For Ultra-Low Voltage VLSIDocument9 pagesDynamic Threshold-Voltage MOSFET (DTMOS) For Ultra-Low Voltage VLSIBüşra AkyıldızNo ratings yet

- Chapter 4 Metal Oxide Semiconductor FET (MOSFET)Document47 pagesChapter 4 Metal Oxide Semiconductor FET (MOSFET)redhataNo ratings yet

- 2 8 1623818035 1ijsstdec20211Document10 pages2 8 1623818035 1ijsstdec20211TJPRC PublicationsNo ratings yet

- Modeling The I-V Characteristics of Fully-Depleted SO1 Mosfets Including Self-HeatingDocument2 pagesModeling The I-V Characteristics of Fully-Depleted SO1 Mosfets Including Self-HeatingShivam Kumar GuptaNo ratings yet

- A 130 NM Generation Logic Technology Featuring 70nm Transistors, Dual VT Transistors and 6 Layers of InterconnectsDocument4 pagesA 130 NM Generation Logic Technology Featuring 70nm Transistors, Dual VT Transistors and 6 Layers of InterconnectskeerthiNo ratings yet

- Design and Analysis of Double Gate MOSFET Devices Using High-K DielectricDocument8 pagesDesign and Analysis of Double Gate MOSFET Devices Using High-K Dielectricabhimanyu_bhate6264No ratings yet

- 5 NM) Gate-All-Around CMOS Devices: High-Performance Fully Depleted Silicon Nanowire (DiameterDocument4 pages5 NM) Gate-All-Around CMOS Devices: High-Performance Fully Depleted Silicon Nanowire (DiameterRàhuł MathiasNo ratings yet

- Fabrication of Vacuum Tube Arrays With A Sub-Micron Dimension Using Anodic Aluminum Oxide Nano-TemplatesDocument6 pagesFabrication of Vacuum Tube Arrays With A Sub-Micron Dimension Using Anodic Aluminum Oxide Nano-TemplatesyahyaNo ratings yet

- Mosfet: Metal Oxide Semiconductor Field Effect TransistorsDocument47 pagesMosfet: Metal Oxide Semiconductor Field Effect Transistorschandanayadav8490No ratings yet

- High Dielectric Constant OxidesDocument27 pagesHigh Dielectric Constant OxidesChithraParameswaranNo ratings yet

- Overview of Ald Applications For Advanced Cmos PDFDocument4 pagesOverview of Ald Applications For Advanced Cmos PDFtbpjmxobaubjtwcqdeNo ratings yet

- Top-Gated MOS2 Capacitors and Transistors With High-K Dielectrics For Interface StudyDocument4 pagesTop-Gated MOS2 Capacitors and Transistors With High-K Dielectrics For Interface Studysritama royNo ratings yet

- 1987 Samsung SFET Data BookDocument446 pages1987 Samsung SFET Data BookAsad AhmedNo ratings yet

- Highly Manufacturable Advanced Gate StacDocument11 pagesHighly Manufacturable Advanced Gate StacDr-Narendar VadthiyaNo ratings yet

- Microelectronic CircuitDocument696 pagesMicroelectronic CircuitImtiaz AhmedNo ratings yet

- Molchanov A 2014Document7 pagesMolchanov A 2014mayuri sritharanNo ratings yet

- Work Function Investigation in Advanced Metal Gate Hfo2 Sio2 System PDFDocument4 pagesWork Function Investigation in Advanced Metal Gate Hfo2 Sio2 System PDFlakhlefNo ratings yet

- TFET Tunnel FET'sDocument2 pagesTFET Tunnel FET'sMohit KumarNo ratings yet

- Nano GabyDocument6 pagesNano GabyMihalache GabrielaNo ratings yet

- Sic Mos Trench Self Align Micromachines-14-02212Document12 pagesSic Mos Trench Self Align Micromachines-14-02212terry chenNo ratings yet

- Inkjet-Printed, Vertically-Integrated, High-Performance Inductors and Transformers On Flexible LCP Substrate - CookDocument4 pagesInkjet-Printed, Vertically-Integrated, High-Performance Inductors and Transformers On Flexible LCP Substrate - CookMarcel BlechNo ratings yet

- On PD-SOIDocument27 pagesOn PD-SOIpramodagarwal_nitrklNo ratings yet

- MosfetDocument20 pagesMosfetMohammad Rameez100% (2)

- 1 s2.0 S1434841117318769 MainDocument8 pages1 s2.0 S1434841117318769 Mainzinouu113113No ratings yet

- Recent Advances in NM-OSCILLATOR Design With CMOS Technology: An OverviewDocument6 pagesRecent Advances in NM-OSCILLATOR Design With CMOS Technology: An OverviewInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- VLSI Unit 2 Technology - SDocument52 pagesVLSI Unit 2 Technology - SIndrajeet GautamNo ratings yet

- Finfet With Isolated N+ and P+ Gate Regions Strapped With Metal and PolysiliconDocument2 pagesFinfet With Isolated N+ and P+ Gate Regions Strapped With Metal and PolysiliconNishana KumarNo ratings yet

- IL2225 L10 ManufacturingDocument29 pagesIL2225 L10 ManufacturingJordi AltayóNo ratings yet

- Design and Simulation of Double Gate Fets Using Atlas: National Institute of Technology RourkelaDocument33 pagesDesign and Simulation of Double Gate Fets Using Atlas: National Institute of Technology RourkelaPraveen KumarNo ratings yet

- 2007-APL-Satoshi Ogawa-Trap Elimination and Injection Switching at Organic Field Effect Transistor byDocument4 pages2007-APL-Satoshi Ogawa-Trap Elimination and Injection Switching at Organic Field Effect Transistor byRajesh AgarwalNo ratings yet

- Nanowire FET JurnalDocument5 pagesNanowire FET JurnalMuhammad Rizki RamadhanNo ratings yet

- Voinigescu Book ChapterDocument30 pagesVoinigescu Book Chapterwantcheck1No ratings yet

- 2023 弹道InSe晶体管 NatureDocument22 pages2023 弹道InSe晶体管 NatureXingxia SunNo ratings yet

- All-Optical NOT Gate Based On Nanoring Silver-Air Plasmonic WaveguideDocument4 pagesAll-Optical NOT Gate Based On Nanoring Silver-Air Plasmonic WaveguideSaif HassanNo ratings yet

- Characterization of Interface Traps in The Subthreshold Region of Implanted 4H and 6H-Sic MosfetsDocument4 pagesCharacterization of Interface Traps in The Subthreshold Region of Implanted 4H and 6H-Sic Mosfetsedwin7029No ratings yet

- Advancement and Challenges in MOSFET ScalingDocument17 pagesAdvancement and Challenges in MOSFET ScalingRajatNo ratings yet

- Mosfet de NanohiloDocument9 pagesMosfet de NanohiloRodrigo LoboNo ratings yet

- Impact of Gate Direct Tunneling Current On Circuit Performance: A Simulation StudyDocument7 pagesImpact of Gate Direct Tunneling Current On Circuit Performance: A Simulation StudyRashmi RavindranathNo ratings yet

- 60nm P-Well MOSFETDocument4 pages60nm P-Well MOSFETKathleen Zipora RahuellahNo ratings yet

- An Evolutionary Transition of Conventional N MOS VLSI To CMOS Considering Scaling, Low Power and Higher MobilityDocument11 pagesAn Evolutionary Transition of Conventional N MOS VLSI To CMOS Considering Scaling, Low Power and Higher MobilityAJER JOURNALNo ratings yet

- Heteroepitaxial Diamond Field-Effect Transistor For High Voltage ApplicationsDocument4 pagesHeteroepitaxial Diamond Field-Effect Transistor For High Voltage ApplicationsilyasoftNo ratings yet

- High-Temperature Performance of Silicon Junctionless MOSFETs-ZWI PDFDocument7 pagesHigh-Temperature Performance of Silicon Junctionless MOSFETs-ZWI PDFdwdwad awwdawdwNo ratings yet

- Review and PerspectiveDocument11 pagesReview and PerspectiveSandeep GaanNo ratings yet

- M. Khaouani, A. Guen M. Khaouani, A. Guen-Bouazza, B. Bouazza, Z. KourdiDocument4 pagesM. Khaouani, A. Guen M. Khaouani, A. Guen-Bouazza, B. Bouazza, Z. KourdiRiya SahaNo ratings yet

- Resonant Tunnelling High Electron Mobility TransistorDocument20 pagesResonant Tunnelling High Electron Mobility TransistorMamta JatoliaNo ratings yet

- Superlattices and Microstructures: SciencedirectDocument6 pagesSuperlattices and Microstructures: SciencedirectVincent RonaldoNo ratings yet

- 2000 Simwonis SldStateIonics NickelCoarseningInAnnealedNi8YSZAnodeSubstratesforSOFCDocument11 pages2000 Simwonis SldStateIonics NickelCoarseningInAnnealedNi8YSZAnodeSubstratesforSOFCAndres CamposNo ratings yet

- 2016 - Effect of A New Methacrylic Monomer On Diode Parameters of Agp-Si Schottky ContactDocument7 pages2016 - Effect of A New Methacrylic Monomer On Diode Parameters of Agp-Si Schottky ContactmehmetNo ratings yet

- Copper Electrodeposition for Nanofabrication of Electronics DevicesFrom EverandCopper Electrodeposition for Nanofabrication of Electronics DevicesNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Delay and Power PDFDocument4 pagesDelay and Power PDFAnala MNo ratings yet

- 3, SaibalDocument19 pages3, SaibalAnala MNo ratings yet

- 5, NarendraDocument310 pages5, NarendraAnala MNo ratings yet

- On Leakage CurrentsDocument94 pagesOn Leakage CurrentsAnala MNo ratings yet

- Analysis of Various Adder Circuits For Low Power Consumption and Minimum Propagation DelayDocument9 pagesAnalysis of Various Adder Circuits For Low Power Consumption and Minimum Propagation DelayAnala MNo ratings yet

- Summary of Literature Review On FinFETsDocument1 pageSummary of Literature Review On FinFETsAnala MNo ratings yet

- DDRS, para Yield 2004Document6 pagesDDRS, para Yield 2004Anala MNo ratings yet

- FET Small Signal Analysis: ENGI 242 ELEC 222Document18 pagesFET Small Signal Analysis: ENGI 242 ELEC 222Anala MNo ratings yet

- AP7201Document8 pagesAP7201Anala MNo ratings yet

- RCA Cleaning ProcessDocument3 pagesRCA Cleaning ProcessAnala MNo ratings yet

- Capacitance and Power Modeling at Logic-Level: C V F PowerDocument7 pagesCapacitance and Power Modeling at Logic-Level: C V F PowerAnala MNo ratings yet

- Workfunction, Hfin, L, Wfin, Tox, Temperature 20nm IonDocument5 pagesWorkfunction, Hfin, L, Wfin, Tox, Temperature 20nm IonAnala MNo ratings yet

- K.S. School of Engineering & Management: First Internals Test Question PaperDocument1 pageK.S. School of Engineering & Management: First Internals Test Question PaperAnala MNo ratings yet

- MNE Question Bank 2Document1 pageMNE Question Bank 2Anala MNo ratings yet

- MramDocument15 pagesMramVeerendra VermaNo ratings yet

- Diff BTWN MOSFET and BJTDocument2 pagesDiff BTWN MOSFET and BJTMadan R HonnalagereNo ratings yet

- Ecd LR - 1Document21 pagesEcd LR - 1Faaran Ahmed Zaheer AhmedNo ratings yet

- Valliammai Engineering College: Department ofDocument10 pagesValliammai Engineering College: Department ofmaheshwarivikas1982No ratings yet

- Data Sheet: N-Channel Enhancement Mode MOS TransistorDocument8 pagesData Sheet: N-Channel Enhancement Mode MOS TransistorArgenis VeraNo ratings yet

- Nguyễn Đức Linh - chapter 5Document3 pagesNguyễn Đức Linh - chapter 5Nguyen Duc Linh (K17 HCM)No ratings yet

- A Simple Subthreshold Swing Model For SHDocument7 pagesA Simple Subthreshold Swing Model For SHSwapna BharaliNo ratings yet

- Common Base Transistor - UpdatedDocument23 pagesCommon Base Transistor - UpdatedAliza TariqNo ratings yet

- Verilog-A Implementation of SOI MOSFET-Based Amplifier and RingDocument9 pagesVerilog-A Implementation of SOI MOSFET-Based Amplifier and RingAdib ShadmanNo ratings yet

- AC 128, Tube AC128 Válvula AC 128 ID33948, TransistorDocument1 pageAC 128, Tube AC128 Válvula AC 128 ID33948, TransistorAle 777No ratings yet

- ECE467: Introduction To VLSI DesignDocument51 pagesECE467: Introduction To VLSI Designsnagaraj.cool7813No ratings yet

- EC8095-VLSI Design - 01 - by WWW - LearnEngineering.inDocument134 pagesEC8095-VLSI Design - 01 - by WWW - LearnEngineering.inDelphin ShibinNo ratings yet

- Session-03 - ECN-341 - Yawalkar Ajinkya GanpatiDocument3 pagesSession-03 - ECN-341 - Yawalkar Ajinkya GanpatiAjinkya YawalkarNo ratings yet

- Cmos Inverter CharacteristicsDocument8 pagesCmos Inverter CharacteristicsShambhavi SonuNo ratings yet

- 3 N 187Document1 page3 N 187Axel Ricardo RojasNo ratings yet

- Pdfslide - Tips Persamaan TransistorDocument6 pagesPdfslide - Tips Persamaan TransistorLord BoyNo ratings yet

- Ram and RomDocument3 pagesRam and RomMEENA J RCBSNo ratings yet

- Chapter 4 Dec 50143Document47 pagesChapter 4 Dec 50143Kohilan VenugopalNo ratings yet

- Module 2 FET TransistorDocument50 pagesModule 2 FET TransistorVaishnavi BharatiNo ratings yet

- Assignment 1Document2 pagesAssignment 1mid_cycloneNo ratings yet

- Stick DiagDocument6 pagesStick DiagSrinu BoddulaNo ratings yet

- Design and Performance Analysis of 2Document24 pagesDesign and Performance Analysis of 2Dilip Kumar100% (1)

- M.tech - Thesis SramsDocument69 pagesM.tech - Thesis SramsRatnakarVarunNo ratings yet

- Emitter-Coupled Logic Element Simulation PDFDocument4 pagesEmitter-Coupled Logic Element Simulation PDFAli TayefehNo ratings yet

- Persamaan Mosfet Laptop: AO4407A (Lazada 15k)Document2 pagesPersamaan Mosfet Laptop: AO4407A (Lazada 15k)Hotel WijayaNo ratings yet

- CMOS InverterDocument16 pagesCMOS Invertersreekanthreddy peramNo ratings yet

- IRFD9120: 1.0A, 100V, 0.6 Ohm, P-Channel Power Mosfet FeaturesDocument6 pagesIRFD9120: 1.0A, 100V, 0.6 Ohm, P-Channel Power Mosfet FeaturesJaime Enrique ValbuenaNo ratings yet

- Boylestad Electronics Multiple Choice Q&a ChapterDocument7 pagesBoylestad Electronics Multiple Choice Q&a ChapterDenaiya Watton LeehNo ratings yet