Professional Documents

Culture Documents

Sabitha Susan Joseph MTech Elec Google

Sabitha Susan Joseph MTech Elec Google

Uploaded by

Garg Acharya DuttaCopyright:

Available Formats

You might also like

- PAG 05.3 - Determining Frequency and Amplitude With An OscilloscopeDocument2 pagesPAG 05.3 - Determining Frequency and Amplitude With An OscilloscopejmsonlNo ratings yet

- Ejercicios RMS PDFDocument2 pagesEjercicios RMS PDFNicolás CanaríaNo ratings yet

- Comparison of Switching Strategies For An Ultrasonic Cleaner PDFDocument5 pagesComparison of Switching Strategies For An Ultrasonic Cleaner PDFBogdan HaiducNo ratings yet

- CH Trivikram - ResumeDocument4 pagesCH Trivikram - ResumeDarbha ShaliniNo ratings yet

- VLSI Lab ManualDocument41 pagesVLSI Lab ManualDyavegowda PNo ratings yet

- Awneeppandey - Memory Design Engineer - IIT BHUDocument2 pagesAwneeppandey - Memory Design Engineer - IIT BHUawneepNo ratings yet

- Myresume PDFDocument3 pagesMyresume PDFRocker byNo ratings yet

- DVD ManualDocument125 pagesDVD Manualmadhusudhantm.ec21No ratings yet

- Scholastic Achievements: Guide: Prof. Madhav P. Desai, Electrical Engineering Dept., IIT BombayDocument2 pagesScholastic Achievements: Guide: Prof. Madhav P. Desai, Electrical Engineering Dept., IIT BombayArghya Kamal DeyNo ratings yet

- VLSI LabDocument4 pagesVLSI Labnithyamohan82No ratings yet

- Ashwini ResumeDocument5 pagesAshwini ResumekalyanNo ratings yet

- Ashika Nayak: EducationDocument2 pagesAshika Nayak: EducationAnil DharavathNo ratings yet

- C. Laxmikanth ReddyDocument26 pagesC. Laxmikanth ReddymritNo ratings yet

- Cmme302 00Document15 pagesCmme302 00Little VoiceNo ratings yet

- Anum Ahmed Pirkani UkDocument5 pagesAnum Ahmed Pirkani UkAnum AhmedNo ratings yet

- Sradha M (RESUME) - QualcommDocument1 pageSradha M (RESUME) - Qualcommskrxbbr7nhNo ratings yet

- ECEN 5853 Embedding Sensors and MotorsDocument2 pagesECEN 5853 Embedding Sensors and MotorsMehul PatelNo ratings yet

- DVD Manual RvceDocument125 pagesDVD Manual RvcesonaNo ratings yet

- PG CO Second Semester PDFDocument9 pagesPG CO Second Semester PDFMaxuell SmashNo ratings yet

- An Internship Seminar On: "VLSI Design"Document21 pagesAn Internship Seminar On: "VLSI Design"sooraj naikNo ratings yet

- Custom Ic Design: Cmos Standard Cell Circuit Design, Simulation and LayoutDocument19 pagesCustom Ic Design: Cmos Standard Cell Circuit Design, Simulation and Layoutkajal awasthiNo ratings yet

- CV VishrutDave R5Document4 pagesCV VishrutDave R5avishek001No ratings yet

- Akash Kumar IITMandiDocument1 pageAkash Kumar IITMandib21215No ratings yet

- Abhishek Deo (16017108927)Document4 pagesAbhishek Deo (16017108927)abhishek deoNo ratings yet

- Balaji Emulation InternDocument3 pagesBalaji Emulation InternfreebhushanNo ratings yet

- Core 3Document2 pagesCore 3RidhiNo ratings yet

- Research Notes On VlsiDocument70 pagesResearch Notes On VlsiMohit GirdharNo ratings yet

- Mounika.M: Education Program Institution %/CGPA YearDocument3 pagesMounika.M: Education Program Institution %/CGPA Yearmounika morampudiNo ratings yet

- VLSI LabDocument103 pagesVLSI Labutso boseNo ratings yet

- Post Graduation Graduation Graduation Specialization: Electronics & Communication IIT Bombay NIT Silchar IIT Bombay NIT Silchar 2024 2018 8.56 5.88Document1 pagePost Graduation Graduation Graduation Specialization: Electronics & Communication IIT Bombay NIT Silchar IIT Bombay NIT Silchar 2024 2018 8.56 5.88Dheeraj SinghNo ratings yet

- 637862647808605476ece 18ecl77 E1s1 PPTDocument37 pages637862647808605476ece 18ecl77 E1s1 PPTSiddu UmaraniNo ratings yet

- TCADDocument33 pagesTCADvpsampathNo ratings yet

- Muhammad Hamza Aslam: ObjectiveDocument2 pagesMuhammad Hamza Aslam: Objectivehamza aslamNo ratings yet

- AcknowledgementDocument8 pagesAcknowledgementHarishNo ratings yet

- ResumeDocument2 pagesResumeArnab DuttaNo ratings yet

- Resume Srinivasa GadigatlaDocument3 pagesResume Srinivasa GadigatlasgadigatNo ratings yet

- (New) EC304 Comm Lab II Course Eval PlanDocument3 pages(New) EC304 Comm Lab II Course Eval PlanShivam PrajapatiNo ratings yet

- DE CourseResume ENGDocument2 pagesDE CourseResume ENG潘卫平No ratings yet

- Rajufinal Project 22.01.2022 4.21PMDocument49 pagesRajufinal Project 22.01.2022 4.21PMR.R.RaoNo ratings yet

- CV AdityaDocument3 pagesCV Adityaratna sinhaNo ratings yet

- Monika NIT Kurukshetra June 2021 PDFDocument3 pagesMonika NIT Kurukshetra June 2021 PDFS KkNo ratings yet

- Shreya Arodia: Rochester Hills, MI 48309Document2 pagesShreya Arodia: Rochester Hills, MI 48309SandhyaNo ratings yet

- Rucha Joshi MTech Elec AppleDocument2 pagesRucha Joshi MTech Elec ApplemekarandeepsinghNo ratings yet

- Pedavegi Sravani: Academic Details Examination Institute Year CGPA/%Document2 pagesPedavegi Sravani: Academic Details Examination Institute Year CGPA/%Himanshu PariharNo ratings yet

- Atharva Tambat Resume PDFDocument2 pagesAtharva Tambat Resume PDFtejasnarwade2k5No ratings yet

- 1582566171823resume RakeshDocument2 pages1582566171823resume RakeshRakesh TigadiNo ratings yet

- Sampuuuu Project PG EditedDocument81 pagesSampuuuu Project PG EditedVinith RaoNo ratings yet

- (Tutorials in Electronic Materials, Circuits and Devices) Milin Zhang, Zhihua Wang, Jan Van Der Spiegel, Franco Maloberti - Advanced Tutorial On Analog Circuit Design-River Publishers (2023)Document449 pages(Tutorials in Electronic Materials, Circuits and Devices) Milin Zhang, Zhihua Wang, Jan Van Der Spiegel, Franco Maloberti - Advanced Tutorial On Analog Circuit Design-River Publishers (2023)PANKAJ KUMARNo ratings yet

- Anupriya Mishra-ResumeDocument2 pagesAnupriya Mishra-ResumeDivya srivastavaNo ratings yet

- Mixed Signal DesignDocument5 pagesMixed Signal DesignNallaManoharReddyNo ratings yet

- Sri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsDocument132 pagesSri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsRAAJ KISHOR R HNo ratings yet

- First Course Handout EE610ADocument1 pageFirst Course Handout EE610AAayush GodaraNo ratings yet

- Simulation of Communication Systems: Professor Z. GhassemlooyDocument49 pagesSimulation of Communication Systems: Professor Z. Ghassemlooys.b.v.seshagiri1407No ratings yet

- Vijay Kumar Physical Design EngineerDocument3 pagesVijay Kumar Physical Design EngineerKarthik VarmaNo ratings yet

- Harish ResumeDocument3 pagesHarish ResumeGanesh NAGARAJANNo ratings yet

- EEE4134 CO Spring2021Document4 pagesEEE4134 CO Spring2021Abdullah Al SakibNo ratings yet

- ResumefinalDocument1 pageResumefinalapi-606482363No ratings yet

- Pipelined ADC ThesisDocument54 pagesPipelined ADC ThesisHarshita MehtonNo ratings yet

- Shubham.p ResumeDocument4 pagesShubham.p ResumeShubham PatilNo ratings yet

- JournalNX - Bridge Disaster MonitoringDocument3 pagesJournalNX - Bridge Disaster MonitoringJournalNX - a Multidisciplinary Peer Reviewed JournalNo ratings yet

- CansatDocument17 pagesCansatprachisabadeNo ratings yet

- Transportation and Power Grid in Smart Cities: Communication Networks and ServicesFrom EverandTransportation and Power Grid in Smart Cities: Communication Networks and ServicesNo ratings yet

- Online AlgorithmsDocument4 pagesOnline AlgorithmsGarg Acharya DuttaNo ratings yet

- Markov 1 - Crop RotationDocument10 pagesMarkov 1 - Crop RotationGarg Acharya DuttaNo ratings yet

- Markov 2 - Crop RotationDocument16 pagesMarkov 2 - Crop RotationGarg Acharya DuttaNo ratings yet

- Temp 3Document8 pagesTemp 3Garg Acharya DuttaNo ratings yet

- Pigeonhole PrincipleDocument30 pagesPigeonhole PrincipleGarg Acharya DuttaNo ratings yet

- Temp 2Document8 pagesTemp 2Garg Acharya DuttaNo ratings yet

- ModifiedDocument8 pagesModifiedGarg Acharya DuttaNo ratings yet

- TempDocument8 pagesTempGarg Acharya DuttaNo ratings yet

- RTN 980L V100R009C10 Product Description (Split LH) 01Document179 pagesRTN 980L V100R009C10 Product Description (Split LH) 01Lima Anjos AnjosNo ratings yet

- 2nd Review PPT (521) FinalDocument32 pages2nd Review PPT (521) FinalVenkatGolla33% (3)

- Lec. 2Document22 pagesLec. 2محمدNo ratings yet

- Ec2305 Transmission Lines and Wave Guides Question BankDocument16 pagesEc2305 Transmission Lines and Wave Guides Question BanksharonfranklinNo ratings yet

- OfdmDocument16 pagesOfdmMansoorNo ratings yet

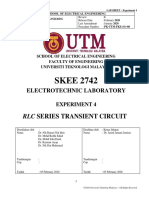

- Experiment 4 - RLC SERIES TRANSIENT CIRCUITDocument3 pagesExperiment 4 - RLC SERIES TRANSIENT CIRCUITHafiziAhmadNo ratings yet

- Flexi RF Module 3TX 2100 : Technical SpecificationsDocument9 pagesFlexi RF Module 3TX 2100 : Technical SpecificationsReza BordbarNo ratings yet

- Transmission Lines (Blake C14) : True/FalseDocument6 pagesTransmission Lines (Blake C14) : True/FalseLovely Eulin FulgarNo ratings yet

- Cell Search Techniques in LTE PaperDocument10 pagesCell Search Techniques in LTE PaperManoj WanjariNo ratings yet

- HFE0111 FirasDocument6 pagesHFE0111 Firaschiase83No ratings yet

- AAU5613 Hardware Description (04) (PDF) - enDocument20 pagesAAU5613 Hardware Description (04) (PDF) - enSurendra MaharjanNo ratings yet

- Adjustable Cable Equalizer Combines Wideband Differential Receiver With Analog SwitchesDocument4 pagesAdjustable Cable Equalizer Combines Wideband Differential Receiver With Analog SwitchesAkhileshKesavanunnithanNo ratings yet

- Coupling-Matrix Design of Dual and Triple Passband FiltersDocument7 pagesCoupling-Matrix Design of Dual and Triple Passband FiltersrallabhandiSKNo ratings yet

- ALARM Description 3GDocument6 pagesALARM Description 3GJaypee Sharma100% (1)

- Altran Private NetworksDocument21 pagesAltran Private NetworkssteadyspikeNo ratings yet

- Chapter 2: Classical Encryption Techniques: Information System SecurityDocument15 pagesChapter 2: Classical Encryption Techniques: Information System SecurityKavin MartinNo ratings yet

- Cisco 1000 Series Integrated Services Routers Ordering Guide 1kseries-Integrated-Services-Routers-GuideDocument23 pagesCisco 1000 Series Integrated Services Routers Ordering Guide 1kseries-Integrated-Services-Routers-Guidemarc1249No ratings yet

- DCS MID - II Set ADocument2 pagesDCS MID - II Set AN.RAMAKUMARNo ratings yet

- Mediterranean Microwave Symposium 2022 - Call For PapersDocument2 pagesMediterranean Microwave Symposium 2022 - Call For PapersMMS2022No ratings yet

- Steganography: Khan, Mohammed MinhajuddinDocument13 pagesSteganography: Khan, Mohammed MinhajuddinShivaEshwariNo ratings yet

- Non Resonant RadiatorsDocument27 pagesNon Resonant RadiatorsNuzhath FathimaNo ratings yet

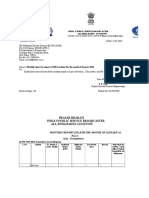

- Monthly Report in Respect of AIR Lucknow For January 2016Document84 pagesMonthly Report in Respect of AIR Lucknow For January 2016Joshua JacksonNo ratings yet

- BGP Vibroseis Acquisition TechniquesDocument4 pagesBGP Vibroseis Acquisition TechniquesMustapha ChettouhNo ratings yet

- Ele06 - Takehome PrelimDocument3 pagesEle06 - Takehome PrelimEllieNo ratings yet

- DatasheetDocument1 pageDatasheetnomi_nomiNo ratings yet

Sabitha Susan Joseph MTech Elec Google

Sabitha Susan Joseph MTech Elec Google

Uploaded by

Garg Acharya DuttaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sabitha Susan Joseph MTech Elec Google

Sabitha Susan Joseph MTech Elec Google

Uploaded by

Garg Acharya DuttaCopyright:

Available Formats

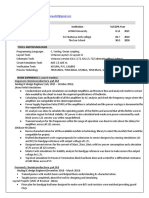

Sabitha Susan Joseph 183079028

Electrical Engineering M.Tech.

Indian Institute of Technology, Bombay Gender: Female

Specialization: Electronic Systems DOB: 11-10-1993

Examination University Institute Year CPI / %

Post Graduation IIT Bombay IIT Bombay 2021 9.13

Graduation University of Kerala College of Engineering Trivandrum 2015 8.42

Graduation Specialization: Applied Electronics and Instrumentation

Intermediate CBSE Holy Angels School, Vanchiyoor 2011 92.00%

Matriculation CBSE Holy Angels School, Vanchiyoor 2009 92.60%

KEY SKILLED AREAS

Digital VLSI Design, System Design, Mixed Signal VLSI Design, Analog VLSI Design

RELEVANT COURSES

• VLSI Design • Systems Design • Foundation of VLSI CAD

• DSP-System Design & Implementation • Mixed-Signal VLSI Design • CMOS Analog VLSI Design

PROFESSIONAL EXPERIENCE

• TISMO Technology Solutions | Designation: Electronics Engineer Jun ’15 - May’ 17

o Developed high-level electronic designs with detailed schematic and layout design in Altium Designer

o Procured the components and coordinated fabrication as well as assembly of the developed PCB designs

o Maintained associated technical documents and project documentation in accordance with the project plan

o Tested the developed designs, prepared the test reports and followed up on the defect handling process

MAJOR PROJECT AND SEMINAR

• M.Tech Thesis Jun ’20 - Present

Title: Enhancement of SAR ADC resolution using I-Σ∆ DAC for CDAC calibration

Guide: Prof. Maryam Shojaei Baghini, Dept. of EE, IIT Bombay

o Literature review of various hybrid architectures of SAR ADC for resolution enhancement

o System-level design and simulation of the 12-bit SAR ADC using ideal blocks in Cadence

o Verilog implementation of SAR logic for monotonic switching scheme and Merged Capacitor switching scheme

o Ongoing and future work includes implementation of the Calibration technique for the calibration of 12-bit

SAR ADC Capacitive DAC (CDAC) using an Incremental Sigma-Delta DAC in UMC 180-nm Technology

• M.Tech Seminar Nov ’19

Title: Overview of hybrid SAR ADC architectures for enhanced Power and Area Efficiency

Guide: Prof. Maryam Shojaei Baghini, Dept. of EE, IIT Bombay

o Review of 10-bit SAR ADC with hybrid Cap-MOS DAC which is more efficient than binary-weighted CDAC

o Review of 13-bit SAR-Incremental Sigma-Delta Modulator ADC with an opamp-less time-domain integrator

KEY COURSE PROJECTS AND ASSIGNMENTS

• Implementation of an 8-bit Dadda Multiply and Accumulate circuit | VLSI Design Nov ’18

o Implemented half and full adders as behaviourally described building blocks for unsigned 8-bit MAC operation

o Implemented the design in Verilog and simulated the design with random test vectors using Icarus Verilog

• Implementation of a 32-bit Brent Kung adder | VLSI Design Oct ’18

o Designed adder circuit using domino logic to generate G and P signals for unsigned addition of 32-bit numbers

o Implemented the design in VHDL and simulated in GHDL with proper test vectors to find the worst-case delay

• Design of SAT Solver | Foundation of VLSI CAD Nov ’19

o Implemented a Conjunctive Normal Form Satisfiability (CNF-SAT) problem solver algorithm in MATLAB

• Design of PLL | Systems Design Mar ’19

o Designed and characterised Bang-Bang phase detector and Hogge phase detector in Cadence Virtuoso

o Implemented Hogge phase detector based PLL and got center alignment of clock and data in the eye diagram

o Analyzed the transient response for step and ramp inputs and frequency response of the PLL in MATLAB

• Design and implementation of Adaptive Equalizer | Systems Design Apr ’19

o Implemented a 4-tap FIR filter with the tap coefficients being set by LMS algorithm in VerilogA

o Verified filter operation by using 20 Gbps PRBS data received from a matched 10m lossy transmission line

o Implemented Continuous Time Linear Equalizer, Decision Feedback Equalizer and Feed Forward Equalizer

o Verified the equalizer operations by using PRBS data received from a transmission line in presence of noise

• Design of Guitar Tuner | DSP-System Design & Implementation Nov ’19

o Implemented a Guitar Tuner based on Fast Fourier Transform algorithm on TMS320C5535 DSP platform

o Implemented spectral peak location algorithms for the frequency estimation of tones based on FFT samples

o Achieved a frequency resolution of ±1 Hz with just a sampling frequency of 8000 Hz and 2048 point FFT

• Design & layout of Operational Transconductance Amplifier | CMOS Analog VLSI Design Oct ’18

o Designed fully differential input, single-ended output 2 stage Folded Cascode OTA in Cadence Virtuoso

o Implemented Rz tracking for pole-zero cancellation and layout of the design in 180-nm CMOS Technology

o Followed common centroid technique for the layout and verified the post-layout simulations using Calibre

• Design & characterisation of a 4-bit 1 GS/s Folding Flash ADC | Mixed-Signal VLSI Design Feb ’19

o Designed and implemented differential track and hold circuit followed by variable gain amplifier, folding network

and unity gain buffer in 45-nm CMOS Technology in Cadence Virtuoso

o Designed and implemented 3-bit flash ADC using StrongARM Latch based LSB comparator with provisions

for reference subtraction and kickback reduction that settles within 1 LSB (4-bits) of DC rail in 200 ps

• Simulation of 16-PAM Transceiver | Mixed-Signal VLSI Design Mar ’19

o Designed 4-bit differential Current Steering DAC & obtained ENOB of 3.995 bits in 45-nm CMOS Technology

o Analysed the effect of frequency, length & characteristics of transmission line on SNDR and SFDR of transceiver

o Integrated and characterized complete 16-PAM transceiver with ADC and DAC using microstrip line as channel

• Voltage Controlled Oscillator using Switched Capacitors | Electronic Systems Design Nov ’18

o Implemented a stray insensitive Switched Capacitor based VCO that works using single DC power supply

o Generated non-overlapping clocks by passing 555 Timer output through a circuit with NOR & NOT Gates

ACHIEVEMENTS

• Awarded with certificate of Excellence in Research Assistantship for Electronic Circuits Lab, Spring 2019

• Secured 99.37 percentile in Electronics and Communication GATE 2018 among 1,25,870 candidates

• Secured AA grade in Foundation of VLSI CAD course among 71 candidates

• School Topper in Central Board of Secondary Education XIIth Examination, 2011

TECHNICAL SKILLS

• Tools: Cadence Virtuoso, Altium, Ngspice, MATLAB, Code Composer Studio, Eagle, XCircuit, LATEX

• Languages: Verilog, VHDL, VerilogA, C, C++ | Hardware: TMS320C5535 eZdsp board

POSITIONS OF RESPONSIBILITY

• Research Assistant | Wadhwani Electronics Laboratory, IIT Bombay Jul ’18 - Present

o Mentors and evaluates undergraduates enrolled in ’Electronic Devices’ and ’Analog Circuits’ Lab courses

o Assists Course Instructors in setting up tutorial sessions, question papers & in the evaluation of answer sheets

• Student Companion | Institute Student Companion Program, IIT Bombay Jun ’19 - Mar ’20

o Mentored 11 freshmen M.Tech students by providing help and support in academic and non-academic fronts

o Helped the Department Coordinators in creating the Department Handbook for the academic year 2019-2020

• Executive committee member | ISTE Student Chapter, College of Engineering Trivandrum Jul’13 - Jun’14

o Organised events and competitions along with crowd management

o Set up technical exhibitions open to the general public

• Student co-ordinator | Swarm Robotics Workshop conducted, Technophilia Systems Sept’13

o Handled end to end coordination & overseeing of the 2-day workshop held at College of Engineering Trivandrum

EXTRACURRICULAR ACTIVITIES

• Multiple accolades received for art and cultural events like group song, fabric painting, mehandi designing etc.

• Passionate landscape photographer who loves to explore and capture the everyday experiences of the cityscape

• Enjoys the experiences of craftworks, origami, quilling, painting, designing and decorating personal living spaces

Scholastic achievements and extracurricular activities are not verified by the Placement Cell

You might also like

- PAG 05.3 - Determining Frequency and Amplitude With An OscilloscopeDocument2 pagesPAG 05.3 - Determining Frequency and Amplitude With An OscilloscopejmsonlNo ratings yet

- Ejercicios RMS PDFDocument2 pagesEjercicios RMS PDFNicolás CanaríaNo ratings yet

- Comparison of Switching Strategies For An Ultrasonic Cleaner PDFDocument5 pagesComparison of Switching Strategies For An Ultrasonic Cleaner PDFBogdan HaiducNo ratings yet

- CH Trivikram - ResumeDocument4 pagesCH Trivikram - ResumeDarbha ShaliniNo ratings yet

- VLSI Lab ManualDocument41 pagesVLSI Lab ManualDyavegowda PNo ratings yet

- Awneeppandey - Memory Design Engineer - IIT BHUDocument2 pagesAwneeppandey - Memory Design Engineer - IIT BHUawneepNo ratings yet

- Myresume PDFDocument3 pagesMyresume PDFRocker byNo ratings yet

- DVD ManualDocument125 pagesDVD Manualmadhusudhantm.ec21No ratings yet

- Scholastic Achievements: Guide: Prof. Madhav P. Desai, Electrical Engineering Dept., IIT BombayDocument2 pagesScholastic Achievements: Guide: Prof. Madhav P. Desai, Electrical Engineering Dept., IIT BombayArghya Kamal DeyNo ratings yet

- VLSI LabDocument4 pagesVLSI Labnithyamohan82No ratings yet

- Ashwini ResumeDocument5 pagesAshwini ResumekalyanNo ratings yet

- Ashika Nayak: EducationDocument2 pagesAshika Nayak: EducationAnil DharavathNo ratings yet

- C. Laxmikanth ReddyDocument26 pagesC. Laxmikanth ReddymritNo ratings yet

- Cmme302 00Document15 pagesCmme302 00Little VoiceNo ratings yet

- Anum Ahmed Pirkani UkDocument5 pagesAnum Ahmed Pirkani UkAnum AhmedNo ratings yet

- Sradha M (RESUME) - QualcommDocument1 pageSradha M (RESUME) - Qualcommskrxbbr7nhNo ratings yet

- ECEN 5853 Embedding Sensors and MotorsDocument2 pagesECEN 5853 Embedding Sensors and MotorsMehul PatelNo ratings yet

- DVD Manual RvceDocument125 pagesDVD Manual RvcesonaNo ratings yet

- PG CO Second Semester PDFDocument9 pagesPG CO Second Semester PDFMaxuell SmashNo ratings yet

- An Internship Seminar On: "VLSI Design"Document21 pagesAn Internship Seminar On: "VLSI Design"sooraj naikNo ratings yet

- Custom Ic Design: Cmos Standard Cell Circuit Design, Simulation and LayoutDocument19 pagesCustom Ic Design: Cmos Standard Cell Circuit Design, Simulation and Layoutkajal awasthiNo ratings yet

- CV VishrutDave R5Document4 pagesCV VishrutDave R5avishek001No ratings yet

- Akash Kumar IITMandiDocument1 pageAkash Kumar IITMandib21215No ratings yet

- Abhishek Deo (16017108927)Document4 pagesAbhishek Deo (16017108927)abhishek deoNo ratings yet

- Balaji Emulation InternDocument3 pagesBalaji Emulation InternfreebhushanNo ratings yet

- Core 3Document2 pagesCore 3RidhiNo ratings yet

- Research Notes On VlsiDocument70 pagesResearch Notes On VlsiMohit GirdharNo ratings yet

- Mounika.M: Education Program Institution %/CGPA YearDocument3 pagesMounika.M: Education Program Institution %/CGPA Yearmounika morampudiNo ratings yet

- VLSI LabDocument103 pagesVLSI Labutso boseNo ratings yet

- Post Graduation Graduation Graduation Specialization: Electronics & Communication IIT Bombay NIT Silchar IIT Bombay NIT Silchar 2024 2018 8.56 5.88Document1 pagePost Graduation Graduation Graduation Specialization: Electronics & Communication IIT Bombay NIT Silchar IIT Bombay NIT Silchar 2024 2018 8.56 5.88Dheeraj SinghNo ratings yet

- 637862647808605476ece 18ecl77 E1s1 PPTDocument37 pages637862647808605476ece 18ecl77 E1s1 PPTSiddu UmaraniNo ratings yet

- TCADDocument33 pagesTCADvpsampathNo ratings yet

- Muhammad Hamza Aslam: ObjectiveDocument2 pagesMuhammad Hamza Aslam: Objectivehamza aslamNo ratings yet

- AcknowledgementDocument8 pagesAcknowledgementHarishNo ratings yet

- ResumeDocument2 pagesResumeArnab DuttaNo ratings yet

- Resume Srinivasa GadigatlaDocument3 pagesResume Srinivasa GadigatlasgadigatNo ratings yet

- (New) EC304 Comm Lab II Course Eval PlanDocument3 pages(New) EC304 Comm Lab II Course Eval PlanShivam PrajapatiNo ratings yet

- DE CourseResume ENGDocument2 pagesDE CourseResume ENG潘卫平No ratings yet

- Rajufinal Project 22.01.2022 4.21PMDocument49 pagesRajufinal Project 22.01.2022 4.21PMR.R.RaoNo ratings yet

- CV AdityaDocument3 pagesCV Adityaratna sinhaNo ratings yet

- Monika NIT Kurukshetra June 2021 PDFDocument3 pagesMonika NIT Kurukshetra June 2021 PDFS KkNo ratings yet

- Shreya Arodia: Rochester Hills, MI 48309Document2 pagesShreya Arodia: Rochester Hills, MI 48309SandhyaNo ratings yet

- Rucha Joshi MTech Elec AppleDocument2 pagesRucha Joshi MTech Elec ApplemekarandeepsinghNo ratings yet

- Pedavegi Sravani: Academic Details Examination Institute Year CGPA/%Document2 pagesPedavegi Sravani: Academic Details Examination Institute Year CGPA/%Himanshu PariharNo ratings yet

- Atharva Tambat Resume PDFDocument2 pagesAtharva Tambat Resume PDFtejasnarwade2k5No ratings yet

- 1582566171823resume RakeshDocument2 pages1582566171823resume RakeshRakesh TigadiNo ratings yet

- Sampuuuu Project PG EditedDocument81 pagesSampuuuu Project PG EditedVinith RaoNo ratings yet

- (Tutorials in Electronic Materials, Circuits and Devices) Milin Zhang, Zhihua Wang, Jan Van Der Spiegel, Franco Maloberti - Advanced Tutorial On Analog Circuit Design-River Publishers (2023)Document449 pages(Tutorials in Electronic Materials, Circuits and Devices) Milin Zhang, Zhihua Wang, Jan Van Der Spiegel, Franco Maloberti - Advanced Tutorial On Analog Circuit Design-River Publishers (2023)PANKAJ KUMARNo ratings yet

- Anupriya Mishra-ResumeDocument2 pagesAnupriya Mishra-ResumeDivya srivastavaNo ratings yet

- Mixed Signal DesignDocument5 pagesMixed Signal DesignNallaManoharReddyNo ratings yet

- Sri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsDocument132 pagesSri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsRAAJ KISHOR R HNo ratings yet

- First Course Handout EE610ADocument1 pageFirst Course Handout EE610AAayush GodaraNo ratings yet

- Simulation of Communication Systems: Professor Z. GhassemlooyDocument49 pagesSimulation of Communication Systems: Professor Z. Ghassemlooys.b.v.seshagiri1407No ratings yet

- Vijay Kumar Physical Design EngineerDocument3 pagesVijay Kumar Physical Design EngineerKarthik VarmaNo ratings yet

- Harish ResumeDocument3 pagesHarish ResumeGanesh NAGARAJANNo ratings yet

- EEE4134 CO Spring2021Document4 pagesEEE4134 CO Spring2021Abdullah Al SakibNo ratings yet

- ResumefinalDocument1 pageResumefinalapi-606482363No ratings yet

- Pipelined ADC ThesisDocument54 pagesPipelined ADC ThesisHarshita MehtonNo ratings yet

- Shubham.p ResumeDocument4 pagesShubham.p ResumeShubham PatilNo ratings yet

- JournalNX - Bridge Disaster MonitoringDocument3 pagesJournalNX - Bridge Disaster MonitoringJournalNX - a Multidisciplinary Peer Reviewed JournalNo ratings yet

- CansatDocument17 pagesCansatprachisabadeNo ratings yet

- Transportation and Power Grid in Smart Cities: Communication Networks and ServicesFrom EverandTransportation and Power Grid in Smart Cities: Communication Networks and ServicesNo ratings yet

- Online AlgorithmsDocument4 pagesOnline AlgorithmsGarg Acharya DuttaNo ratings yet

- Markov 1 - Crop RotationDocument10 pagesMarkov 1 - Crop RotationGarg Acharya DuttaNo ratings yet

- Markov 2 - Crop RotationDocument16 pagesMarkov 2 - Crop RotationGarg Acharya DuttaNo ratings yet

- Temp 3Document8 pagesTemp 3Garg Acharya DuttaNo ratings yet

- Pigeonhole PrincipleDocument30 pagesPigeonhole PrincipleGarg Acharya DuttaNo ratings yet

- Temp 2Document8 pagesTemp 2Garg Acharya DuttaNo ratings yet

- ModifiedDocument8 pagesModifiedGarg Acharya DuttaNo ratings yet

- TempDocument8 pagesTempGarg Acharya DuttaNo ratings yet

- RTN 980L V100R009C10 Product Description (Split LH) 01Document179 pagesRTN 980L V100R009C10 Product Description (Split LH) 01Lima Anjos AnjosNo ratings yet

- 2nd Review PPT (521) FinalDocument32 pages2nd Review PPT (521) FinalVenkatGolla33% (3)

- Lec. 2Document22 pagesLec. 2محمدNo ratings yet

- Ec2305 Transmission Lines and Wave Guides Question BankDocument16 pagesEc2305 Transmission Lines and Wave Guides Question BanksharonfranklinNo ratings yet

- OfdmDocument16 pagesOfdmMansoorNo ratings yet

- Experiment 4 - RLC SERIES TRANSIENT CIRCUITDocument3 pagesExperiment 4 - RLC SERIES TRANSIENT CIRCUITHafiziAhmadNo ratings yet

- Flexi RF Module 3TX 2100 : Technical SpecificationsDocument9 pagesFlexi RF Module 3TX 2100 : Technical SpecificationsReza BordbarNo ratings yet

- Transmission Lines (Blake C14) : True/FalseDocument6 pagesTransmission Lines (Blake C14) : True/FalseLovely Eulin FulgarNo ratings yet

- Cell Search Techniques in LTE PaperDocument10 pagesCell Search Techniques in LTE PaperManoj WanjariNo ratings yet

- HFE0111 FirasDocument6 pagesHFE0111 Firaschiase83No ratings yet

- AAU5613 Hardware Description (04) (PDF) - enDocument20 pagesAAU5613 Hardware Description (04) (PDF) - enSurendra MaharjanNo ratings yet

- Adjustable Cable Equalizer Combines Wideband Differential Receiver With Analog SwitchesDocument4 pagesAdjustable Cable Equalizer Combines Wideband Differential Receiver With Analog SwitchesAkhileshKesavanunnithanNo ratings yet

- Coupling-Matrix Design of Dual and Triple Passband FiltersDocument7 pagesCoupling-Matrix Design of Dual and Triple Passband FiltersrallabhandiSKNo ratings yet

- ALARM Description 3GDocument6 pagesALARM Description 3GJaypee Sharma100% (1)

- Altran Private NetworksDocument21 pagesAltran Private NetworkssteadyspikeNo ratings yet

- Chapter 2: Classical Encryption Techniques: Information System SecurityDocument15 pagesChapter 2: Classical Encryption Techniques: Information System SecurityKavin MartinNo ratings yet

- Cisco 1000 Series Integrated Services Routers Ordering Guide 1kseries-Integrated-Services-Routers-GuideDocument23 pagesCisco 1000 Series Integrated Services Routers Ordering Guide 1kseries-Integrated-Services-Routers-Guidemarc1249No ratings yet

- DCS MID - II Set ADocument2 pagesDCS MID - II Set AN.RAMAKUMARNo ratings yet

- Mediterranean Microwave Symposium 2022 - Call For PapersDocument2 pagesMediterranean Microwave Symposium 2022 - Call For PapersMMS2022No ratings yet

- Steganography: Khan, Mohammed MinhajuddinDocument13 pagesSteganography: Khan, Mohammed MinhajuddinShivaEshwariNo ratings yet

- Non Resonant RadiatorsDocument27 pagesNon Resonant RadiatorsNuzhath FathimaNo ratings yet

- Monthly Report in Respect of AIR Lucknow For January 2016Document84 pagesMonthly Report in Respect of AIR Lucknow For January 2016Joshua JacksonNo ratings yet

- BGP Vibroseis Acquisition TechniquesDocument4 pagesBGP Vibroseis Acquisition TechniquesMustapha ChettouhNo ratings yet

- Ele06 - Takehome PrelimDocument3 pagesEle06 - Takehome PrelimEllieNo ratings yet

- DatasheetDocument1 pageDatasheetnomi_nomiNo ratings yet