Professional Documents

Culture Documents

Model2 COA 2022

Model2 COA 2022

Uploaded by

Hritik KaulOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Model2 COA 2022

Model2 COA 2022

Uploaded by

Hritik KaulCopyright:

Available Formats

(Page 1 of 2)

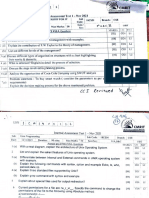

USN 21CST304

Dr. Ambedkar Institute of Technology, Bangalore

B. E. Third Semester End Examination

Model Paper - 2

Computer Organization and Architecture

[Time: 3 Hours ] [ Maximum Marks: 100]

Note: 1. Answer ANY FIVE fully Question.

Marks CO RBT

Level

1.a) Describe the basic functional units of a computer with a neat [10Marks] CO1 L1

diagram.

b) Write a program to evaluate the expression Z= (A + B) × (C + [10Marks] CO1 L2

D) using one address, and two address instruction format.

OR

2.a) What is an addressing mode? Explain different addressing [10Marks] CO1 L1

modes.

b) What are conditional code flags? Explain only four [05Marks] CO1 L2

c) Write a program that evaluate A × B + C × D in a single [05Marks] CO1 L2

accumulator processor.

3.a) Explain the hardware registers that are required in a DMA [06Marks] CO2 L2

controller.

b) Discuss Interrupt I/O method for data transfer. [06Marks] CO2 L2

c) Explain with a block diagram, a general 8-bit parallel interface [08Marks] CO2 L3

OR

4.a) Explain a synchronous bus. Also give the timing diagram of an [06Marks] CO2 L2

input transfer on s synchronous bus.

b) Define the following: [06Marks] CO2 L2

a) Burst Mode.

b) Handshaking Mechanism.

c) What is bus arbitration? Explain the centralized arbitration with [06Marks] CO2 L2

a neat diagram.

5.a) Explain direct mapping and set-associative mapping between [10Marks] CO3 L2

cache memory and main memory.

b) What is a virtual memory? With a neat diagram, explain virtual [10Marks] CO3 L1

memory address translation.

OR

6.a) Describe the terms: [10Marks] CO3 L2

a) locality of reference

b) Replacement algorithms.

b) What is a cache? Explain any two mapping functions. [10Marks] CO3 L2

7.a) With neat diagram, explain the floating –point [10Marks] CO4 L2

addition/subtraction unit

b) With a neat diagram, explain the 4-bit carry look-ahead adder. [10Marks] CO4 L2

OR

Dr. Ambedkar Institute of Technology, Bangalore – 560056

(Autonomous Institution Affiliated to Visvesveraya Technological University, Belgaum)

(Page 2 of 2)

8.a) Explain single bus organization if the processor with a neat [06Marks] CO4 L2

diagram.

b) Discuss how unconditional branching is taken into account in a [07Marks] CO4 L2

control sequence

c) Discuss the organization of hardwired control unit. [07Marks] CO4 L2

9.a) Describe pipelining. [05Marks] CO5 L1

b) Explain the Characteristics of multi-processor [05Marks] CO5 L1

c) What is arithmetic pipeline and explain it clearly? [05Marks] CO5

d) Describe Instruction pipeline. [05Marks] C05

OR

10. Describe the vector processing. [05Marks] CO5 L1

a)

b) Explain the following: [05Marks] CO5 L2

a) Data hazard

b) Control hazard

c) Structural hazard

Dr. Ambedkar Institute of Technology, Bangalore – 560056

(Autonomous Institution Affiliated to Visvesveraya Technological University, Belgaum)

You might also like

- Kit Kat Case StudyDocument6 pagesKit Kat Case Studyms.Ahmed0% (1)

- Management Tri Nova CaseDocument4 pagesManagement Tri Nova CaseAie Kah Dupal100% (2)

- 935 Robert Bosch Interview Questions in C A Micro Controllers PDFDocument2 pages935 Robert Bosch Interview Questions in C A Micro Controllers PDFdhapra0% (1)

- Notice of Liability Regarding Trespassing TechnologyDocument20 pagesNotice of Liability Regarding Trespassing TechnologyJoshua Daniel-SettlorNo ratings yet

- Model1 COA 2022Document2 pagesModel1 COA 2022Hritik KaulNo ratings yet

- 21EIT403 - Model QP - 1Document2 pages21EIT403 - Model QP - 1Adithya A RNo ratings yet

- Vlsi QBDocument5 pagesVlsi QBManaswiNo ratings yet

- MSD Model Latest For 2020 (1) MMN 2023Document2 pagesMSD Model Latest For 2020 (1) MMN 2023srujangowdasj2002No ratings yet

- 21EIT403 - Model QP - 2Document2 pages21EIT403 - Model QP - 2Adithya A RNo ratings yet

- Sree Vidyanikethan Engineering College: III B.Tech II Semester (SVEC-16) Supplementary Examinations March - 2021Document2 pagesSree Vidyanikethan Engineering College: III B.Tech II Semester (SVEC-16) Supplementary Examinations March - 2021Umesh MosurNo ratings yet

- Pcs 3Document2 pagesPcs 3Karan JagannathNo ratings yet

- IoT ELE Model Question Paper 3Document2 pagesIoT ELE Model Question Paper 3SobjianNo ratings yet

- It - Kit 601 - Pes - QP - 31.05.2023Document2 pagesIt - Kit 601 - Pes - QP - 31.05.2023srivastavarishi427No ratings yet

- Coa Cie 1Document1 pageCoa Cie 1Vinay VarumaniNo ratings yet

- Ramaiah: Makeup Examinations - March 2017Document2 pagesRamaiah: Makeup Examinations - March 2017ArunNo ratings yet

- COA Question Paper CAT 1Document1 pageCOA Question Paper CAT 1Thamaraiselvi SNo ratings yet

- CO MP CS45O JUNE 2020Document2 pagesCO MP CS45O JUNE 2020shrinidhipawar09No ratings yet

- Cadcam Iat - 3 Question PaperDocument1 pageCadcam Iat - 3 Question PaperSelvaraj GNo ratings yet

- 18EC56Document3 pages18EC56sha istaNo ratings yet

- Sathish S 18me731 2023 24 Cim Model 1Document3 pagesSathish S 18me731 2023 24 Cim Model 1srujangowdasj2002No ratings yet

- Coa Ese Q (2022)Document2 pagesCoa Ese Q (2022)Aayush Kumar DubeyNo ratings yet

- Os - Set 2Document2 pagesOs - Set 2saraswathiNo ratings yet

- 16ec416-Electronic Measurementsand InstrumentationDocument6 pages16ec416-Electronic Measurementsand InstrumentationAjit PatraNo ratings yet

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Document8 pagesWWW - Manaresults.Co - In: (Electronics and Communication Engineering)Adhvay KrishnaNo ratings yet

- Btech Cs 3 Sem Computer Organization and Architecture kcs302 2022Document2 pagesBtech Cs 3 Sem Computer Organization and Architecture kcs302 2022Harshit dubeyNo ratings yet

- Me 8073 - Unconventional Machining Processes: Kothandaraman Nagar, Dindigul - 624 622Document2 pagesMe 8073 - Unconventional Machining Processes: Kothandaraman Nagar, Dindigul - 624 622balajimeieNo ratings yet

- A18-AC - (EEE, ECE & ECM) - 25-08-2021 - (Regular)Document1 pageA18-AC - (EEE, ECE & ECM) - 25-08-2021 - (Regular)BATHULA BALAKRISHNANo ratings yet

- 14CS2005 2017Document1 page14CS2005 2017Property RequestNo ratings yet

- 3rd Sem Bca BSC It Jan 2023Document27 pages3rd Sem Bca BSC It Jan 2023yATHARTH TyagiNo ratings yet

- Emi QB & BBDocument26 pagesEmi QB & BBswetha bagadi it's good but how it will workNo ratings yet

- IP - PVP23 Question BankDocument9 pagesIP - PVP23 Question Bank23501a0568No ratings yet

- 18EE0216-Power Systems - IIDocument7 pages18EE0216-Power Systems - IIfaisal sbennaNo ratings yet

- 18EC752 - Crypto - Model QP - 2 - 2021-22Document2 pages18EC752 - Crypto - Model QP - 2 - 2021-22Rohan SNo ratings yet

- 16ec416-Electronic Measurementsand InstrumentationDocument6 pages16ec416-Electronic Measurementsand InstrumentationplanningratnagiriNo ratings yet

- VI Sem Jun-July 2005Document10 pagesVI Sem Jun-July 2005Suraj KumarNo ratings yet

- Cmrit: (B) Discuss About TheDocument7 pagesCmrit: (B) Discuss About TheSAKSHI RAINANo ratings yet

- MP2 Coa BCS302 Paper 2022-23Document2 pagesMP2 Coa BCS302 Paper 2022-23mcuthor98No ratings yet

- BMA302 - Computer Aided Design - B Tech ASE 5th SemDocument1 pageBMA302 - Computer Aided Design - B Tech ASE 5th SemArvind KatyayanNo ratings yet

- Adsa Au4Document2 pagesAdsa Au4sridharNo ratings yet

- IV-i Question Bank (r15)Document82 pagesIV-i Question Bank (r15)kd17209No ratings yet

- BCS302 Set 2Document2 pagesBCS302 Set 2megumifushiguru999No ratings yet

- 14CS2005 April May 2018Document2 pages14CS2005 April May 2018Property RequestNo ratings yet

- B) All Sub-Parts of A Question Must Be Answered at One Place Only, Otherwise It Will Not Be Valued. C) Missing Data Can Be Assumed SuitablyDocument1 pageB) All Sub-Parts of A Question Must Be Answered at One Place Only, Otherwise It Will Not Be Valued. C) Missing Data Can Be Assumed SuitablyGayathri KalyankarNo ratings yet

- Jntu Vlsi Systems DesignDocument5 pagesJntu Vlsi Systems Design9010469071No ratings yet

- C Byregowda Institute of Technology: Answer The Following Questions by Selecting ONE Full Question From Each PARTDocument2 pagesC Byregowda Institute of Technology: Answer The Following Questions by Selecting ONE Full Question From Each PARTshirisha gowdaNo ratings yet

- 1st Internals QB 15CS562Document4 pages1st Internals QB 15CS562Manjunath YadavNo ratings yet

- 4th Sem AssignmentsDocument8 pages4th Sem Assignmentszore zoreNo ratings yet

- WWW - Manaresults.Co - In: What Is Barkhausen Criteria For Sustained Oscillation?Document2 pagesWWW - Manaresults.Co - In: What Is Barkhausen Criteria For Sustained Oscillation?TriveniNo ratings yet

- New Horizon College of Engineering, Bangalore: 19CSE33 USNDocument12 pagesNew Horizon College of Engineering, Bangalore: 19CSE33 USNAhmad RazaNo ratings yet

- Mca 1 Sem Computer Organization and Architecture Kca105 2022Document1 pageMca 1 Sem Computer Organization and Architecture Kca105 2022kimog66911No ratings yet

- Bvrajuinstitute Oftechnology, Narsap UR: Code No: A27AF R15Document1 pageBvrajuinstitute Oftechnology, Narsap UR: Code No: A27AF R15rajeshNo ratings yet

- PSP - IA 1 (Non Selected)Document2 pagesPSP - IA 1 (Non Selected)Hamsa A SNo ratings yet

- Nov Dec 2017Document2 pagesNov Dec 2017manashNo ratings yet

- WWW - Manaresults.co - In: Set No. 1Document1 pageWWW - Manaresults.co - In: Set No. 1HaripriyaNo ratings yet

- Copy1-CAO IA 2 FinDocument1 pageCopy1-CAO IA 2 Finmagy1989No ratings yet

- DLD QB - Final - 27.5.23Document5 pagesDLD QB - Final - 27.5.23BHARATH KAMASANINo ratings yet

- VLSIDesignDocument5 pagesVLSIDesignVenkatesh KolatiNo ratings yet

- Instructions To The Candidates I. Answer Five Full QuestionsDocument3 pagesInstructions To The Candidates I. Answer Five Full QuestionsKaran JagannathNo ratings yet

- Cao Iat 1 QP 2019 Set1Document2 pagesCao Iat 1 QP 2019 Set1formyphdNo ratings yet

- Cambridge Institute of Technology: Department of ( (Type in Bold Letters) (Font 14) )Document1 pageCambridge Institute of Technology: Department of ( (Type in Bold Letters) (Font 14) )Mr girishNo ratings yet

- 523 BA19 Ad 01Document5 pages523 BA19 Ad 01ramesh1926No ratings yet

- CAE 1 & 2 PaperDocument9 pagesCAE 1 & 2 Paperlapaw11259No ratings yet

- Attainable Region Theory: An Introduction to Choosing an Optimal ReactorFrom EverandAttainable Region Theory: An Introduction to Choosing an Optimal ReactorNo ratings yet

- Electrochemical Processes in Biological SystemsFrom EverandElectrochemical Processes in Biological SystemsAndrzej LewenstamNo ratings yet

- DLD Unit 2 Combinational Circuits (2022)Document35 pagesDLD Unit 2 Combinational Circuits (2022)Hritik KaulNo ratings yet

- Model1 COA 2022Document2 pagesModel1 COA 2022Hritik KaulNo ratings yet

- COA Assignment 1Document5 pagesCOA Assignment 1Hritik KaulNo ratings yet

- Coa Assignment 2Document5 pagesCoa Assignment 2Hritik KaulNo ratings yet

- 10T SRAM Computing-in-Memory Macros For Binary andDocument15 pages10T SRAM Computing-in-Memory Macros For Binary and그랬구나No ratings yet

- MetaSwitch MG3510Document2 pagesMetaSwitch MG3510MC BklynNo ratings yet

- Homework VolcanoesDocument6 pagesHomework Volcanoesafnofbfqearczc100% (2)

- WRF Hydro User Guide v3.0 CLEANDocument123 pagesWRF Hydro User Guide v3.0 CLEANisraelmpNo ratings yet

- Engineering Properties of Reactive Clay Earthworks in SE QueenslandDocument16 pagesEngineering Properties of Reactive Clay Earthworks in SE QueenslandKamesh KumarNo ratings yet

- 013 Ching Vs CA 181 Scra 9 1990Document2 pages013 Ching Vs CA 181 Scra 9 1990frank japos100% (1)

- Socio Lecture PPT 2Document330 pagesSocio Lecture PPT 2Bhenjo Hernandez BaronaNo ratings yet

- Empowerment DLP (August 01, 2019)Document2 pagesEmpowerment DLP (August 01, 2019)Clars Ramos Beldad100% (2)

- MT 110 Advice of Cheque(s)Document19 pagesMT 110 Advice of Cheque(s)VladimirNo ratings yet

- BTH Thesis ArchiveDocument7 pagesBTH Thesis ArchiveWriteMyPaperForMeFastSingapore100% (1)

- Equipo Ultrasonido TUD300 PDFDocument2 pagesEquipo Ultrasonido TUD300 PDFjoseperezoso100% (1)

- Glutaraldehyde MsdsDocument8 pagesGlutaraldehyde MsdsU.s. Ezhil ArivudainambiNo ratings yet

- United States Court of Appeals, Fourth CircuitDocument4 pagesUnited States Court of Appeals, Fourth CircuitScribd Government DocsNo ratings yet

- LASSOFF v. GOOGLE, INC. - Document No. 5Document2 pagesLASSOFF v. GOOGLE, INC. - Document No. 5Justia.comNo ratings yet

- Waiting at The TableDocument20 pagesWaiting at The TableHelene Forte100% (1)

- Personal Kanban - Mapping Work, Navigating LifeDocument149 pagesPersonal Kanban - Mapping Work, Navigating LifeDario Dorko100% (2)

- 02 - Property Tables and ChartsDocument2 pages02 - Property Tables and ChartsjhamilcarNo ratings yet

- Review Aruna 3Document7 pagesReview Aruna 3Angel Francisco Zacarias MartinezNo ratings yet

- Introduction To Statistical TheoryDocument5 pagesIntroduction To Statistical TheoryAhmad SattarNo ratings yet

- Glossary of Pharmaceutical TermsDocument140 pagesGlossary of Pharmaceutical Termsmohammed goudaNo ratings yet

- Optimization Techniques DraftDocument4 pagesOptimization Techniques DraftTabitha RajNo ratings yet

- KP53V85 Tech ManualDocument106 pagesKP53V85 Tech ManualrichiegranNo ratings yet

- Group 2 - Food World - Batch 2Document11 pagesGroup 2 - Food World - Batch 2Shreya GuptaNo ratings yet

- React JS: Notes For ProfessionalsDocument110 pagesReact JS: Notes For ProfessionalsudNo ratings yet

- Logic Controller: Multitechnology Know-HowDocument12 pagesLogic Controller: Multitechnology Know-HowPrIsmatIIcONo ratings yet

- Company Registration PPT Module 5Document3 pagesCompany Registration PPT Module 5Anonymous uxd1ydNo ratings yet